lec 5 296arch.ppt

- Количество слайдов: 42

Микроконтроллерные системы на кристалле СЕМЕЙСТВО MCS-296 С ИНТЕГРИРОВАННЫМИ СРЕДСТВАМИ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ Лекция 5 проф. Шеховцов Б. Г. Факультет компьютерной инженерии и управления, кафедра ЭВМ, ХНУРЭ Лекция 5 Март 2013 1

Микроконтроллерные системы на кристалле СЕМЕЙСТВО MCS-296 С ИНТЕГРИРОВАННЫМИ СРЕДСТВАМИ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ Лекция 5 проф. Шеховцов Б. Г. Факультет компьютерной инженерии и управления, кафедра ЭВМ, ХНУРЭ Лекция 5 Март 2013 1

ОСНОВНЫЕ ТЕМЫ ЛЕКЦИИ • MCS с цифровыми сигнальными процессорами DSP (Digital Signal Processor). • Характеристики систем MCS -296. • Упрощенная структура i 80296 SA. Лекция 5 , Март 2013 2

ОСНОВНЫЕ ТЕМЫ ЛЕКЦИИ • MCS с цифровыми сигнальными процессорами DSP (Digital Signal Processor). • Характеристики систем MCS -296. • Упрощенная структура i 80296 SA. Лекция 5 , Март 2013 2

MCS с цифровыми сигнальными процессорами — DSP • Задачи по ЦОС стали появляться во многих областях техники при массовом переходе от аналоговых систем управления к цифровым, начиная с 80 -х годов. • Лекция 5 , Март 2013 3

MCS с цифровыми сигнальными процессорами — DSP • Задачи по ЦОС стали появляться во многих областях техники при массовом переходе от аналоговых систем управления к цифровым, начиная с 80 -х годов. • Лекция 5 , Март 2013 3

• Это цифровые фильтры в модемах, радиотелефонах, аудио-, видео- и телевизионной технике, системах слежения за объектами в авиации, космосе и т. д. • Специализированные микропроцессоры — DSP (Digital Signal Processor), которые продвигались на рынок корпорациями Texas Instruments, Motorola, Analog Devices, NEC оказались не в состоянии справиться с возросшим количеством задач. • Для приводов жестких дисков, сканеров, офисных копировальных аппаратов, факс-машин, цифровых видеокамер, модемов и телефонных аппаратов на рынке возникла потребность в микросхемах, которые на одном кристалле выполняли бы функции как обработки событий в реальном времени, так и функции цифровой фильтрации входных сигналов. Лекция 5 Март 2013 4

• Это цифровые фильтры в модемах, радиотелефонах, аудио-, видео- и телевизионной технике, системах слежения за объектами в авиации, космосе и т. д. • Специализированные микропроцессоры — DSP (Digital Signal Processor), которые продвигались на рынок корпорациями Texas Instruments, Motorola, Analog Devices, NEC оказались не в состоянии справиться с возросшим количеством задач. • Для приводов жестких дисков, сканеров, офисных копировальных аппаратов, факс-машин, цифровых видеокамер, модемов и телефонных аппаратов на рынке возникла потребность в микросхемах, которые на одном кристалле выполняли бы функции как обработки событий в реальном времени, так и функции цифровой фильтрации входных сигналов. Лекция 5 Март 2013 4

Высокопроизводительные решения в MCS-296 Фирма Intel одной из первых отреагировала на возникновение спроса на рынке устройств с комбинированными возможностями для обработки, как событий, так и сигналов. • С 1996 г. выпускаются i 80296 SA. SA • Традиционно DSP разрабатывались для выполнения математических функций при цифровой фильтрации сигналов. • • Лекция 5 Март 2013 5

Высокопроизводительные решения в MCS-296 Фирма Intel одной из первых отреагировала на возникновение спроса на рынке устройств с комбинированными возможностями для обработки, как событий, так и сигналов. • С 1996 г. выпускаются i 80296 SA. SA • Традиционно DSP разрабатывались для выполнения математических функций при цифровой фильтрации сигналов. • • Лекция 5 Март 2013 5

MCS-296 ориентированы на использование в приводах жестких дисков, принтерах, сканерах и т. д. ), в копировальной технике, медицинской технике, в телекоммуникационных устройствах и устройствах промышленной автоматики, системах привода с инверторами напряжения (насосы, вентиляторы, кондиционеры, станки, роботы и пр. ). В автомобилестроении в системах управления двигателями внутреннего сгорания, тормозной системой, системой анти блокировки колес и т. д. Лекция 5 Март 2013 6

MCS-296 ориентированы на использование в приводах жестких дисков, принтерах, сканерах и т. д. ), в копировальной технике, медицинской технике, в телекоммуникационных устройствах и устройствах промышленной автоматики, системах привода с инверторами напряжения (насосы, вентиляторы, кондиционеры, станки, роботы и пр. ). В автомобилестроении в системах управления двигателями внутреннего сгорания, тормозной системой, системой анти блокировки колес и т. д. Лекция 5 Март 2013 6

Intel интегрировала следующие идеи, апробированные фирмами-производителями DSP, соединив их с преимуществами регистровой архитектуры MCS-196: • Повышение производительности центрального процессора за счет сокращения времени выборки из памяти программ и данных. Осуществляется предварительная выборка кодов команд с размещением их очередь длиной 10 байт. Практически всегда в очереди есть команда. • Выборка операндов из памяти всегда имеет приоритет над выборкой кодов команд. Лекция 5 Март 2013 7

Intel интегрировала следующие идеи, апробированные фирмами-производителями DSP, соединив их с преимуществами регистровой архитектуры MCS-196: • Повышение производительности центрального процессора за счет сокращения времени выборки из памяти программ и данных. Осуществляется предварительная выборка кодов команд с размещением их очередь длиной 10 байт. Практически всегда в очереди есть команда. • Выборка операндов из памяти всегда имеет приоритет над выборкой кодов команд. Лекция 5 Март 2013 7

• Использование конвейерного режима для резкого сокращения времени командного цикла. • В DSP обычно применяется двух- или трехкаскадный конвейер. Конвейер MCS 296 рассчитан на одновременное выполнение 4 -х команд. • Применение аппаратных умножителей и делителей, которые позволяют резко сократить время выполнения самых распространенных при ЦОС операций, в частности операций умножения с накоплением. Лекция 5 Март 2013 8

• Использование конвейерного режима для резкого сокращения времени командного цикла. • В DSP обычно применяется двух- или трехкаскадный конвейер. Конвейер MCS 296 рассчитан на одновременное выполнение 4 -х команд. • Применение аппаратных умножителей и делителей, которые позволяют резко сократить время выполнения самых распространенных при ЦОС операций, в частности операций умножения с накоплением. Лекция 5 Март 2013 8

• Включение в систему команд специальных команд - цифровой обработки сигналов. MCS-296 имеют 17 новых команд, оптимизированных для решения задач построения цифровых фильтров и регуляторов: умножения с накоплением, повторения, автоматизации обновления данных в таблицах последовательных выборок входных сигналов по мере их использования и т. д. Лекция 5 Март 2013 9

• Включение в систему команд специальных команд - цифровой обработки сигналов. MCS-296 имеют 17 новых команд, оптимизированных для решения задач построения цифровых фильтров и регуляторов: умножения с накоплением, повторения, автоматизации обновления данных в таблицах последовательных выборок входных сигналов по мере их использования и т. д. Лекция 5 Март 2013 9

НАИБОЛЕЕ ВАЖНЫЕ ДАННЫЕ MCS-296 • Тактовая частота 50 Мгц. • 6 Мбайт линейно-адресуемой памяти (Linear Address Space). • 512 байт регистрового ОЗУ (Register RAM). • 2 Кбайта кодовой памяти/памяти данных (Code/Data RAM). • Регистровая архитектура (наличие RALU). • Аппаратная и функциональная совместимость с MCS 8 x. C 196 NP/NU. • 19 источников прерываний, из них 14 прерываний с программируемым приоритетом. • два 16 -разрядных таймера/счетчика с возможностями «квадратурного» счета. Лекция 5 Март 2013 10

НАИБОЛЕЕ ВАЖНЫЕ ДАННЫЕ MCS-296 • Тактовая частота 50 Мгц. • 6 Мбайт линейно-адресуемой памяти (Linear Address Space). • 512 байт регистрового ОЗУ (Register RAM). • 2 Кбайта кодовой памяти/памяти данных (Code/Data RAM). • Регистровая архитектура (наличие RALU). • Аппаратная и функциональная совместимость с MCS 8 x. C 196 NP/NU. • 19 источников прерываний, из них 14 прерываний с программируемым приоритетом. • два 16 -разрядных таймера/счетчика с возможностями «квадратурного» счета. Лекция 5 Март 2013 10

• 3 -х фазный широтно-импульсный модулятор (ШИМ), возможность прямого цифрового управления быстродействующими приводами дисководов. • Полно дуплексный последовательный порт • Набор процессоров событий (Event Processor Array) с 4 -мя высоко скоростными каналами захвата/сравнения. • Умножение с накоплением MAC (multiply and accumulate) с использованием 40 -разрядного аккумулятора всего лишь за 80 нс, что обеспечивает быстродействие в 12. 5 DSP MIPS. • Уникальной особенностью 80296 SA является расширение возможностей оконной адресации внутреннего регистрового ОЗУ на область внешней памяти. Лекция 5 11 Март 2013

• 3 -х фазный широтно-импульсный модулятор (ШИМ), возможность прямого цифрового управления быстродействующими приводами дисководов. • Полно дуплексный последовательный порт • Набор процессоров событий (Event Processor Array) с 4 -мя высоко скоростными каналами захвата/сравнения. • Умножение с накоплением MAC (multiply and accumulate) с использованием 40 -разрядного аккумулятора всего лишь за 80 нс, что обеспечивает быстродействие в 12. 5 DSP MIPS. • Уникальной особенностью 80296 SA является расширение возможностей оконной адресации внутреннего регистрового ОЗУ на область внешней памяти. Лекция 5 11 Март 2013

Модуль выборки внешних устройств имеет: имеет • 6 выводов выборки кристаллов (Chip-Select Pins) внешних устройств. • Динамически мультиплицируемую/ демультиплицируемую шину адреса/ данных для каждого из “чип- селектов”. • Программируемое число тактов ожидания (Wait States) в диапазоне от 0 до 15 для каждого из “чип- селектов”. • Программируемую ширину шины (Bus width) 8 или 16 бит для каждого из “чип- селектов”. • Программируемый диапазон адресов для каждого из “чип- селектов”. На начальной стадии производства 80296 SA Фирма Intel рекомендовала цену 14$. Лекция 5 Март 2013 12

Модуль выборки внешних устройств имеет: имеет • 6 выводов выборки кристаллов (Chip-Select Pins) внешних устройств. • Динамически мультиплицируемую/ демультиплицируемую шину адреса/ данных для каждого из “чип- селектов”. • Программируемое число тактов ожидания (Wait States) в диапазоне от 0 до 15 для каждого из “чип- селектов”. • Программируемую ширину шины (Bus width) 8 или 16 бит для каждого из “чип- селектов”. • Программируемый диапазон адресов для каждого из “чип- селектов”. На начальной стадии производства 80296 SA Фирма Intel рекомендовала цену 14$. Лекция 5 Март 2013 12

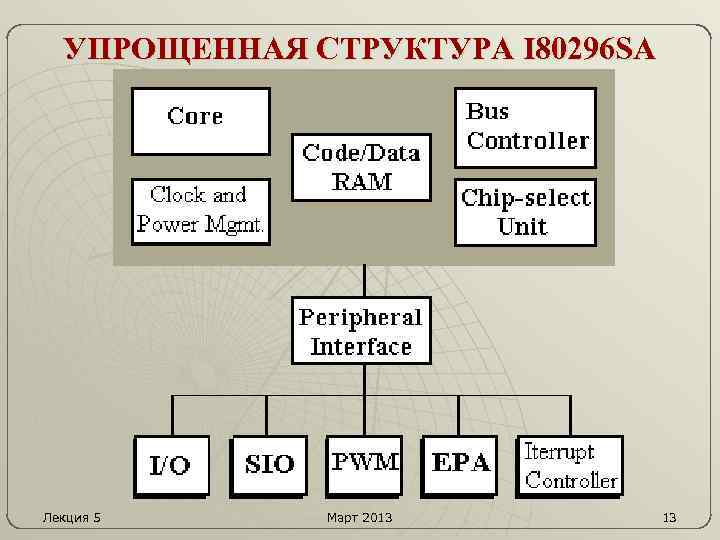

УПРОЩЕННАЯ СТРУКТУРА I 80296 SA Лекция 5 Март 2013 13

УПРОЩЕННАЯ СТРУКТУРА I 80296 SA Лекция 5 Март 2013 13

Главные блоки: Модуль центрального процессора включает ядро, блок тактового генератора и схему управления питанием, ОЗУ программ и данных (Code/Data RAM), контроллер шины (Bus Controller) и модуль выборки внешних устройств (Chip-select Unit). Периферийные устройства порты ввода/вывода (I/O), порт последовательного ввода/вывода (SIO), генератор ШИМ- сигналов (PWM), многоканальный процессор событий (ЕРА) и программируемый контроллер , прерываний (Interrupt Controller). Лекция 5 Март 2013 14

Главные блоки: Модуль центрального процессора включает ядро, блок тактового генератора и схему управления питанием, ОЗУ программ и данных (Code/Data RAM), контроллер шины (Bus Controller) и модуль выборки внешних устройств (Chip-select Unit). Периферийные устройства порты ввода/вывода (I/O), порт последовательного ввода/вывода (SIO), генератор ШИМ- сигналов (PWM), многоканальный процессор событий (ЕРА) и программируемый контроллер , прерываний (Interrupt Controller). Лекция 5 Март 2013 14

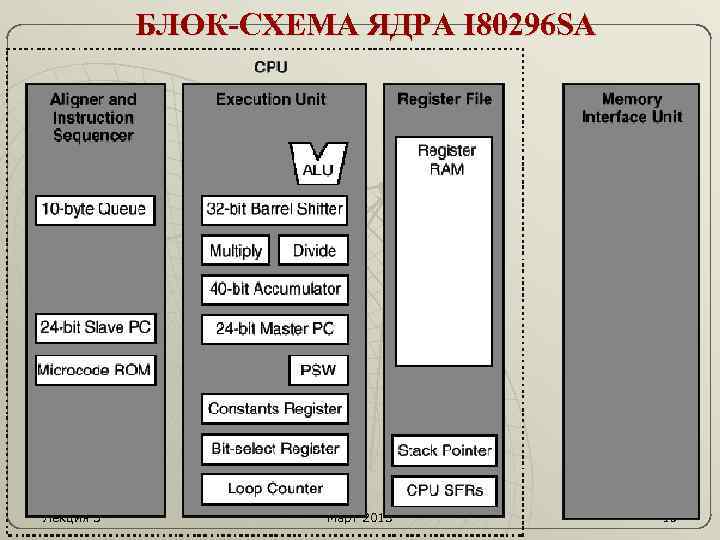

Ниже приводится описание БЛОК-СХЕМЫ ЯДРА I 80296 SA Ознакомиться самостоятельно. Все вопросы на занятиях Лекция 5 Март 2013 15

Ниже приводится описание БЛОК-СХЕМЫ ЯДРА I 80296 SA Ознакомиться самостоятельно. Все вопросы на занятиях Лекция 5 Март 2013 15

БЛОК-СХЕМА ЯДРА I 80296 SA Лекция 5 Март 2013 16

БЛОК-СХЕМА ЯДРА I 80296 SA Лекция 5 Март 2013 16

ЯДРО состоит: • из центрального процессора ЦПУ В состав центрального процессора входят: блок выравнивания (Aligner) и упорядочивания команд (Instruction Sequencer), исполнительный модуль (Execution Unit) и модуль внутреннего регистрового ОЗУ -регистровый файл (Register File). Лекция 5 Март 2013 17

ЯДРО состоит: • из центрального процессора ЦПУ В состав центрального процессора входят: блок выравнивания (Aligner) и упорядочивания команд (Instruction Sequencer), исполнительный модуль (Execution Unit) и модуль внутреннего регистрового ОЗУ -регистровый файл (Register File). Лекция 5 Март 2013 17

• из модуля интерфейса памяти Модуль интерфейса памяти связан с центральным процессором и контроллером шины 24 -разрядной шиной адреса. Младшие 8 разрядов этой шины через интерфейс шин встроенной периферии образуют шину адреса периферийных устройств, которая обеспечивает доступ к контроллеру прерываний и другим встроенным на кристалле периферийным устройствам. Лекция 5 Март 2013 18

• из модуля интерфейса памяти Модуль интерфейса памяти связан с центральным процессором и контроллером шины 24 -разрядной шиной адреса. Младшие 8 разрядов этой шины через интерфейс шин встроенной периферии образуют шину адреса периферийных устройств, которая обеспечивает доступ к контроллеру прерываний и другим встроенным на кристалле периферийным устройствам. Лекция 5 Март 2013 18

CPU С КОНВЕЙЕРНОЙ АРХИТЕКТУРОЙ • Конвейер команд формирует сигналы исполнительному модулю при выполнении операций с байтами, словами или двойными словами, расположенными как в нижнем файле RRAM , так и в любом произвольном месте памяти при оконной адресации операндов. • Два дополнительных индексных регистра IDXO и IDXI обеспечивают быстрый доступ в режиме индексной адресации операндов к любой области 16 -Мбайтового адресного пространства. Лекция 5 Март 2013 19

CPU С КОНВЕЙЕРНОЙ АРХИТЕКТУРОЙ • Конвейер команд формирует сигналы исполнительному модулю при выполнении операций с байтами, словами или двойными словами, расположенными как в нижнем файле RRAM , так и в любом произвольном месте памяти при оконной адресации операндов. • Два дополнительных индексных регистра IDXO и IDXI обеспечивают быстрый доступ в режиме индексной адресации операндов к любой области 16 -Мбайтового адресного пространства. Лекция 5 Март 2013 19

• Индексные регистры в свою очередь могут адресоваться косвенно с помощью так называемых регистров индексных ссылок ICX 0 и ICX 1, являющихся регистрами специального назначения имеющих короткие байтовые адреса в нижнем регистровом файле. • Использование индексных регистров позволяет быстро обратиться к любому операнду в памяти с использованием принципиально нового способа адресации – Kocвенноиндексной адресации. Лекция 5 Март 2013 20

• Индексные регистры в свою очередь могут адресоваться косвенно с помощью так называемых регистров индексных ссылок ICX 0 и ICX 1, являющихся регистрами специального назначения имеющих короткие байтовые адреса в нижнем регистровом файле. • Использование индексных регистров позволяет быстро обратиться к любому операнду в памяти с использованием принципиально нового способа адресации – Kocвенноиндексной адресации. Лекция 5 Март 2013 20

• Команды, извлекаемые из памяти (с помощью модуля интерфейса памяти), поступают в очередь команд длиной 10 байт, из нее в блок упорядочивания команд и далее на конвейер выполнения (Execution pipeline). · Модули выравнивания и упорядочивания команд обеспечивают устойчивый поток команд на конвейер выполнения. Лекция 5 Март 2013 21

• Команды, извлекаемые из памяти (с помощью модуля интерфейса памяти), поступают в очередь команд длиной 10 байт, из нее в блок упорядочивания команд и далее на конвейер выполнения (Execution pipeline). · Модули выравнивания и упорядочивания команд обеспечивают устойчивый поток команд на конвейер выполнения. Лекция 5 Март 2013 21

ВЫПОЛНЕНИЕ КОМАНД НА КОНВЕЙЕРЕ Лекция 5 Март 2013 22

ВЫПОЛНЕНИЕ КОМАНД НА КОНВЕЙЕРЕ Лекция 5 Март 2013 22

ВЫПОЛНЕНИЕ КОМАНД НА КОНВЕЙЕРЕ • Каждая команда на конвейере выполняется в четыре этапа: выборки, декодирования, чтения-выполнения, выполнения-записи. • На первом этапе производится выборка команды № 1. • На втором этапе параллельно выполняются уже два действия: выборка следующей команды № 2 и декодирование предыдущей команды № 1. • На третьем этапе вступает в действие еще одна ступень конвейера: считывается заданный в команде № 1 операнд и выполняются действия, предусмотренные командой после получения операндов -источников (Read-Execute); одновременно производится декодирование команды № 2 и выборка Лекция 5 23 Март 2013 новой команды № 3.

ВЫПОЛНЕНИЕ КОМАНД НА КОНВЕЙЕРЕ • Каждая команда на конвейере выполняется в четыре этапа: выборки, декодирования, чтения-выполнения, выполнения-записи. • На первом этапе производится выборка команды № 1. • На втором этапе параллельно выполняются уже два действия: выборка следующей команды № 2 и декодирование предыдущей команды № 1. • На третьем этапе вступает в действие еще одна ступень конвейера: считывается заданный в команде № 1 операнд и выполняются действия, предусмотренные командой после получения операндов -источников (Read-Execute); одновременно производится декодирование команды № 2 и выборка Лекция 5 23 Март 2013 новой команды № 3.

На четвертом этапе вступает в действие последняя ступень конвейера: выполняется команда № 1 с записью результата по месту назначения операнда-приемника (Execute-Write) и параллельно выполняются циклы считываниявыполнения для команды № 2, декодирования для команды № 3 и выборки команды № 4. • • Далее все ступени конвейера работают параллельно с четырьмя последовательно расположенными в памяти командами. Конвейерная архитектура обеспечивает резкое повышение производительности процессора. Лекция 5 Март 2013 24

На четвертом этапе вступает в действие последняя ступень конвейера: выполняется команда № 1 с записью результата по месту назначения операнда-приемника (Execute-Write) и параллельно выполняются циклы считываниявыполнения для команды № 2, декодирования для команды № 3 и выборки команды № 4. • • Далее все ступени конвейера работают параллельно с четырьмя последовательно расположенными в памяти командами. Конвейерная архитектура обеспечивает резкое повышение производительности процессора. Лекция 5 Март 2013 24

ИСПОЛНИТЕЛЬНЫЙ МОДУЛЬ • Содержит: -16 -разрядное регистровое арифметикологическое устройство РАЛУ; - 32 -разрядный кольцевой регистр сдвига для операций сдвига и 40 -разрядный аккумулятор; 24 -разрядный основной счетчик команд (Master PC), всегда содержит адрес выполнения следующей команды и обеспечивает линейную адресацию памяти команд объемом до 16 Мбайт без сегментирования. - регистр слова состояния программы (PSW), - регистр выбора бит в операндах и счетчик числа циклов. Лекция 5 Март 2013 25

ИСПОЛНИТЕЛЬНЫЙ МОДУЛЬ • Содержит: -16 -разрядное регистровое арифметикологическое устройство РАЛУ; - 32 -разрядный кольцевой регистр сдвига для операций сдвига и 40 -разрядный аккумулятор; 24 -разрядный основной счетчик команд (Master PC), всегда содержит адрес выполнения следующей команды и обеспечивает линейную адресацию памяти команд объемом до 16 Мбайт без сегментирования. - регистр слова состояния программы (PSW), - регистр выбора бит в операндах и счетчик числа циклов. Лекция 5 Март 2013 25

• В РАЛУ выполняются арифметические и логические операции. • Для выполнения деления отдельный модуль, специальный модуль умножения для обычных операций умножения и операций умножения с накоплением multiply-accumulate operations (MAC) для ЦОС. • Схема автоматического инкрементирования вычисляет адрес следующей команды в зависимости от длины текущей. Лекция 5 Март 2013 26

• В РАЛУ выполняются арифметические и логические операции. • Для выполнения деления отдельный модуль, специальный модуль умножения для обычных операций умножения и операций умножения с накоплением multiply-accumulate operations (MAC) для ЦОС. • Схема автоматического инкрементирования вычисляет адрес следующей команды в зависимости от длины текущей. Лекция 5 Март 2013 26

• Счетчик команд загружается непосредственно в командах перехода, вызова и возврата из подпрограмм, обработки прерываний. • Регистр PSW содержит флаг маскируемых прерываний и 6 флагов состояния программы пользователя. • Ускорение вычислений в РАЛУ обеспечивается также использованием регистров-констант (0, 1, 2), например, при инкрементирования и декрементирования. • Счетчик циклов предназначен для подсчета числа сдвигов в операциях сдвига. Лекция 5 Март 2013 27

• Счетчик команд загружается непосредственно в командах перехода, вызова и возврата из подпрограмм, обработки прерываний. • Регистр PSW содержит флаг маскируемых прерываний и 6 флагов состояния программы пользователя. • Ускорение вычислений в РАЛУ обеспечивается также использованием регистров-констант (0, 1, 2), например, при инкрементирования и декрементирования. • Счетчик циклов предназначен для подсчета числа сдвигов в операциях сдвига. Лекция 5 Март 2013 27

МОДУЛЬ ИНТЕРФЕЙСА ПАМЯТИ • Модуль обеспечивает доступ ко всей памяти, за исключением внутреннего регистрового файла. • CPU работает с регистровым файлом непосредственно, а с внутренней памятью программ/данных и внешней памятью — через модуль интерфейса памяти. • Модуль управляет двумя внутренними шинами: 24 -разрядной шиной адреса памяти и 16 -разрядной шиной данных памяти. Внешняя шина адреса/данных формируется уже контроллером шины. Лекция 5 Март 2013 28

МОДУЛЬ ИНТЕРФЕЙСА ПАМЯТИ • Модуль обеспечивает доступ ко всей памяти, за исключением внутреннего регистрового файла. • CPU работает с регистровым файлом непосредственно, а с внутренней памятью программ/данных и внешней памятью — через модуль интерфейса памяти. • Модуль управляет двумя внутренними шинами: 24 -разрядной шиной адреса памяти и 16 -разрядной шиной данных памяти. Внешняя шина адреса/данных формируется уже контроллером шины. Лекция 5 Март 2013 28

• Одна из главных задач модуля состоит в обеспечении предварительной выборки машинных кодов команд из памяти программ и размещение их в очередь на выполнение. • Вторая задача состоит в считывании операндов из памяти и записи результатов выполнения операций в память при работе конвейера команд. • Вторая задача доступа к данным в памяти имеет приоритет над задачей предварительной выборки команд. Лекция 5 Март 2013 29

• Одна из главных задач модуля состоит в обеспечении предварительной выборки машинных кодов команд из памяти программ и размещение их в очередь на выполнение. • Вторая задача состоит в считывании операндов из памяти и записи результатов выполнения операций в память при работе конвейера команд. • Вторая задача доступа к данным в памяти имеет приоритет над задачей предварительной выборки команд. Лекция 5 Март 2013 29

Одновременно процессор отслеживает как бы два потока команд: команд первый –это поток команд, выполняемых на конвейере. второй — поток команд, предварительно выбираемых из памяти и размещаемых в очередь на выполнение. • Основной счетчик команд (Master PC) следит за первым потоком, а вспомогательный (Slave PC) — за вторым. • Если линейная последовательность выполнения команд нарушается (например, при переходе, вызове подпрограммы и т. д. ), то содержимое основного счетчика автоматически перегружается во Лекция 5 Март 2013 вспомогательный и очередь команд очищается. 30

Одновременно процессор отслеживает как бы два потока команд: команд первый –это поток команд, выполняемых на конвейере. второй — поток команд, предварительно выбираемых из памяти и размещаемых в очередь на выполнение. • Основной счетчик команд (Master PC) следит за первым потоком, а вспомогательный (Slave PC) — за вторым. • Если линейная последовательность выполнения команд нарушается (например, при переходе, вызове подпрограммы и т. д. ), то содержимое основного счетчика автоматически перегружается во Лекция 5 Март 2013 вспомогательный и очередь команд очищается. 30

КОНТРОЛЛЕР ШИНЫ И МОДУЛЬ ВЫБОРКИ ВНЕШНИХ УСТРОЙСТВ • Непосредственный доступ к внешней памяти обеспечивает контроллер шины. Кроме обычной 16 -разрядной мультиплицированной шины адреса/данных AD 15: 0 i 80 C 296 SA имеется порт расширенной адресации А 19: 16, что позволяет обращаться к внешней памяти объемом 1 Мбайт с помощью команд, поддерживающих расширенную адресацию. Обращение к внутреннему ОЗУ программ/данных через окно в нижнем регистровом файле производится непосредственно, без участия контроллера шины. Лекция 5 Март 2013 31

КОНТРОЛЛЕР ШИНЫ И МОДУЛЬ ВЫБОРКИ ВНЕШНИХ УСТРОЙСТВ • Непосредственный доступ к внешней памяти обеспечивает контроллер шины. Кроме обычной 16 -разрядной мультиплицированной шины адреса/данных AD 15: 0 i 80 C 296 SA имеется порт расширенной адресации А 19: 16, что позволяет обращаться к внешней памяти объемом 1 Мбайт с помощью команд, поддерживающих расширенную адресацию. Обращение к внутреннему ОЗУ программ/данных через окно в нижнем регистровом файле производится непосредственно, без участия контроллера шины. Лекция 5 Март 2013 31

КОНТРОЛЛЕР ШИНЫ И МОДУЛЬ ВЫБОРКИ ВНЕШНИХ УСТРОЙСТВ • Если оконная адресация не применяется, то доступ к внутреннему ОЗУ осуществляется через контроллер шины. • Модуль выборки внешних устройств упрощает для пользователя подключение внешней памяти и периферии. Имея шесть выходов, модуль допускает подключение до 6 Мбайт внешней памяти. Лекция 5 Март 2013 32

КОНТРОЛЛЕР ШИНЫ И МОДУЛЬ ВЫБОРКИ ВНЕШНИХ УСТРОЙСТВ • Если оконная адресация не применяется, то доступ к внутреннему ОЗУ осуществляется через контроллер шины. • Модуль выборки внешних устройств упрощает для пользователя подключение внешней памяти и периферии. Имея шесть выходов, модуль допускает подключение до 6 Мбайт внешней памяти. Лекция 5 Март 2013 32

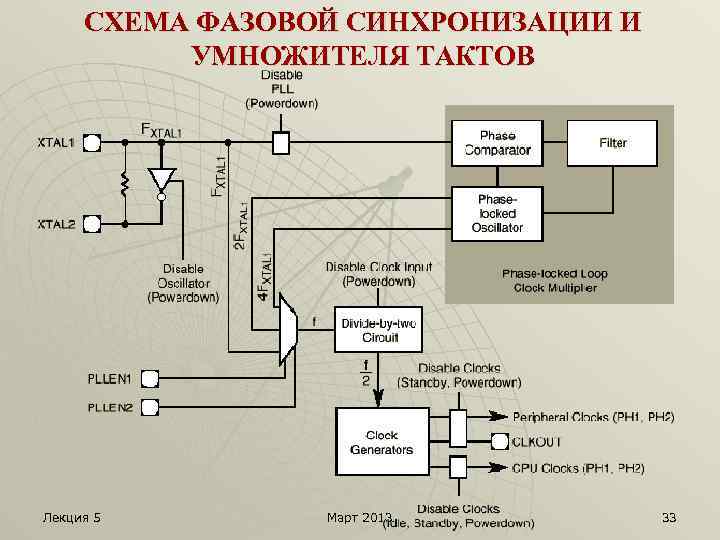

СХЕМА ФАЗОВОЙ СИНХРОНИЗАЦИИ И УМНОЖИТЕЛЯ ТАКТОВ Лекция 5 Март 2013 33

СХЕМА ФАЗОВОЙ СИНХРОНИЗАЦИИ И УМНОЖИТЕЛЯ ТАКТОВ Лекция 5 Март 2013 33

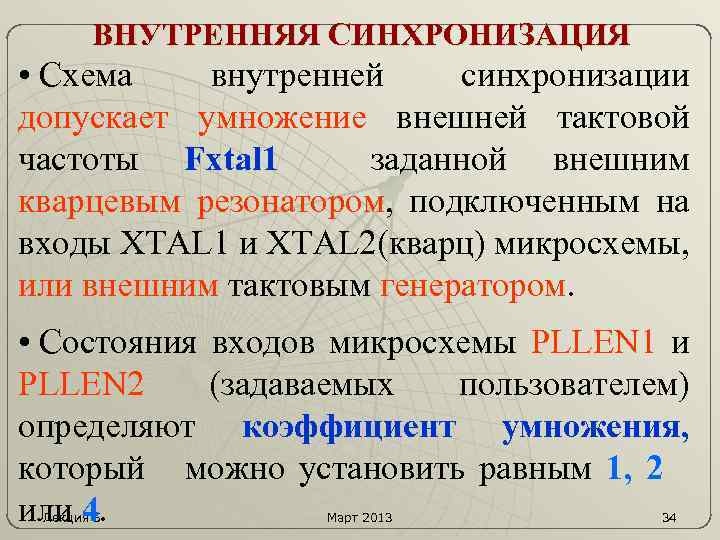

ВНУТРЕННЯЯ СИНХРОНИЗАЦИЯ • Схема внутренней синхронизации допускает умножение внешней тактовой частоты Fxtal 1 заданной внешним кварцевым резонатором, подключенным на входы XTAL 1 и XTAL 2(кварц) микросхемы, или внешним тактовым генератором. • Состояния входов микросхемы PLLEN 1 и PLLEN 2 (задаваемых пользователем) определяют коэффициент умножения, который можно установить равным 1, 2 или 4. Лекция 5 Март 2013 34

ВНУТРЕННЯЯ СИНХРОНИЗАЦИЯ • Схема внутренней синхронизации допускает умножение внешней тактовой частоты Fxtal 1 заданной внешним кварцевым резонатором, подключенным на входы XTAL 1 и XTAL 2(кварц) микросхемы, или внешним тактовым генератором. • Состояния входов микросхемы PLLEN 1 и PLLEN 2 (задаваемых пользователем) определяют коэффициент умножения, который можно установить равным 1, 2 или 4. Лекция 5 Март 2013 34

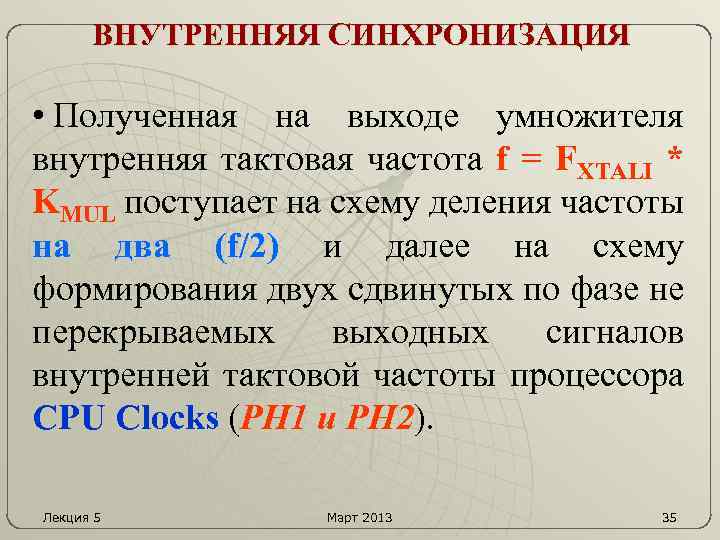

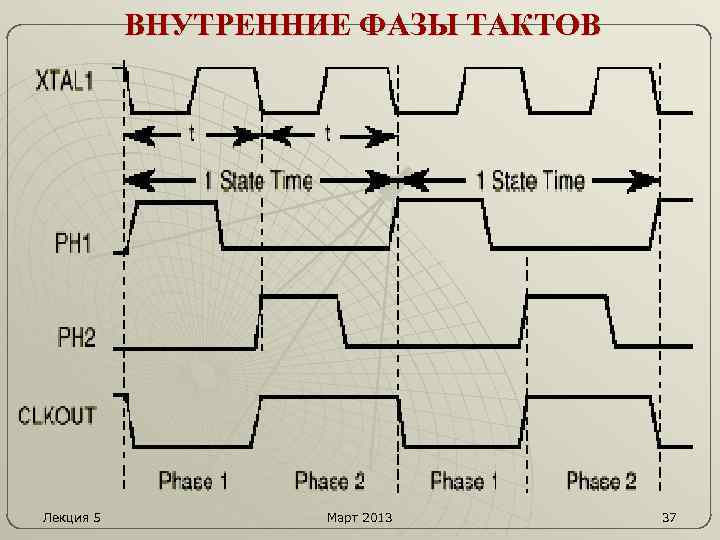

ВНУТРЕННЯЯ СИНХРОНИЗАЦИЯ • Полученная на выходе умножителя внутренняя тактовая частота f = FXTALI * KMUL поступает на схему деления частоты на два (f/2) и далее на схему формирования двух сдвинутых по фазе не перекрываемых выходных сигналов внутренней тактовой частоты процессора CPU Clocks (PH 1 и РН 2). Лекция 5 Март 2013 35

ВНУТРЕННЯЯ СИНХРОНИЗАЦИЯ • Полученная на выходе умножителя внутренняя тактовая частота f = FXTALI * KMUL поступает на схему деления частоты на два (f/2) и далее на схему формирования двух сдвинутых по фазе не перекрываемых выходных сигналов внутренней тактовой частоты процессора CPU Clocks (PH 1 и РН 2). Лекция 5 Март 2013 35

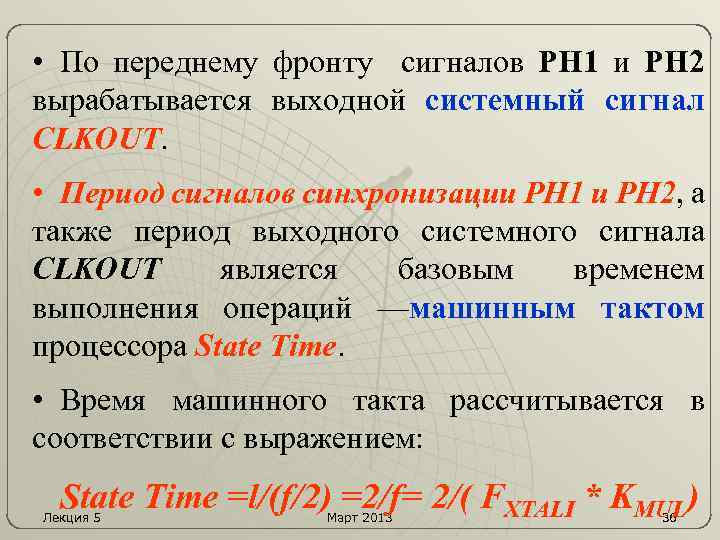

• По переднему фронту сигналов PH 1 и РН 2 вырабатывается выходной системный сигнал CLKOUT. • Период сигналов синхронизации РН 1 и РН 2, а также период выходного системного сигнала CLKOUT является базовым временем выполнения операций —машинным тактом процессора State Time. • Время машинного такта рассчитывается в соответствии с выражением: State Time =l/(f/2) =2/f= 2/( FXTALI * KMUL) Лекция 5 Март 2013 36

• По переднему фронту сигналов PH 1 и РН 2 вырабатывается выходной системный сигнал CLKOUT. • Период сигналов синхронизации РН 1 и РН 2, а также период выходного системного сигнала CLKOUT является базовым временем выполнения операций —машинным тактом процессора State Time. • Время машинного такта рассчитывается в соответствии с выражением: State Time =l/(f/2) =2/f= 2/( FXTALI * KMUL) Лекция 5 Март 2013 36

ВНУТРЕННИЕ ФАЗЫ ТАКТОВ Лекция 5 Март 2013 37

ВНУТРЕННИЕ ФАЗЫ ТАКТОВ Лекция 5 Март 2013 37

МОНИТОРИНГ ПИТАНИЯ ПРОЦЕССОРА • В 80 C 296 SA предусмотрены три специальных режима экономии электроэнергии за счет остановки внутренних “системных сигналов” и перевода процессора в неактивное состояние: режим ожидания (idle); режим резерва (standby); режим отключения питания (power down). Лекция 5 Март 2013 38

МОНИТОРИНГ ПИТАНИЯ ПРОЦЕССОРА • В 80 C 296 SA предусмотрены три специальных режима экономии электроэнергии за счет остановки внутренних “системных сигналов” и перевода процессора в неактивное состояние: режим ожидания (idle); режим резерва (standby); режим отключения питания (power down). Лекция 5 Март 2013 38

• Режимы экономии энергии разрешаются при конфигурировании системы. • Активизируется режим экономии после выполнения команды IDLPD #key с соответствующим значением ключа - 1, 2, 3. • В режиме ожидания (idle) ЦП прекращает выполнять команды, однако тактирование и работа периферийных устройств продолжаются. Потребляемая мощность снижается до 40%. • Выходит из неактивного режима при сбросе системы или по внутреннему запросу на прерывание. Лекция 5 Март 2013 39

• Режимы экономии энергии разрешаются при конфигурировании системы. • Активизируется режим экономии после выполнения команды IDLPD #key с соответствующим значением ключа - 1, 2, 3. • В режиме ожидания (idle) ЦП прекращает выполнять команды, однако тактирование и работа периферийных устройств продолжаются. Потребляемая мощность снижается до 40%. • Выходит из неактивного режима при сбросе системы или по внутреннему запросу на прерывание. Лекция 5 Март 2013 39

• В режиме резерва (standby) все внутренние сигналы процессора, в том числе “сигналы для периферийных устройств”, заморожены. Работает только генератор тактовой частоты. Потребляемая мощность снижается до уровня 10%. Выход из режима резерва производится по сбросу системы или при поступлении внешнего разрешенного прерывания. • В режиме отключения питания (power down) “заморожены” не только внутренние сигналы процессора, но и тактовый генератор. Потребление снижается до уровня микро-Ватт. В этом режиме содержимое RRAM, SFRs сохраняется неизменным (если питание на процессор подается). Лекция 5 Март 2013 40

• В режиме резерва (standby) все внутренние сигналы процессора, в том числе “сигналы для периферийных устройств”, заморожены. Работает только генератор тактовой частоты. Потребляемая мощность снижается до уровня 10%. Выход из режима резерва производится по сбросу системы или при поступлении внешнего разрешенного прерывания. • В режиме отключения питания (power down) “заморожены” не только внутренние сигналы процессора, но и тактовый генератор. Потребление снижается до уровня микро-Ватт. В этом режиме содержимое RRAM, SFRs сохраняется неизменным (если питание на процессор подается). Лекция 5 Март 2013 40

ВЫВОДЫ • Использование конвейерной архитектуры центрального процессора позволило в несколько раз повысить производительность MCS-296 по сравнению со своими предшественниками MCS-196. • Встроенный сигнальный процессор среднего быстродействия расширил области применения микроконтроллерных систем на кристалле задачами, в которых требуется сочетание высокой производительности процессора как при обработке внешних событий, так и при обработке сигналов. событий сигналов Лекция 5 Март 2013 41

ВЫВОДЫ • Использование конвейерной архитектуры центрального процессора позволило в несколько раз повысить производительность MCS-296 по сравнению со своими предшественниками MCS-196. • Встроенный сигнальный процессор среднего быстродействия расширил области применения микроконтроллерных систем на кристалле задачами, в которых требуется сочетание высокой производительности процессора как при обработке внешних событий, так и при обработке сигналов. событий сигналов Лекция 5 Март 2013 41

• Процессор 80 C 296 SA не имеет встроенного аналого-цифрового преобразователя и должен комплектоваться внешним АЦП • Видимо это связано с возросшими требованиями к АЦП по времени преобразования и нецелесообразностью размещения на кристалле относительно медленного последовательного АЦП процессоров MCS-196. Лекция 5 Март 2013 42

• Процессор 80 C 296 SA не имеет встроенного аналого-цифрового преобразователя и должен комплектоваться внешним АЦП • Видимо это связано с возросшими требованиями к АЦП по времени преобразования и нецелесообразностью размещения на кристалле относительно медленного последовательного АЦП процессоров MCS-196. Лекция 5 Март 2013 42