325ab97f0c41a4e9b49ebbc8f52be2a5.ppt

- Количество слайдов: 26

Microsystem and So. C Design with UMIPS Lecturer Michael S. Mc. Corquodale Authors Michael S. Mc. Corquodale, Eric D. Marsman, Robert M. Senger, Fadi H. Gebara, Matthew R. Guthaus, Daniel J. Burke, and Richard B. Brown Solid State Electronics Laboratory Center for Wireless Integrated Microsystems (WIMS) Department of Electrical Engineering and Computer Science University of Michigan Ann Arbor, MI USA 48109 -2122 IFIP International Conference on VLSI-So. C, Darmstadt, Germany, 2003

Microsystem and So. C Design with UMIPS Lecturer Michael S. Mc. Corquodale Authors Michael S. Mc. Corquodale, Eric D. Marsman, Robert M. Senger, Fadi H. Gebara, Matthew R. Guthaus, Daniel J. Burke, and Richard B. Brown Solid State Electronics Laboratory Center for Wireless Integrated Microsystems (WIMS) Department of Electrical Engineering and Computer Science University of Michigan Ann Arbor, MI USA 48109 -2122 IFIP International Conference on VLSI-So. C, Darmstadt, Germany, 2003

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Lecture Overview • Wireless Integrated Microsystems • Background on IP • Review of IP formats and nomenclature • Overview of previous research • UMIPS as a research IP repository • A microsystem design with UMIPS • Conclusions and future work NSF ERC for Wireless Integrated Micro. Systems (WIMS) 2

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Lecture Overview • Wireless Integrated Microsystems • Background on IP • Review of IP formats and nomenclature • Overview of previous research • UMIPS as a research IP repository • A microsystem design with UMIPS • Conclusions and future work NSF ERC for Wireless Integrated Micro. Systems (WIMS) 2

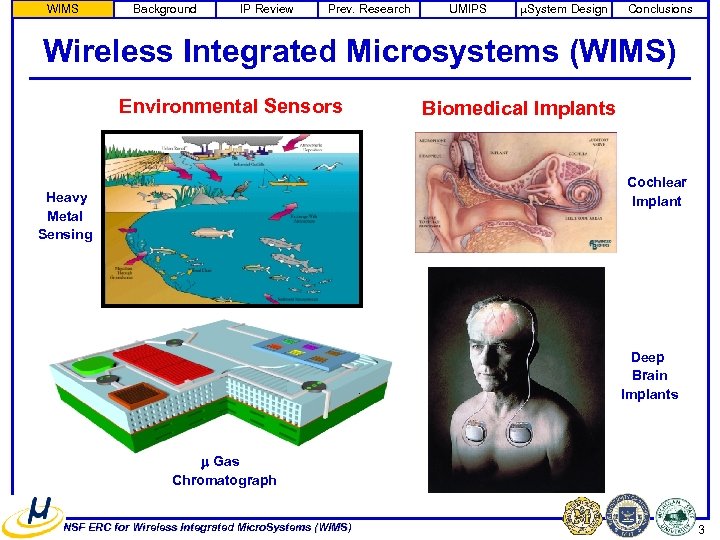

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Wireless Integrated Microsystems (WIMS) Environmental Sensors Biomedical Implants Cochlear Implant Heavy Metal Sensing Deep Brain Implants m Gas Chromatograph NSF ERC for Wireless Integrated Micro. Systems (WIMS) 3

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Wireless Integrated Microsystems (WIMS) Environmental Sensors Biomedical Implants Cochlear Implant Heavy Metal Sensing Deep Brain Implants m Gas Chromatograph NSF ERC for Wireless Integrated Micro. Systems (WIMS) 3

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Background on IP • Semiconductor design-productivity gap – Design productivity increasing by ~28%/yr. – Capacity increasing by ~58%/yr. • ASIC vs. So. C – ASIC productivity increased by 2. 5 X from 1996 -2000 – So. C productivity increased by 7 X from 1996 -2000 • Why the difference? – IP design and reuse • Challenges – Need for repositories and standards – Need for analog/RF and mixed-signal IP – VCX, D&R, etc. exist for industry, what about the research community? • UMIPS – University of Michigan Intellectual Property Source – Focus on digital, analog, RF, and MEMS IP – First a review NSF ERC for Wireless Integrated Micro. Systems (WIMS) 4

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Background on IP • Semiconductor design-productivity gap – Design productivity increasing by ~28%/yr. – Capacity increasing by ~58%/yr. • ASIC vs. So. C – ASIC productivity increased by 2. 5 X from 1996 -2000 – So. C productivity increased by 7 X from 1996 -2000 • Why the difference? – IP design and reuse • Challenges – Need for repositories and standards – Need for analog/RF and mixed-signal IP – VCX, D&R, etc. exist for industry, what about the research community? • UMIPS – University of Michigan Intellectual Property Source – Focus on digital, analog, RF, and MEMS IP – First a review NSF ERC for Wireless Integrated Micro. Systems (WIMS) 4

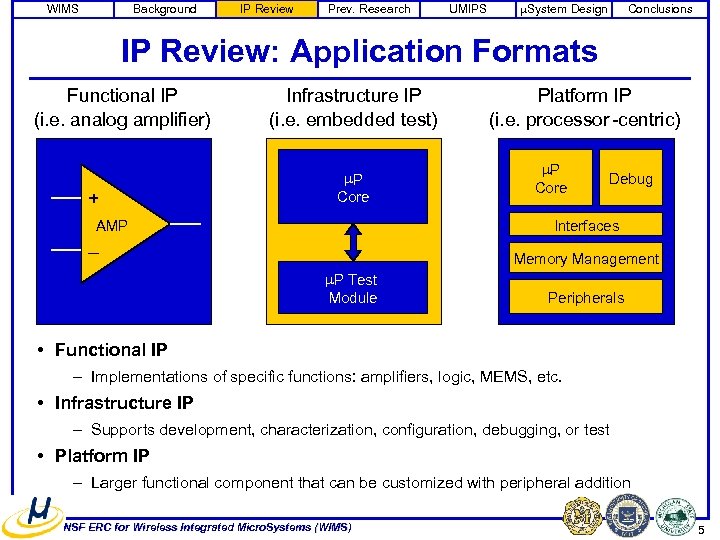

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions IP Review: Application Formats Functional IP (i. e. analog amplifier) + Infrastructure IP (i. e. embedded test) m. P Core AMP Platform IP (i. e. processor -centric) m. P Core Debug Interfaces _ Memory Management m. P Test Module Peripherals • Functional IP – Implementations of specific functions: amplifiers, logic, MEMS, etc. • Infrastructure IP – Supports development, characterization, configuration, debugging, or test • Platform IP – Larger functional component that can be customized with peripheral addition NSF ERC for Wireless Integrated Micro. Systems (WIMS) 5

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions IP Review: Application Formats Functional IP (i. e. analog amplifier) + Infrastructure IP (i. e. embedded test) m. P Core AMP Platform IP (i. e. processor -centric) m. P Core Debug Interfaces _ Memory Management m. P Test Module Peripherals • Functional IP – Implementations of specific functions: amplifiers, logic, MEMS, etc. • Infrastructure IP – Supports development, characterization, configuration, debugging, or test • Platform IP – Larger functional component that can be customized with peripheral addition NSF ERC for Wireless Integrated Micro. Systems (WIMS) 5

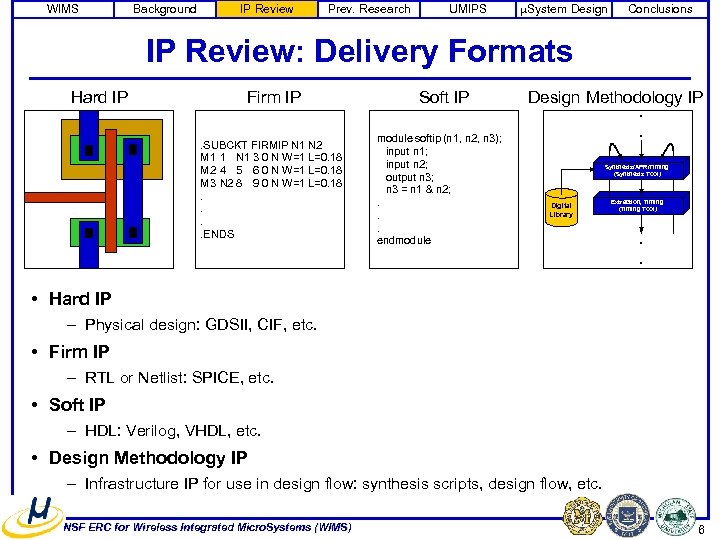

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions IP Review: Delivery Formats Hard IP Firm IP. SUBCKT FIRMIP N 1 N 2 M 1 1 N 1 3 0 N W=1 L=0. 18 M 2 4 5 6 0 N W=1 L=0. 18 M 3 N 2 8 9 0 N W=1 L=0. 18. . ENDS Soft IP module softip (n 1, n 2, n 3); input n 1; input n 2; output n 3; n 3 = n 1 & n 2; . . . endmodule Design Methodology IP. . Synthesis/APR/Timing (Synthesis Tool) Digital Library Extraction, Timing (Timing Tool) . . • Hard IP – Physical design: GDSII, CIF, etc. • Firm IP – RTL or Netlist: SPICE, etc. • Soft IP – HDL: Verilog, VHDL, etc. • Design Methodology IP – Infrastructure IP for use in design flow: synthesis scripts, design flow, etc. NSF ERC for Wireless Integrated Micro. Systems (WIMS) 6

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions IP Review: Delivery Formats Hard IP Firm IP. SUBCKT FIRMIP N 1 N 2 M 1 1 N 1 3 0 N W=1 L=0. 18 M 2 4 5 6 0 N W=1 L=0. 18 M 3 N 2 8 9 0 N W=1 L=0. 18. . ENDS Soft IP module softip (n 1, n 2, n 3); input n 1; input n 2; output n 3; n 3 = n 1 & n 2; . . . endmodule Design Methodology IP. . Synthesis/APR/Timing (Synthesis Tool) Digital Library Extraction, Timing (Timing Tool) . . • Hard IP – Physical design: GDSII, CIF, etc. • Firm IP – RTL or Netlist: SPICE, etc. • Soft IP – HDL: Verilog, VHDL, etc. • Design Methodology IP – Infrastructure IP for use in design flow: synthesis scripts, design flow, etc. NSF ERC for Wireless Integrated Micro. Systems (WIMS) 6

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Previous Research Projects • Independent research projects – Monolithic & Top-Down Clock Synthesis with Micromachined RF Reference M. S. Mc. Corquodale – 900 m. V Analog Front End for Low Power Applications F. H. Gebara – 16 -Bit Low-Power Microcontroller and Peripherals for Sensor Processing R. M. Senger, E. D. Marsman, M. R. Guthaus, D. J. Burke • The concept – Convert projects into IP-blocks – Develop microsystem including each project – Target development toward test beds for WIMS – First some background on each project NSF ERC for Wireless Integrated Micro. Systems (WIMS) 7

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Previous Research Projects • Independent research projects – Monolithic & Top-Down Clock Synthesis with Micromachined RF Reference M. S. Mc. Corquodale – 900 m. V Analog Front End for Low Power Applications F. H. Gebara – 16 -Bit Low-Power Microcontroller and Peripherals for Sensor Processing R. M. Senger, E. D. Marsman, M. R. Guthaus, D. J. Burke • The concept – Convert projects into IP-blocks – Develop microsystem including each project – Target development toward test beds for WIMS – First some background on each project NSF ERC for Wireless Integrated Micro. Systems (WIMS) 7

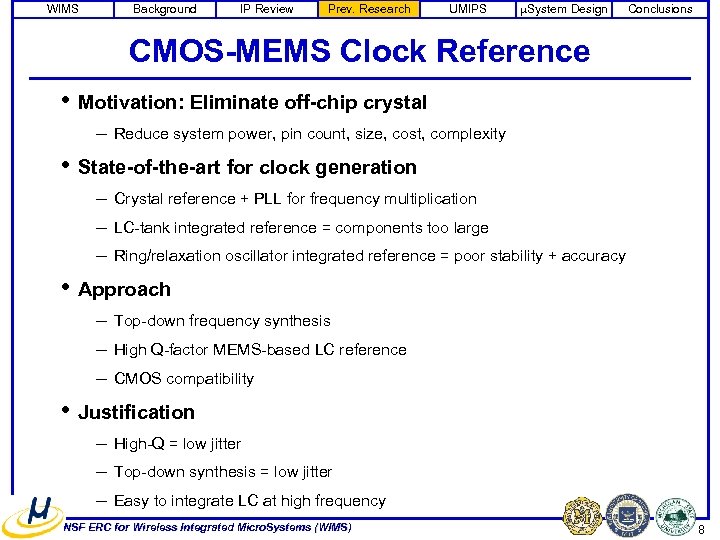

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions CMOS-MEMS Clock Reference • Motivation: Eliminate off-chip crystal – Reduce system power, pin count, size, cost, complexity • State-of-the-art for clock generation – Crystal reference + PLL for frequency multiplication – LC-tank integrated reference = components too large – Ring/relaxation oscillator integrated reference = poor stability + accuracy • Approach – Top-down frequency synthesis – High Q-factor MEMS-based LC reference – CMOS compatibility • Justification – High-Q = low jitter – Top-down synthesis = low jitter – Easy to integrate LC at high frequency NSF ERC for Wireless Integrated Micro. Systems (WIMS) 8

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions CMOS-MEMS Clock Reference • Motivation: Eliminate off-chip crystal – Reduce system power, pin count, size, cost, complexity • State-of-the-art for clock generation – Crystal reference + PLL for frequency multiplication – LC-tank integrated reference = components too large – Ring/relaxation oscillator integrated reference = poor stability + accuracy • Approach – Top-down frequency synthesis – High Q-factor MEMS-based LC reference – CMOS compatibility • Justification – High-Q = low jitter – Top-down synthesis = low jitter – Easy to integrate LC at high frequency NSF ERC for Wireless Integrated Micro. Systems (WIMS) 8

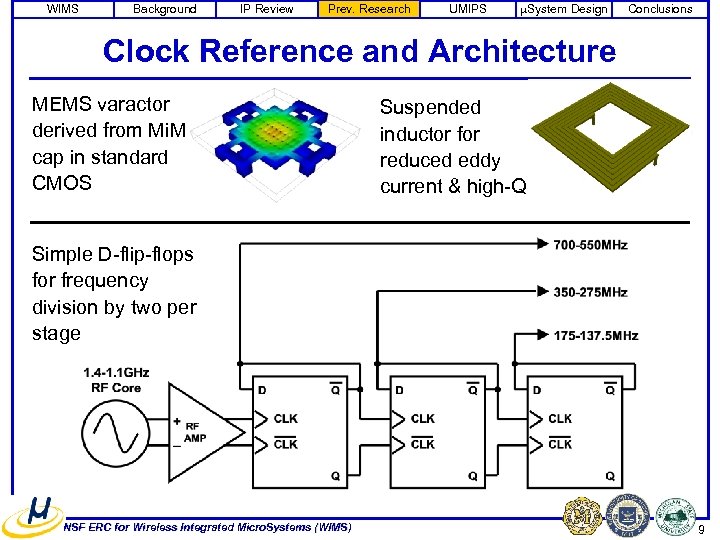

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Clock Reference and Architecture MEMS varactor derived from Mi. M cap in standard CMOS Suspended inductor for reduced eddy current & high-Q Simple D-flip-flops for frequency division by two per stage NSF ERC for Wireless Integrated Micro. Systems (WIMS) 9

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Clock Reference and Architecture MEMS varactor derived from Mi. M cap in standard CMOS Suspended inductor for reduced eddy current & high-Q Simple D-flip-flops for frequency division by two per stage NSF ERC for Wireless Integrated Micro. Systems (WIMS) 9

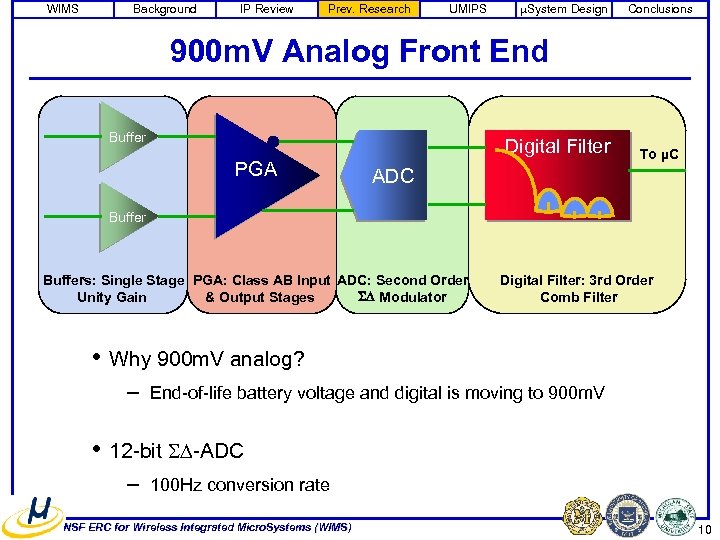

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions 900 m. V Analog Front End Buffer Digital Filter PGA To µC ADC Buffers: Single Stage PGA: Class AB Input ADC: Second Order Unity Gain & Output Stages SD Modulator Digital Filter: 3 rd Order Comb Filter • Why 900 m. V analog? – End-of-life battery voltage and digital is moving to 900 m. V • 12 -bit SD-ADC – 100 Hz conversion rate NSF ERC for Wireless Integrated Micro. Systems (WIMS) 10

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions 900 m. V Analog Front End Buffer Digital Filter PGA To µC ADC Buffers: Single Stage PGA: Class AB Input ADC: Second Order Unity Gain & Output Stages SD Modulator Digital Filter: 3 rd Order Comb Filter • Why 900 m. V analog? – End-of-life battery voltage and digital is moving to 900 m. V • 12 -bit SD-ADC – 100 Hz conversion rate NSF ERC for Wireless Integrated Micro. Systems (WIMS) 10

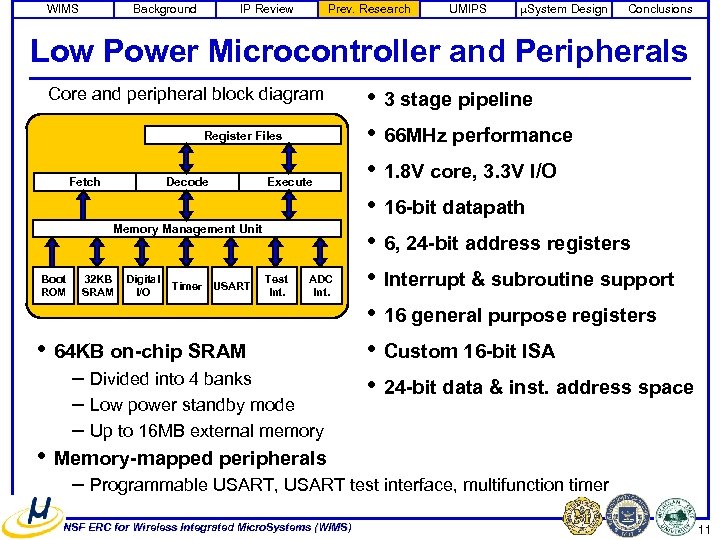

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Low Power Microcontroller and Peripherals Core and peripheral block diagram Register Files Fetch Decode Execute Memory Management Unit Boot ROM 32 KB SRAM Digital I/O Timer USART Test Int. ADC Int. • 64 KB on-chip SRAM – Divided into 4 banks – Low power standby mode – Up to 16 MB external memory • 3 stage pipeline • 66 MHz performance • 1. 8 V core, 3. 3 V I/O • 16 -bit datapath • 6, 24 -bit address registers • Interrupt & subroutine support • 16 general purpose registers • Custom 16 -bit ISA • 24 -bit data & inst. address space • Memory-mapped peripherals – Programmable USART, USART test interface, multifunction timer NSF ERC for Wireless Integrated Micro. Systems (WIMS) 11

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Low Power Microcontroller and Peripherals Core and peripheral block diagram Register Files Fetch Decode Execute Memory Management Unit Boot ROM 32 KB SRAM Digital I/O Timer USART Test Int. ADC Int. • 64 KB on-chip SRAM – Divided into 4 banks – Low power standby mode – Up to 16 MB external memory • 3 stage pipeline • 66 MHz performance • 1. 8 V core, 3. 3 V I/O • 16 -bit datapath • 6, 24 -bit address registers • Interrupt & subroutine support • 16 general purpose registers • Custom 16 -bit ISA • 24 -bit data & inst. address space • Memory-mapped peripherals – Programmable USART, USART test interface, multifunction timer NSF ERC for Wireless Integrated Micro. Systems (WIMS) 11

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions UMIPS a Research IP Repository: Mission • Previously described IP marked the founding contributions • Why found UMIPS? – UMIPS was founded due to the lack of research IP • Mission – UMIPS is a collaborative effort between Electrical Engineering and Computer Science students, faculty, and researchers to leverage each others’ integrated circuit development in the pursuit of cutting-edge microsystems and So. C research • Motivation: Benefits of design reuse to research – Elimination of repetitive basic design activities – Research IP repository can support many semiconductor technologies – Student experience NSF ERC for Wireless Integrated Micro. Systems (WIMS) 12

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions UMIPS a Research IP Repository: Mission • Previously described IP marked the founding contributions • Why found UMIPS? – UMIPS was founded due to the lack of research IP • Mission – UMIPS is a collaborative effort between Electrical Engineering and Computer Science students, faculty, and researchers to leverage each others’ integrated circuit development in the pursuit of cutting-edge microsystems and So. C research • Motivation: Benefits of design reuse to research – Elimination of repetitive basic design activities – Research IP repository can support many semiconductor technologies – Student experience NSF ERC for Wireless Integrated Micro. Systems (WIMS) 12

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions UMIPS: Interface and Access • UMIPS is managed by founders at UMICH – Accessible by all researchers in the academic community – For noncommercial use only • UMIPS submissions – Received and posted submissions from UMICH & other institutions • Access – Main internet portal: www. eecs. umich. edu/umips – Nonproprietary descriptions of the IP components • UMIPS IP Checkout – Submit a request for IP to the management team – Authentication info. provided for the specific IP NSF ERC for Wireless Integrated Micro. Systems (WIMS) 13

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions UMIPS: Interface and Access • UMIPS is managed by founders at UMICH – Accessible by all researchers in the academic community – For noncommercial use only • UMIPS submissions – Received and posted submissions from UMICH & other institutions • Access – Main internet portal: www. eecs. umich. edu/umips – Nonproprietary descriptions of the IP components • UMIPS IP Checkout – Submit a request for IP to the management team – Authentication info. provided for the specific IP NSF ERC for Wireless Integrated Micro. Systems (WIMS) 13

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions UMIPS: Supported IP • UMIPS supported IP – Application formats: functional and structural – Delivery formats: hard, soft, and design methodology formats – Platform and firm IP not supported currently • Organized by function and by process technology – All MOSIS supported processes – Future: UMIPS will support IP specific internal solid-state electronics laboratory as well as MEMS foundries NSF ERC for Wireless Integrated Micro. Systems (WIMS) 14

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions UMIPS: Supported IP • UMIPS supported IP – Application formats: functional and structural – Delivery formats: hard, soft, and design methodology formats – Platform and firm IP not supported currently • Organized by function and by process technology – All MOSIS supported processes – Future: UMIPS will support IP specific internal solid-state electronics laboratory as well as MEMS foundries NSF ERC for Wireless Integrated Micro. Systems (WIMS) 14

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions UMIPS: Standards and Quality Control • Deliverables for all IP – Description, specification, README • Deliverables for Soft IP – Synthesizable HDL, test fixture and vectors, synthesis scripts, process specific details • Deliverables for Hard IP – Netlist, physical design, map table, routing file, verification reports, verification decks, model files, HDL model, test vectors • Details in proceedings NSF ERC for Wireless Integrated Micro. Systems (WIMS) 15

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions UMIPS: Standards and Quality Control • Deliverables for all IP – Description, specification, README • Deliverables for Soft IP – Synthesizable HDL, test fixture and vectors, synthesis scripts, process specific details • Deliverables for Hard IP – Netlist, physical design, map table, routing file, verification reports, verification decks, model files, HDL model, test vectors • Details in proceedings NSF ERC for Wireless Integrated Micro. Systems (WIMS) 15

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions UMIPS: Qualification Metrics • Pre-silicon verified – Simulation, extraction, and verification – Least rigorous • Post-silicon verified – Verified by test – Most rigorous • Uninstantiated – Has not been developed into larger project • Instantiated – Has been developed into larger project – Indicates deliverables are indeed sufficient NSF ERC for Wireless Integrated Micro. Systems (WIMS) 16

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions UMIPS: Qualification Metrics • Pre-silicon verified – Simulation, extraction, and verification – Least rigorous • Post-silicon verified – Verified by test – Most rigorous • Uninstantiated – Has not been developed into larger project • Instantiated – Has been developed into larger project – Indicates deliverables are indeed sufficient NSF ERC for Wireless Integrated Micro. Systems (WIMS) 16

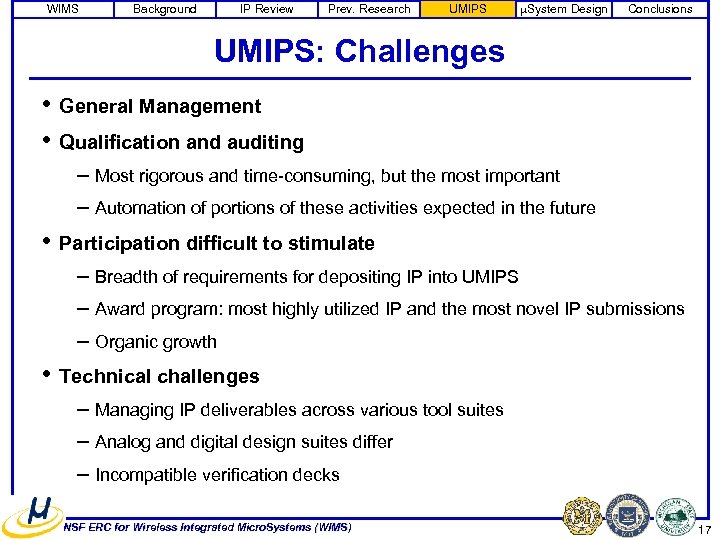

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions UMIPS: Challenges • General Management • Qualification and auditing – Most rigorous and time-consuming, but the most important – Automation of portions of these activities expected in the future • Participation difficult to stimulate – Breadth of requirements for depositing IP into UMIPS – Award program: most highly utilized IP and the most novel IP submissions – Organic growth • Technical challenges – Managing IP deliverables across various tool suites – Analog and digital design suites differ – Incompatible verification decks NSF ERC for Wireless Integrated Micro. Systems (WIMS) 17

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions UMIPS: Challenges • General Management • Qualification and auditing – Most rigorous and time-consuming, but the most important – Automation of portions of these activities expected in the future • Participation difficult to stimulate – Breadth of requirements for depositing IP into UMIPS – Award program: most highly utilized IP and the most novel IP submissions – Organic growth • Technical challenges – Managing IP deliverables across various tool suites – Analog and digital design suites differ – Incompatible verification decks NSF ERC for Wireless Integrated Micro. Systems (WIMS) 17

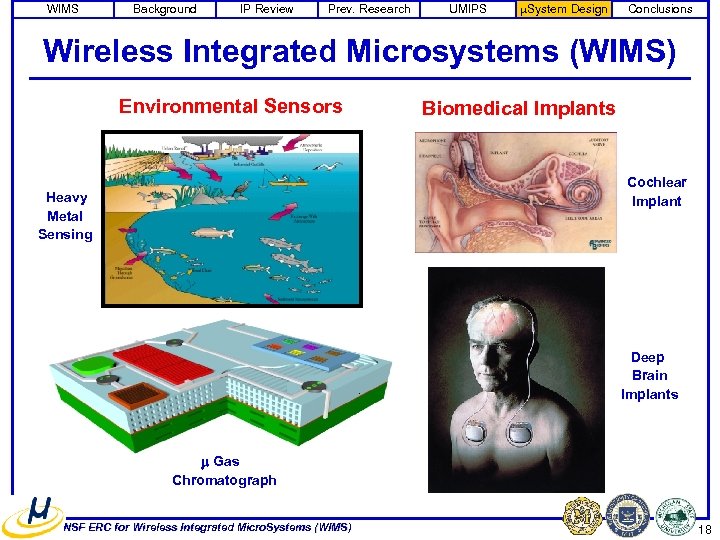

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Wireless Integrated Microsystems (WIMS) Environmental Sensors Biomedical Implants Cochlear Implant Heavy Metal Sensing Deep Brain Implants m Gas Chromatograph NSF ERC for Wireless Integrated Micro. Systems (WIMS) 18

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Wireless Integrated Microsystems (WIMS) Environmental Sensors Biomedical Implants Cochlear Implant Heavy Metal Sensing Deep Brain Implants m Gas Chromatograph NSF ERC for Wireless Integrated Micro. Systems (WIMS) 18

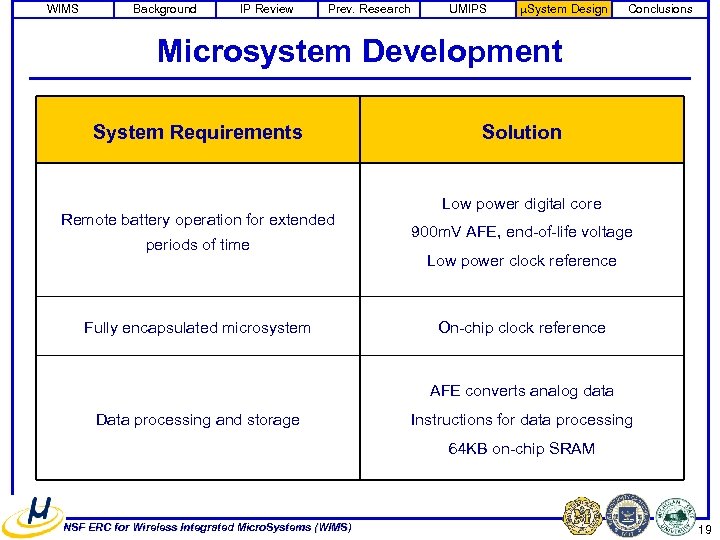

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Microsystem Development System Requirements Remote battery operation for extended periods of time Fully encapsulated microsystem Solution Low power digital core 900 m. V AFE, end-of-life voltage Low power clock reference On-chip clock reference AFE converts analog data Data processing and storage Instructions for data processing 64 KB on-chip SRAM NSF ERC for Wireless Integrated Micro. Systems (WIMS) 19

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Microsystem Development System Requirements Remote battery operation for extended periods of time Fully encapsulated microsystem Solution Low power digital core 900 m. V AFE, end-of-life voltage Low power clock reference On-chip clock reference AFE converts analog data Data processing and storage Instructions for data processing 64 KB on-chip SRAM NSF ERC for Wireless Integrated Micro. Systems (WIMS) 19

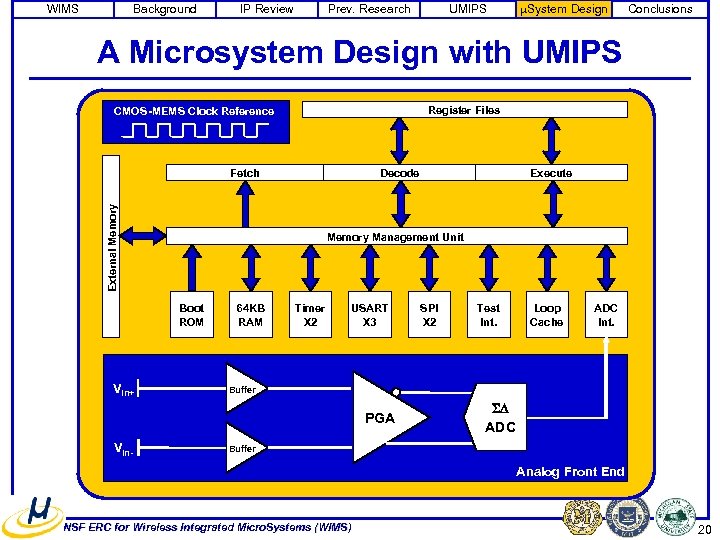

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions A Microsystem Design with UMIPS Register Files CMOS -MEMS Clock Reference Decode External Memory Fetch Memory Management Unit Boot ROM Vin+ 64 KB RAM Timer X 2 USART X 3 SPI X 2 Test Int. Loop Cache ADC Int. Buffer PGA Vin- Execute SD ADC Buffer Analog Front End NSF ERC for Wireless Integrated Micro. Systems (WIMS) 20

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions A Microsystem Design with UMIPS Register Files CMOS -MEMS Clock Reference Decode External Memory Fetch Memory Management Unit Boot ROM Vin+ 64 KB RAM Timer X 2 USART X 3 SPI X 2 Test Int. Loop Cache ADC Int. Buffer PGA Vin- Execute SD ADC Buffer Analog Front End NSF ERC for Wireless Integrated Micro. Systems (WIMS) 20

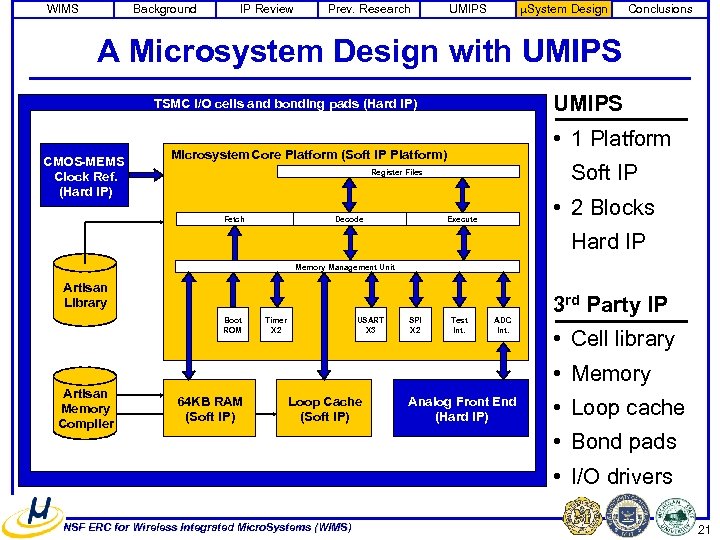

WIMS Background IP Review Prev. Research m. System Design UMIPS Conclusions A Microsystem Design with UMIPS TSMC I/O cells and bonding pads (Hard IP) CMOS-MEMS Clock Ref. (Hard IP) • 1 Platform Microsystem Core Platform (Soft IP Platform) Soft IP Register Files Fetch Decode • 2 Blocks Execute Hard IP Memory Management Unit Artisan Library Boot ROM Timer X 2 USART X 3 SPI X 2 Test Int. ADC Int. 3 rd Party IP • Cell library • Memory Artisan Memory Compiler 64 KB RAM (Soft IP) Loop Cache (Soft IP) Analog Front End (Hard IP) • Loop cache • Bond pads • I/O drivers NSF ERC for Wireless Integrated Micro. Systems (WIMS) 21

WIMS Background IP Review Prev. Research m. System Design UMIPS Conclusions A Microsystem Design with UMIPS TSMC I/O cells and bonding pads (Hard IP) CMOS-MEMS Clock Ref. (Hard IP) • 1 Platform Microsystem Core Platform (Soft IP Platform) Soft IP Register Files Fetch Decode • 2 Blocks Execute Hard IP Memory Management Unit Artisan Library Boot ROM Timer X 2 USART X 3 SPI X 2 Test Int. ADC Int. 3 rd Party IP • Cell library • Memory Artisan Memory Compiler 64 KB RAM (Soft IP) Loop Cache (Soft IP) Analog Front End (Hard IP) • Loop cache • Bond pads • I/O drivers NSF ERC for Wireless Integrated Micro. Systems (WIMS) 21

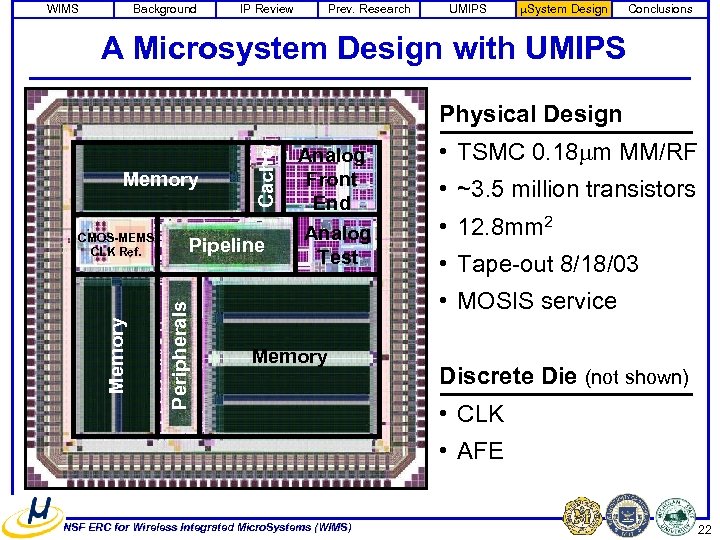

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions A Microsystem Design with UMIPS Memory Pipeline Peripherals Memory CMOS-MEMS CLK Ref. Cache Physical Design Analog Front End Analog Test • TSMC 0. 18 mm MM/RF • ~3. 5 million transistors • 12. 8 mm 2 • Tape-out 8/18/03 • MOSIS service Memory Discrete Die (not shown) • CLK • AFE NSF ERC for Wireless Integrated Micro. Systems (WIMS) 22

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions A Microsystem Design with UMIPS Memory Pipeline Peripherals Memory CMOS-MEMS CLK Ref. Cache Physical Design Analog Front End Analog Test • TSMC 0. 18 mm MM/RF • ~3. 5 million transistors • 12. 8 mm 2 • Tape-out 8/18/03 • MOSIS service Memory Discrete Die (not shown) • CLK • AFE NSF ERC for Wireless Integrated Micro. Systems (WIMS) 22

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Microsystem Current Status • Si Delivery 11/03 üBy TSMC through the MOSIS service üIntegrated microsystem and discrete die • Clock generator üFully functional as separate die üFully functional on microcontroller die • Analog front end üFully functional as separate die – Test in progress on microcontroller die • Microcontroller and peripherals üLogic fully functional – Peripherals in test NSF ERC for Wireless Integrated Micro. Systems (WIMS) 23

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Microsystem Current Status • Si Delivery 11/03 üBy TSMC through the MOSIS service üIntegrated microsystem and discrete die • Clock generator üFully functional as separate die üFully functional on microcontroller die • Analog front end üFully functional as separate die – Test in progress on microcontroller die • Microcontroller and peripherals üLogic fully functional – Peripherals in test NSF ERC for Wireless Integrated Micro. Systems (WIMS) 23

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions and Future Work • Clear need for IP design and reuse within the research community – Must support analog, RF, MEMS, etc. • Announcing launch of early-stage research IP repository: UMIPS – Already contains submissions from UMICH and other institutions • First IP-based design reported using UMIPS – Complete test results to be published shortly • IP-based design enhances quality of research – Disjoint projects combined to present more substantial work • Challenges still ahead – Sustainability – Automation – Security, piracy, etc. NSF ERC for Wireless Integrated Micro. Systems (WIMS) 24

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions and Future Work • Clear need for IP design and reuse within the research community – Must support analog, RF, MEMS, etc. • Announcing launch of early-stage research IP repository: UMIPS – Already contains submissions from UMICH and other institutions • First IP-based design reported using UMIPS – Complete test results to be published shortly • IP-based design enhances quality of research – Disjoint projects combined to present more substantial work • Challenges still ahead – Sustainability – Automation – Security, piracy, etc. NSF ERC for Wireless Integrated Micro. Systems (WIMS) 24

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Acknowledgment • Fabrication service – MOSIS, TSMC • IP providers – Artisan, TSMC • CAD tool providers – Synopsys, Cadence, Mentor, Coventor • Collaborators – Dr. Michael Flynn • Funding – NSF ERC for Wireless Integrated Micro. Systems (WIMS) 25

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Acknowledgment • Fabrication service – MOSIS, TSMC • IP providers – Artisan, TSMC • CAD tool providers – Synopsys, Cadence, Mentor, Coventor • Collaborators – Dr. Michael Flynn • Funding – NSF ERC for Wireless Integrated Micro. Systems (WIMS) 25

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Microsystem and So. C Design with UMIPS Questions? NSF ERC for Wireless Integrated Micro. Systems (WIMS) 26

WIMS Background IP Review Prev. Research UMIPS m. System Design Conclusions Microsystem and So. C Design with UMIPS Questions? NSF ERC for Wireless Integrated Micro. Systems (WIMS) 26