6087eb33a5aab017dcbc96f805350604.ppt

- Количество слайдов: 8

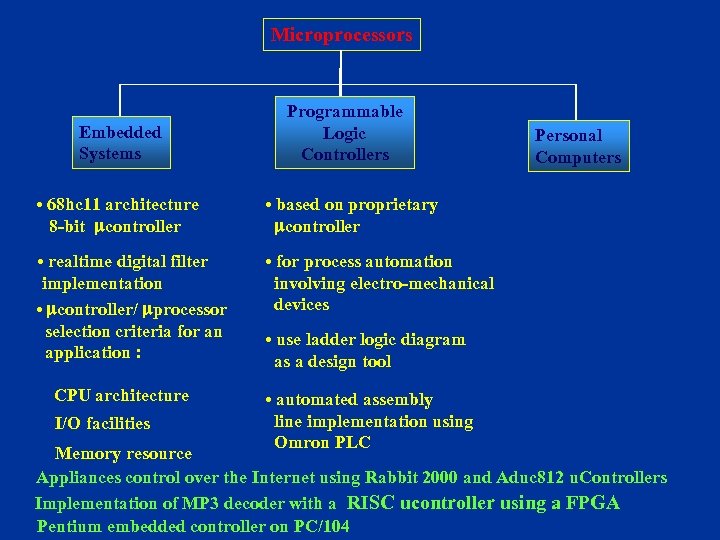

Microprocessors Embedded Systems Programmable Logic Controllers • 68 hc 11 architecture 8 -bit controller • based on proprietary controller • realtime digital filter implementation • controller/ processor selection criteria for an application : Personal Computers • for process automation involving electro-mechanical devices CPU architecture I/O facilities • use ladder logic diagram as a design tool • automated assembly line implementation using Omron PLC Memory resource Appliances control over the Internet using Rabbit 2000 and Aduc 812 u. Controllers Implementation of MP 3 decoder with a RISC ucontroller using a FPGA Pentium embedded controller on PC/104

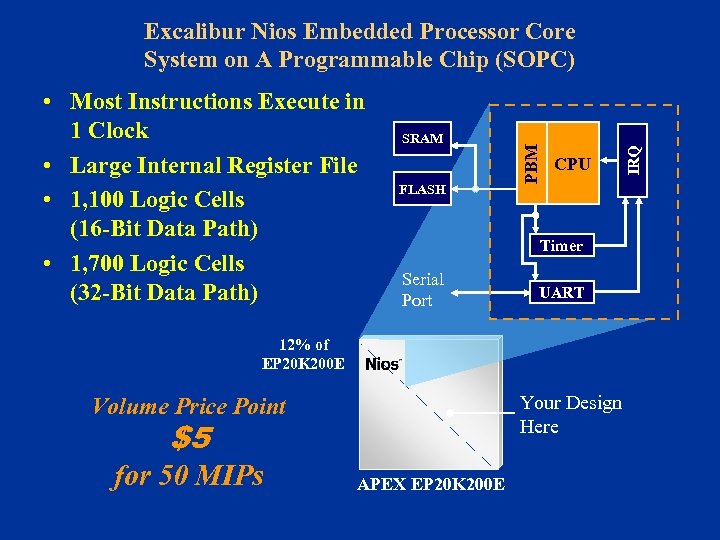

SRAM FLASH CPU Timer Serial Port UART 12% of EP 20 K 200 E Your Design Here Volume Price Point $5 for 50 MIPs APEX EP 20 K 200 E IRQ • Most Instructions Execute in 1 Clock • Large Internal Register File • 1, 100 Logic Cells (16 -Bit Data Path) • 1, 700 Logic Cells (32 -Bit Data Path) PBM Excalibur Nios Embedded Processor Core System on A Programmable Chip (SOPC)

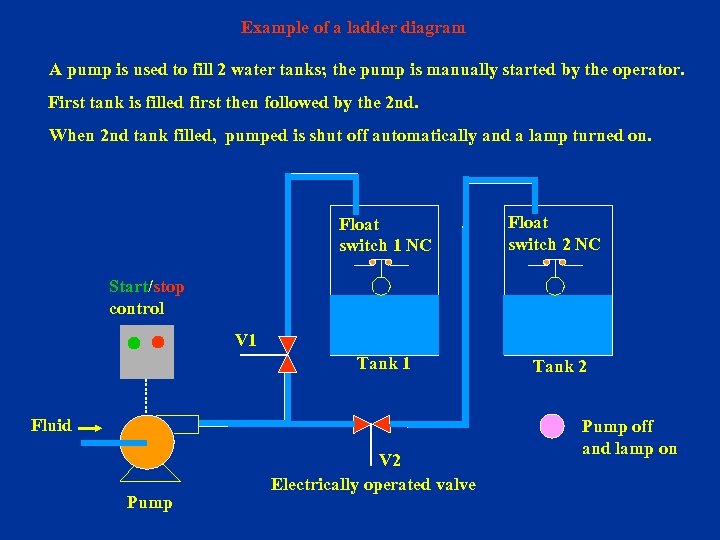

Example of a ladder diagram A pump is used to fill 2 water tanks; the pump is manually started by the operator. First tank is filled first then followed by the 2 nd. When 2 nd tank filled, pumped is shut off automatically and a lamp turned on. Float switch 1 NC Float switch 2 NC Tank 1 Tank 2 Start/stop control V 1 Fluid Pump V 2 Electrically operated valve Pump off and lamp on

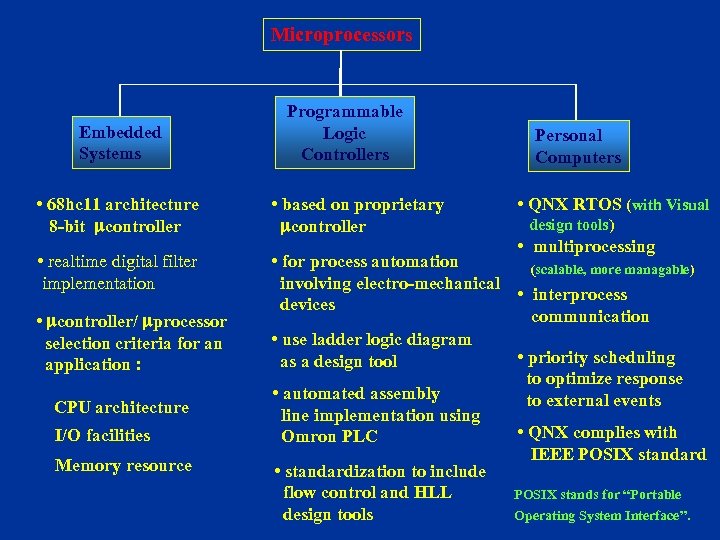

Microprocessors Embedded Systems • 68 hc 11 architecture 8 -bit controller • realtime digital filter implementation • controller/ processor selection criteria for an application : CPU architecture I/O facilities Memory resource Programmable Logic Controllers • based on proprietary controller Personal Computers • QNX RTOS (with Visual design tools) • multiprocessing • for process automation (scalable, more managable) involving electro-mechanical • interprocess devices communication • use ladder logic diagram • priority scheduling as a design tool to optimize response • automated assembly to external events line implementation using • QNX complies with Omron PLC IEEE POSIX standard • standardization to include flow control and HLL POSIX stands for “Portable design tools Operating System Interface”.

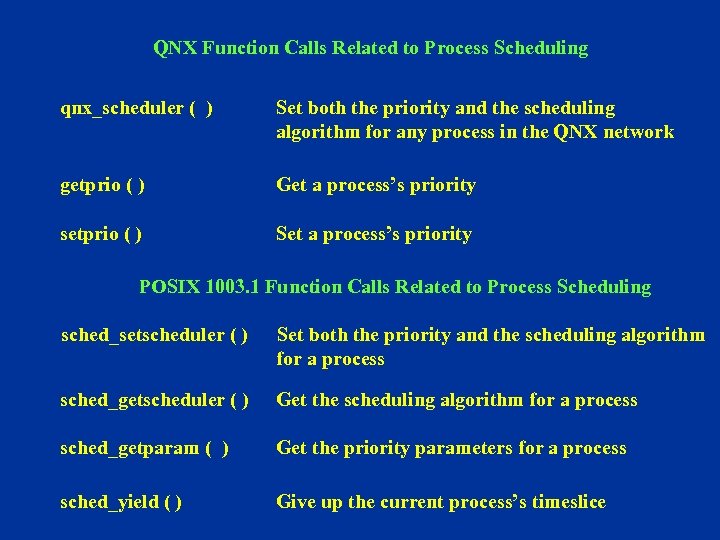

QNX Function Calls Related to Process Scheduling qnx_scheduler ( ) Set both the priority and the scheduling algorithm for any process in the QNX network getprio ( ) Get a process’s priority setprio ( ) Set a process’s priority POSIX 1003. 1 Function Calls Related to Process Scheduling sched_setscheduler ( ) Set both the priority and the scheduling algorithm for a process sched_getscheduler ( ) Get the scheduling algorithm for a process sched_getparam ( ) Get the priority parameters for a process sched_yield ( ) Give up the current process’s timeslice

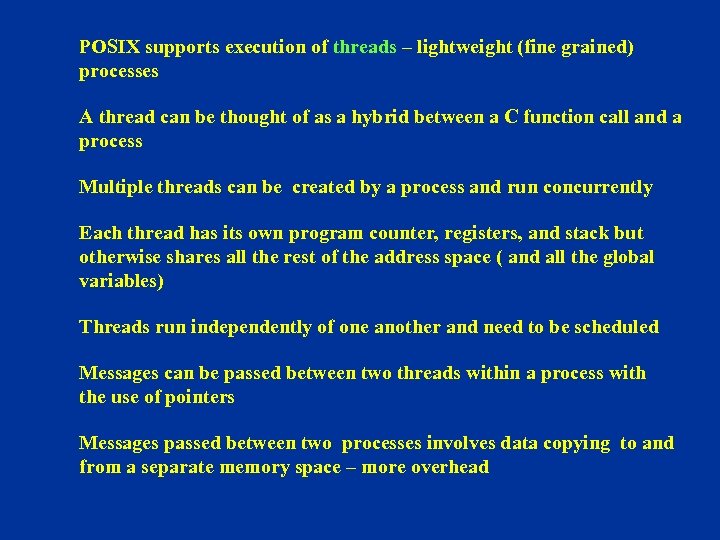

POSIX supports execution of threads – lightweight (fine grained) processes A thread can be thought of as a hybrid between a C function call and a process Multiple threads can be created by a process and run concurrently Each thread has its own program counter, registers, and stack but otherwise shares all the rest of the address space ( and all the global variables) Threads run independently of one another and need to be scheduled Messages can be passed between two threads within a process with the use of pointers Messages passed between two processes involves data copying to and from a separate memory space – more overhead

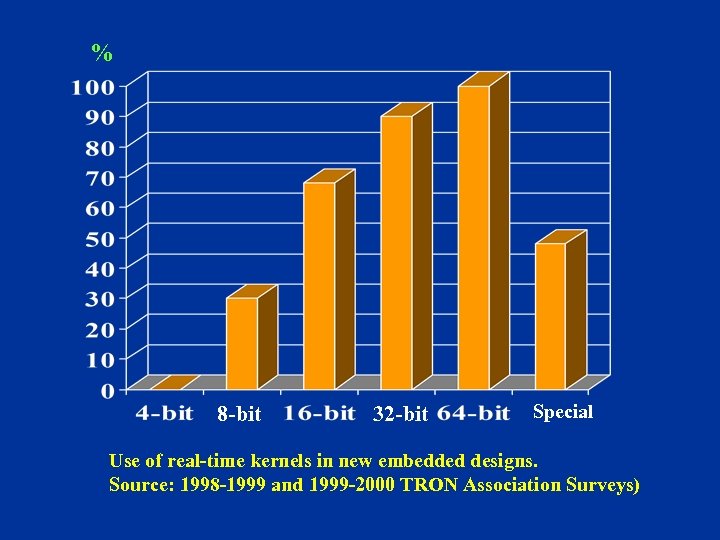

% 8 -bit 32 -bit Special Use of real-time kernels in new embedded designs. Source: 1998 -1999 and 1999 -2000 TRON Association Surveys)

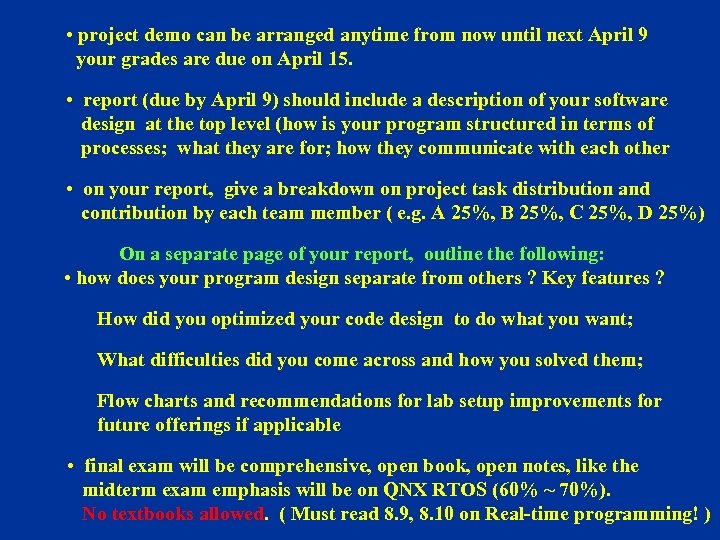

• project demo can be arranged anytime from now until next April 9 your grades are due on April 15. • report (due by April 9) should include a description of your software design at the top level (how is your program structured in terms of processes; what they are for; how they communicate with each other • on your report, give a breakdown on project task distribution and contribution by each team member ( e. g. A 25%, B 25%, C 25%, D 25%) On a separate page of your report, outline the following: • how does your program design separate from others ? Key features ? How did you optimized your code design to do what you want; What difficulties did you come across and how you solved them; Flow charts and recommendations for lab setup improvements for future offerings if applicable • final exam will be comprehensive, open book, open notes, like the midterm exam emphasis will be on QNX RTOS (60% ~ 70%). No textbooks allowed. ( Must read 8. 9, 8. 10 on Real-time programming! )

6087eb33a5aab017dcbc96f805350604.ppt