41051915f9d6e02728fc40ee8c8ca4a9.ppt

- Количество слайдов: 11

MGPA Linearity Non-linearity measurements in the lab hardware description method results Mark Raymond (Dec. 2004) 1

Linearity test bench 40 MHz clock and ADC trig. Digital Sequencer 10 ns trig. prog. delay (0 – 250 ns 1 ns steps) trig. AWG (AG 33250) programmable Cinj attenuator (HP 8494+HP 8495) 1 db steps MGPA level shift 14 -bit ADC (SIS 3301) Lab. View automated use prog. attenuator, rather than changing amp. of AWG O/P to avoid contribution from AWG O/P stage linearity AWG prog. attenuator prog. delay 14 -bit ADC -> negligible INL and DNL contribution to measurement for MGPA test board use either RAL PCB with socket easy chip exchange or VFE card verify performance in final configuration 14 -bit VME ADC MGPA test board 2

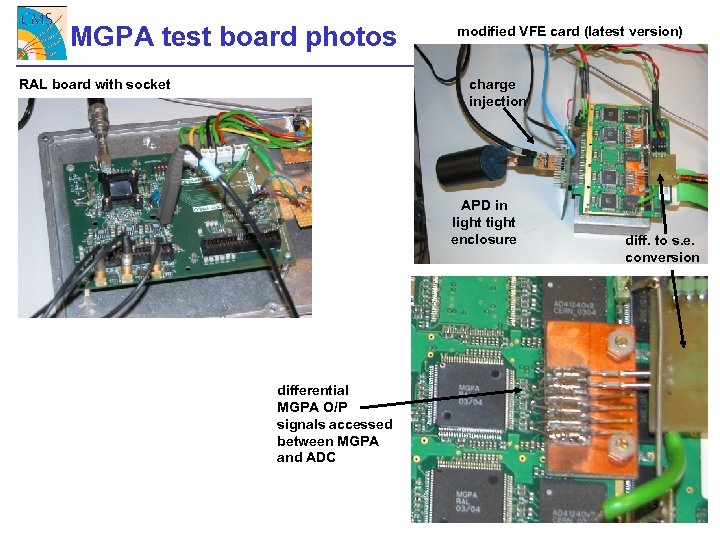

MGPA test board photos RAL board with socket modified VFE card (latest version) charge injection APD in light tight enclosure diff. to s. e. conversion differential MGPA O/P signals accessed between MGPA and ADC 3

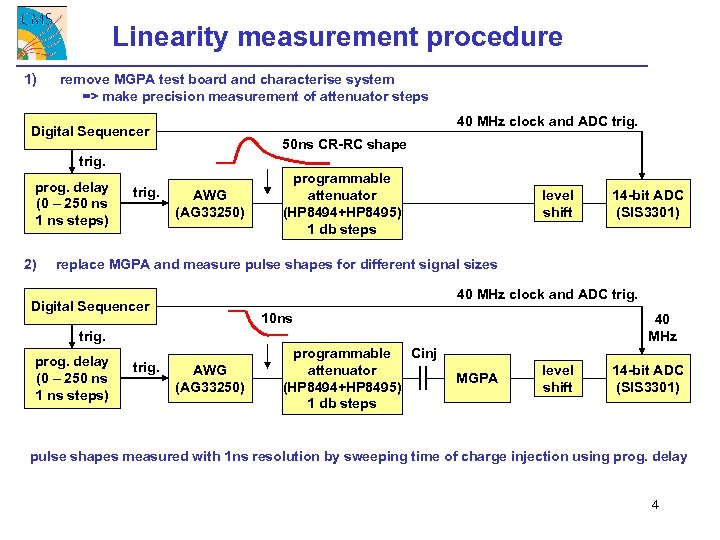

Linearity measurement procedure 1) remove MGPA test board and characterise system => make precision measurement of attenuator steps 40 MHz clock and ADC trig. Digital Sequencer 50 ns CR-RC shape trig. prog. delay (0 – 250 ns 1 ns steps) 2) trig. AWG (AG 33250) programmable attenuator (HP 8494+HP 8495) 1 db steps level shift 14 -bit ADC (SIS 3301) replace MGPA and measure pulse shapes for different signal sizes 40 MHz clock and ADC trig. Digital Sequencer 10 ns 40 MHz trig. prog. delay (0 – 250 ns 1 ns steps) trig. AWG (AG 33250) programmable Cinj attenuator (HP 8494+HP 8495) 1 db steps MGPA level shift 14 -bit ADC (SIS 3301) pulse shapes measured with 1 ns resolution by sweeping time of charge injection using prog. delay 4

Typical non-linearity measurement (1) high gain channel (VFE card) 180 p. F Cin added fullscale signal = 5. 8 p. C signal sizes not linearly spaced because of logarithmic attenuator steps ADC range 5. 8 p. C subtract pedestals 5

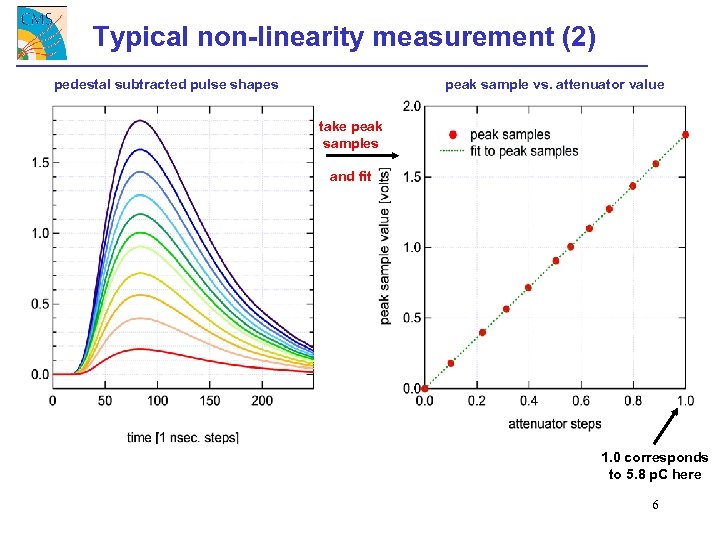

Typical non-linearity measurement (2) pedestal subtracted pulse shapes peak sample vs. attenuator value take peak samples and fit 1. 0 corresponds to 5. 8 p. C here 6

![Typical non-linearity measurement (3) finally calculate linearity Non-linearity [% fullscale] = peak pulse ht. Typical non-linearity measurement (3) finally calculate linearity Non-linearity [% fullscale] = peak pulse ht.](https://present5.com/presentation/41051915f9d6e02728fc40ee8c8ca4a9/image-7.jpg)

Typical non-linearity measurement (3) finally calculate linearity Non-linearity [% fullscale] = peak pulse ht. – fit (to pk pulse ht) x 100 fullscale signal (1. 8 V) 7

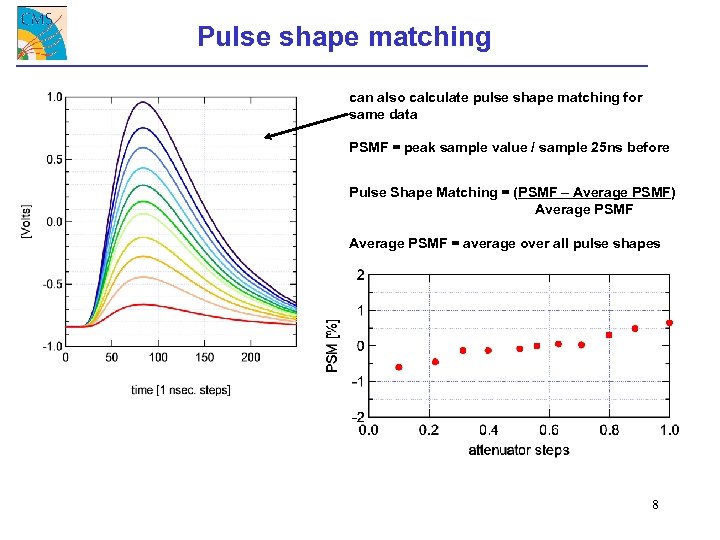

Pulse shape matching can also calculate pulse shape matching for same data PSMF = peak sample value / sample 25 ns before Pulse Shape Matching = (PSMF – Average PSMF) Average PSMF = average over all pulse shapes 8

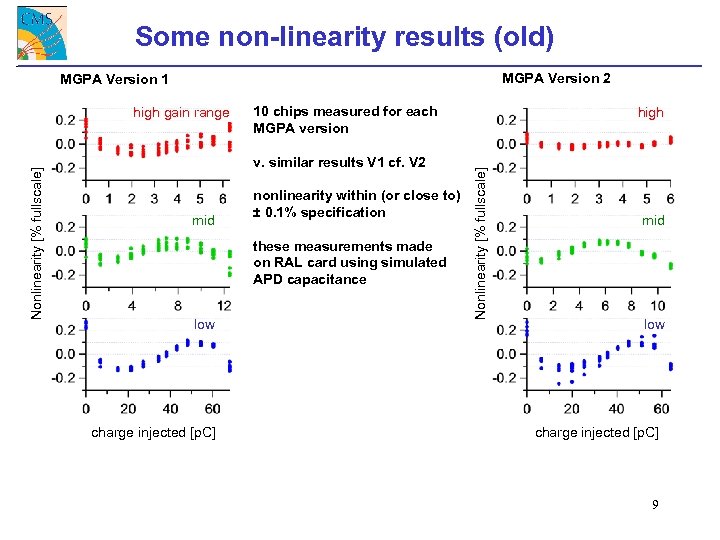

Some non-linearity results (old) MGPA Version 2 MGPA Version 1 10 chips measured for each MGPA version v. similar results V 1 cf. V 2 mid nonlinearity within (or close to) ± 0. 1% specification these measurements made on RAL card using simulated APD capacitance low charge injected [p. C] high Nonlinearity [% fullscale] high gain range mid low charge injected [p. C] 9

New results Hi gain channel non-linearity measured on VFE card Why is non-linearity worse in H 4 beam? (noticeable fall-off for small signals on high gain channel) Could there be an APD effect? No – no significant difference between 180 p. F and APD biased at 350 V Could signal risetime be shorter than expected? No - changing charge injection 10 ns -> 5 ns doesn’t make much difference (at least for high gain channel) 10

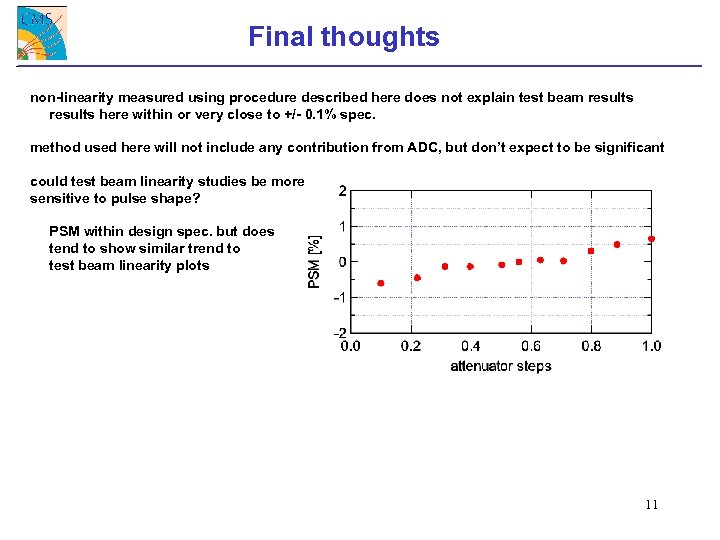

Final thoughts non-linearity measured using procedure described here does not explain test beam results here within or very close to +/- 0. 1% spec. method used here will not include any contribution from ADC, but don’t expect to be significant could test beam linearity studies be more sensitive to pulse shape? PSM within design spec. but does tend to show similar trend to test beam linearity plots 11

41051915f9d6e02728fc40ee8c8ca4a9.ppt