c691f2807b63be89283d92e728a1436e.ppt

- Количество слайдов: 42

Methods to Differentiate Mil/Aero Solutions Using FPGAs Dan Gardner Final MAPLD Presentation

Methods to Differentiate Mil/Aero Solutions Using FPGAs Dan Gardner Final MAPLD Presentation

Agenda n n n Why FPGA technology is important Technology to consider for FPGA EDA software Why you need these for Mil/Aero FPGA Gardner 2 MAPLD 2005/P 145

Agenda n n n Why FPGA technology is important Technology to consider for FPGA EDA software Why you need these for Mil/Aero FPGA Gardner 2 MAPLD 2005/P 145

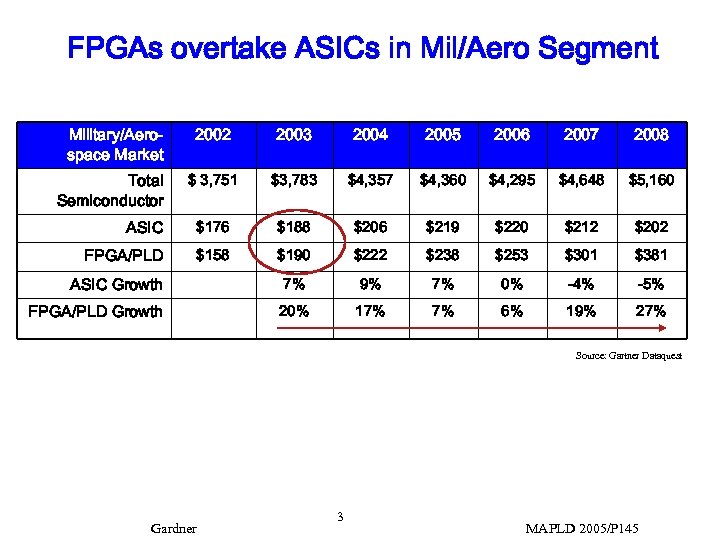

FPGAs overtake ASICs in Mil/Aero Segment Military/Aerospace Market 2002 2003 2004 2005 2006 2007 2008 $ 3, 751 $3, 783 $4, 357 $4, 360 $4, 295 $4, 648 $5, 160 ASIC $176 $188 $206 $219 $220 $212 $202 FPGA/PLD $158 $190 $222 $238 $253 $301 $381 ASIC Growth 7% 9% 7% 0% -4% -5% FPGA/PLD Growth 20% 17% 7% 6% 19% 27% Total Semiconductor Source: Gartner Dataquest Gardner 3 MAPLD 2005/P 145

FPGAs overtake ASICs in Mil/Aero Segment Military/Aerospace Market 2002 2003 2004 2005 2006 2007 2008 $ 3, 751 $3, 783 $4, 357 $4, 360 $4, 295 $4, 648 $5, 160 ASIC $176 $188 $206 $219 $220 $212 $202 FPGA/PLD $158 $190 $222 $238 $253 $301 $381 ASIC Growth 7% 9% 7% 0% -4% -5% FPGA/PLD Growth 20% 17% 7% 6% 19% 27% Total Semiconductor Source: Gartner Dataquest Gardner 3 MAPLD 2005/P 145

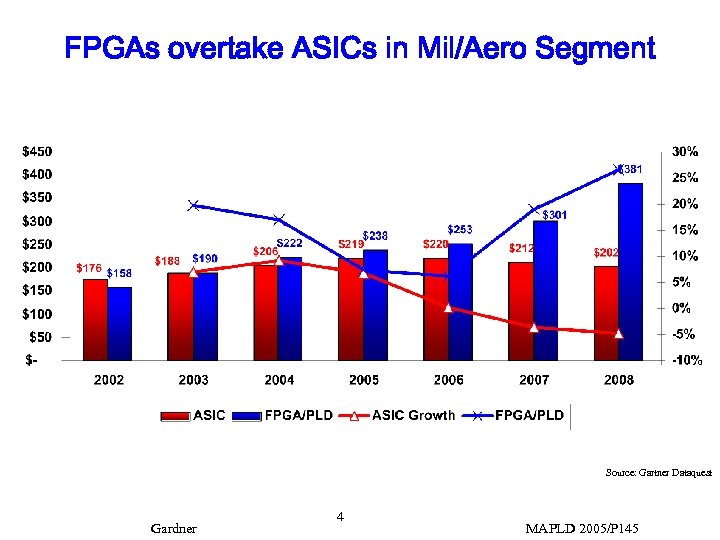

FPGAs overtake ASICs in Mil/Aero Segment Source: Gartner Dataquest Gardner 4 MAPLD 2005/P 145

FPGAs overtake ASICs in Mil/Aero Segment Source: Gartner Dataquest Gardner 4 MAPLD 2005/P 145

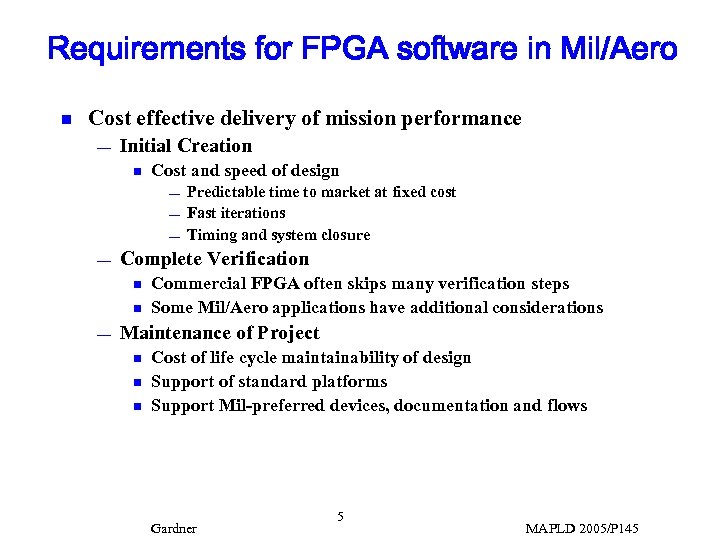

Requirements for FPGA software in Mil/Aero n Cost effective delivery of mission performance — Initial Creation n Cost and speed of design — — Complete Verification n n — Predictable time to market at fixed cost Fast iterations Timing and system closure Commercial FPGA often skips many verification steps Some Mil/Aero applications have additional considerations Maintenance of Project n n n Cost of life cycle maintainability of design Support of standard platforms Support Mil-preferred devices, documentation and flows Gardner 5 MAPLD 2005/P 145

Requirements for FPGA software in Mil/Aero n Cost effective delivery of mission performance — Initial Creation n Cost and speed of design — — Complete Verification n n — Predictable time to market at fixed cost Fast iterations Timing and system closure Commercial FPGA often skips many verification steps Some Mil/Aero applications have additional considerations Maintenance of Project n n n Cost of life cycle maintainability of design Support of standard platforms Support Mil-preferred devices, documentation and flows Gardner 5 MAPLD 2005/P 145

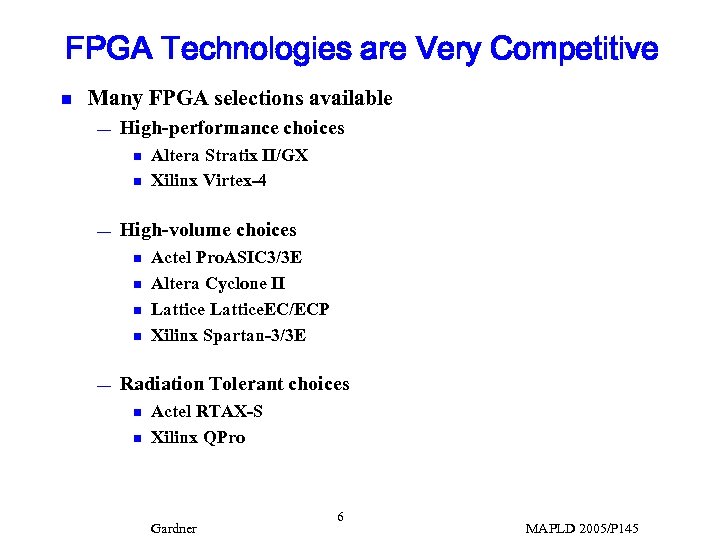

FPGA Technologies are Very Competitive n Many FPGA selections available — High-performance choices n n — High-volume choices n n — Altera Stratix II/GX Xilinx Virtex-4 Actel Pro. ASIC 3/3 E Altera Cyclone II Lattice. EC/ECP Xilinx Spartan-3/3 E Radiation Tolerant choices n n Actel RTAX-S Xilinx QPro Gardner 6 MAPLD 2005/P 145

FPGA Technologies are Very Competitive n Many FPGA selections available — High-performance choices n n — High-volume choices n n — Altera Stratix II/GX Xilinx Virtex-4 Actel Pro. ASIC 3/3 E Altera Cyclone II Lattice. EC/ECP Xilinx Spartan-3/3 E Radiation Tolerant choices n n Actel RTAX-S Xilinx QPro Gardner 6 MAPLD 2005/P 145

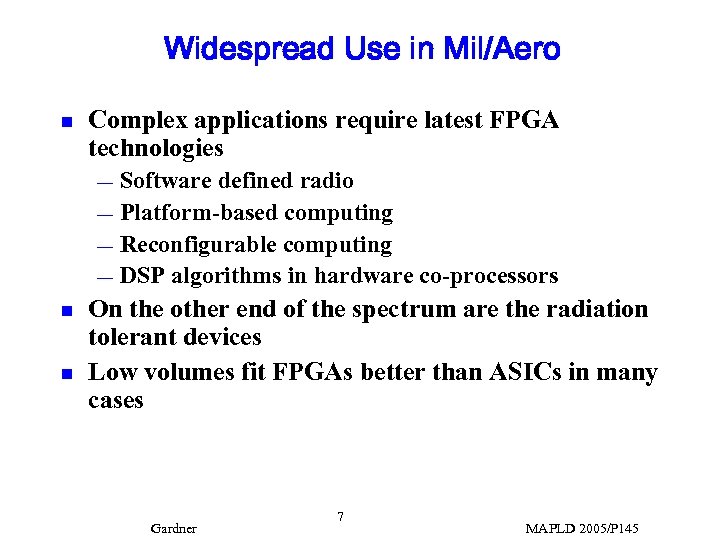

Widespread Use in Mil/Aero n Complex applications require latest FPGA technologies Software defined radio — Platform-based computing — Reconfigurable computing — DSP algorithms in hardware co-processors — n n On the other end of the spectrum are the radiation tolerant devices Low volumes fit FPGAs better than ASICs in many cases Gardner 7 MAPLD 2005/P 145

Widespread Use in Mil/Aero n Complex applications require latest FPGA technologies Software defined radio — Platform-based computing — Reconfigurable computing — DSP algorithms in hardware co-processors — n n On the other end of the spectrum are the radiation tolerant devices Low volumes fit FPGAs better than ASICs in many cases Gardner 7 MAPLD 2005/P 145

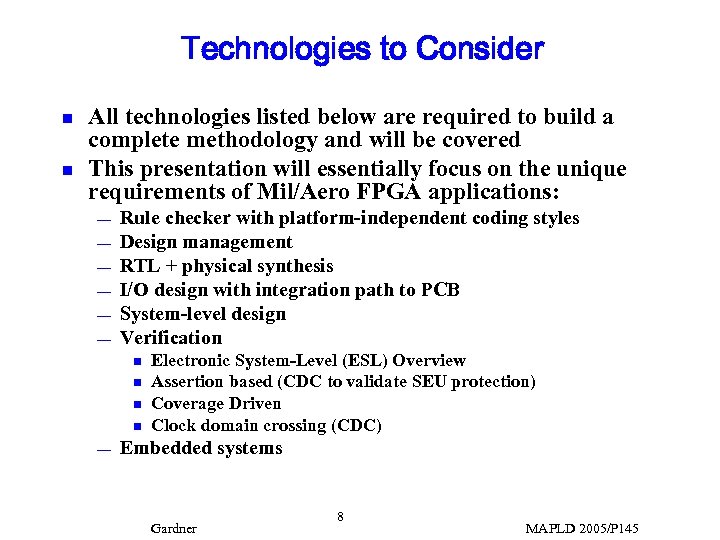

Technologies to Consider n n All technologies listed below are required to build a complete methodology and will be covered This presentation will essentially focus on the unique requirements of Mil/Aero FPGA applications: — — — Rule checker with platform-independent coding styles Design management RTL + physical synthesis I/O design with integration path to PCB System-level design Verification n n — Electronic System-Level (ESL) Overview Assertion based (CDC to validate SEU protection) Coverage Driven Clock domain crossing (CDC) Embedded systems Gardner 8 MAPLD 2005/P 145

Technologies to Consider n n All technologies listed below are required to build a complete methodology and will be covered This presentation will essentially focus on the unique requirements of Mil/Aero FPGA applications: — — — Rule checker with platform-independent coding styles Design management RTL + physical synthesis I/O design with integration path to PCB System-level design Verification n n — Electronic System-Level (ESL) Overview Assertion based (CDC to validate SEU protection) Coverage Driven Clock domain crossing (CDC) Embedded systems Gardner 8 MAPLD 2005/P 145

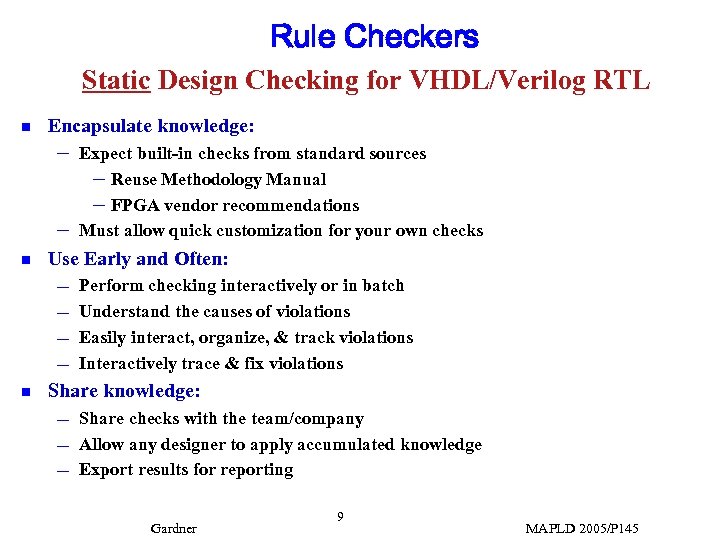

Rule Checkers Static Design Checking for VHDL/Verilog RTL n Encapsulate knowledge: – – n Use Early and Often: — — n Expect built-in checks from standard sources – Reuse Methodology Manual – FPGA vendor recommendations Must allow quick customization for your own checks Perform checking interactively or in batch Understand the causes of violations Easily interact, organize, & track violations Interactively trace & fix violations Share knowledge: — — — Share checks with the team/company Allow any designer to apply accumulated knowledge Export results for reporting Gardner 9 MAPLD 2005/P 145

Rule Checkers Static Design Checking for VHDL/Verilog RTL n Encapsulate knowledge: – – n Use Early and Often: — — n Expect built-in checks from standard sources – Reuse Methodology Manual – FPGA vendor recommendations Must allow quick customization for your own checks Perform checking interactively or in batch Understand the causes of violations Easily interact, organize, & track violations Interactively trace & fix violations Share knowledge: — — — Share checks with the team/company Allow any designer to apply accumulated knowledge Export results for reporting Gardner 9 MAPLD 2005/P 145

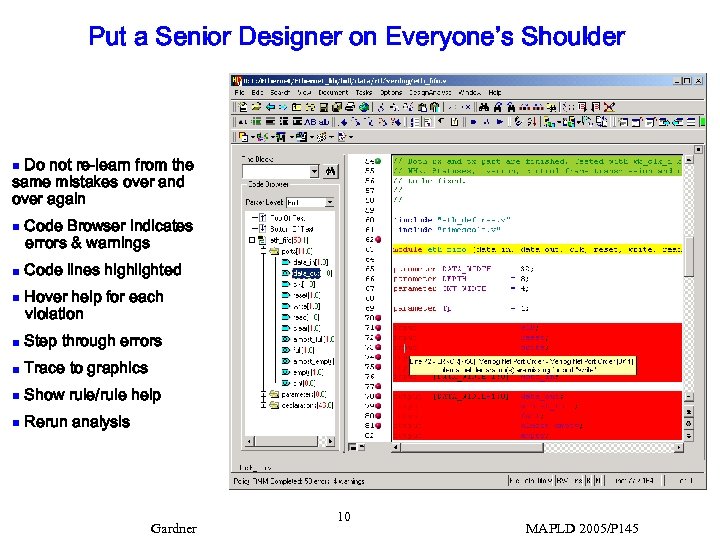

Put a Senior Designer on Everyone’s Shoulder Do not re-learn from the same mistakes over and over again n n Code Browser indicates errors & warnings Code lines highlighted Hover help for each violation n Step through errors n Trace to graphics n Show rule/rule help n Rerun analysis Gardner 10 MAPLD 2005/P 145

Put a Senior Designer on Everyone’s Shoulder Do not re-learn from the same mistakes over and over again n n Code Browser indicates errors & warnings Code lines highlighted Hover help for each violation n Step through errors n Trace to graphics n Show rule/rule help n Rerun analysis Gardner 10 MAPLD 2005/P 145

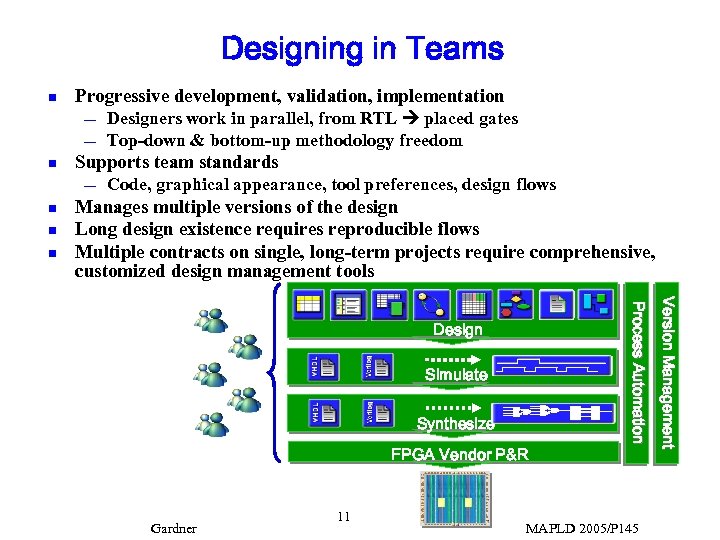

Designing in Teams n Progressive development, validation, implementation — — n Supports team standards — n n n Designers work in parallel, from RTL placed gates Top-down & bottom-up methodology freedom Code, graphical appearance, tool preferences, design flows Manages multiple versions of the design Long design existence requires reproducible flows Multiple contracts on single, long-term projects require comprehensive, customized design management tools Synthesize FPGA Vendor P&R Gardner 11 MAPLD 2005/P 145 Version Management Simulate Process Automation Design

Designing in Teams n Progressive development, validation, implementation — — n Supports team standards — n n n Designers work in parallel, from RTL placed gates Top-down & bottom-up methodology freedom Code, graphical appearance, tool preferences, design flows Manages multiple versions of the design Long design existence requires reproducible flows Multiple contracts on single, long-term projects require comprehensive, customized design management tools Synthesize FPGA Vendor P&R Gardner 11 MAPLD 2005/P 145 Version Management Simulate Process Automation Design

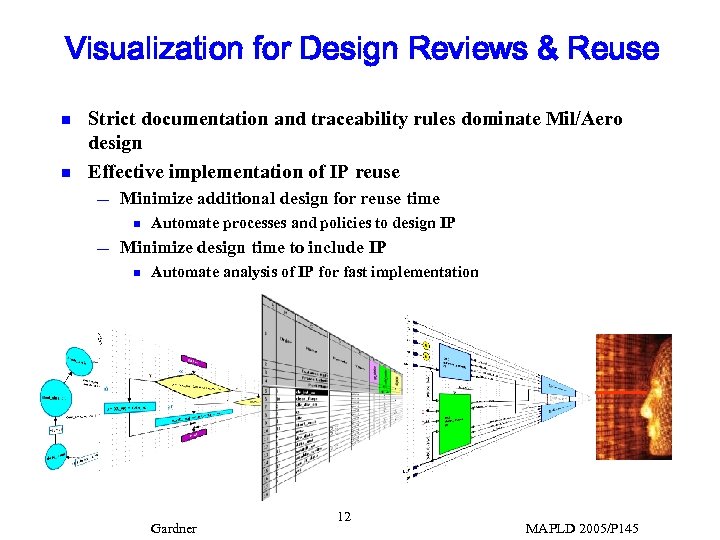

Visualization for Design Reviews & Reuse n n Strict documentation and traceability rules dominate Mil/Aero design Effective implementation of IP reuse — Minimize additional design for reuse time n — Automate processes and policies to design IP Minimize design time to include IP n Automate analysis of IP for fast implementation Gardner 12 MAPLD 2005/P 145

Visualization for Design Reviews & Reuse n n Strict documentation and traceability rules dominate Mil/Aero design Effective implementation of IP reuse — Minimize additional design for reuse time n — Automate processes and policies to design IP Minimize design time to include IP n Automate analysis of IP for fast implementation Gardner 12 MAPLD 2005/P 145

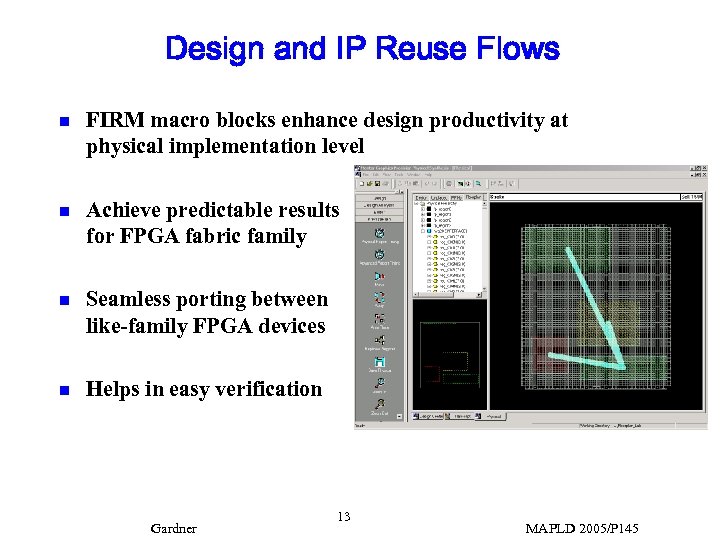

Design and IP Reuse Flows n FIRM macro blocks enhance design productivity at physical implementation level n Achieve predictable results for FPGA fabric family n Seamless porting between like-family FPGA devices n Helps in easy verification Gardner 13 MAPLD 2005/P 145

Design and IP Reuse Flows n FIRM macro blocks enhance design productivity at physical implementation level n Achieve predictable results for FPGA fabric family n Seamless porting between like-family FPGA devices n Helps in easy verification Gardner 13 MAPLD 2005/P 145

Platform FPGA Technology vs. Pushbutton FPGA Design Flow n Major technology changes in platform FPGA — — Specialized embedded technology — Specialized interconnect — n More gates per part High-speed device effects Emerging design challenges — Design debug process is unreliable for complex designs — Harder to bring quality product to market quickly — Harder to manage flows: n — Design reuse & IP integration Harder to predict development costs Gardner 14 MAPLD 2005/P 145

Platform FPGA Technology vs. Pushbutton FPGA Design Flow n Major technology changes in platform FPGA — — Specialized embedded technology — Specialized interconnect — n More gates per part High-speed device effects Emerging design challenges — Design debug process is unreliable for complex designs — Harder to bring quality product to market quickly — Harder to manage flows: n — Design reuse & IP integration Harder to predict development costs Gardner 14 MAPLD 2005/P 145

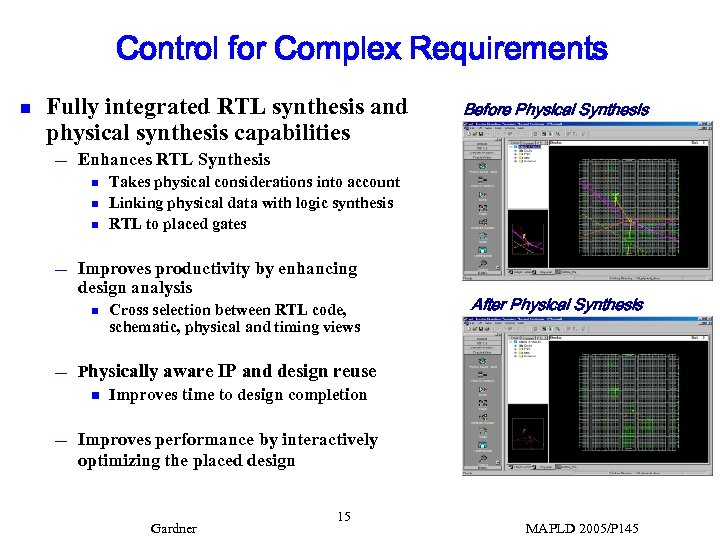

Control for Complex Requirements n Fully integrated RTL synthesis and physical synthesis capabilities — Enhances RTL Synthesis n n n — — Takes physical considerations into account Linking physical data with logic synthesis RTL to placed gates Improves productivity by enhancing design analysis n — Before Physical Synthesis Cross selection between RTL code, schematic, physical and timing views After Physical Synthesis Physically aware IP and design reuse n Improves time to design completion Improves performance by interactively optimizing the placed design Gardner 15 MAPLD 2005/P 145

Control for Complex Requirements n Fully integrated RTL synthesis and physical synthesis capabilities — Enhances RTL Synthesis n n n — — Takes physical considerations into account Linking physical data with logic synthesis RTL to placed gates Improves productivity by enhancing design analysis n — Before Physical Synthesis Cross selection between RTL code, schematic, physical and timing views After Physical Synthesis Physically aware IP and design reuse n Improves time to design completion Improves performance by interactively optimizing the placed design Gardner 15 MAPLD 2005/P 145

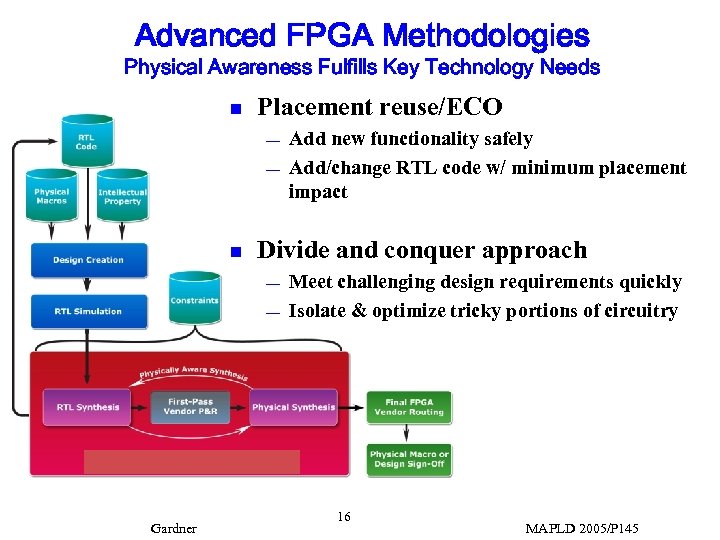

Advanced FPGA Methodologies Physical Awareness Fulfills Key Technology Needs n Placement reuse/ECO — — n Divide and conquer approach — — Gardner Add new functionality safely Add/change RTL code w/ minimum placement impact Meet challenging design requirements quickly Isolate & optimize tricky portions of circuitry 16 MAPLD 2005/P 145

Advanced FPGA Methodologies Physical Awareness Fulfills Key Technology Needs n Placement reuse/ECO — — n Divide and conquer approach — — Gardner Add new functionality safely Add/change RTL code w/ minimum placement impact Meet challenging design requirements quickly Isolate & optimize tricky portions of circuitry 16 MAPLD 2005/P 145

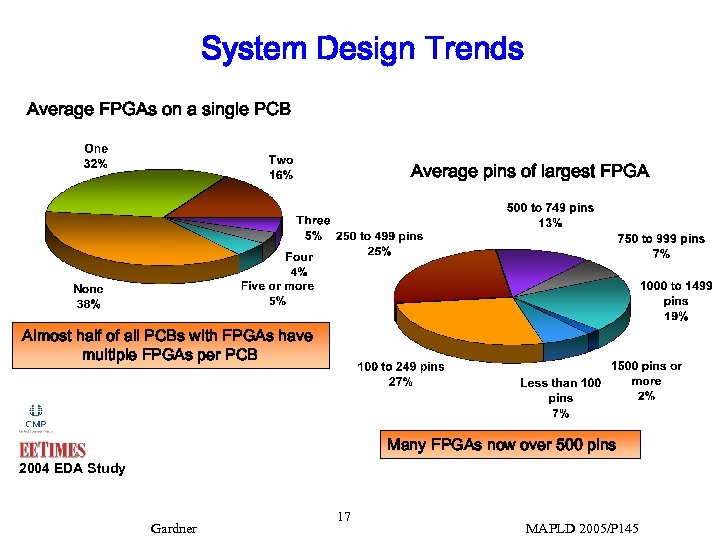

System Design Trends Average FPGAs on a single PCB Average pins of largest FPGA Almost half of all PCBs with FPGAs have multiple FPGAs per PCB Many FPGAs now over 500 pins 2004 EDA Study Gardner 17 MAPLD 2005/P 145

System Design Trends Average FPGAs on a single PCB Average pins of largest FPGA Almost half of all PCBs with FPGAs have multiple FPGAs per PCB Many FPGAs now over 500 pins 2004 EDA Study Gardner 17 MAPLD 2005/P 145

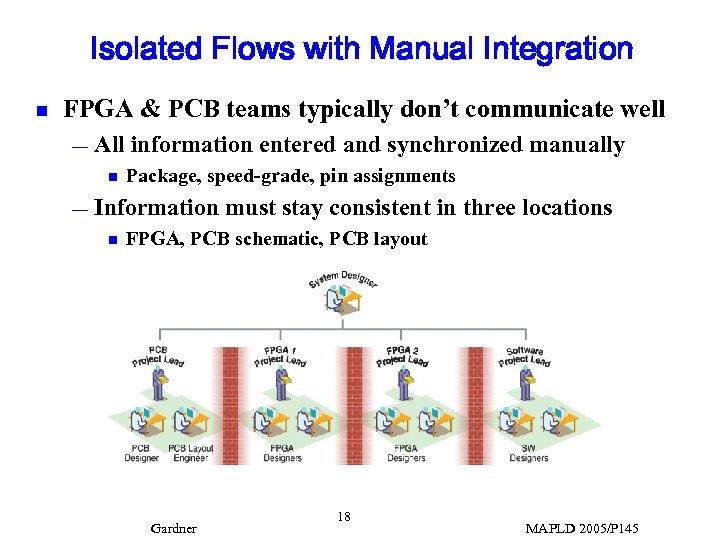

Isolated Flows with Manual Integration n FPGA & PCB teams typically don’t communicate well — All information entered and synchronized manually n — Package, speed-grade, pin assignments Information must stay consistent in three locations n FPGA, PCB schematic, PCB layout Gardner 18 MAPLD 2005/P 145

Isolated Flows with Manual Integration n FPGA & PCB teams typically don’t communicate well — All information entered and synchronized manually n — Package, speed-grade, pin assignments Information must stay consistent in three locations n FPGA, PCB schematic, PCB layout Gardner 18 MAPLD 2005/P 145

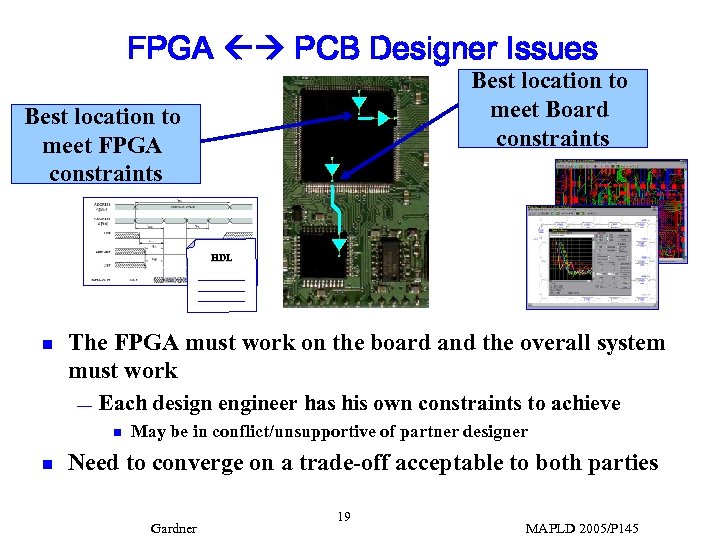

FPGA PCB Designer Issues Best location to meet Board constraints Best location to meet FPGA constraints HDL n The FPGA must work on the board and the overall system must work — Each design engineer has his own constraints to achieve n n May be in conflict/unsupportive of partner designer Need to converge on a trade-off acceptable to both parties Gardner 19 MAPLD 2005/P 145

FPGA PCB Designer Issues Best location to meet Board constraints Best location to meet FPGA constraints HDL n The FPGA must work on the board and the overall system must work — Each design engineer has his own constraints to achieve n n May be in conflict/unsupportive of partner designer Need to converge on a trade-off acceptable to both parties Gardner 19 MAPLD 2005/P 145

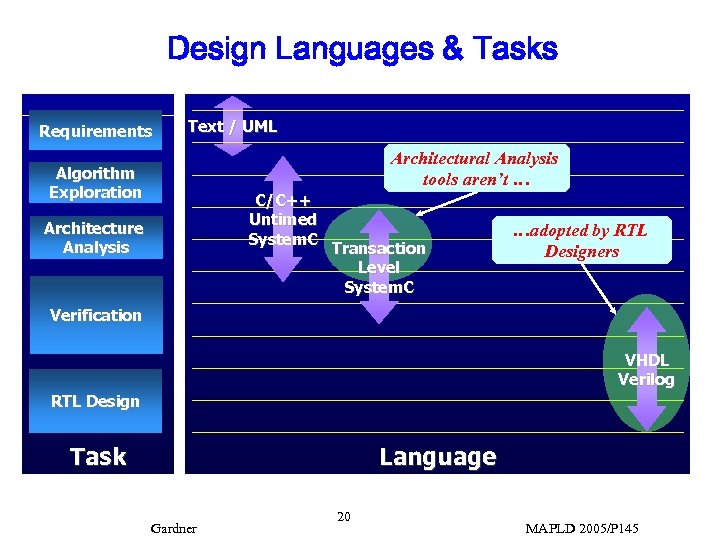

Design Languages & Tasks Requirements Text / UML Architectural Analysis tools aren’t … Algorithm Exploration C/C++ Untimed System. C Architecture Analysis Transaction Level System. C …adopted by RTL Designers Verification VHDL Verilog RTL Design Task Language Gardner 20 MAPLD 2005/P 145

Design Languages & Tasks Requirements Text / UML Architectural Analysis tools aren’t … Algorithm Exploration C/C++ Untimed System. C Architecture Analysis Transaction Level System. C …adopted by RTL Designers Verification VHDL Verilog RTL Design Task Language Gardner 20 MAPLD 2005/P 145

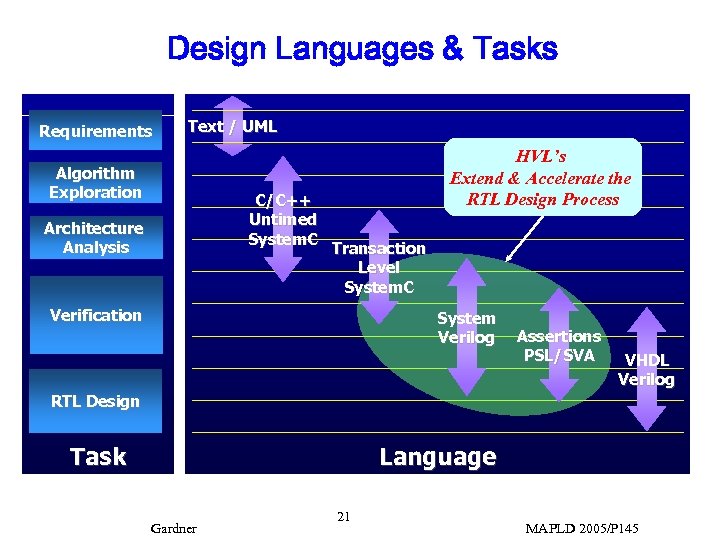

Design Languages & Tasks Requirements Text / UML Algorithm Exploration C/C++ Untimed System. C Architecture Analysis HVL’s Extend & Accelerate the RTL Design Process Transaction Level System. C Verification System Verilog Assertions PSL/SVA VHDL Verilog RTL Design Task Language Gardner 21 MAPLD 2005/P 145

Design Languages & Tasks Requirements Text / UML Algorithm Exploration C/C++ Untimed System. C Architecture Analysis HVL’s Extend & Accelerate the RTL Design Process Transaction Level System. C Verification System Verilog Assertions PSL/SVA VHDL Verilog RTL Design Task Language Gardner 21 MAPLD 2005/P 145

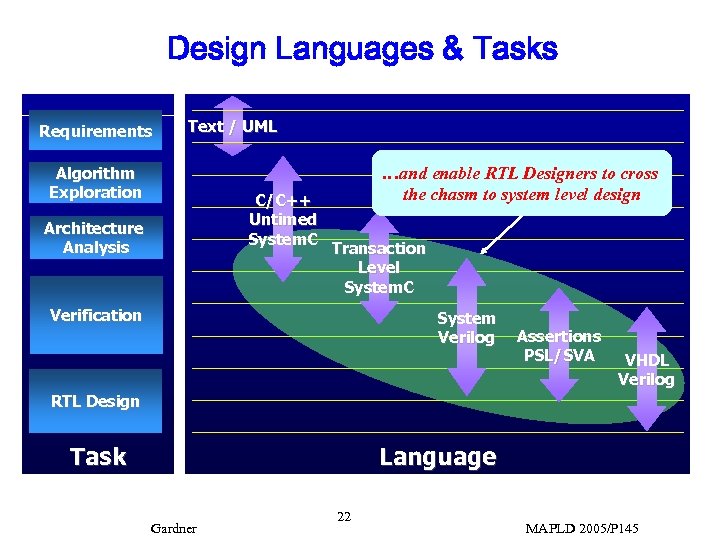

Design Languages & Tasks Requirements Text / UML Algorithm Exploration C/C++ Untimed System. C Architecture Analysis …and enable RTL Designers to cross the chasm to system level design Transaction Level System. C Verification System Verilog Assertions PSL/SVA VHDL Verilog RTL Design Task Language Gardner 22 MAPLD 2005/P 145

Design Languages & Tasks Requirements Text / UML Algorithm Exploration C/C++ Untimed System. C Architecture Analysis …and enable RTL Designers to cross the chasm to system level design Transaction Level System. C Verification System Verilog Assertions PSL/SVA VHDL Verilog RTL Design Task Language Gardner 22 MAPLD 2005/P 145

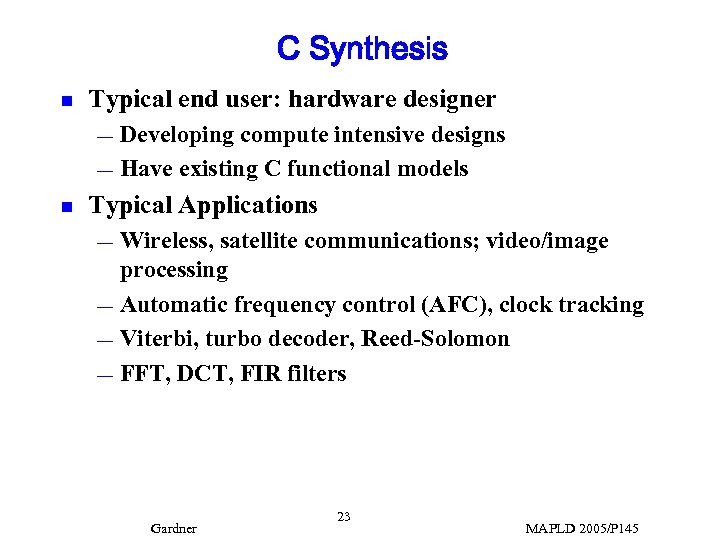

C Synthesis n Typical end user: hardware designer Developing compute intensive designs — Have existing C functional models — n Typical Applications Wireless, satellite communications; video/image processing — Automatic frequency control (AFC), clock tracking — Viterbi, turbo decoder, Reed-Solomon — FFT, DCT, FIR filters — Gardner 23 MAPLD 2005/P 145

C Synthesis n Typical end user: hardware designer Developing compute intensive designs — Have existing C functional models — n Typical Applications Wireless, satellite communications; video/image processing — Automatic frequency control (AFC), clock tracking — Viterbi, turbo decoder, Reed-Solomon — FFT, DCT, FIR filters — Gardner 23 MAPLD 2005/P 145

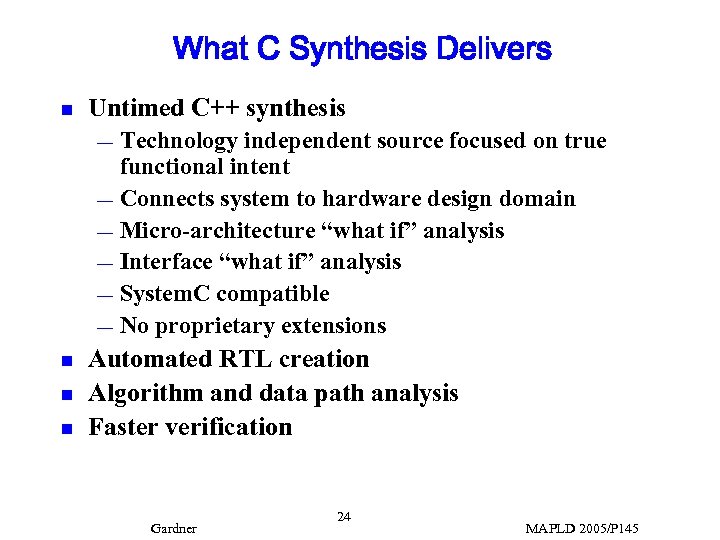

What C Synthesis Delivers n Untimed C++ synthesis Technology independent source focused on true functional intent — Connects system to hardware design domain — Micro-architecture “what if” analysis — Interface “what if” analysis — System. C compatible — No proprietary extensions — n n n Automated RTL creation Algorithm and data path analysis Faster verification Gardner 24 MAPLD 2005/P 145

What C Synthesis Delivers n Untimed C++ synthesis Technology independent source focused on true functional intent — Connects system to hardware design domain — Micro-architecture “what if” analysis — Interface “what if” analysis — System. C compatible — No proprietary extensions — n n n Automated RTL creation Algorithm and data path analysis Faster verification Gardner 24 MAPLD 2005/P 145

Why System. Verilog for Design? n n n Encapsulation allows designers to model at more abstract levels Scalability makes incremental design changes simpler Code re-usability increases design efficiency Easier to model accurate, synthesizable models of any size designs Not only system-level designers need System. Verilog Both Synthesis and Simulation benefit from System. Verilog Gardner 25 MAPLD 2005/P 145

Why System. Verilog for Design? n n n Encapsulation allows designers to model at more abstract levels Scalability makes incremental design changes simpler Code re-usability increases design efficiency Easier to model accurate, synthesizable models of any size designs Not only system-level designers need System. Verilog Both Synthesis and Simulation benefit from System. Verilog Gardner 25 MAPLD 2005/P 145

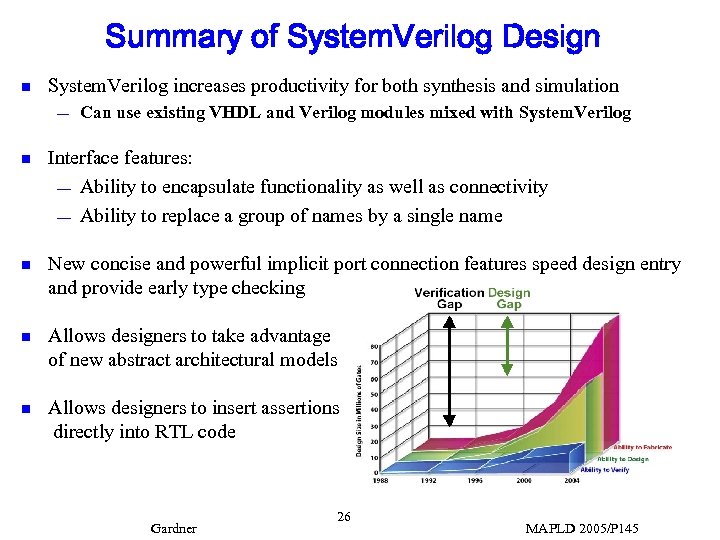

Summary of System. Verilog Design n System. Verilog increases productivity for both synthesis and simulation — Can use existing VHDL and Verilog modules mixed with System. Verilog n Interface features: — Ability to encapsulate functionality as well as connectivity — Ability to replace a group of names by a single name n New concise and powerful implicit port connection features speed design entry and provide early type checking n Allows designers to take advantage of new abstract architectural models n Allows designers to insert assertions directly into RTL code Gardner 26 MAPLD 2005/P 145

Summary of System. Verilog Design n System. Verilog increases productivity for both synthesis and simulation — Can use existing VHDL and Verilog modules mixed with System. Verilog n Interface features: — Ability to encapsulate functionality as well as connectivity — Ability to replace a group of names by a single name n New concise and powerful implicit port connection features speed design entry and provide early type checking n Allows designers to take advantage of new abstract architectural models n Allows designers to insert assertions directly into RTL code Gardner 26 MAPLD 2005/P 145

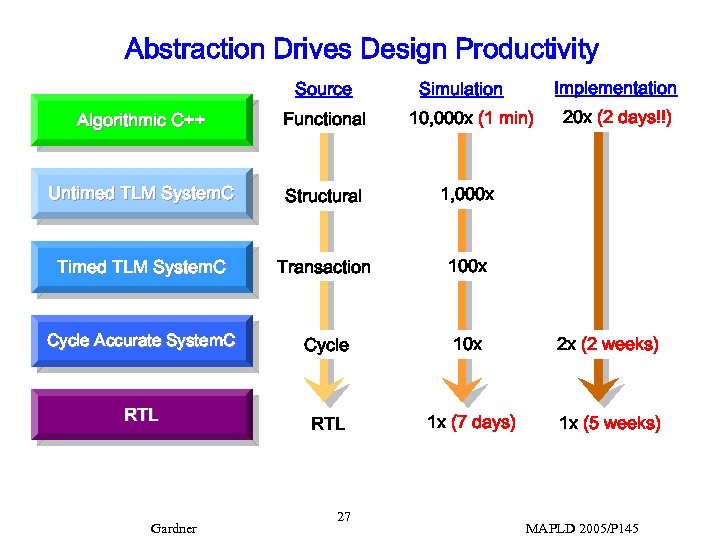

Abstraction Drives Design Productivity Source Implementation Simulation 20 x (2 days!!) Algorithmic C++ Functional 10, 000 x (1 min) Untimed TLM System. C Structural 1, 000 x Timed TLM System. C Transaction 100 x Cycle Accurate System. C Cycle 10 x 2 x (2 weeks) RTL 1 x (7 days) 1 x (5 weeks) Gardner 27 MAPLD 2005/P 145

Abstraction Drives Design Productivity Source Implementation Simulation 20 x (2 days!!) Algorithmic C++ Functional 10, 000 x (1 min) Untimed TLM System. C Structural 1, 000 x Timed TLM System. C Transaction 100 x Cycle Accurate System. C Cycle 10 x 2 x (2 weeks) RTL 1 x (7 days) 1 x (5 weeks) Gardner 27 MAPLD 2005/P 145

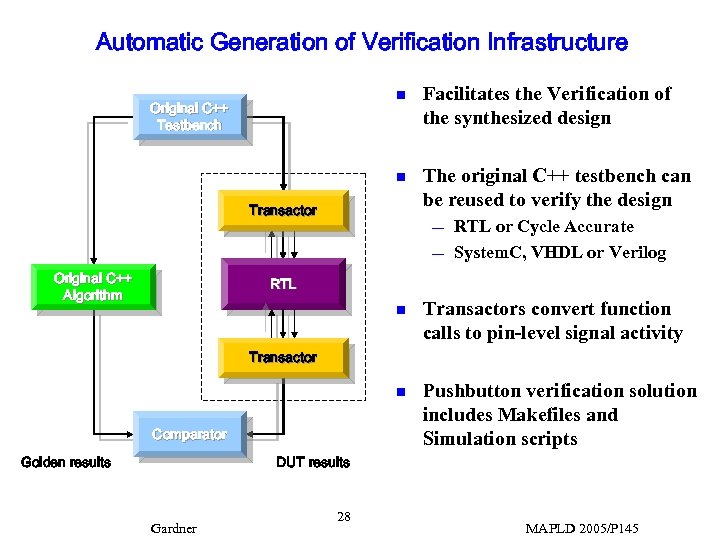

Automatic Generation of Verification Infrastructure n Facilitates the Verification of the synthesized design n Original C++ Testbench The original C++ testbench can be reused to verify the design Transactor — — Original C++ Algorithm RTL or Cycle Accurate System. C, VHDL or Verilog RTL n Transactors convert function calls to pin-level signal activity n Pushbutton verification solution includes Makefiles and Simulation scripts Transactor Comparator Golden results DUT results Gardner 28 MAPLD 2005/P 145

Automatic Generation of Verification Infrastructure n Facilitates the Verification of the synthesized design n Original C++ Testbench The original C++ testbench can be reused to verify the design Transactor — — Original C++ Algorithm RTL or Cycle Accurate System. C, VHDL or Verilog RTL n Transactors convert function calls to pin-level signal activity n Pushbutton verification solution includes Makefiles and Simulation scripts Transactor Comparator Golden results DUT results Gardner 28 MAPLD 2005/P 145

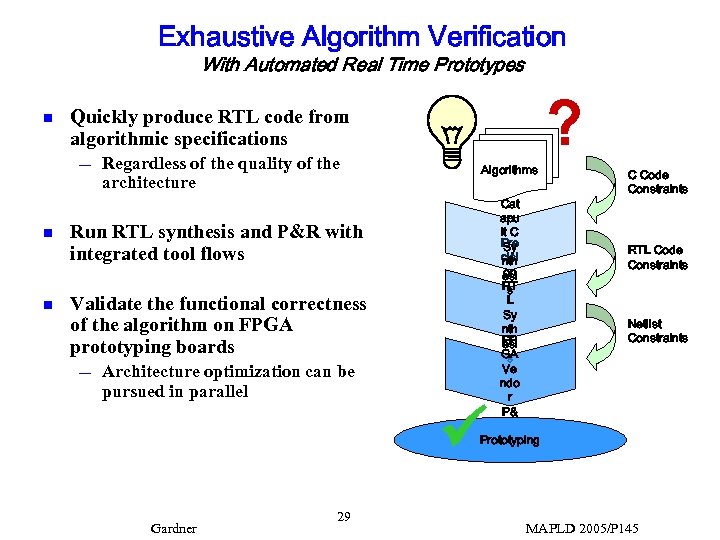

Exhaustive Algorithm Verification With Automated Real Time Prototypes n — n n ? Quickly produce RTL code from algorithmic specifications Regardless of the quality of the architecture Run RTL synthesis and P&R with integrated tool flows Validate the functional correctness of the algorithm on FPGA prototyping boards — Architecture optimization can be pursued in parallel Gardner 29 Algorithms Cat apu lt C Pre Sy cisi nth on esi RT s L Sy nth FP esi GA s Ve ndo r P& R Prototyping C Code Constraints RTL Code Constraints Netlist Constraints MAPLD 2005/P 145

Exhaustive Algorithm Verification With Automated Real Time Prototypes n — n n ? Quickly produce RTL code from algorithmic specifications Regardless of the quality of the architecture Run RTL synthesis and P&R with integrated tool flows Validate the functional correctness of the algorithm on FPGA prototyping boards — Architecture optimization can be pursued in parallel Gardner 29 Algorithms Cat apu lt C Pre Sy cisi nth on esi RT s L Sy nth FP esi GA s Ve ndo r P& R Prototyping C Code Constraints RTL Code Constraints Netlist Constraints MAPLD 2005/P 145

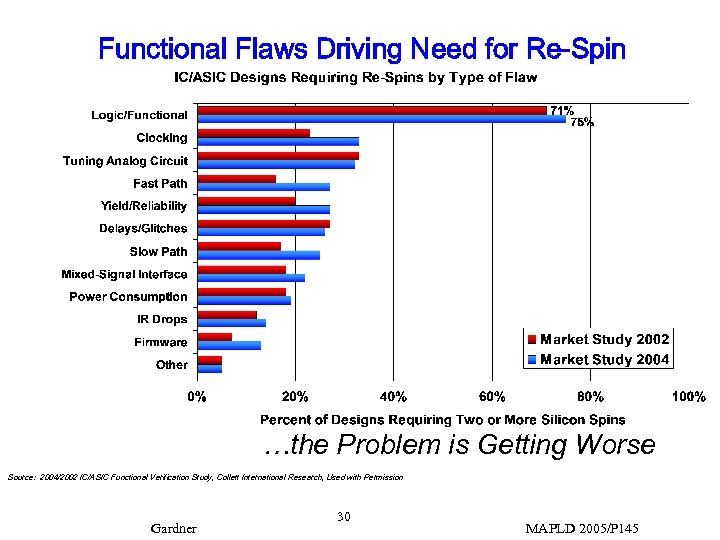

Functional Flaws Driving Need for Re-Spin …the Problem is Getting Worse Source: 2004/2002 IC/ASIC Functional Verification Study, Collett International Research, Used with Permission Gardner 30 MAPLD 2005/P 145

Functional Flaws Driving Need for Re-Spin …the Problem is Getting Worse Source: 2004/2002 IC/ASIC Functional Verification Study, Collett International Research, Used with Permission Gardner 30 MAPLD 2005/P 145

Methodology Explosion Targeting Verification n n n n Assertion-based verification Functional coverage Constrained-random testing Coverage-driven verification Dynamic-formal verification Transaction-level verification Model checking And more. . . Gardner 31 MAPLD 2005/P 145

Methodology Explosion Targeting Verification n n n n Assertion-based verification Functional coverage Constrained-random testing Coverage-driven verification Dynamic-formal verification Transaction-level verification Model checking And more. . . Gardner 31 MAPLD 2005/P 145

System. Verilog for Verification n System. Verilog is a complete Verification Language — — Can be used with VHDL Stimulus generation capabilities n n n — Functional coverage modeling n n — Measure the verification quality and test effectiveness Dynamic reactivity with constrained-random stimulus generation Assertion-Based Verification n n — Dynamically configurable constrained-random value generation Ability to generate constrained-random stimulus sequences Ability to randomly select control paths (test scenario selection, etc. ) Property specification Assertion & coverage monitoring High-level modeling (programming) capabilities n n Efficiently and effectively model the operational environment Develop reusable verification environments Gardner 32 MAPLD 2005/P 145

System. Verilog for Verification n System. Verilog is a complete Verification Language — — Can be used with VHDL Stimulus generation capabilities n n n — Functional coverage modeling n n — Measure the verification quality and test effectiveness Dynamic reactivity with constrained-random stimulus generation Assertion-Based Verification n n — Dynamically configurable constrained-random value generation Ability to generate constrained-random stimulus sequences Ability to randomly select control paths (test scenario selection, etc. ) Property specification Assertion & coverage monitoring High-level modeling (programming) capabilities n n Efficiently and effectively model the operational environment Develop reusable verification environments Gardner 32 MAPLD 2005/P 145

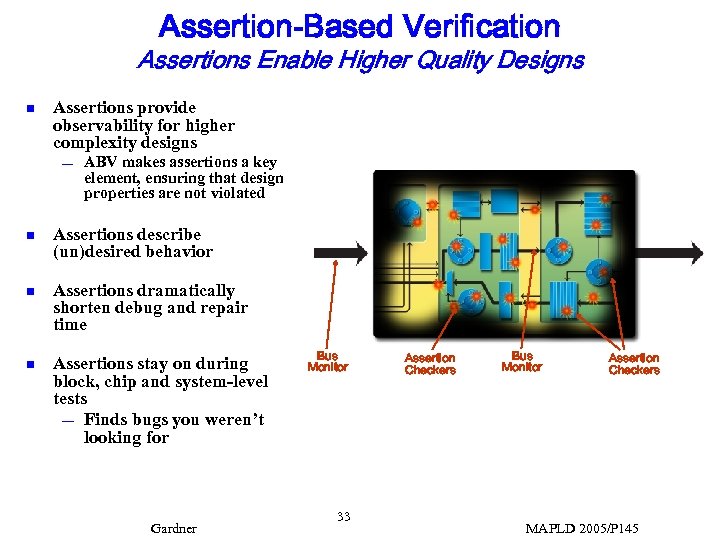

Assertion-Based Verification Assertions Enable Higher Quality Designs n Assertions provide observability for higher complexity designs — Reference Model ABV makes assertions a key element, ensuring that design properties are not violated n Assertions describe (un)desired behavior n Assertions dramatically shorten debug and repair time n Assertions stay on during block, chip and system-level tests — Finds bugs you weren’t looking for Gardner Bus Monitor 33 Assertion Checkers Bus Monitor Assertion Checkers MAPLD 2005/P 145

Assertion-Based Verification Assertions Enable Higher Quality Designs n Assertions provide observability for higher complexity designs — Reference Model ABV makes assertions a key element, ensuring that design properties are not violated n Assertions describe (un)desired behavior n Assertions dramatically shorten debug and repair time n Assertions stay on during block, chip and system-level tests — Finds bugs you weren’t looking for Gardner Bus Monitor 33 Assertion Checkers Bus Monitor Assertion Checkers MAPLD 2005/P 145

Coverage-Driven Verification is effectively metric-less — Few designers know if their strategy is adequate or efficient — Sign-off criteria are ad hoc and vary by company — Code coverage is not a functional verification metric Gardner 34 MAPLD 2005/P 145

Coverage-Driven Verification is effectively metric-less — Few designers know if their strategy is adequate or efficient — Sign-off criteria are ad hoc and vary by company — Code coverage is not a functional verification metric Gardner 34 MAPLD 2005/P 145

Expect Widespread Use of Coverage-Driven Verification n PSL and System. Verilog provide coverage constructs n Simulators integrating functional coverage to improve performance and debug n New test strategies require functional coverage — Random and constrained random tests need coverage to determine what they tested Gardner 35 MAPLD 2005/P 145

Expect Widespread Use of Coverage-Driven Verification n PSL and System. Verilog provide coverage constructs n Simulators integrating functional coverage to improve performance and debug n New test strategies require functional coverage — Random and constrained random tests need coverage to determine what they tested Gardner 35 MAPLD 2005/P 145

Clock-Domain Crossings n Incorrect handling of Clock-Domain Crossing (CDC) signals is the 2 nd major cause of re-spins n Traditional verification techniques do not work for CDC signals n CDC problems are subtle, will occur in hardware, and are complex to debug Assertion Synthesis automates CDC verification, significantly reducing the risk of CDC-related silicon re-spins Gardner 36 MAPLD 2005/P 145

Clock-Domain Crossings n Incorrect handling of Clock-Domain Crossing (CDC) signals is the 2 nd major cause of re-spins n Traditional verification techniques do not work for CDC signals n CDC problems are subtle, will occur in hardware, and are complex to debug Assertion Synthesis automates CDC verification, significantly reducing the risk of CDC-related silicon re-spins Gardner 36 MAPLD 2005/P 145

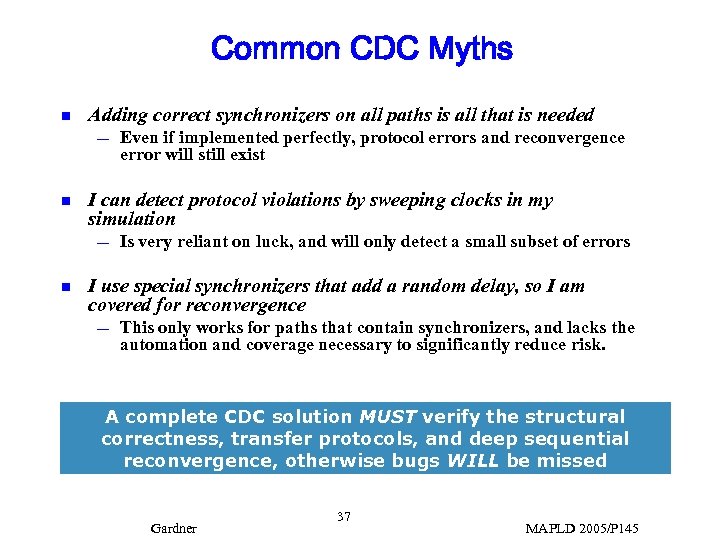

Common CDC Myths n Adding correct synchronizers on all paths is all that is needed — n I can detect protocol violations by sweeping clocks in my simulation — n Even if implemented perfectly, protocol errors and reconvergence error will still exist Is very reliant on luck, and will only detect a small subset of errors I use special synchronizers that add a random delay, so I am covered for reconvergence — This only works for paths that contain synchronizers, and lacks the automation and coverage necessary to significantly reduce risk. A complete CDC solution MUST verify the structural correctness, transfer protocols, and deep sequential reconvergence, otherwise bugs WILL be missed Gardner 37 MAPLD 2005/P 145

Common CDC Myths n Adding correct synchronizers on all paths is all that is needed — n I can detect protocol violations by sweeping clocks in my simulation — n Even if implemented perfectly, protocol errors and reconvergence error will still exist Is very reliant on luck, and will only detect a small subset of errors I use special synchronizers that add a random delay, so I am covered for reconvergence — This only works for paths that contain synchronizers, and lacks the automation and coverage necessary to significantly reduce risk. A complete CDC solution MUST verify the structural correctness, transfer protocols, and deep sequential reconvergence, otherwise bugs WILL be missed Gardner 37 MAPLD 2005/P 145

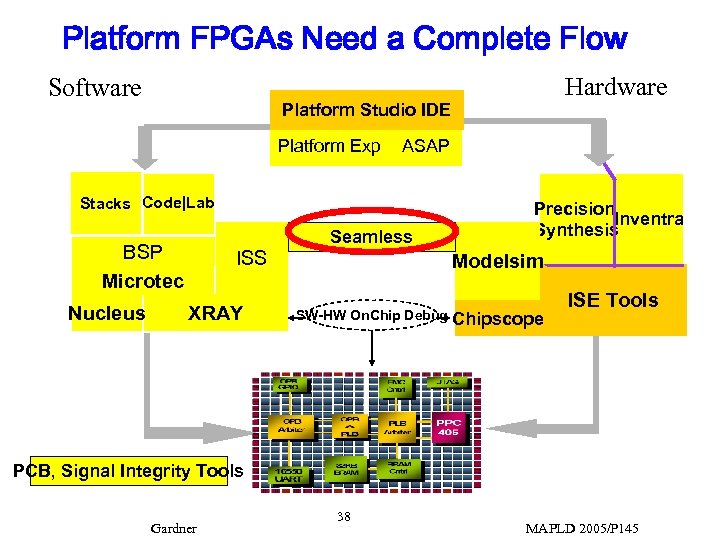

Platform FPGAs Need a Complete Flow Software Platform Studio IDE Platform Exp ASAP Stacks Code|Lab Seamless BSP Microtec Nucleus Hardware ISS XRAY Precision Inventra Synthesis Modelsim SW-HW On. Chip Debug Chipscope ISE Tools PCB, Signal Integrity Tools Gardner 38 MAPLD 2005/P 145

Platform FPGAs Need a Complete Flow Software Platform Studio IDE Platform Exp ASAP Stacks Code|Lab Seamless BSP Microtec Nucleus Hardware ISS XRAY Precision Inventra Synthesis Modelsim SW-HW On. Chip Debug Chipscope ISE Tools PCB, Signal Integrity Tools Gardner 38 MAPLD 2005/P 145

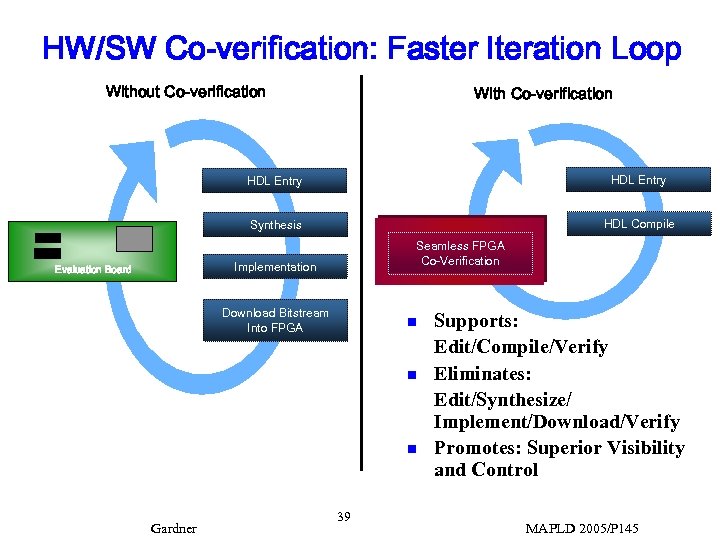

HW/SW Co-verification: Faster Iteration Loop Without Co-verification With Co-verification HDL Entry Synthesis HDL Compile Seamless FPGA Co-Verification Implementation Evaluation Board Download Bitstream Into FPGA n n n Gardner 39 Supports: Edit/Compile/Verify Eliminates: Edit/Synthesize/ Implement/Download/Verify Promotes: Superior Visibility and Control MAPLD 2005/P 145

HW/SW Co-verification: Faster Iteration Loop Without Co-verification With Co-verification HDL Entry Synthesis HDL Compile Seamless FPGA Co-Verification Implementation Evaluation Board Download Bitstream Into FPGA n n n Gardner 39 Supports: Edit/Compile/Verify Eliminates: Edit/Synthesize/ Implement/Download/Verify Promotes: Superior Visibility and Control MAPLD 2005/P 145

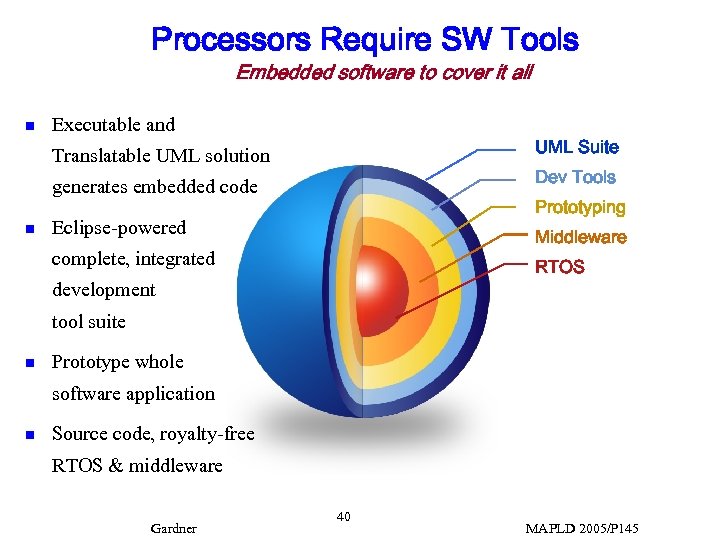

Processors Require SW Tools Embedded software to cover it all n Executable and UML Suite Translatable UML solution Dev Tools generates embedded code n Prototyping Eclipse-powered Middleware complete, integrated RTOS development tool suite n Prototype whole software application n Source code, royalty-free RTOS & middleware Gardner 40 MAPLD 2005/P 145

Processors Require SW Tools Embedded software to cover it all n Executable and UML Suite Translatable UML solution Dev Tools generates embedded code n Prototyping Eclipse-powered Middleware complete, integrated RTOS development tool suite n Prototype whole software application n Source code, royalty-free RTOS & middleware Gardner 40 MAPLD 2005/P 145

Support for Processor-based FPGAs n n RTOS support for both Xilinx Micro. Blaze and Power. PC architectures and Altera NIOS, NIOS II and ARM architectures Target software debugger and build environment Support for Xilinx Spartan 3, Virtex II Pro, and Virtex-4 and Altera Cyclone II and Stratix II Embedded software suite for FPGA system design must include complete tool offerings and target software platform, including high-level modeling with xt. UML and advanced target software debugging environment. Gardner 41 MAPLD 2005/P 145

Support for Processor-based FPGAs n n RTOS support for both Xilinx Micro. Blaze and Power. PC architectures and Altera NIOS, NIOS II and ARM architectures Target software debugger and build environment Support for Xilinx Spartan 3, Virtex II Pro, and Virtex-4 and Altera Cyclone II and Stratix II Embedded software suite for FPGA system design must include complete tool offerings and target software platform, including high-level modeling with xt. UML and advanced target software debugging environment. Gardner 41 MAPLD 2005/P 145

Summary n n With engineers from software, hardware and system disciplines all converging on FPGAs, it is important to focus on the methods that can help differentiate your solution from others. It is necessary to use all the basic verification and design tools, but there are new technologies emerging that can better address the unique requirements of Mil/Aero applications. Gardner 42 MAPLD 2005/P 145

Summary n n With engineers from software, hardware and system disciplines all converging on FPGAs, it is important to focus on the methods that can help differentiate your solution from others. It is necessary to use all the basic verification and design tools, but there are new technologies emerging that can better address the unique requirements of Mil/Aero applications. Gardner 42 MAPLD 2005/P 145