7fcc26a3dd608cbd8a110f20da4feb23.ppt

- Количество слайдов: 42

MCAO Control System Corinne Boyer

Changes since the Co. DR MCAO • The requirements for all the sub-systems of the MCAO have been modified and refined. • The Interface Control Documents (ICDs) between MCAO and the other telescopes systems have been written as well as the internal sub-system interface ICD. • Preliminary design documents (mainly flow diagrams) have been written for some of the sub-systems. May 24 -25, 2001 MCAO Preliminary Design Review 2

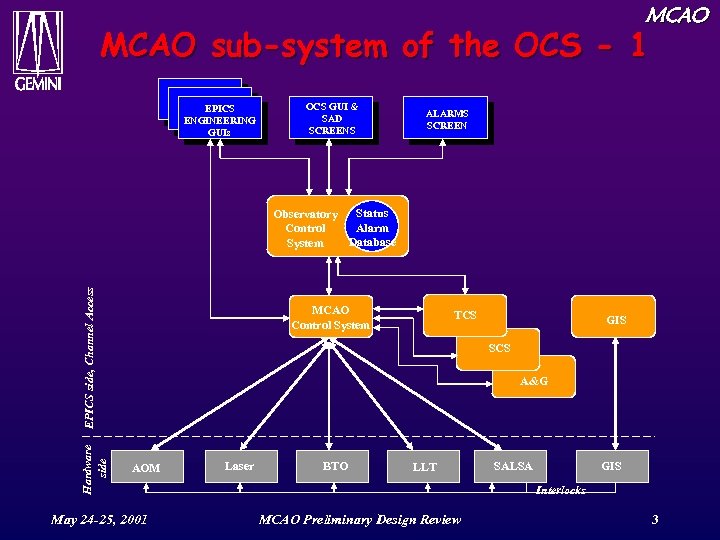

MCAO sub-system of the OCS - 1 EPICS ENGINEERING GUIs OCS GUI & SAD SCREENS ALARMS SCREEN Hardware side EPICS side, Channel Access Status Observatory Alarm Control Database System MCAO Control System TCS GIS SCS A&G AOM May 24 -25, 2001 Laser BTO LLT SALSA GIS Interlocks MCAO Preliminary Design Review 3

MCAO sub-system of the OCS - 2 • This solution is different from the one chosen for the Altair, which is a subsystem of the TCS. The reasons are: – The MCAO system is an independent system with a minimal interface to the TCS, – The MCAO system needs to be synchronized with the other instruments controlled by the OCS, – There will be some very complex sequences that need to be done at the level of the Sequencer which will be most efficiently performed by using a direct-access tool like ocswish. May 24 -25, 2001 MCAO Preliminary Design Review 4

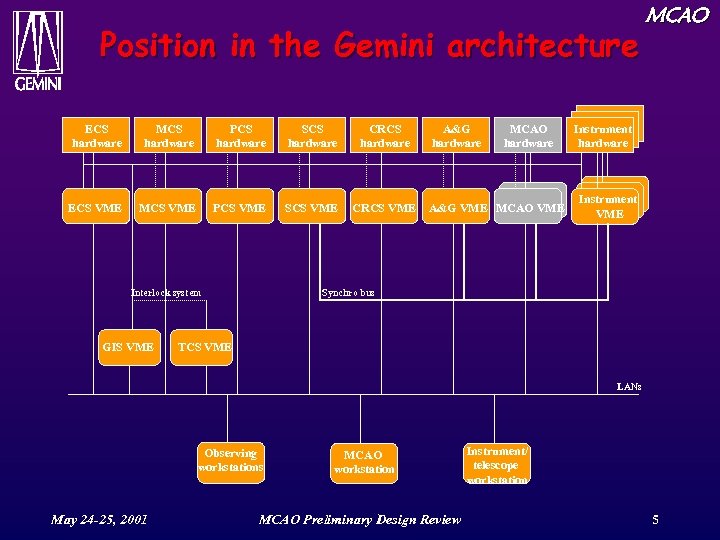

Position in the Gemini architecture ECS hardware MCS hardware PCS hardware SCS hardware CRCS hardware ECS VME MCS VME PCS VME SCS VME CRCS VME Interlock system GIS VME A&G hardware MCAO hardware A&G VME MCAO Instrument hardware Instrument VME Synchro bus TCS VME LANs Observing workstations May 24 -25, 2001 MCAO workstation MCAO Preliminary Design Review Instrument/ telescope workstation 5

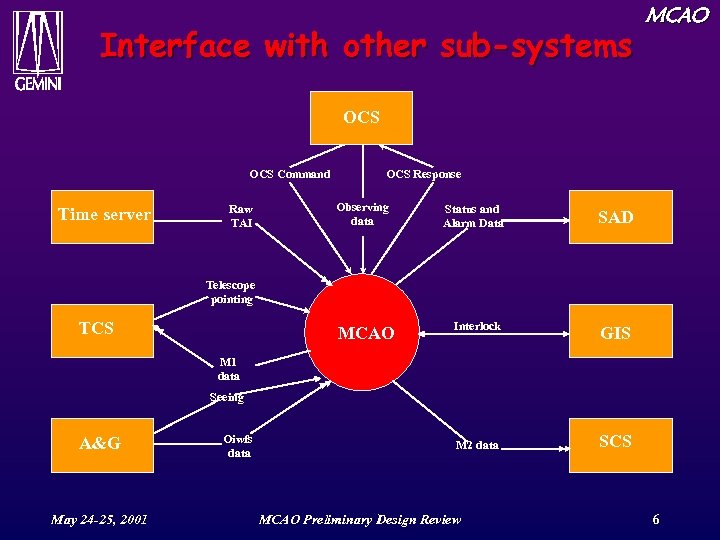

Interface with other sub-systems MCAO OCS Command Time server Raw TAI OCS Response Observing data Status and Alarm Data SAD Telescope pointing TCS MCAO Interlock GIS M 1 data Seeing A&G May 24 -25, 2001 Oiwfs data M 2 data MCAO Preliminary Design Review SCS 6

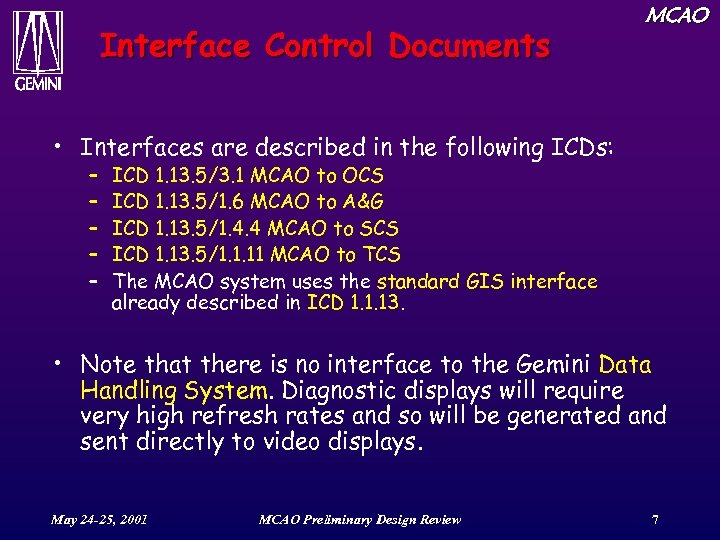

Interface Control Documents MCAO • Interfaces are described in the following ICDs: – – – ICD 1. 13. 5/3. 1 MCAO to OCS ICD 1. 13. 5/1. 6 MCAO to A&G ICD 1. 13. 5/1. 4. 4 MCAO to SCS ICD 1. 13. 5/1. 1. 11 MCAO to TCS The MCAO system uses the standard GIS interface already described in ICD 1. 1. 13. • Note that there is no interface to the Gemini Data Handling System. Diagnostic displays will require very high refresh rates and so will be generated and sent directly to video displays. May 24 -25, 2001 MCAO Preliminary Design Review 7

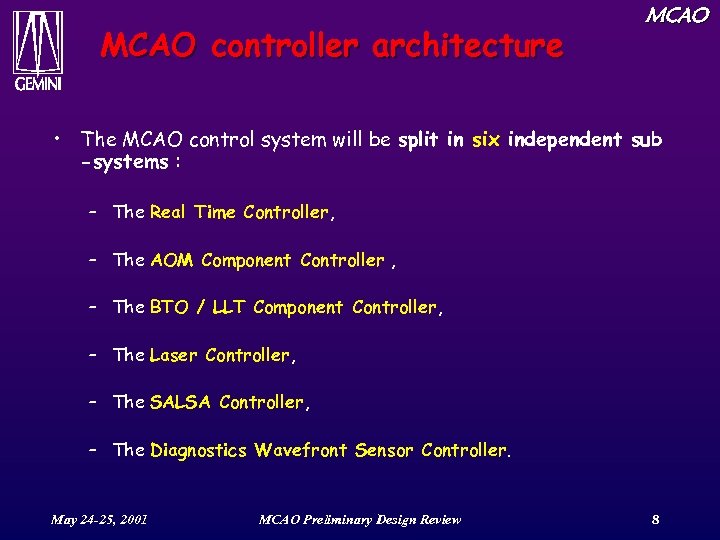

MCAO controller architecture MCAO • The MCAO control system will be split in six independent sub -systems : – The Real Time Controller, – The AOM Component Controller , – The BTO / LLT Component Controller, – The Laser Controller, – The SALSA Controller, – The Diagnostics Wavefront Sensor Controller. May 24 -25, 2001 MCAO Preliminary Design Review 8

Gemini model MCAO • The MCAO control system will be implemented using the standard Gemini control system model. • An Instrument Sequencer will manage the 6 independent subsystems and act as the main public interface for the entire MCAO system. • The sequencer will coordinate all of the internal tasks and provide external systems with the commands and status information they need, to control the MCAO System. May 24 -25, 2001 MCAO Preliminary Design Review 9

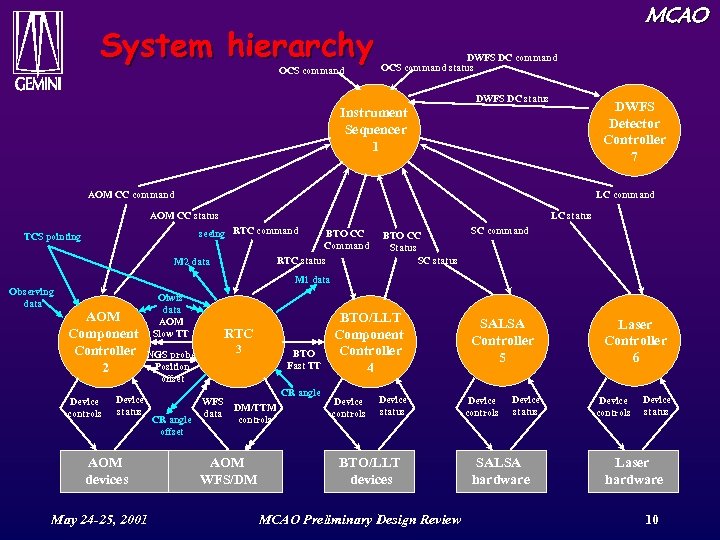

System hierarchy OCS command MCAO DWFS DC command OCS command status DWFS DC status DWFS Detector Controller 7 Instrument Sequencer 1 AOM CC command LC command AOM CC status LC status seeing RTC command TCS pointing BTO CC Command RTC status M 2 data BTO CC Status SC status SC command M 1 data Observing data AOM Component Controller 2 Device controls Oiwfs data AOM Slow TT RTC 3 NGS probe Position offset Device status AOM devices May 24 -25, 2001 CR angle offset WFS data BTO Fast TT CR angle DM/TTM controls AOM WFS/DM BTO/LLT Component Controller 4 Device controls Device status BTO/LLT devices MCAO Preliminary Design Review SALSA Controller 5 Device controls Device status SALSA hardware Laser Controller 6 Device controls Device status Laser hardware 10

MCAO Sequencer - 1 MCAO • The Sequencer will be implemented using only standard EPICS records. • Command status information that pass between the OCS and MCAO systems is described in the OCS/MCAO ICD. • The commands reboot, initialize, datum, park, test, simulate and debug will be implemented to perform global actions on all of the associated devices for all the sub-systems. May 24 -25, 2001 MCAO Preliminary Design Review 11

MCAO Sequencer - 2 MCAO • The standard commands pause, continue, stop and abort will not be implemented. The observe command will be rejected during the preset directive and the others commands verify, end. Verify, guide, end. Guide, end. Observe will be ignored. • Night operation and calibration and maintenance sequences will be implemented using ocswish tool. • The setup/engineering command set can be found in the MCAO Internal ICD. May 24 -25, 2001 MCAO Preliminary Design Review 12

BTO/LLT Component Controller MCAO • This sub-system is responsible for managing all of the optomechanical devices associated with the BTO and LLT under the direct control of the MCAO Instrument Sequencer. • The commands initialize, datum, park, test, simulate and debug will be implemented to perform global actions on all of the associated devices. • The component controller will be a hybrid EPICS/Vx. Works implementation which uses a mix of standard EPICS records and custom assembly and device control records and also dedicated Vx. Works tasks. May 24 -25, 2001 MCAO Preliminary Design Review 13

BTO/LLT CC Interfaces MCAO • The BTO/LLT CC will interface directly with: – the RTC to receive Fast Steering Array commands, – the SALSA sub-system to sense the state of the SALSA shutter, – the Gemini GIS system to disable all motions in the case of a hardware interlock, – the TCS system to read the telescope pointing information. May 24 -25, 2001 MCAO Preliminary Design Review 14

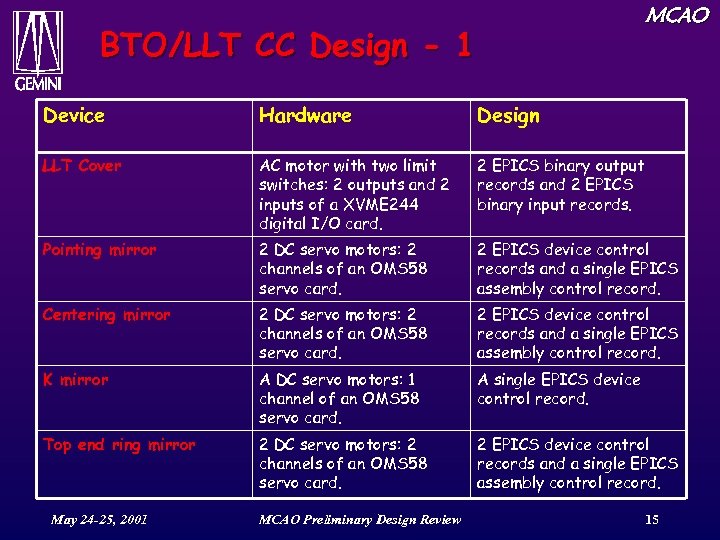

MCAO BTO/LLT CC Design - 1 Device Hardware Design LLT Cover AC motor with two limit switches: 2 outputs and 2 inputs of a XVME 244 digital I/O card. 2 EPICS binary output records and 2 EPICS binary input records. Pointing mirror 2 DC servo motors: 2 channels of an OMS 58 servo card. 2 EPICS device control records and a single EPICS assembly control record. Centering mirror 2 DC servo motors: 2 channels of an OMS 58 servo card. 2 EPICS device control records and a single EPICS assembly control record. K mirror A DC servo motors: 1 channel of an OMS 58 servo card. A single EPICS device control record. Top end ring mirror 2 DC servo motors: 2 channels of an OMS 58 servo card. 2 EPICS device control records and a single EPICS assembly control record. May 24 -25, 2001 MCAO Preliminary Design Review 15

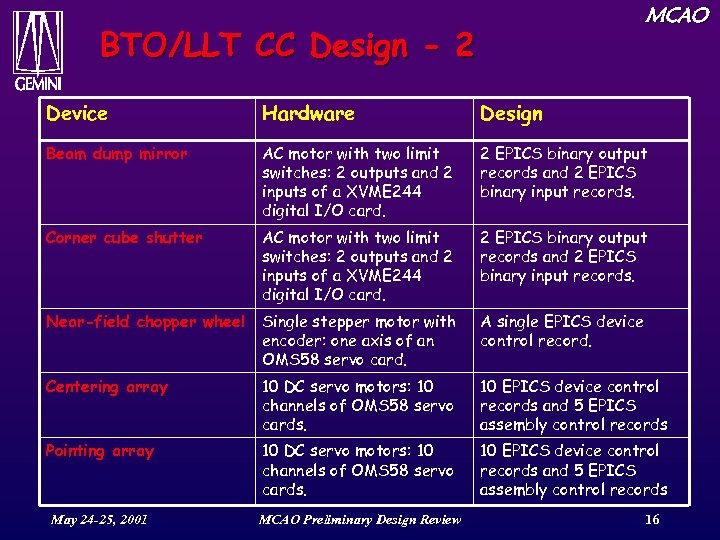

MCAO BTO/LLT CC Design - 2 Device Hardware Design Beam dump mirror AC motor with two limit switches: 2 outputs and 2 inputs of a XVME 244 digital I/O card. 2 EPICS binary output records and 2 EPICS binary input records. Corner cube shutter AC motor with two limit switches: 2 outputs and 2 inputs of a XVME 244 digital I/O card. 2 EPICS binary output records and 2 EPICS binary input records. Near-field chopper wheel Single stepper motor with encoder: one axis of an OMS 58 servo card. A single EPICS device control record. Centering array 10 DC servo motors: 10 channels of OMS 58 servo cards. 10 EPICS device control records and 5 EPICS assembly control records Pointing array 10 DC servo motors: 10 channels of OMS 58 servo cards. 10 EPICS device control records and 5 EPICS assembly control records May 24 -25, 2001 MCAO Preliminary Design Review 16

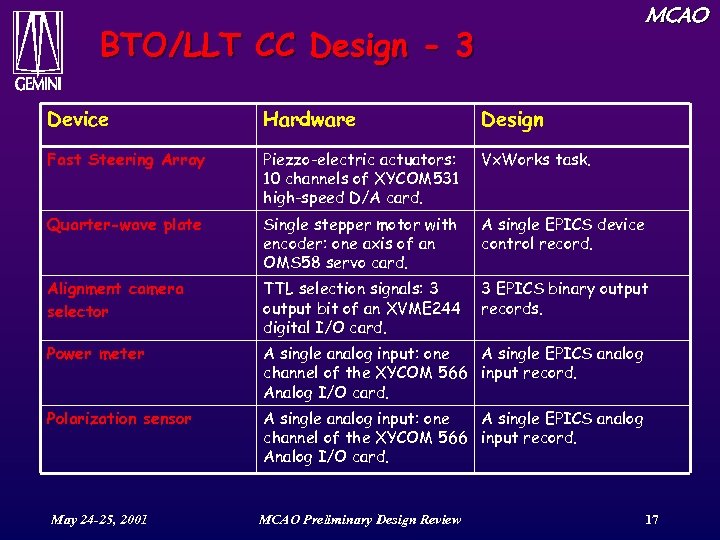

MCAO BTO/LLT CC Design - 3 Device Hardware Design Fast Steering Array Piezzo-electric actuators: 10 channels of XYCOM 531 high-speed D/A card. Vx. Works task. Quarter-wave plate Single stepper motor with encoder: one axis of an OMS 58 servo card. A single EPICS device control record. Alignment camera selector TTL selection signals: 3 output bit of an XVME 244 digital I/O card. 3 EPICS binary output records. Power meter A single analog input: one A single EPICS analog channel of the XYCOM 566 input record. Analog I/O card. Polarization sensor A single analog input: one A single EPICS analog channel of the XYCOM 566 input record. Analog I/O card. May 24 -25, 2001 MCAO Preliminary Design Review 17

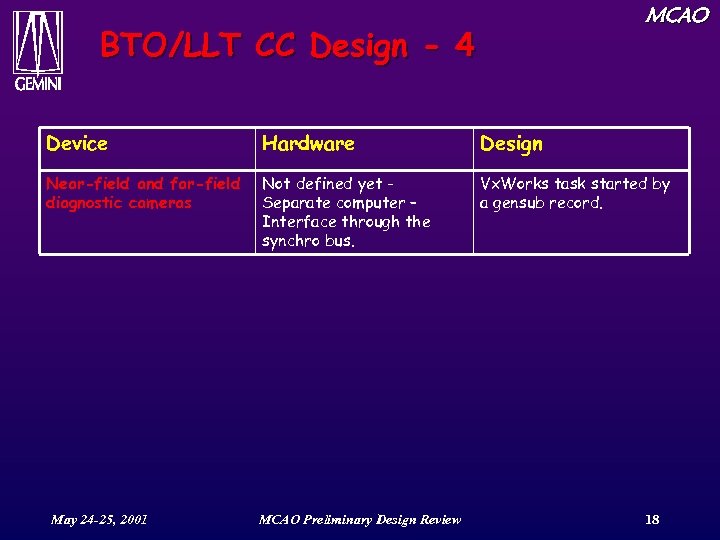

MCAO BTO/LLT CC Design - 4 Device Hardware Design Near-field and far-field diagnostic cameras Not defined yet Separate computer – Interface through the synchro bus. Vx. Works task started by a gensub record. May 24 -25, 2001 MCAO Preliminary Design Review 18

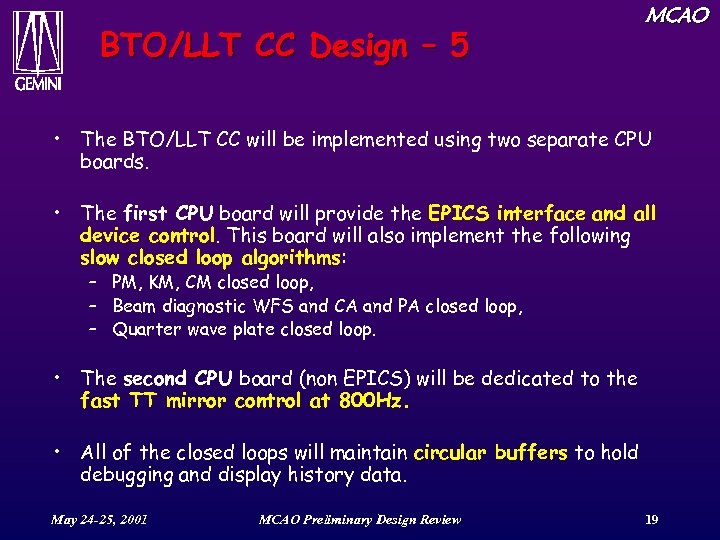

BTO/LLT CC Design – 5 MCAO • The BTO/LLT CC will be implemented using two separate CPU boards. • The first CPU board will provide the EPICS interface and all device control. This board will also implement the following slow closed loop algorithms: – PM, KM, CM closed loop, – Beam diagnostic WFS and CA and PA closed loop, – Quarter wave plate closed loop. • The second CPU board (non EPICS) will be dedicated to the fast TT mirror control at 800 Hz. • All of the closed loops will maintain circular buffers to hold debugging and display history data. May 24 -25, 2001 MCAO Preliminary Design Review 19

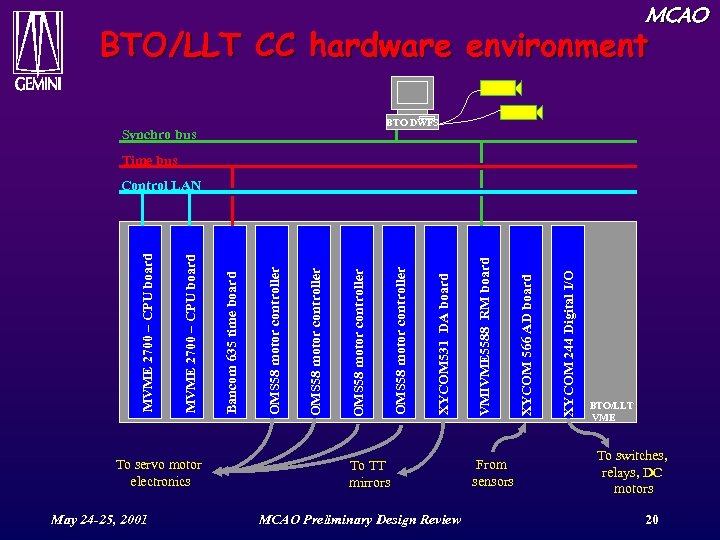

May 24 -25, 2001 To servo motor electronics To TT mirrors MCAO Preliminary Design Review From sensors XYCOM 244 Digital I/O XYCOM 566 AD board VMIVME 5588 RM board XYCOM 531 DA board Synchro bus OMS 58 motor controller Bancom 635 time board MVME 2700 – CPU board MCAO BTO/LLT CC hardware environment BTO DWFS Time bus Control LAN BTO/LLT VME To switches, relays, DC motors 20

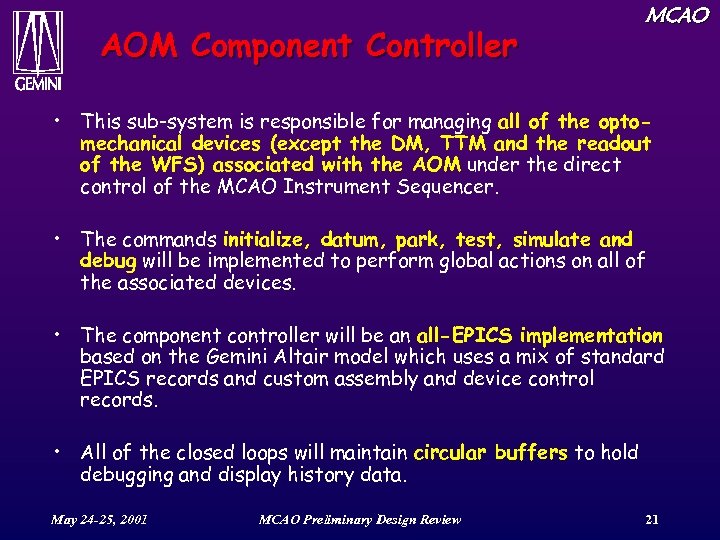

AOM Component Controller MCAO • This sub-system is responsible for managing all of the optomechanical devices (except the DM, TTM and the readout of the WFS) associated with the AOM under the direct control of the MCAO Instrument Sequencer. • The commands initialize, datum, park, test, simulate and debug will be implemented to perform global actions on all of the associated devices. • The component controller will be an all-EPICS implementation based on the Gemini Altair model which uses a mix of standard EPICS records and custom assembly and device control records. • All of the closed loops will maintain circular buffers to hold debugging and display history data. May 24 -25, 2001 MCAO Preliminary Design Review 21

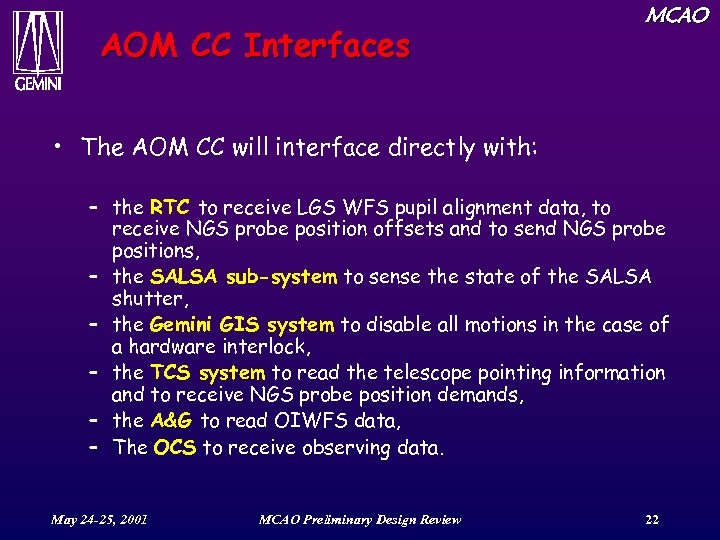

AOM CC Interfaces MCAO • The AOM CC will interface directly with: – the RTC to receive LGS WFS pupil alignment data, to receive NGS probe position offsets and to send NGS probe positions, – the SALSA sub-system to sense the state of the SALSA shutter, – the Gemini GIS system to disable all motions in the case of a hardware interlock, – the TCS system to read the telescope pointing information and to receive NGS probe position demands, – the A&G to read OIWFS data, – The OCS to receive observing data. May 24 -25, 2001 MCAO Preliminary Design Review 22

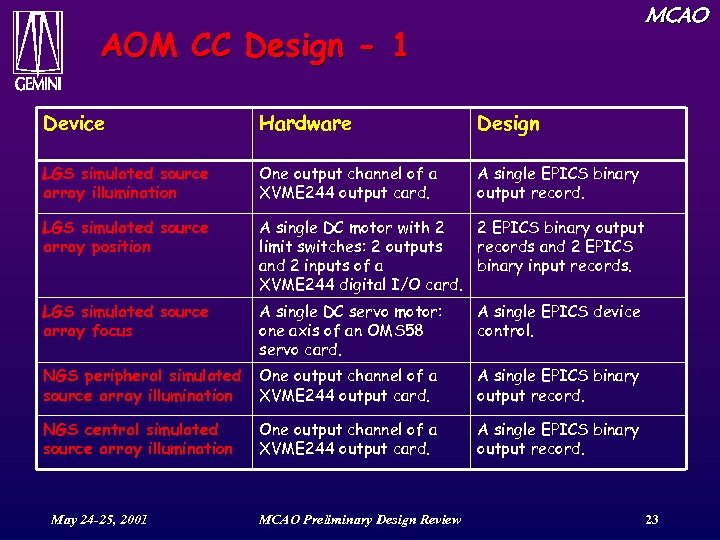

MCAO AOM CC Design - 1 Device Hardware Design LGS simulated source array illumination One output channel of a XVME 244 output card. A single EPICS binary output record. LGS simulated source array position A single DC motor with 2 2 EPICS binary output limit switches: 2 outputs records and 2 EPICS and 2 inputs of a binary input records. XVME 244 digital I/O card. LGS simulated source array focus A single DC servo motor: one axis of an OMS 58 servo card. A single EPICS device control. NGS peripheral simulated source array illumination One output channel of a XVME 244 output card. A single EPICS binary output record. NGS central simulated source array illumination One output channel of a XVME 244 output card. A single EPICS binary output record. May 24 -25, 2001 MCAO Preliminary Design Review 23

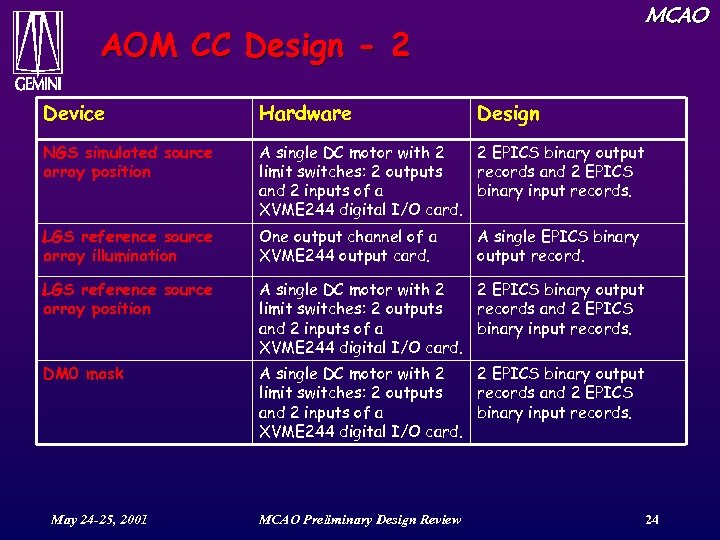

MCAO AOM CC Design - 2 Device Hardware NGS simulated source array position A single DC motor with 2 2 EPICS binary output limit switches: 2 outputs records and 2 EPICS and 2 inputs of a binary input records. XVME 244 digital I/O card. LGS reference source array illumination One output channel of a XVME 244 output card. LGS reference source array position A single DC motor with 2 2 EPICS binary output limit switches: 2 outputs records and 2 EPICS and 2 inputs of a binary input records. XVME 244 digital I/O card. DM 0 mask A single DC motor with 2 2 EPICS binary output limit switches: 2 outputs records and 2 EPICS and 2 inputs of a binary input records. XVME 244 digital I/O card. May 24 -25, 2001 MCAO Preliminary Design Review Design A single EPICS binary output record. 24

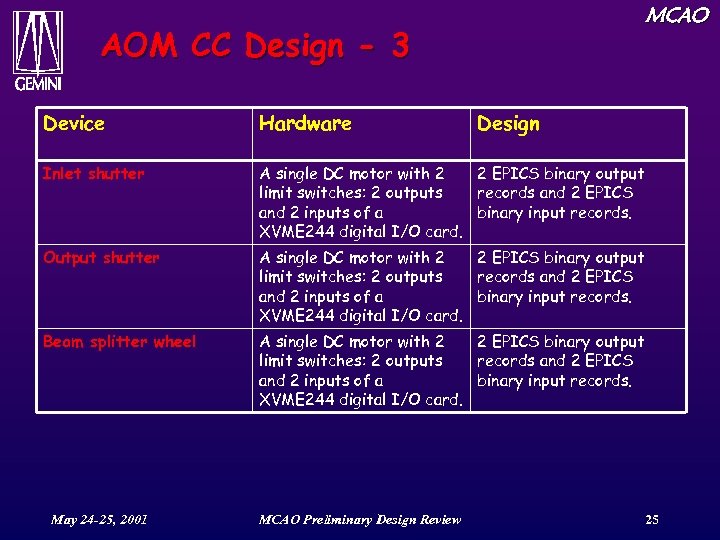

MCAO AOM CC Design - 3 Device Hardware Inlet shutter A single DC motor with 2 2 EPICS binary output limit switches: 2 outputs records and 2 EPICS and 2 inputs of a binary input records. XVME 244 digital I/O card. Output shutter A single DC motor with 2 2 EPICS binary output limit switches: 2 outputs records and 2 EPICS and 2 inputs of a binary input records. XVME 244 digital I/O card. Beam splitter wheel A single DC motor with 2 2 EPICS binary output limit switches: 2 outputs records and 2 EPICS and 2 inputs of a binary input records. XVME 244 digital I/O card. May 24 -25, 2001 MCAO Preliminary Design Review Design 25

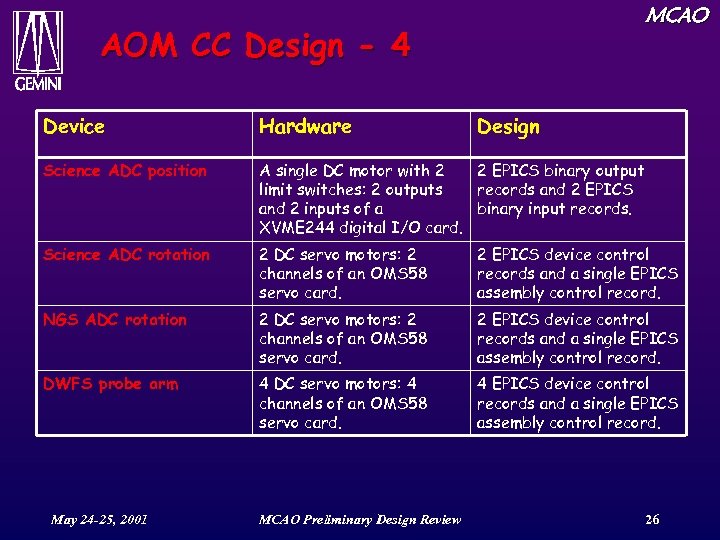

MCAO AOM CC Design - 4 Device Hardware Science ADC position A single DC motor with 2 2 EPICS binary output limit switches: 2 outputs records and 2 EPICS and 2 inputs of a binary input records. XVME 244 digital I/O card. Science ADC rotation 2 DC servo motors: 2 channels of an OMS 58 servo card. 2 EPICS device control records and a single EPICS assembly control record. NGS ADC rotation 2 DC servo motors: 2 channels of an OMS 58 servo card. 2 EPICS device control records and a single EPICS assembly control record. DWFS probe arm 4 DC servo motors: 4 channels of an OMS 58 servo card. 4 EPICS device control records and a single EPICS assembly control record. May 24 -25, 2001 MCAO Preliminary Design Review Design 26

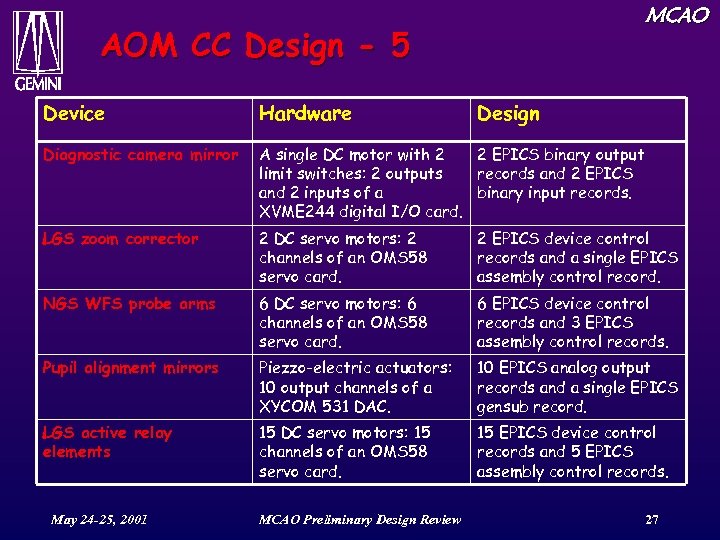

MCAO AOM CC Design - 5 Device Hardware Diagnostic camera mirror A single DC motor with 2 2 EPICS binary output limit switches: 2 outputs records and 2 EPICS and 2 inputs of a binary input records. XVME 244 digital I/O card. LGS zoom corrector 2 DC servo motors: 2 channels of an OMS 58 servo card. 2 EPICS device control records and a single EPICS assembly control record. NGS WFS probe arms 6 DC servo motors: 6 channels of an OMS 58 servo card. 6 EPICS device control records and 3 EPICS assembly control records. Pupil alignment mirrors Piezzo-electric actuators: 10 output channels of a XYCOM 531 DAC. 10 EPICS analog output records and a single EPICS gensub record. LGS active relay elements 15 DC servo motors: 15 channels of an OMS 58 servo card. 15 EPICS device control records and 5 EPICS assembly control records. May 24 -25, 2001 MCAO Preliminary Design Review Design 27

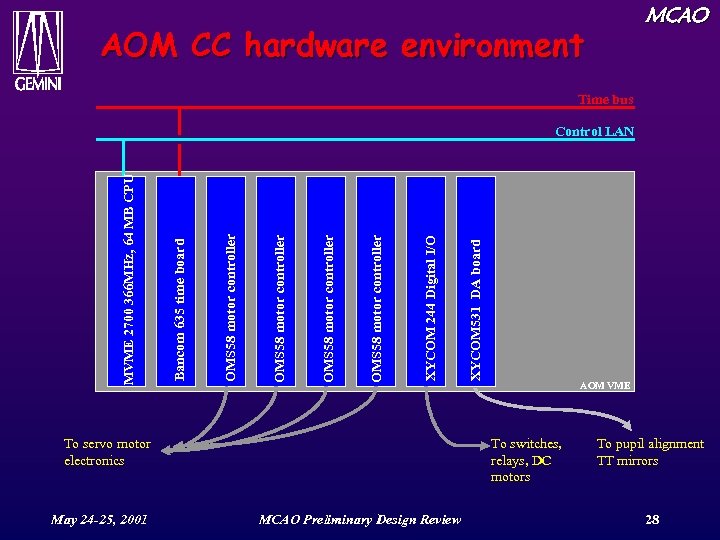

MCAO AOM CC hardware environment Time bus To servo motor electronics May 24 -25, 2001 XYCOM 531 DA board XYCOM 244 Digital I/O OMS 58 motor controller Bancom 635 time board MVME 2700 366 MHz, 64 MB CPU Control LAN AOM VME To switches, relays, DC motors MCAO Preliminary Design Review To pupil alignment TT mirrors 28

SALSA Controller MCAO • Presented with the SALSA sub-system later in the morning May 24 -25, 2001 MCAO Preliminary Design Review 29

DWFS Controller Requirements MCAO • The Diagnostic Wavefront sensor is 32 x 32 sub-aperture SH WFS, each sub aperture being composed of at least 16 x 16 pixels. A 1024 x 1024 standard CCD will be used. • This diagnostic WFS will only be used during the day to calibrate the DM commands to insure the science path wavefront quality. • Basic signal processing will be required at a slow rate: – read the pixel image, save to a file, – subtract a dark to a pixel image, – compute the centroids and save the centroids to a file. May 24 -25, 2001 MCAO Preliminary Design Review 30

DWFS Controller Design MCAO • A frame grabber installed on a PC system or on a Unix host will be implemented to read the pixel data. • Two solutions to perform signal processing: – Use of Wave. Lab, – in house developed IDL routines. • In the two cases, it will be very easy for the instrument sequencer to interface these tools. • Interface with MCAO sequencer has been defined and is described in the ICDs. May 24 -25, 2001 MCAO Preliminary Design Review 31

Real Time Controller MCAO • This controller is dedicated to the AO control loop itself. It is the heart of the system and the most critical in terms of real time performances • It will handle 3 basic real time functions: – The NGS real time control loop, – The LGS real time control loop, – The optimization and background processes. May 24 -25, 2001 MCAO Preliminary Design Review 32

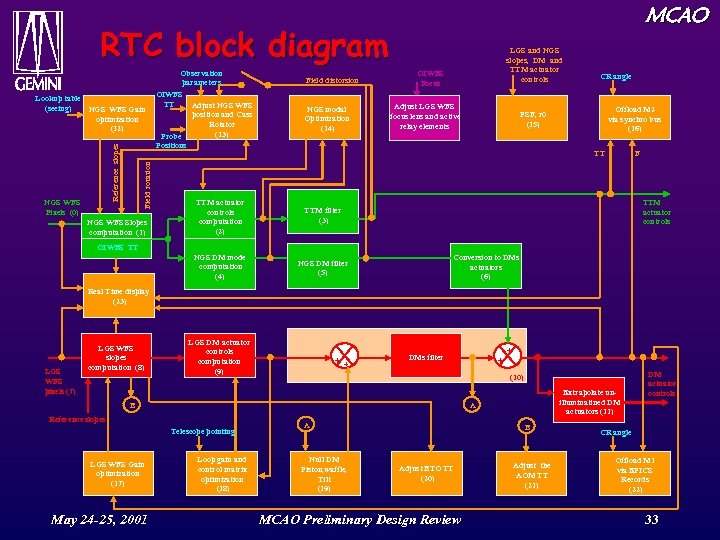

MCAO RTC block diagram Observation parameters Field rotation Reference slopes Lookup table (seeing) NGS WFS Gain optimization (12) OIWFS TT Probe Positions Adjust NGS WFS position and Cass Rotator (13) Field distorsion NGS modal Optimization (14) NGS WFS Slopes computation (1) OIWFS Focus Adjust LGS WFS focus lens and active relay elements CR angle Offload M 2 via synchro bus (16) PSF, r 0 (15) TT TTM actuator controls computation (2) NGS DM filter (5) F TTM filter (3) NGS DM mode computation (4) NGS WFS Pixels (0) LGS and NGS slopes, DM and TTM actuator controls OIWFS TT Conversion to DMs actuators (6) Real Time display (23) LGS WFS pixels (7) LGS WFS slopes computation (8) LGS DM actuator controls computation (9) + + Extrapolate unilluminatined DM actuators (11) A Telescope pointing May 24 -25, 2001 + (10) B Reference slopes LGS WFS Gain optimization (17) + DMs filter Loop gain and control matrix optimization (18) A Null DM Piston, waffle, Tilt (19) B Adjust BTO TT (20) MCAO Preliminary Design Review Adjust the AOM TT (21) DM actuator controls CR angle Offload M 1 via EPICS Records (22) 33

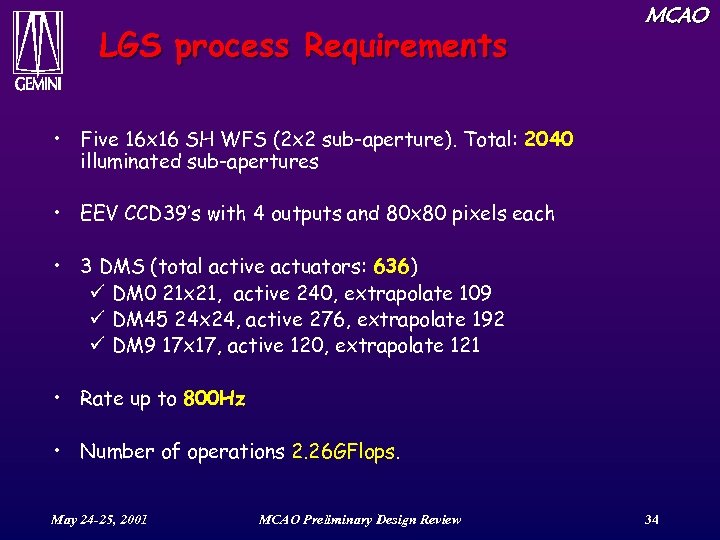

LGS process Requirements MCAO • Five 16 x 16 SH WFS (2 x 2 sub-aperture). Total: 2040 illuminated sub-apertures • EEV CCD 39’s with 4 outputs and 80 x 80 pixels each • 3 DMS (total active actuators: 636) ü DM 0 21 x 21, active 240, extrapolate 109 ü DM 45 24 x 24, active 276, extrapolate 192 ü DM 9 17 x 17, active 120, extrapolate 121 • Rate up to 800 Hz • Number of operations 2. 26 GFlops. May 24 -25, 2001 MCAO Preliminary Design Review 34

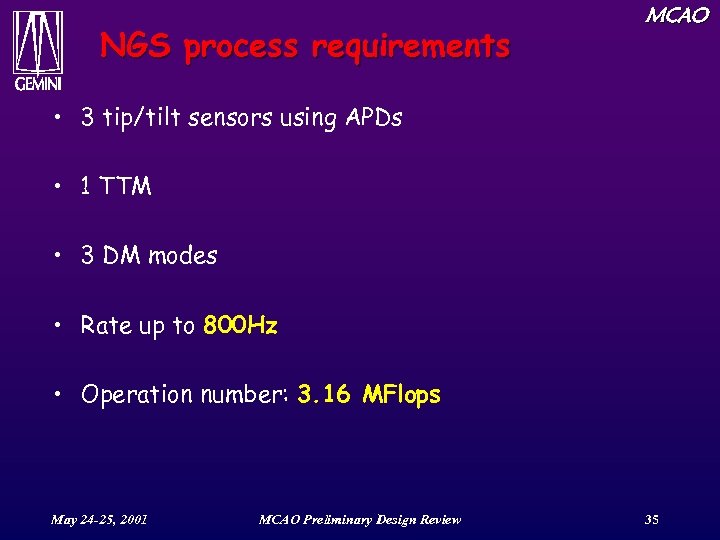

NGS process requirements MCAO • 3 tip/tilt sensors using APDs • 1 TTM • 3 DM modes • Rate up to 800 Hz • Operation number: 3. 16 MFlops May 24 -25, 2001 MCAO Preliminary Design Review 35

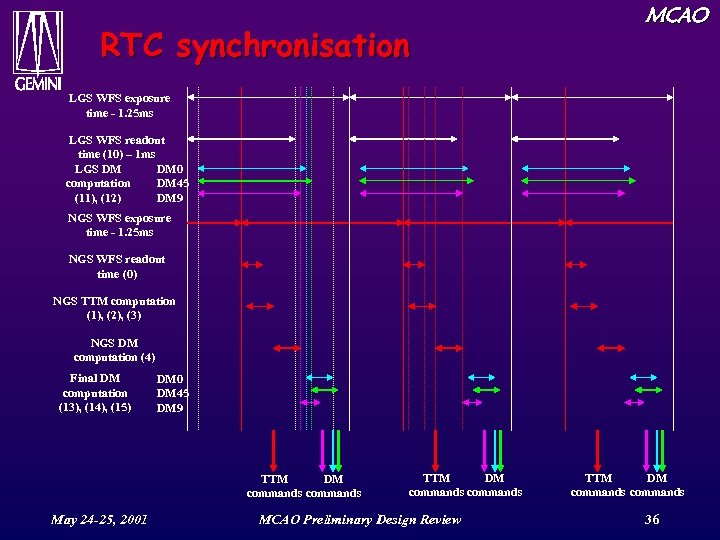

RTC synchronisation MCAO LGS WFS exposure time - 1. 25 ms LGS WFS readout time (10) – 1 ms LGS DM DM 0 computation DM 45 (11), (12) DM 9 NGS WFS exposure time - 1. 25 ms NGS WFS readout time (0) NGS TTM computation (1), (2), (3) NGS DM computation (4) Final DM computation (13), (14), (15) DM 0 DM 45 DM 9 TTM DM commands May 24 -25, 2001 TTM DM commands MCAO Preliminary Design Review TTM DM commands 36

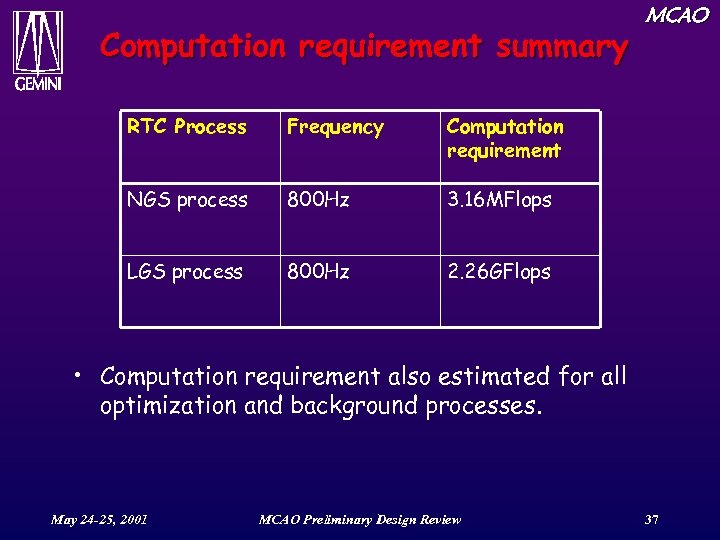

Computation requirement summary RTC Process Frequency Computation requirement NGS process 800 Hz 3. 16 MFlops LGS process 800 Hz MCAO 2. 26 GFlops • Computation requirement also estimated for all optimization and background processes. May 24 -25, 2001 MCAO Preliminary Design Review 37

RTC architecture MCAO • Since the Co. DR, 2 actions: – a VSS 4 Synergy Micro Systems board a VME 64 back plane has been purchased: VME DSP-Quad PPC 7400@433 Mhz, 256 Mb, 8 Mb Backside Cache (2: 1 ratio), VME 64 x. Benchmarks are right now performed by HIA to assess the suitability of this board. – contract some vendors to study other architectures for our requirements. Two vendors have been selectioned : • The Optical Science Company (t. OSC), located in Anaheim-California, • SHAKTIWARE, located in Marseille France. May 24 -25, 2001 MCAO Preliminary Design Review 38

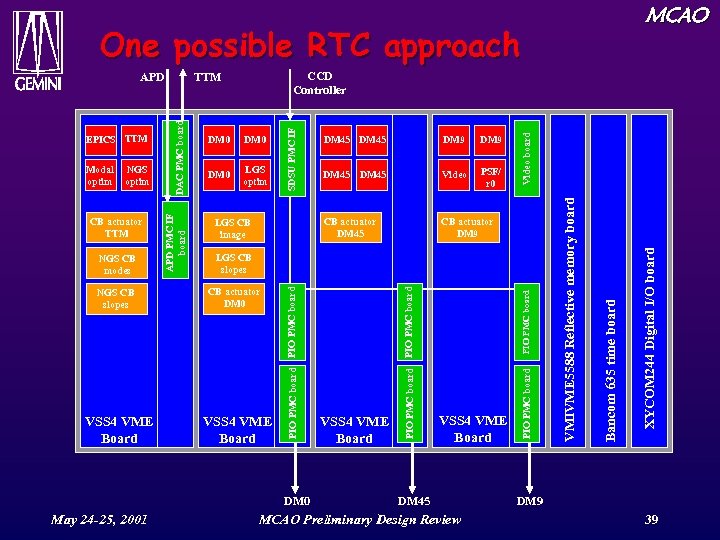

MCAO One possible RTC approach LGS CB slopes VSS 4 VME Board PIO PMC board CB actuator DM 0 VSS 4 VME Board DM 45 MCAO Preliminary Design Review XYCOM 244 Digital I/O board CB actuator DM 9 Bancom 635 time board PSF/ r 0 Video board SDSU PMC IF Video DM 45 CB actuator DM 45 LGS CB image DM 0 May 24 -25, 2001 DM 45 VMIVME 5588 Reflective memory board VSS 4 VME Board DM 9 PIO PMC board NGS CB slopes LGS optim DM 9 PIO PMC board NGS CB modes DM 0 DM 45 PIO PMC board CB actuator TTM DM 0 PIO PMC board NGS optim DM 0 PIO PMC board Modal optim APD PMC IF board EPICS TTM CCD Controller TTM DAC PMC board APD DM 9 39

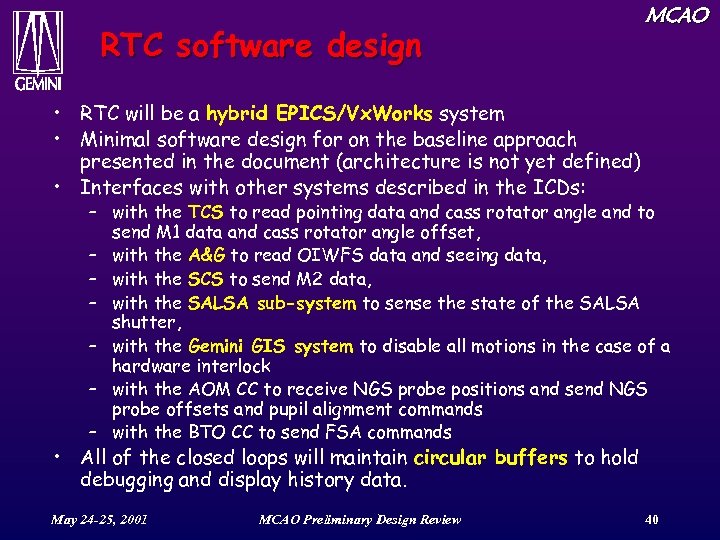

RTC software design MCAO • RTC will be a hybrid EPICS/Vx. Works system • Minimal software design for on the baseline approach presented in the document (architecture is not yet defined) • Interfaces with other systems described in the ICDs: – with the TCS to read pointing data and cass rotator angle and to send M 1 data and cass rotator angle offset, – with the A&G to read OIWFS data and seeing data, – with the SCS to send M 2 data, – with the SALSA sub-system to sense the state of the SALSA shutter, – with the Gemini GIS system to disable all motions in the case of a hardware interlock – with the AOM CC to receive NGS probe positions and send NGS probe offsets and pupil alignment commands – with the BTO CC to send FSA commands • All of the closed loops will maintain circular buffers to hold debugging and display history data. May 24 -25, 2001 MCAO Preliminary Design Review 40

MCAO PDR Agenda Friday, 5/25 0800 Laser System 0900 CTIO Sodium Studies 0915 Control System 0945 Break 1000 RTC Electronics 1045 Safety System 1100 Availability analysis 1130 Closed vendor Sessions 1200 Lunch May 24 -25, 2001 1300 1400 1700 1800 Cost and schedule Committee session Committee report Adjourn MCAO Preliminary Design Review 41

RTC benchmark and studies MCAO • VSS 4 benchmark: – linux installed – Benchmark in progress. First results presented by Les Saddlemyer – HIA • t. OSC study: – Investigate how VME/PCI architectures based on SHARC, Power. PC G 4 processors associated with floating point/fixed point processing will fully conform the MCAO requirements. – Draft report delivered for the PDR and results presented now by Steve Brown • SHAKTIWARE study (Joint funding Gemini and ESO): – Investigate the different processors (DSP, PPC and FGPA) as well as COTS boards which will fully meet the MCAO requirements – Final report delivered for the PDR and results presented now by Didier Rabaud May 24 -25, 2001 MCAO Preliminary Design Review 42

7fcc26a3dd608cbd8a110f20da4feb23.ppt