76c96bda0a82c0410d6cecd89e9125ee.ppt

- Количество слайдов: 26

MAPS ECAL Si. D Workshop RAL 14 -16 Apr 2008 Nigel Watson Birmingham University < Technical Status < Future Plans < Summary For the CALICE MAPS group J. P. Crooks, M. M. Stanitzki, K. D. Stefanov, R. Turchetta, M. Tyndel, E. G. Villani (STFC-RAL) J. A. Ballin, P. D. Dauncey, A. -M. Magnan, M. Noy (Imperial) Y. Mikami, O. D. Miller, Si. D Workshop, RAL, 15 -Apr-2008 V. Rajovic, NKW, J. A. Wilson (Birmingham) Nigel Watson / Birmingham

MAPS ECAL Si. D Workshop RAL 14 -16 Apr 2008 Nigel Watson Birmingham University < Technical Status < Future Plans < Summary For the CALICE MAPS group J. P. Crooks, M. M. Stanitzki, K. D. Stefanov, R. Turchetta, M. Tyndel, E. G. Villani (STFC-RAL) J. A. Ballin, P. D. Dauncey, A. -M. Magnan, M. Noy (Imperial) Y. Mikami, O. D. Miller, Si. D Workshop, RAL, 15 -Apr-2008 V. Rajovic, NKW, J. A. Wilson (Birmingham) Nigel Watson / Birmingham

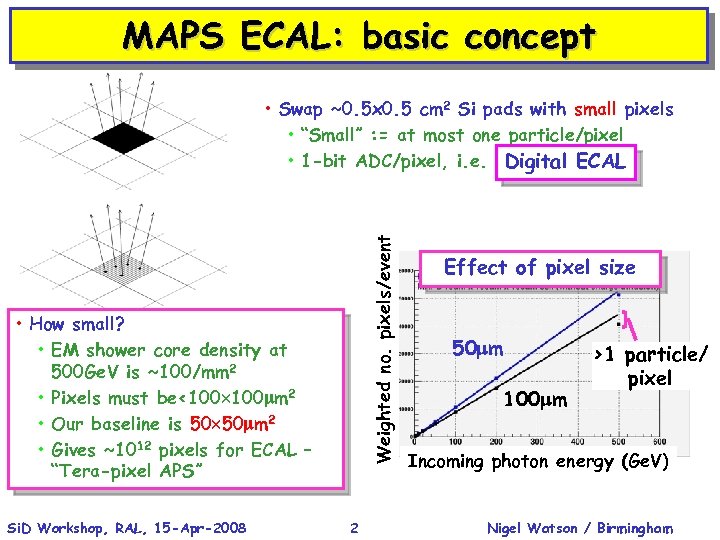

MAPS ECAL: basic concept Weighted no. pixels/event • Swap ~0. 5 x 0. 5 cm 2 Si pads with small pixels • “Small” : = at most one particle/pixel • 1 -bit ADC/pixel, i. e. Digital ECAL • How small? • EM shower core density at 500 Ge. V is ~100/mm 2 • Pixels must be<100 100 mm 2 • Our baseline is 50 50 mm 2 • Gives ~1012 pixels for ECAL – “Tera-pixel APS” Si. D Workshop, RAL, 15 -Apr-2008 2 Effect of pixel size 50 mm 100 mm >1 particle/ pixel Incoming photon energy (Ge. V) Nigel Watson / Birmingham

MAPS ECAL: basic concept Weighted no. pixels/event • Swap ~0. 5 x 0. 5 cm 2 Si pads with small pixels • “Small” : = at most one particle/pixel • 1 -bit ADC/pixel, i. e. Digital ECAL • How small? • EM shower core density at 500 Ge. V is ~100/mm 2 • Pixels must be<100 100 mm 2 • Our baseline is 50 50 mm 2 • Gives ~1012 pixels for ECAL – “Tera-pixel APS” Si. D Workshop, RAL, 15 -Apr-2008 2 Effect of pixel size 50 mm 100 mm >1 particle/ pixel Incoming photon energy (Ge. V) Nigel Watson / Birmingham

New since Jan. workshop?

New since Jan. workshop?

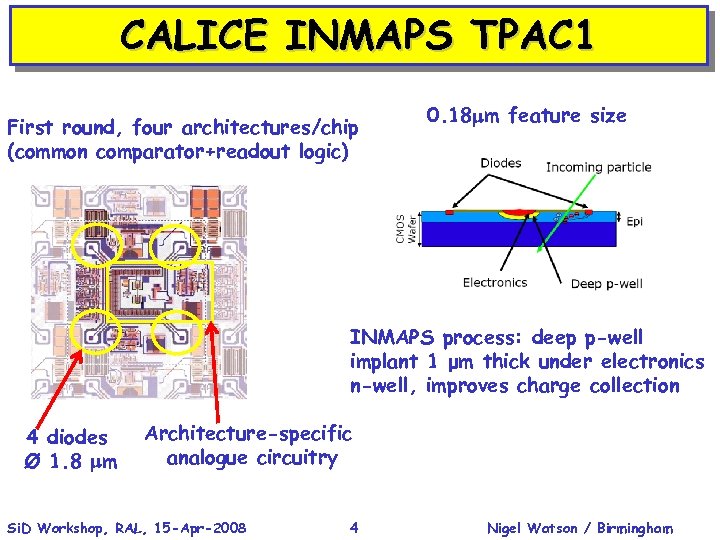

CALICE INMAPS TPAC 1 First round, four architectures/chip (common comparator+readout logic) 0. 18 mm feature size INMAPS process: deep p-well implant 1 μm thick under electronics n-well, improves charge collection 4 diodes Ø 1. 8 mm Architecture-specific analogue circuitry Si. D Workshop, RAL, 15 -Apr-2008 4 Nigel Watson / Birmingham

CALICE INMAPS TPAC 1 First round, four architectures/chip (common comparator+readout logic) 0. 18 mm feature size INMAPS process: deep p-well implant 1 μm thick under electronics n-well, improves charge collection 4 diodes Ø 1. 8 mm Architecture-specific analogue circuitry Si. D Workshop, RAL, 15 -Apr-2008 4 Nigel Watson / Birmingham

The CALICE TPAC 1 < 50 x 50 mm cell size < Comparator per pixel < Capability to mask individual pixels < 4 Diodes for ~uniform response w. r. t threshold < 13 bit time stamp (>8 k bunches individually tagged) < Hit buffering for entire bunch train (~ILC occupancy) < Threshold adjustment for each pixel < Usage of INMAPS (deep-p well) process [Marcel Stanitzki] Si. D Workshop, RAL, 15 -Apr-2008 5 Nigel Watson / Birmingham

The CALICE TPAC 1 < 50 x 50 mm cell size < Comparator per pixel < Capability to mask individual pixels < 4 Diodes for ~uniform response w. r. t threshold < 13 bit time stamp (>8 k bunches individually tagged) < Hit buffering for entire bunch train (~ILC occupancy) < Threshold adjustment for each pixel < Usage of INMAPS (deep-p well) process [Marcel Stanitzki] Si. D Workshop, RAL, 15 -Apr-2008 5 Nigel Watson / Birmingham

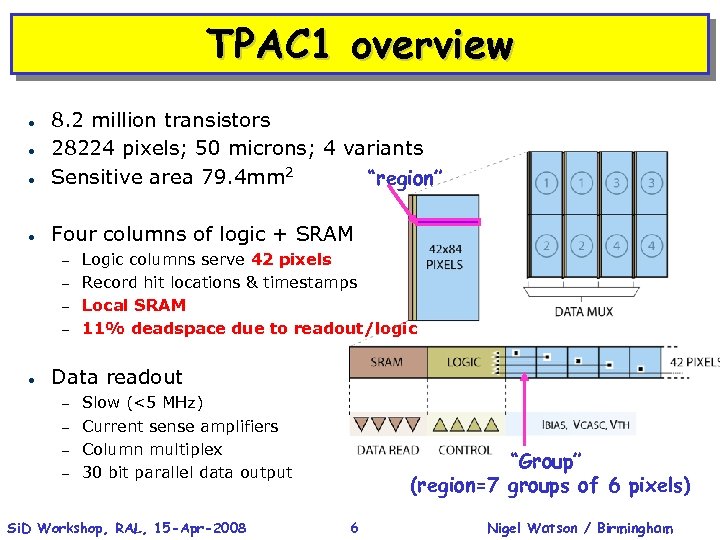

TPAC 1 overview 8. 2 million transistors 28224 pixels; 50 microns; 4 variants Sensitive area 79. 4 mm 2 “region” Four columns of logic + SRAM Logic columns serve 42 pixels Record hit locations & timestamps Local SRAM 11% deadspace due to readout/logic Data readout Slow (<5 MHz) Current sense amplifiers Column multiplex 30 bit parallel data output Si. D Workshop, RAL, 15 -Apr-2008 “Group” (region=7 groups of 6 pixels) 6 Nigel Watson / Birmingham

TPAC 1 overview 8. 2 million transistors 28224 pixels; 50 microns; 4 variants Sensitive area 79. 4 mm 2 “region” Four columns of logic + SRAM Logic columns serve 42 pixels Record hit locations & timestamps Local SRAM 11% deadspace due to readout/logic Data readout Slow (<5 MHz) Current sense amplifiers Column multiplex 30 bit parallel data output Si. D Workshop, RAL, 15 -Apr-2008 “Group” (region=7 groups of 6 pixels) 6 Nigel Watson / Birmingham

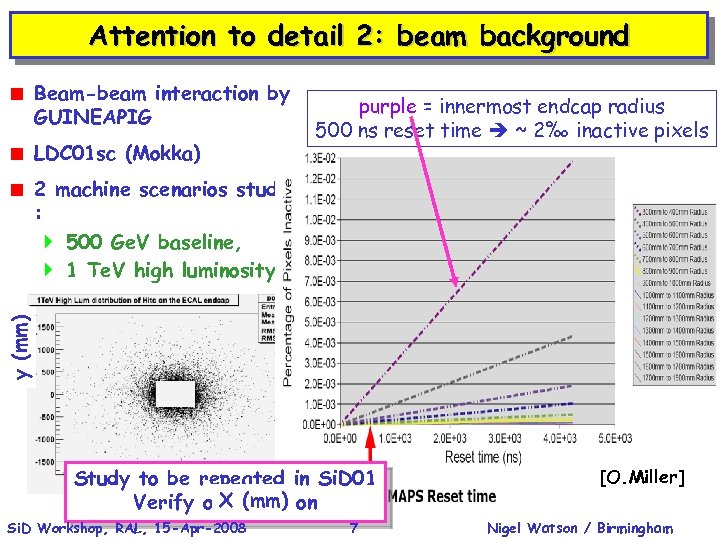

Attention to detail 2: beam background < Beam-beam interaction by GUINEAPIG < LDC 01 sc (Mokka) purple = innermost endcap radius 500 ns reset time ~ 2‰ inactive pixels y (mm) < 2 machine scenarios studied : } 500 Ge. V baseline, } 1 Te. V high luminosity Study to be repeated in Si. D 01 X (mm) Verify optimisation Si. D Workshop, RAL, 15 -Apr-2008 7 [O. Miller] Nigel Watson / Birmingham

Attention to detail 2: beam background < Beam-beam interaction by GUINEAPIG < LDC 01 sc (Mokka) purple = innermost endcap radius 500 ns reset time ~ 2‰ inactive pixels y (mm) < 2 machine scenarios studied : } 500 Ge. V baseline, } 1 Te. V high luminosity Study to be repeated in Si. D 01 X (mm) Verify optimisation Si. D Workshop, RAL, 15 -Apr-2008 7 [O. Miller] Nigel Watson / Birmingham

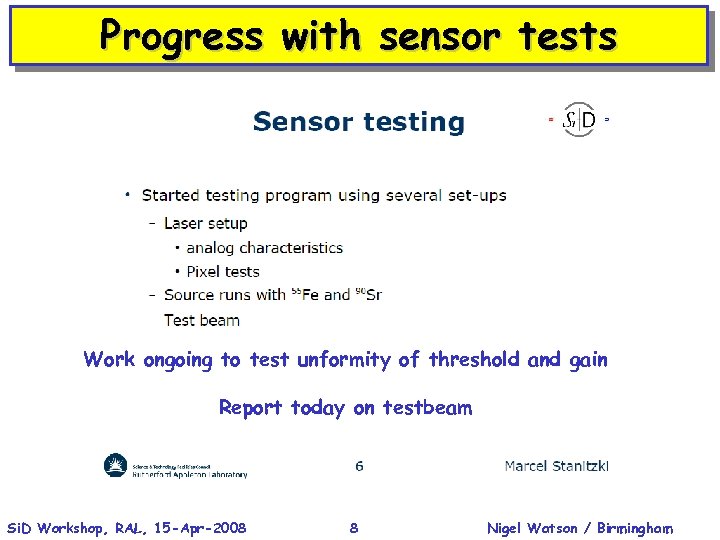

Progress with sensor tests Work ongoing to test unformity of threshold and gain Report today on testbeam Si. D Workshop, RAL, 15 -Apr-2008 8 Nigel Watson / Birmingham

Progress with sensor tests Work ongoing to test unformity of threshold and gain Report today on testbeam Si. D Workshop, RAL, 15 -Apr-2008 8 Nigel Watson / Birmingham

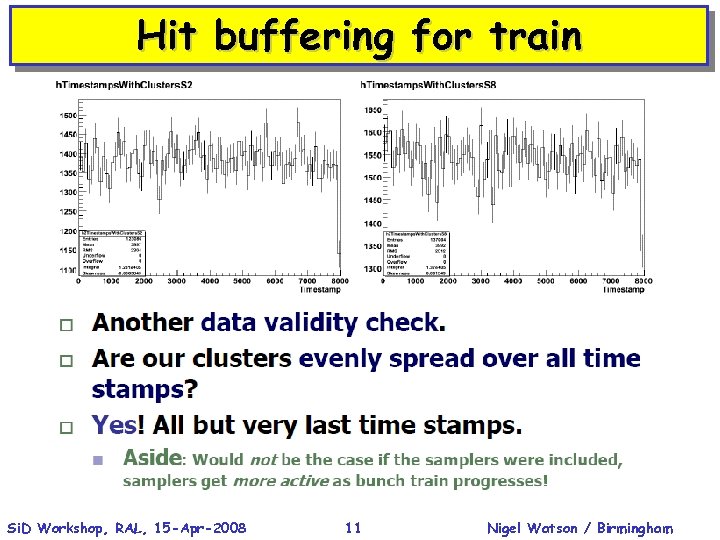

Hit buffering for train Si. D Workshop, RAL, 15 -Apr-2008 11 Nigel Watson / Birmingham

Hit buffering for train Si. D Workshop, RAL, 15 -Apr-2008 11 Nigel Watson / Birmingham

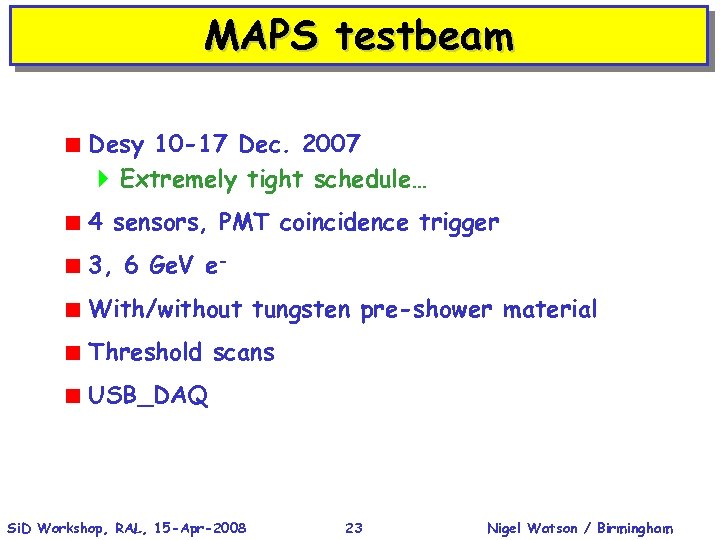

MAPS testbeam < Desy 10 -17 Dec. 2007 } Extremely tight schedule… < 4 sensors, PMT coincidence trigger < 3, 6 Ge. V e< With/without tungsten pre-shower material < Threshold scans < USB_DAQ Si. D Workshop, RAL, 15 -Apr-2008 23 Nigel Watson / Birmingham

MAPS testbeam < Desy 10 -17 Dec. 2007 } Extremely tight schedule… < 4 sensors, PMT coincidence trigger < 3, 6 Ge. V e< With/without tungsten pre-shower material < Threshold scans < USB_DAQ Si. D Workshop, RAL, 15 -Apr-2008 23 Nigel Watson / Birmingham

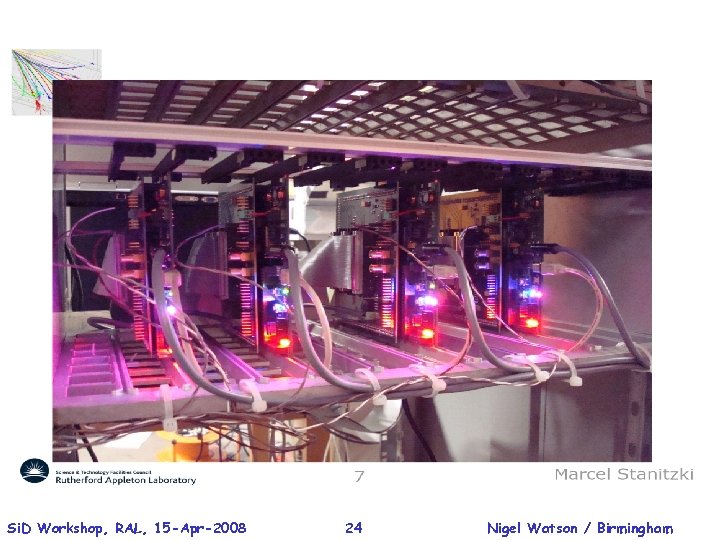

Si. D Workshop, RAL, 15 -Apr-2008 24 Nigel Watson / Birmingham

Si. D Workshop, RAL, 15 -Apr-2008 24 Nigel Watson / Birmingham

Si. D Workshop, RAL, 15 -Apr-2008 25 Nigel Watson / Birmingham

Si. D Workshop, RAL, 15 -Apr-2008 25 Nigel Watson / Birmingham

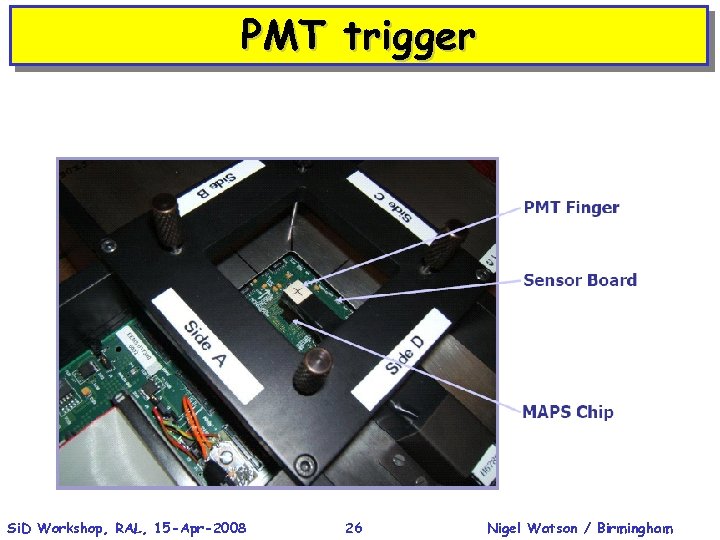

PMT trigger Si. D Workshop, RAL, 15 -Apr-2008 26 Nigel Watson / Birmingham

PMT trigger Si. D Workshop, RAL, 15 -Apr-2008 26 Nigel Watson / Birmingham

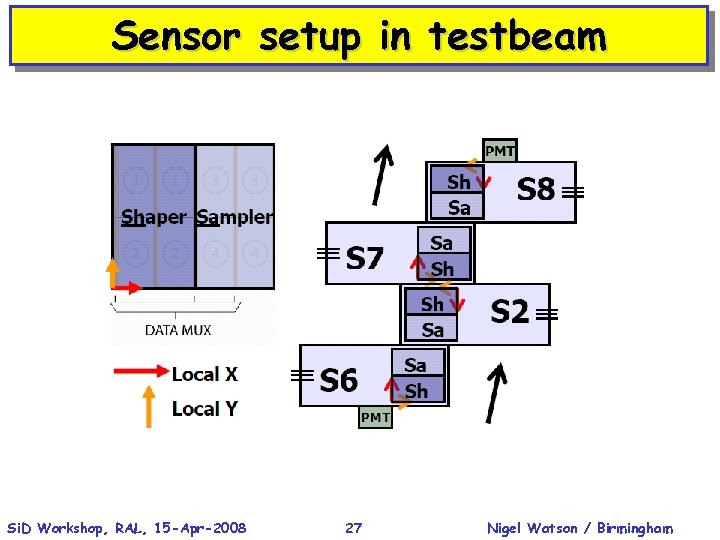

Sensor setup in testbeam Si. D Workshop, RAL, 15 -Apr-2008 27 Nigel Watson / Birmingham

Sensor setup in testbeam Si. D Workshop, RAL, 15 -Apr-2008 27 Nigel Watson / Birmingham

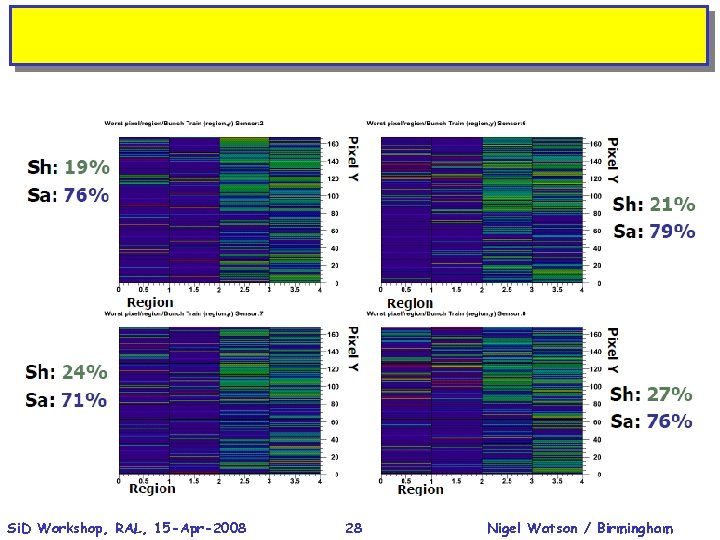

Si. D Workshop, RAL, 15 -Apr-2008 28 Nigel Watson / Birmingham

Si. D Workshop, RAL, 15 -Apr-2008 28 Nigel Watson / Birmingham

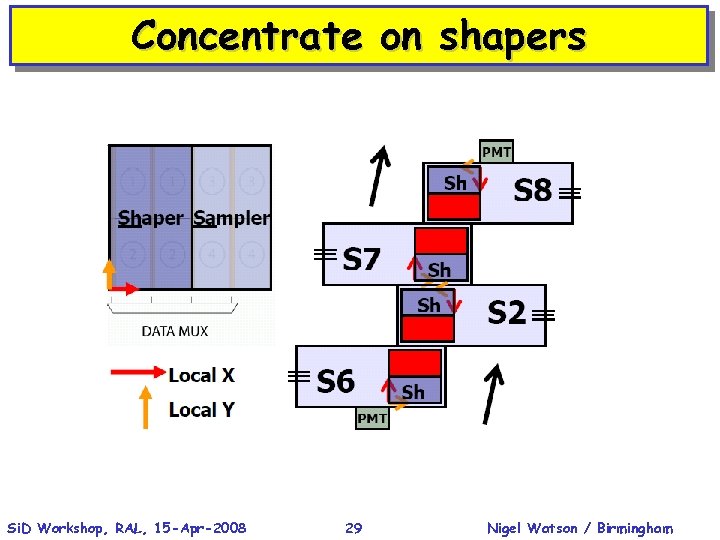

Concentrate on shapers Si. D Workshop, RAL, 15 -Apr-2008 29 Nigel Watson / Birmingham

Concentrate on shapers Si. D Workshop, RAL, 15 -Apr-2008 29 Nigel Watson / Birmingham

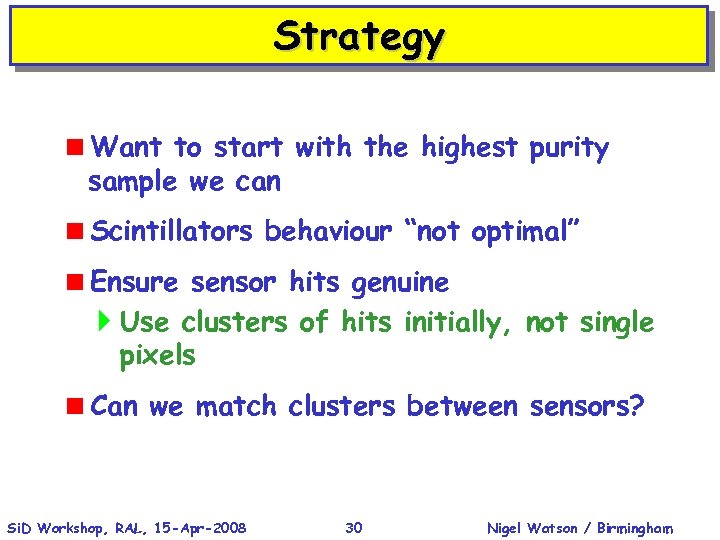

Strategy

Strategy

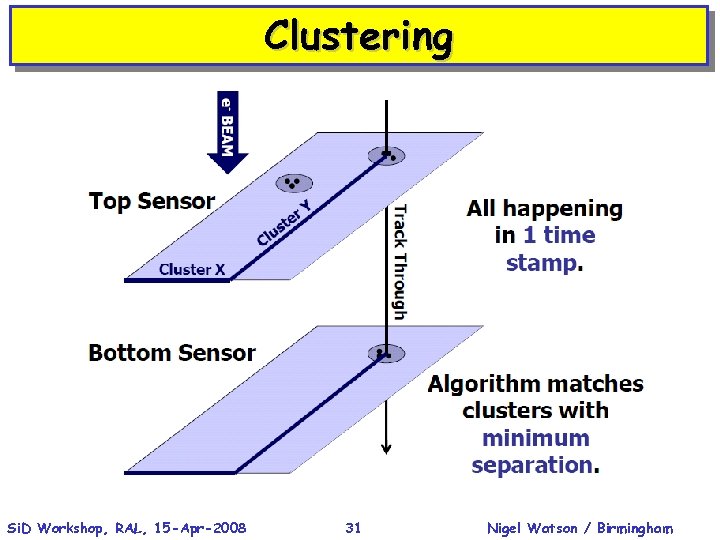

Clustering Si. D Workshop, RAL, 15 -Apr-2008 31 Nigel Watson / Birmingham

Clustering Si. D Workshop, RAL, 15 -Apr-2008 31 Nigel Watson / Birmingham

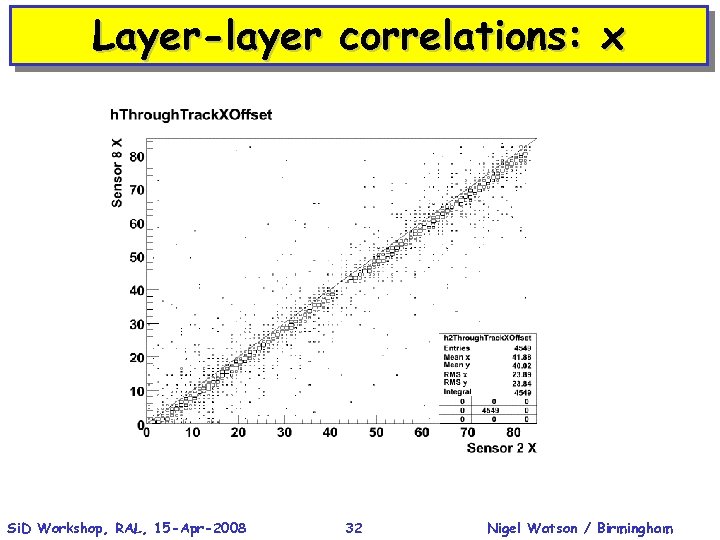

Layer-layer correlations: x Si. D Workshop, RAL, 15 -Apr-2008 32 Nigel Watson / Birmingham

Layer-layer correlations: x Si. D Workshop, RAL, 15 -Apr-2008 32 Nigel Watson / Birmingham

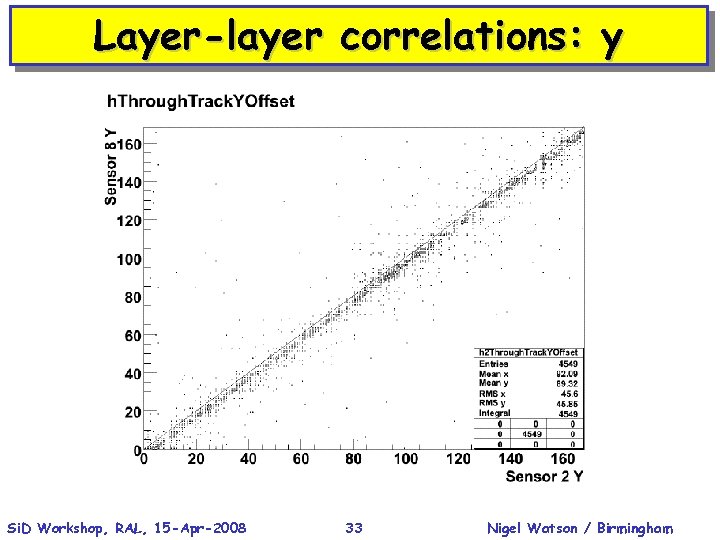

Layer-layer correlations: y Si. D Workshop, RAL, 15 -Apr-2008 33 Nigel Watson / Birmingham

Layer-layer correlations: y Si. D Workshop, RAL, 15 -Apr-2008 33 Nigel Watson / Birmingham

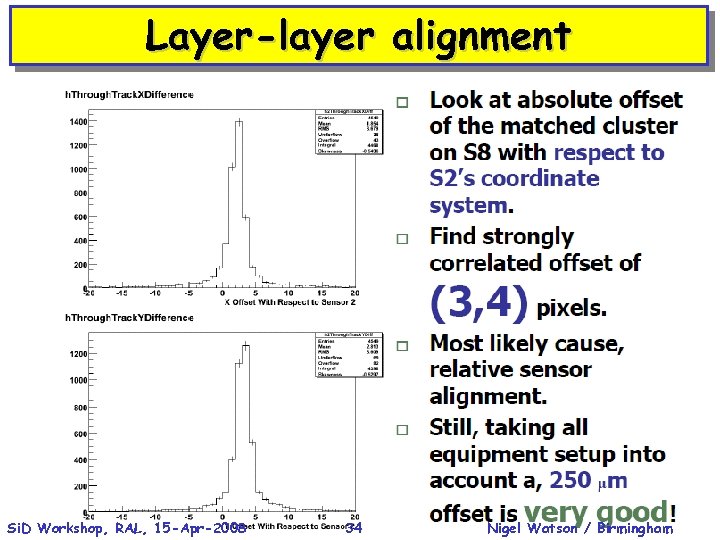

Layer-layer alignment Si. D Workshop, RAL, 15 -Apr-2008 34 Nigel Watson / Birmingham

Layer-layer alignment Si. D Workshop, RAL, 15 -Apr-2008 34 Nigel Watson / Birmingham

…and funding

…and funding

MAPS summary < Concept of CMOS MAPS digital ECAL for ILC } Multi-vendors, cost/performance gains < New INMAPS deep p-well process (optimise charge collection) < Four architectures for sensor on first chips, delivered to RAL Jul 2007 < Tests of sensor performance in progress: sources, charge diffusion, cosmics, testbeam < Physics benchmark studies, compare MAPS vs. analogue Si-W designs } In framework of Si. D and IDC detector concepts Si. D Workshop, RAL, 15 -Apr-2008 36 Nigel Watson / Birmingham

MAPS summary < Concept of CMOS MAPS digital ECAL for ILC } Multi-vendors, cost/performance gains < New INMAPS deep p-well process (optimise charge collection) < Four architectures for sensor on first chips, delivered to RAL Jul 2007 < Tests of sensor performance in progress: sources, charge diffusion, cosmics, testbeam < Physics benchmark studies, compare MAPS vs. analogue Si-W designs } In framework of Si. D and IDC detector concepts Si. D Workshop, RAL, 15 -Apr-2008 36 Nigel Watson / Birmingham

Summary < MAPS ECAL: alternative to baseline design (analogue Si. W) } Multi-vendors, cost/performance gains } New INMAPS deep p-well process (optimise charge collection) } Four architectures for sensor on first chips } Tests of sensor performance ongoing } Physics benchmark studies with MAPS ECAL to evaluate performance relative to standard analogue Si-W designs, for both Si. D (and ILD) detector concepts < Future plans } Systematic studies of pixel to pixel gain and threshold variations } Absolute gain calibration } Second sensor… Si. D Workshop, RAL, 15 -Apr-2008 37 Nigel Watson / Birmingham

Summary < MAPS ECAL: alternative to baseline design (analogue Si. W) } Multi-vendors, cost/performance gains } New INMAPS deep p-well process (optimise charge collection) } Four architectures for sensor on first chips } Tests of sensor performance ongoing } Physics benchmark studies with MAPS ECAL to evaluate performance relative to standard analogue Si-W designs, for both Si. D (and ILD) detector concepts < Future plans } Systematic studies of pixel to pixel gain and threshold variations } Absolute gain calibration } Second sensor… Si. D Workshop, RAL, 15 -Apr-2008 37 Nigel Watson / Birmingham

Backup slides… Si. D Workshop, RAL, 15 -Apr-2008 38 Nigel Watson / Birmingham

Backup slides… Si. D Workshop, RAL, 15 -Apr-2008 38 Nigel Watson / Birmingham

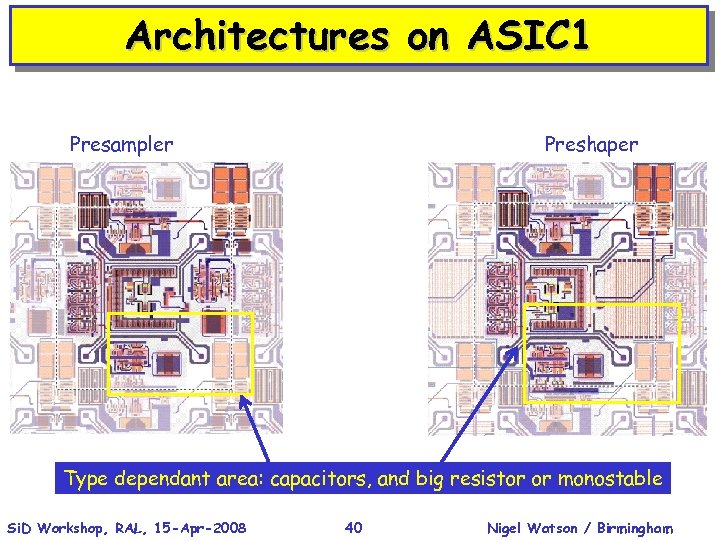

Architectures on ASIC 1 Presampler Preshaper Type dependant area: capacitors, and big resistor or monostable Si. D Workshop, RAL, 15 -Apr-2008 40 Nigel Watson / Birmingham

Architectures on ASIC 1 Presampler Preshaper Type dependant area: capacitors, and big resistor or monostable Si. D Workshop, RAL, 15 -Apr-2008 40 Nigel Watson / Birmingham