Лит. обзор КР 580 (МП ВМ 80 А) 1) Романов Л. Г. Микропроцессорная техника. Часть 1. Конспект лекций. ЗГИА, 2005. КР 1821 (МП ВМ 8085 А) 1) Романов Л. Г. Микропроцессорная техника. Часть 1. Конспект лекций. ЗГИА, 2005. К 1810 (МП ВМ 86/ВМ 88) 1) Романов Л. Г. Микропроцессорная техника. Часть 2. Конспект лекций. ЗГИА, 2005. 2) Казаринов Ю. М. и др. Микропроцессорный комплект К 1810. Структура, программирование, применение. Справочная книга. М. : Высшая школа, 1990. 3) Григорьев В. Л. Программирование однокристальных МП. – М. : Энергоатомиздат, 1987. К 1816 (ВЕ 48, ВЕ 31, ВЕ 51) 1) Романов Л. Г. Микропроцессорная техника. Часть 1. Конспект лекций. ЗГИА, 2005. 2) Проектирование цифровых устройств на однокристальных микроконтроллерах / В. В. Сташин, А. В. Урусов, О. Ф. Малогонцева. – М. : Энергоатомиздат, 1990. 3) Боборыкин А. В. Однокристальные микро. ЭВМ. М. : МИКАП, 1994. – 400 с. Курсовое проектирование 1) Романов Л. Г. , Кузнєцов Д. О. Мікропроцесорна техніка. Методичні вказівки до виконання курсового проекту, практичних занять та лабораторних робіт. – Запоріжжя, 2008. 1

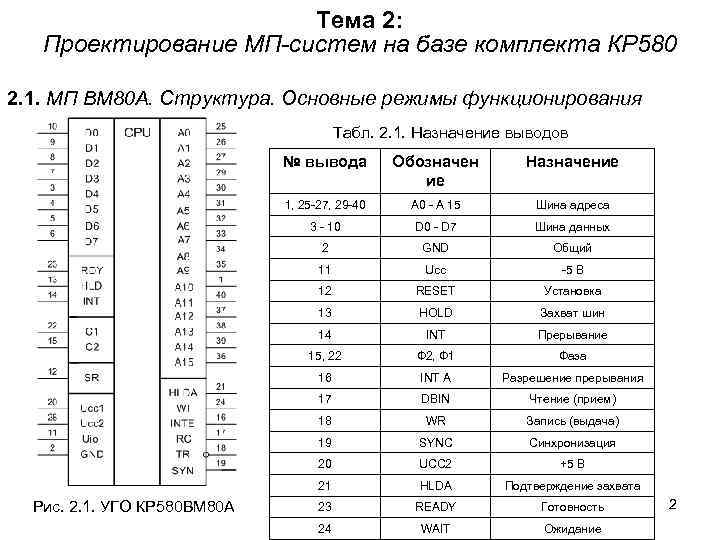

Тема 2: Проектирование МП-систем на базе комплекта КР 580 2. 1. МП ВМ 80 А. Структура. Основные режимы функционирования Табл. 2. 1. Назначение выводов № вывода Назначение 1, 25 27, 29 40 А 0 А 15 Шина адреса 3 10 D 0 D 7 Шина данных 2 GND Общий 11 Ucc 5 В 12 RESET Установка 13 HOLD Захват шин 14 INT Прерывание 15, 22 Ф 2, Ф 1 Фаза 16 INT A Разрешение прерывания 17 DBIN Чтение (прием) 18 WR Запись (выдача) 19 SYNC Синхронизация 20 UCC 2 +5 В 21 Рис. 2. 1. УГО КР 580 ВМ 80 А Обозначен ие HLDA Подтверждение захвата 23 READY Готовность 24 WAIT Ожидание 2

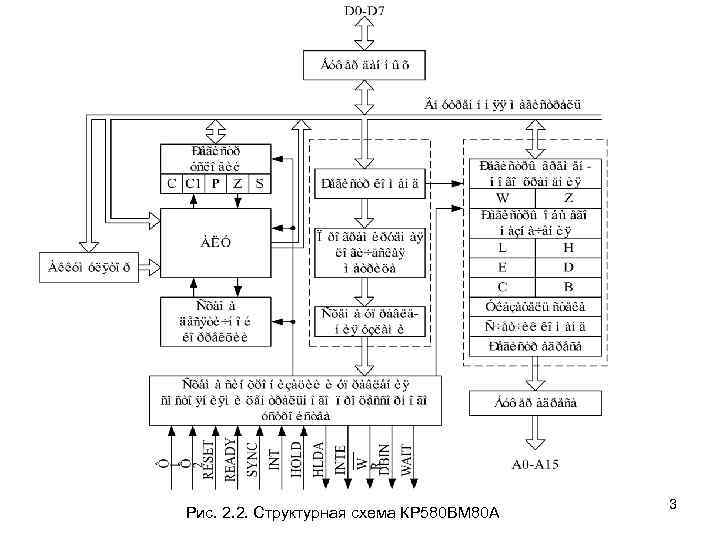

Рис. 2. 2. Структурная схема КР 580 ВМ 80 А 3

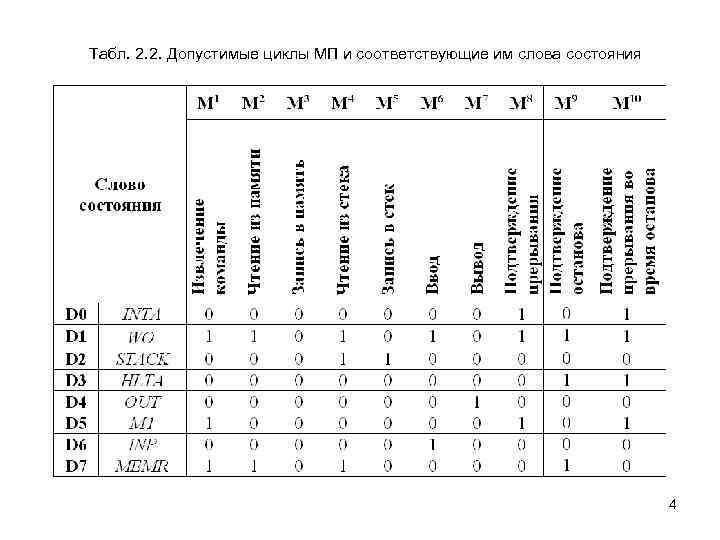

Табл. 2. 2. Допустимые циклы МП и соответствующие им слова состояния 4

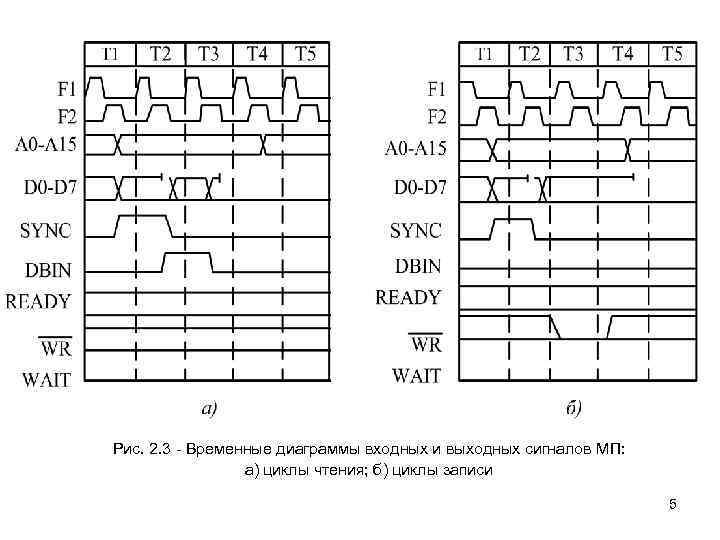

Рис. 2. 3 Временные диаграммы входных и выходных сигналов МП: а) циклы чтения; б) циклы записи 5

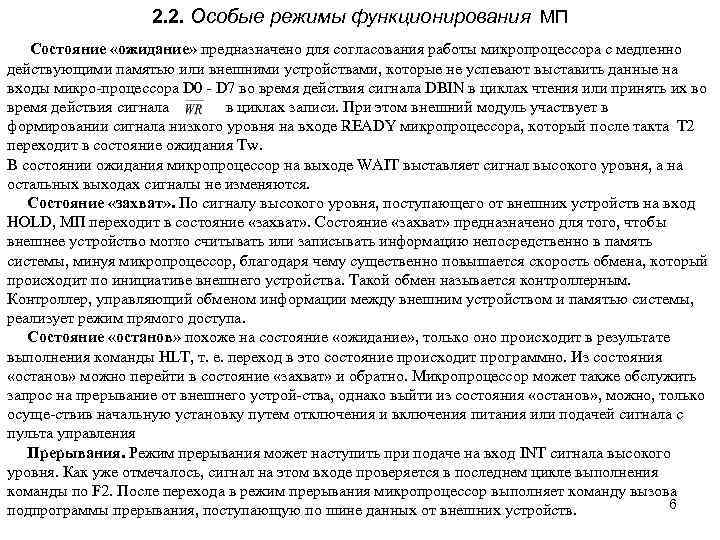

2. 2. Особые режимы функционирования МП Состояние «ожидание» предназначено для согласования работы микропроцессора с медленно действующими памятью или внешними устройствами, которые не успевают выставить данные на входы микро процессора D 0 D 7 во время действия сигнала DBIN в циклах чтения или принять их во время действия сигнала в циклах записи. При этом внешний модуль участвует в формировании сигнала низкого уровня на входе READY микропроцессора, который после такта Т 2 переходит в состояние ожидания Тw. В состоянии ожидания микропроцессор на выходе WAIT выставляет сигнал высокого уровня, а на остальных выходах сигналы не изменяются. Состояние «захват» . По сигналу высокого уровня, поступающего от внешних устройств на вход HOLD, МП переходит в состояние «захват» . Состояние «захват» предназначено для того, чтобы внешнее устройство могло считывать или записывать информацию непосредственно в память системы, минуя микропроцессор, благодаря чему существенно повышается скорость обмена, который происходит по инициативе внешнего устройства. Такой обмен называется контроллерным. Контроллер, управляющий обменом информации между внешним устройством и памятью системы, реализует режим прямого доступа. Состояние «останов» похоже на состояние «ожидание» , только оно происходит в результате выполнения команды HLT, т. е. переход в это состояние происходит программно. Из состояния «останов» можно перейти в состояние «захват» и обратно. Микропроцессор может также обслужить запрос на прерывание от внешнего устрой ства, однако выйти из состояния «останов» , можно, только осуще ствив начальную установку путем отключения и включения питания или подачей сигнала с пульта управления Прерывания. Режим прерывания может наступить при подаче на вход INT сигнала высокого уровня. Как уже отмечалось, сигнал на этом входе проверяется в последнем цикле выполнения команды по F 2. После перехода в режим прерывания микропроцессор выполняет команду вызова 6 подпрограммы прерывания, поступающую по шине данных от внешних устройств.

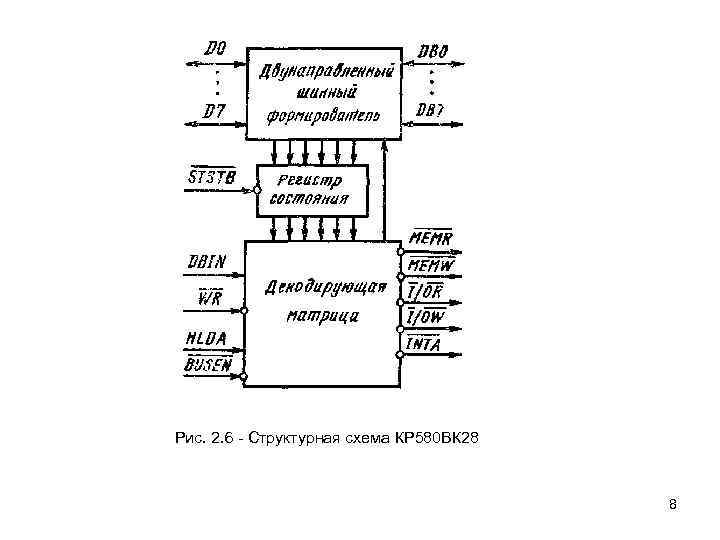

2. 3. Непрограммируемые интерфейсные БИС. Системные контроллер. Рис. 2. 5. Функциональная схема ШФ ВА 86 (а) и его условное гра фическое обозначение (б) Рис. 2. 4. Функциональная схема БР ИР 82 (а) и его условное графическое обозначение (б) 7

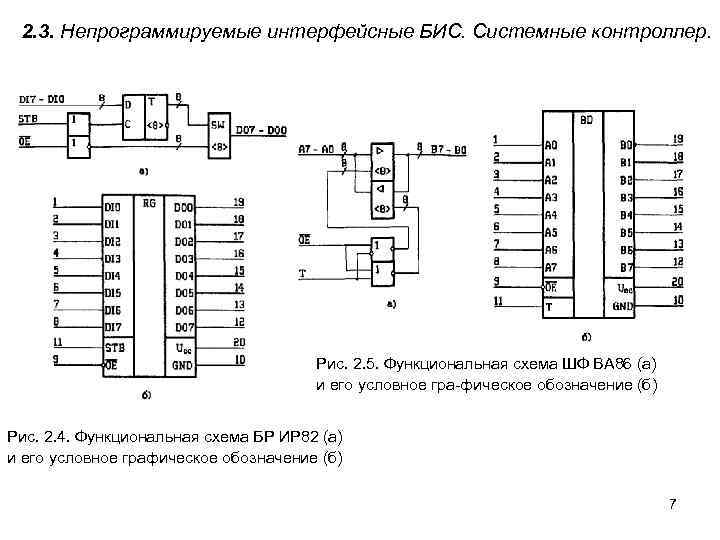

Риc. 2. 6 Структурная схема КР 580 ВК 28 8

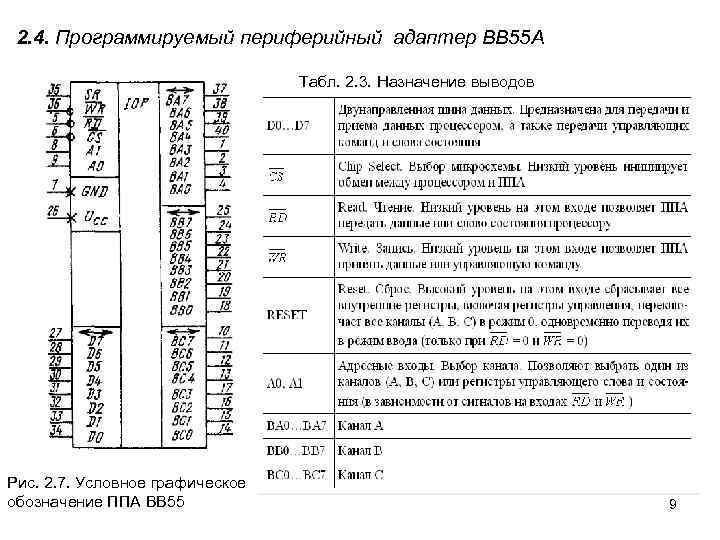

2. 4. Программируемый периферийный адаптер ВВ 55 А Табл. 2. 3. Назначение выводов Рис. 2. 7. Условное графическое обозначение ППА ВВ 55 9

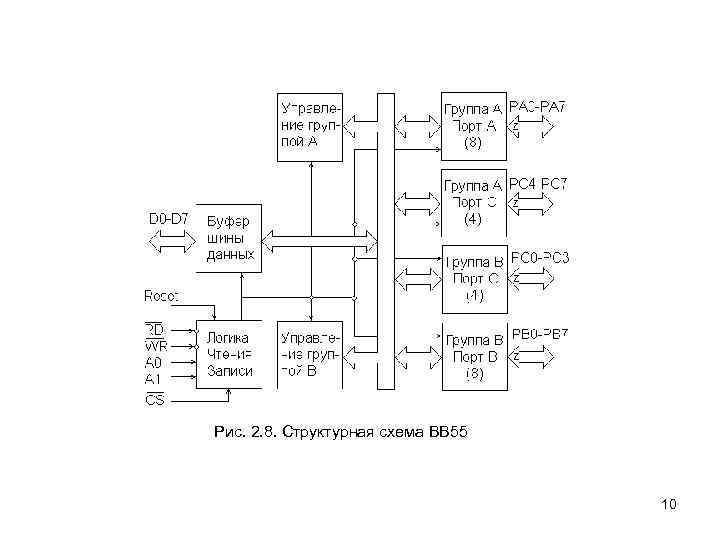

Рис. 2. 8. Структурная схема ВВ 55 10

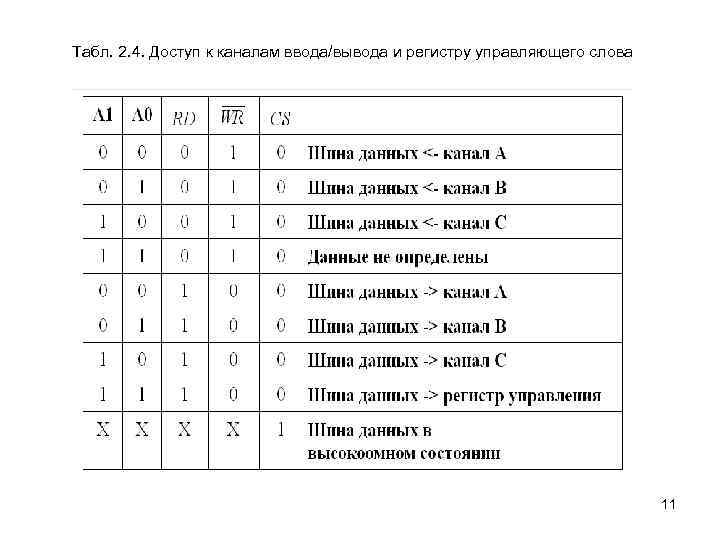

Табл. 2. 4. Доступ к каналам ввода/вывода и регистру управляющего слова 11

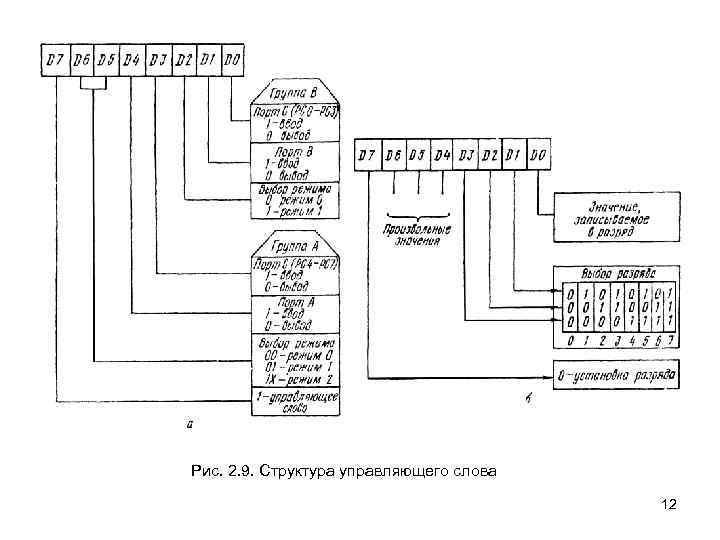

Рис. 2. 9. Структура управляющего слова 12

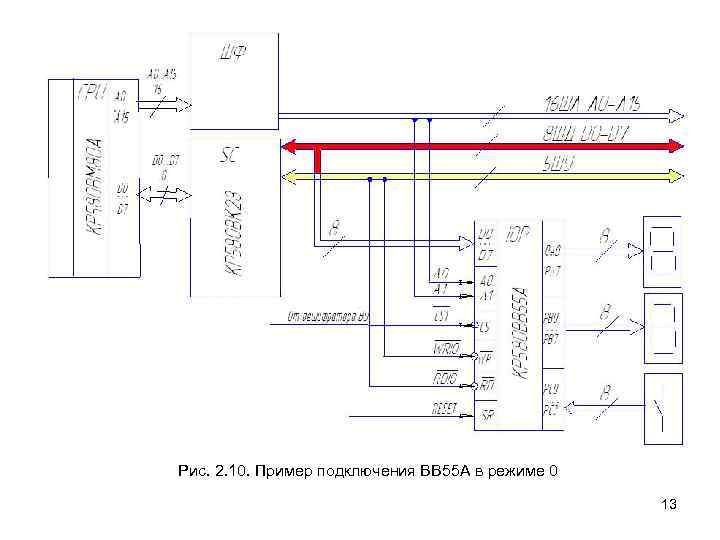

Рис. 2. 10. Пример подключения ВВ 55 А в режиме 0 13

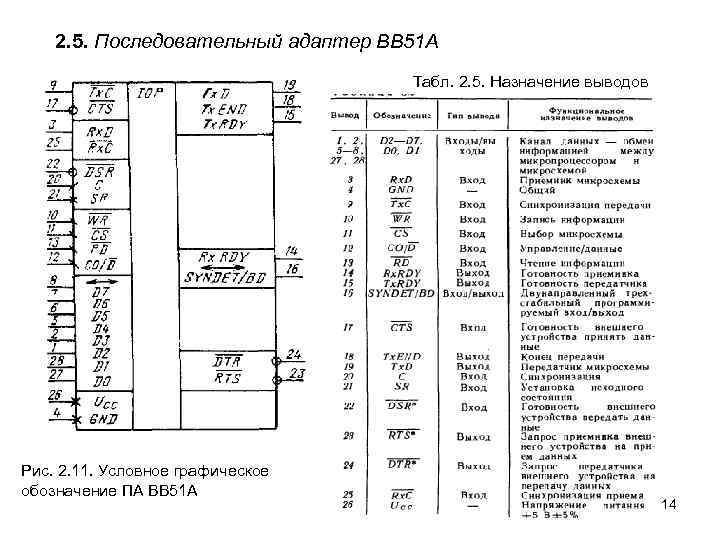

2. 5. Последовательный адаптер ВВ 51 А Табл. 2. 5. Назначение выводов Рис. 2. 11. Условное графическое обозначение ПА ВВ 51 А 14

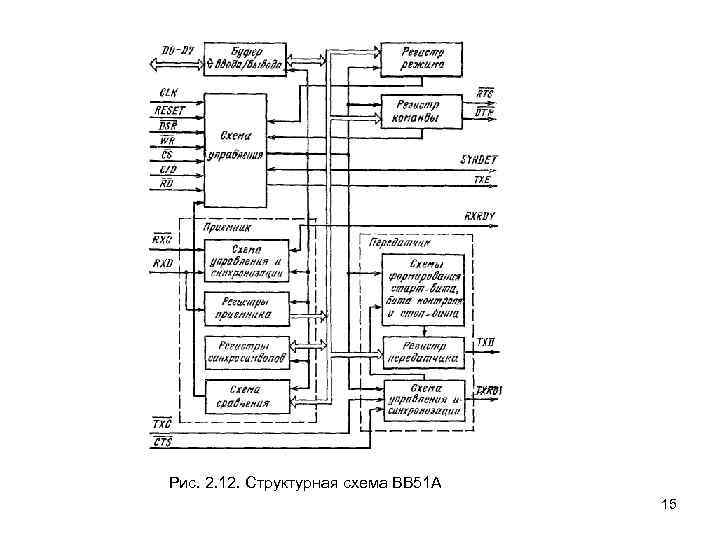

Рис. 2. 12. Структурная схема ВВ 51 А 15

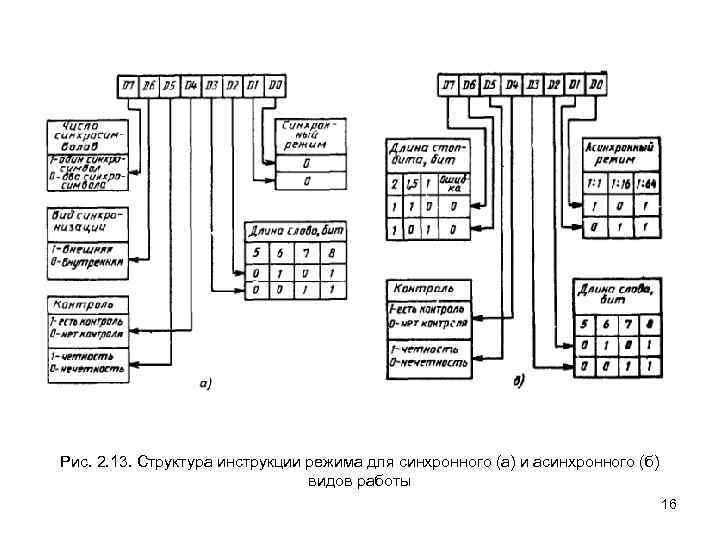

Рис. 2. 13. Структура инструкции режима для синхронного (а) и асинхронного (б) видов работы 16

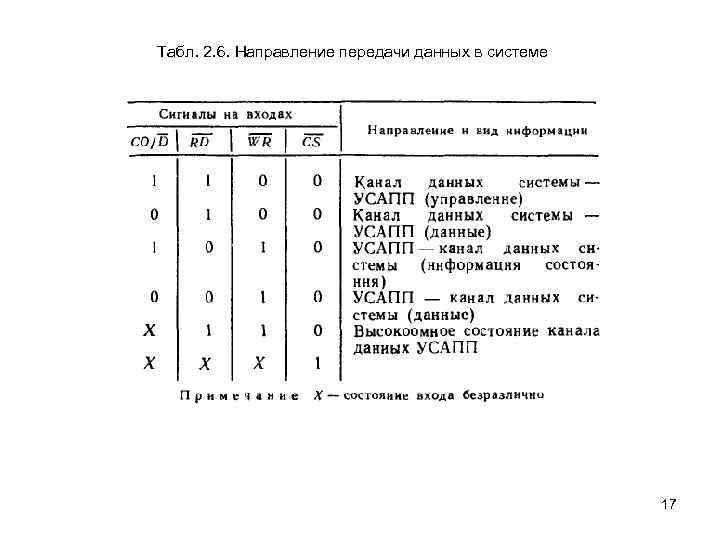

Табл. 2. 6. Направление передачи данных в системе 17

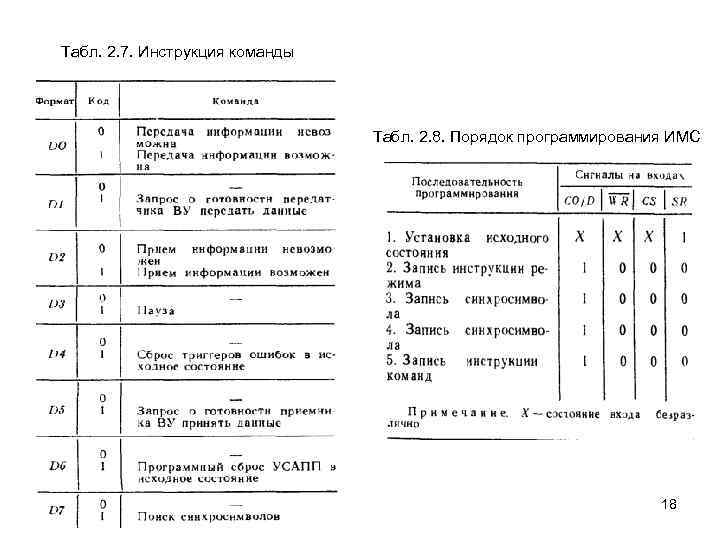

Табл. 2. 7. Инструкция команды Табл. 2. 8. Порядок программирования ИМС 18

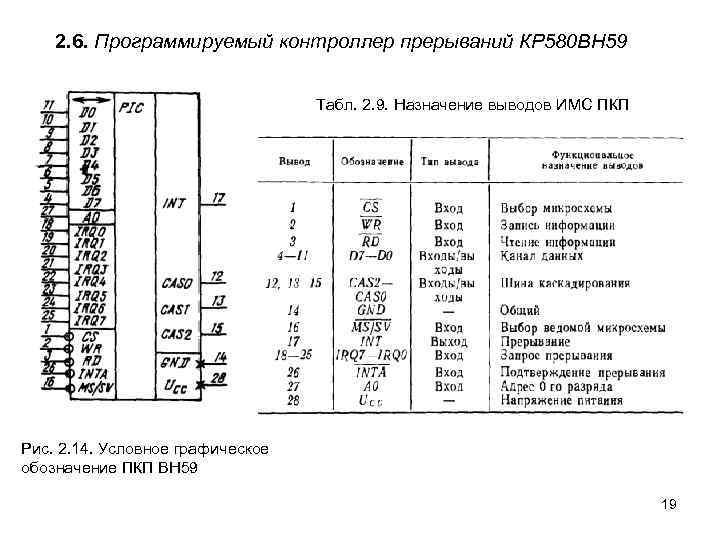

2. 6. Программируемый контроллер прерываний КР 580 ВН 59 Табл. 2. 9. Назначение выводов ИМС ПКП Рис. 2. 14. Условное графическое обозначение ПКП ВН 59 19

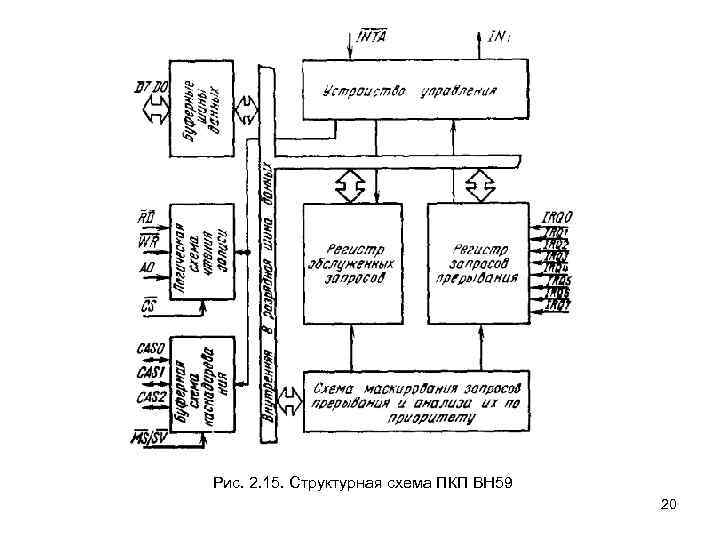

Рис. 2. 15. Структурная схема ПКП ВН 59 20

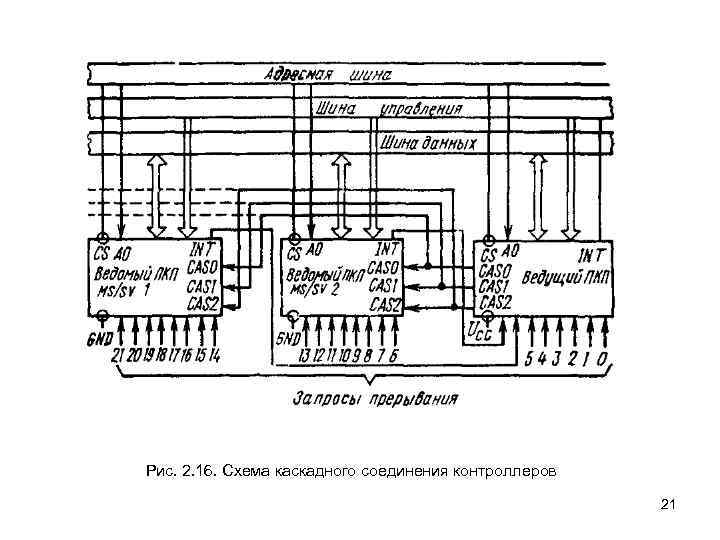

Рис. 2. 16. Схема каскадного соединения контроллеров 21

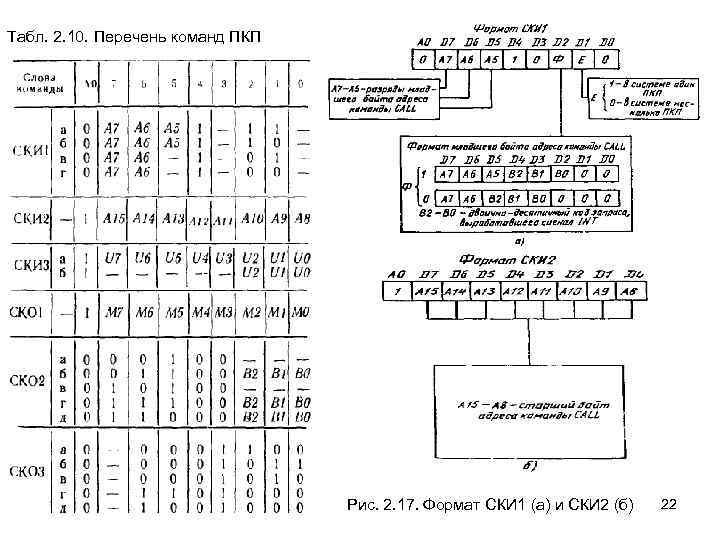

Табл. 2. 10. Перечень команд ПКП Рис. 2. 17. Формат СКИ 1 (а) и СКИ 2 (б) 22

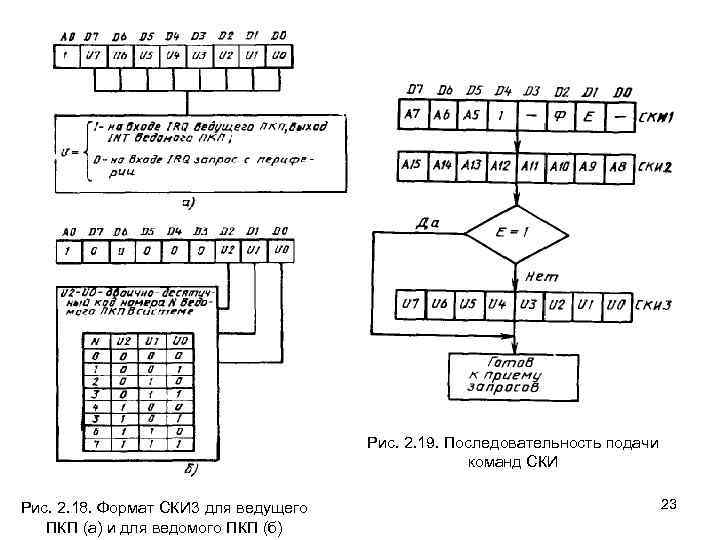

Рис. 2. 19. Последовательность подачи команд СКИ Рис. 2. 18. Формат СКИ 3 для ведущего ПКП (а) и для ведомого ПКП (б) 23

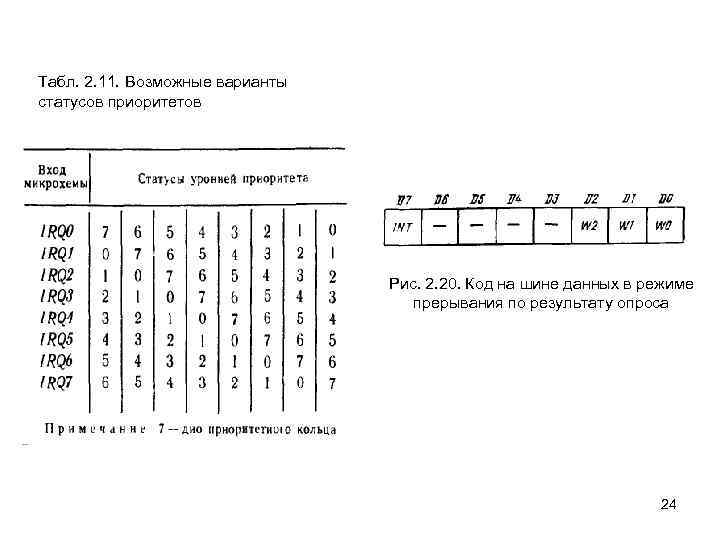

Табл. 2. 11. Возможные варианты статусов приоритетов Рис. 2. 20. Код на шине данных в режиме прерывания по результату опроса 24

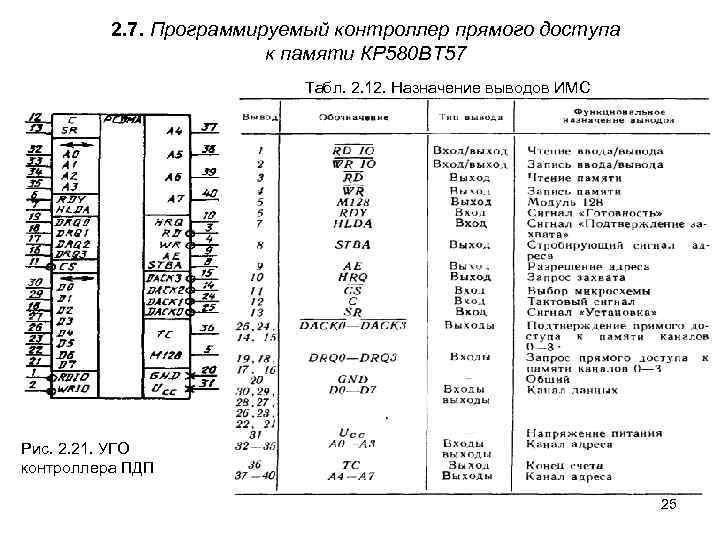

2. 7. Программируемый контроллер прямого доступа к памяти КР 580 ВТ 57 Табл. 2. 12. Назначение выводов ИМС Рис. 2. 21. УГО контроллера ПДП 25

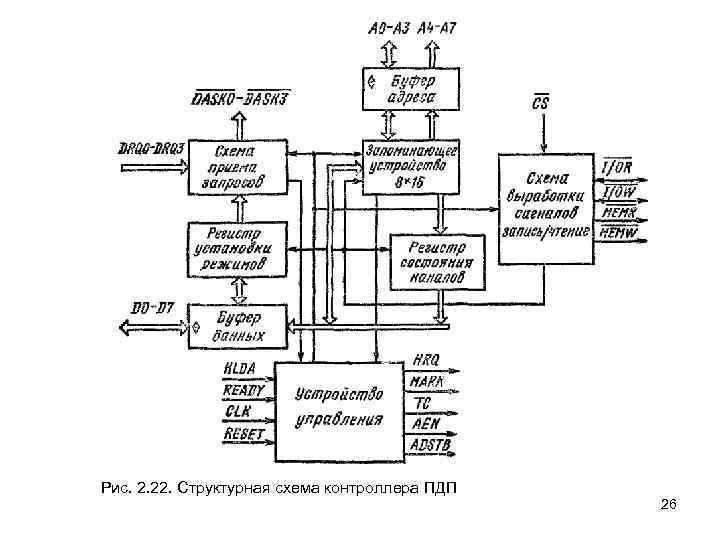

Рис. 2. 22. Структурная схема контроллера ПДП 26

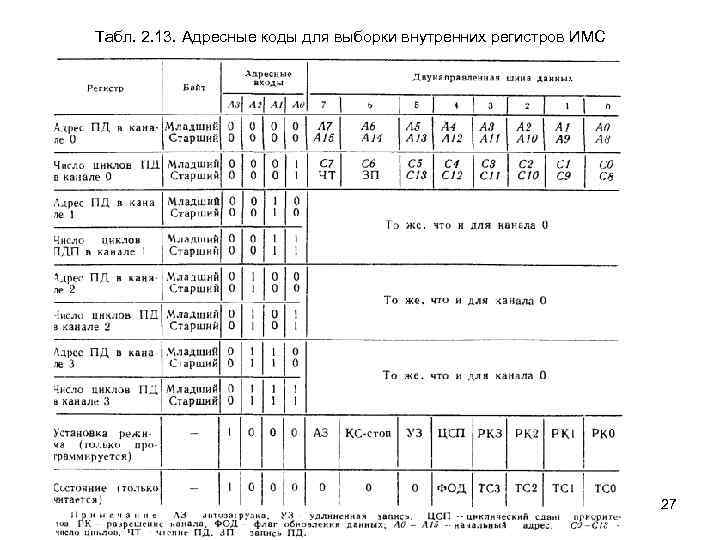

Табл. 2. 13. Адресные коды для выборки внутренних регистров ИМС 27

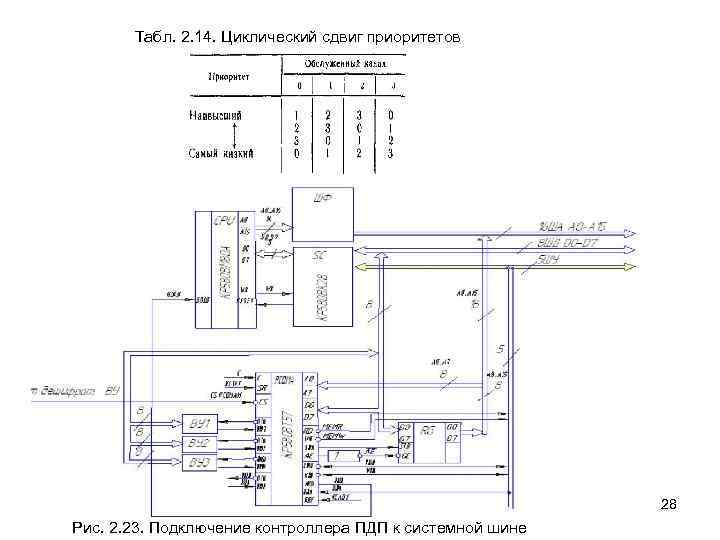

Табл. 2. 14. Циклический сдвиг приоритетов 28 Рис. 2. 23. Подключение контроллера ПДП к системной шине

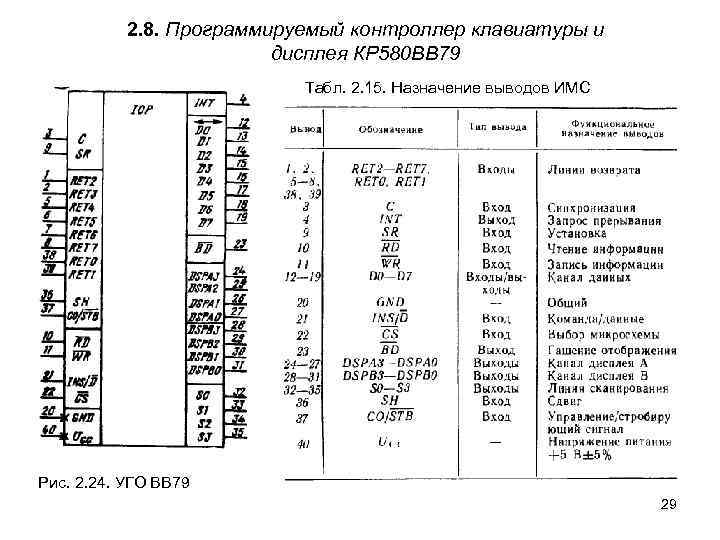

2. 8. Программируемый контроллер клавиатуры и дисплея КР 580 ВВ 79 Табл. 2. 15. Назначение выводов ИМС Рис. 2. 24. УГО ВВ 79 29

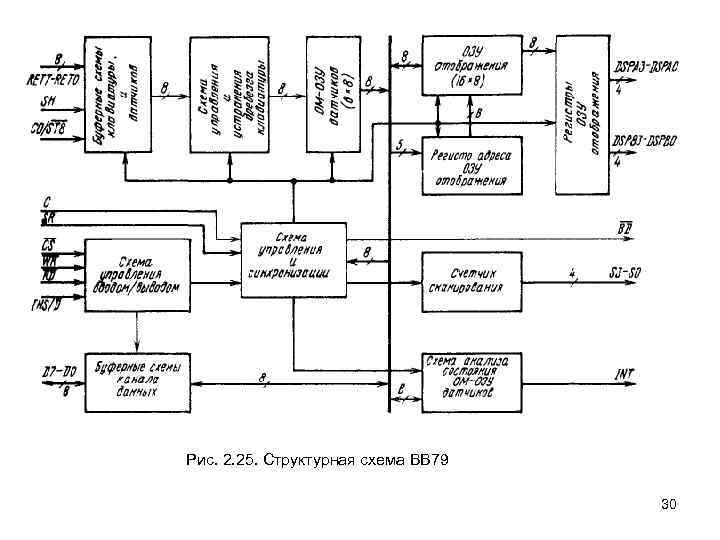

Рис. 2. 25. Структурная схема ВВ 79 30

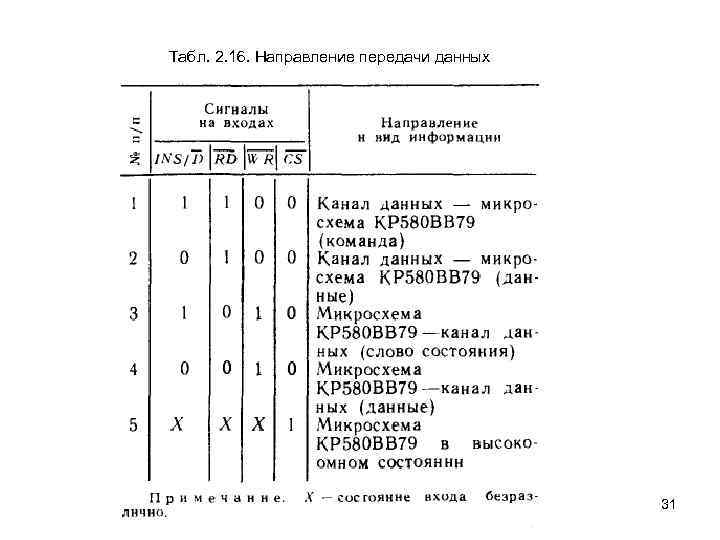

Табл. 2. 16. Направление передачи данных 31

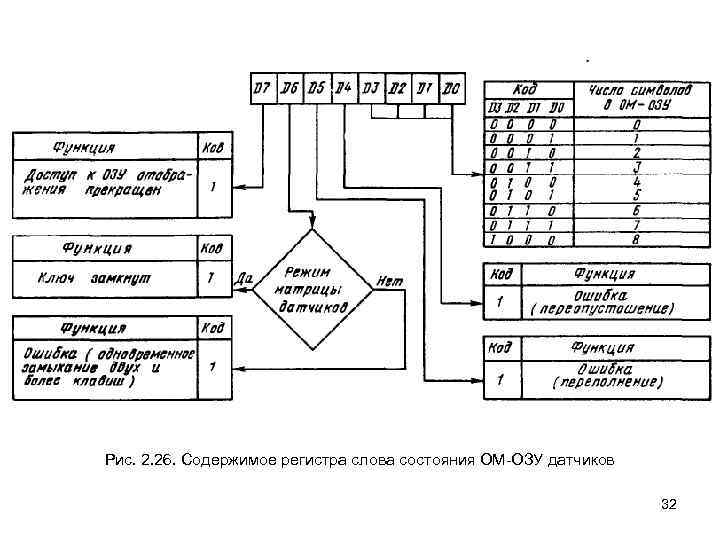

Рис. 2. 26. Содержимое регистра слова состояния ОМ ОЗУ датчиков 32

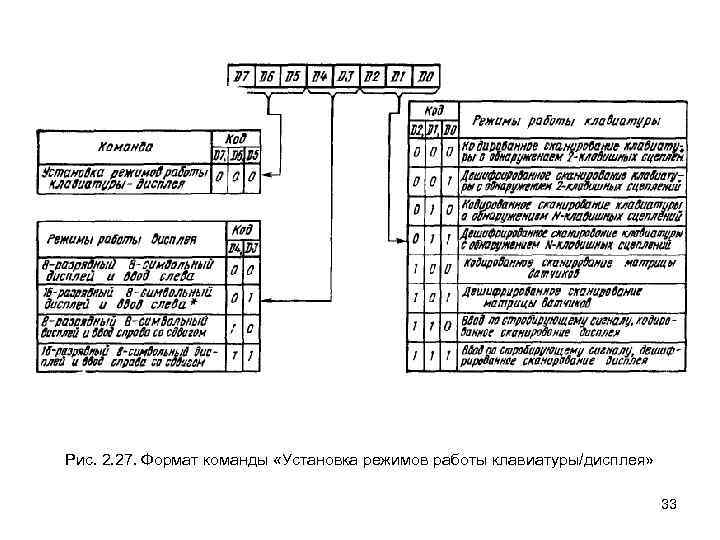

Рис. 2. 27. Формат команды «Установка режимов работы клавиатуры/дисплея» 33

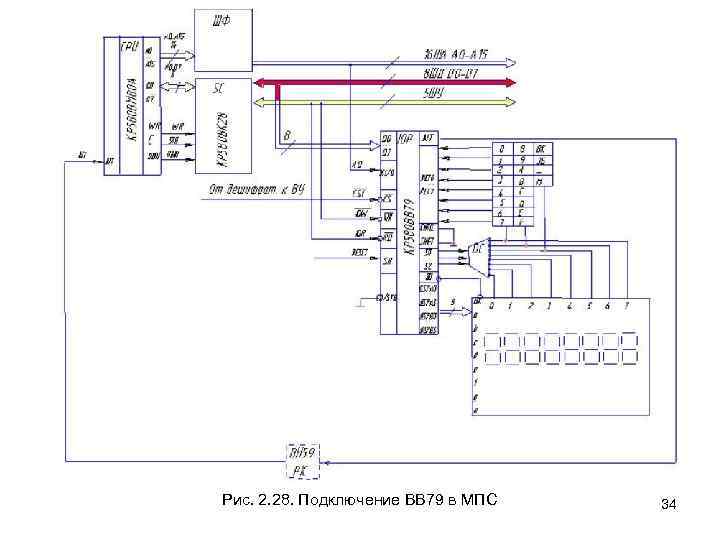

Рис. 2. 28. Подключение ВВ 79 в МПС 34

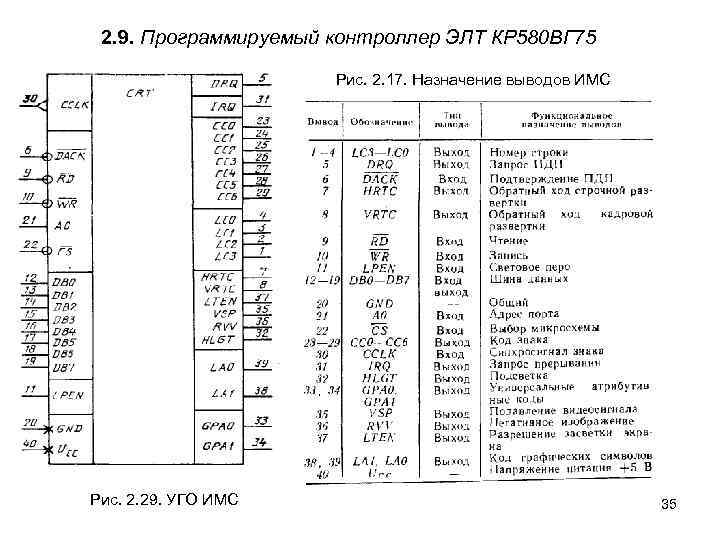

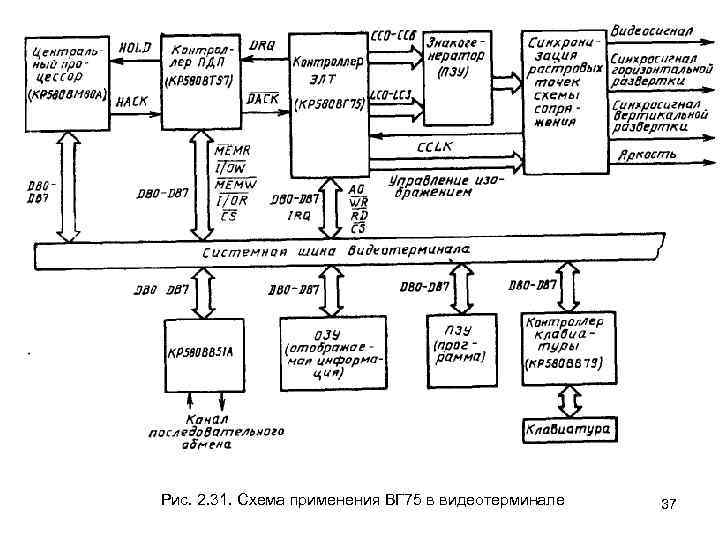

2. 9. Программируемый контроллер ЭЛТ КР 580 ВГ 75 Рис. 2. 17. Назначение выводов ИМС Рис. 2. 29. УГО ИМС 35

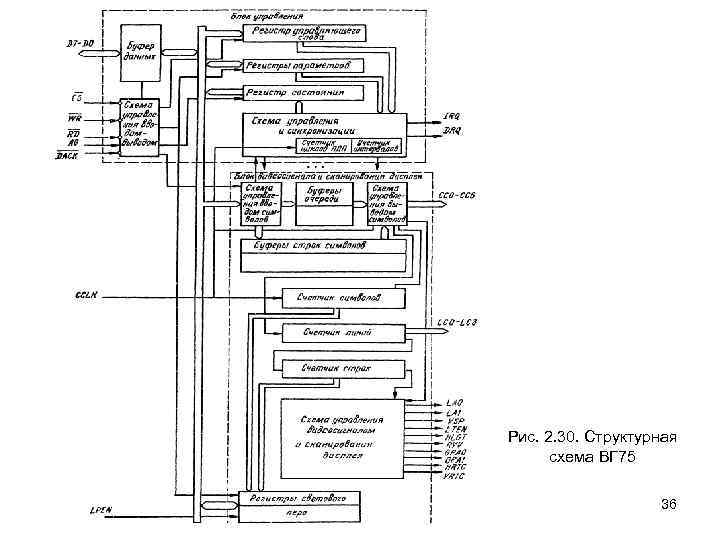

Рис. 2. 30. Структурная схема ВГ 75 36

Рис. 2. 31. Схема применения ВГ 75 в видеотерминале 37

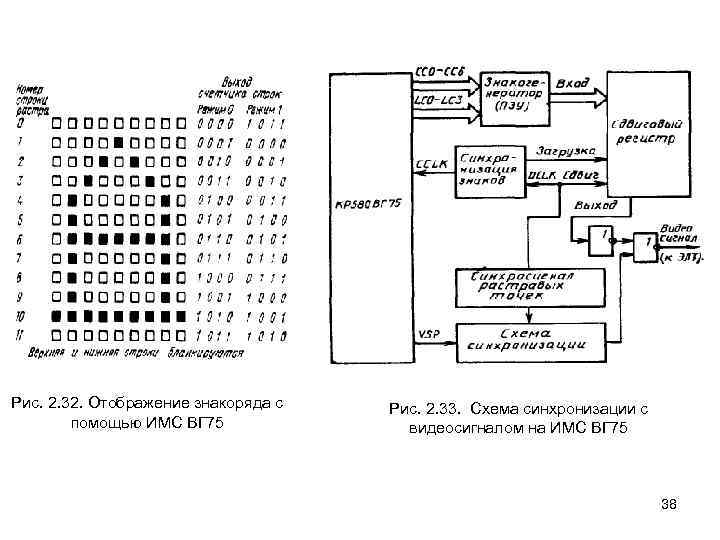

Рис. 2. 32. Отображение знакоряда с помощью ИМС ВГ 75 Рис. 2. 33. Схема синхронизации с видеосигналом на ИМС ВГ 75 38

39

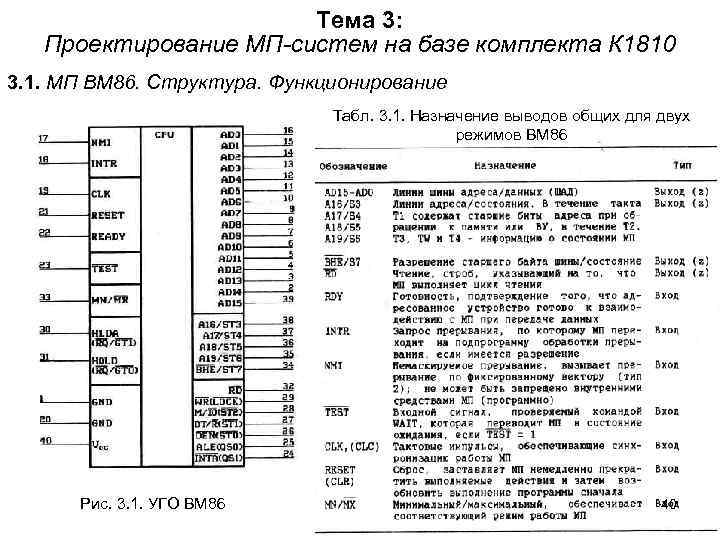

Тема 3: Проектирование МП-систем на базе комплекта К 1810 3. 1. МП ВМ 86. Структура. Функционирование Табл. 3. 1. Назначение выводов общих для двух режимов ВМ 86 Рис. 3. 1. УГО ВМ 86 40

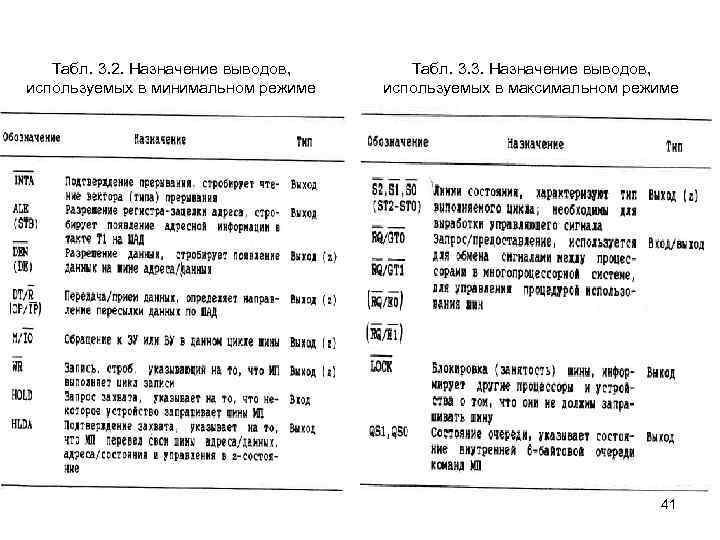

Табл. 3. 2. Назначение выводов, используемых в минимальном режиме Табл. 3. 3. Назначение выводов, используемых в максимальном режиме 41

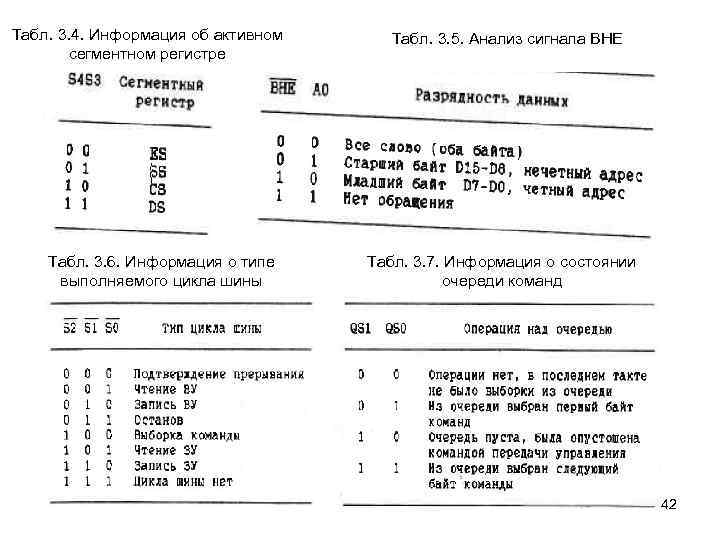

Табл. 3. 4. Информация об активном сегментном регистре Табл. 3. 6. Информация о типе выполняемого цикла шины Табл. 3. 5. Анализ сигнала ВНЕ Табл. 3. 7. Информация о состоянии очереди команд 42

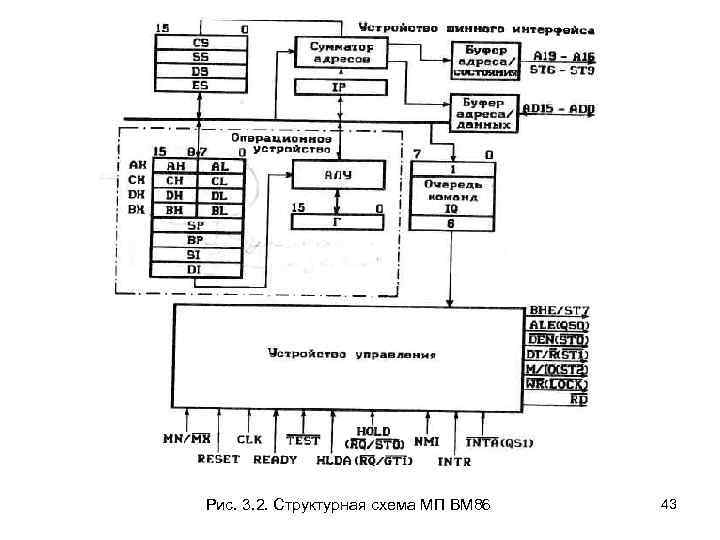

Рис. 3. 2. Структурная схема МП ВМ 86 43

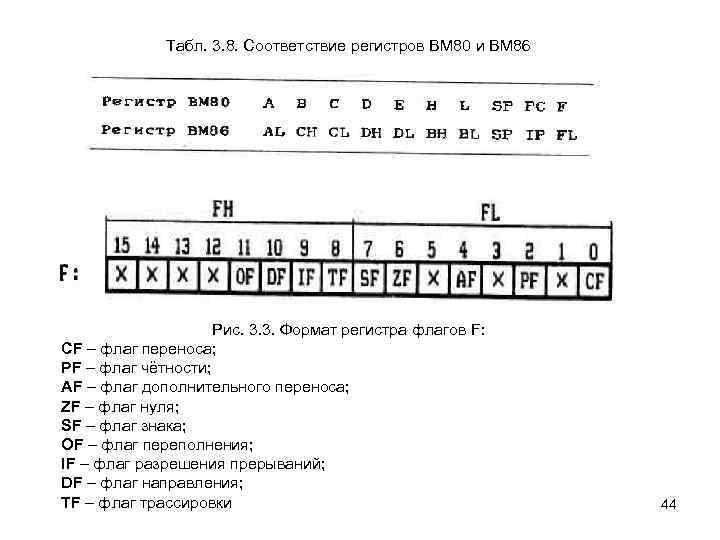

Табл. 3. 8. Соответствие регистров ВМ 80 и ВМ 86 Рис. 3. 3. Формат регистра флагов F: CF – флаг переноса; PF – флаг чётности; AF – флаг дополнительного переноса; ZF – флаг нуля; SF – флаг знака; OF – флаг переполнения; IF – флаг разрешения прерываний; DF – флаг направления; TF – флаг трассировки 44

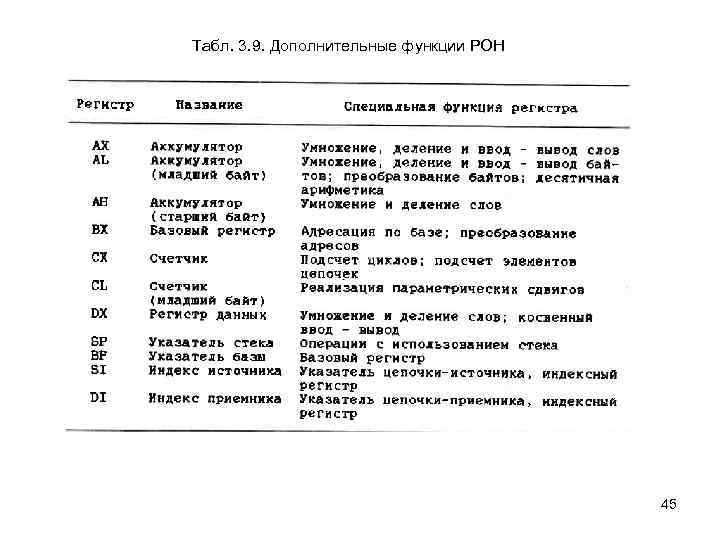

Табл. 3. 9. Дополнительные функции РОН 45

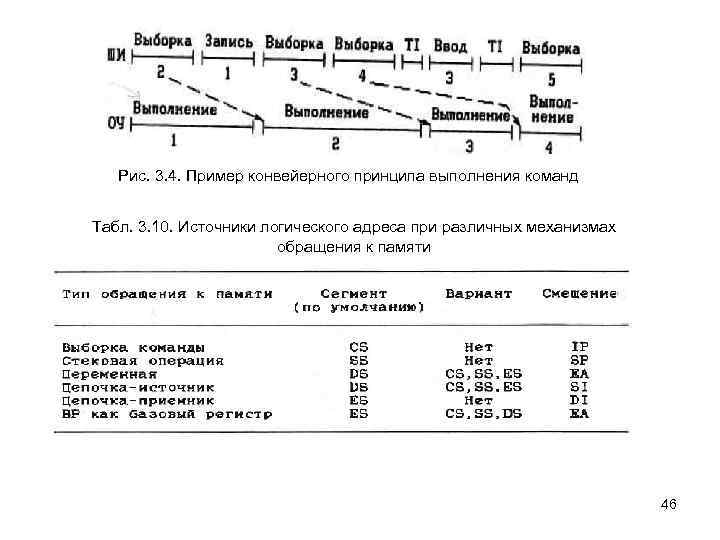

Рис. 3. 4. Пример конвейерного принципа выполнения команд Табл. 3. 10. Источники логического адреса при различных механизмах обращения к памяти 46

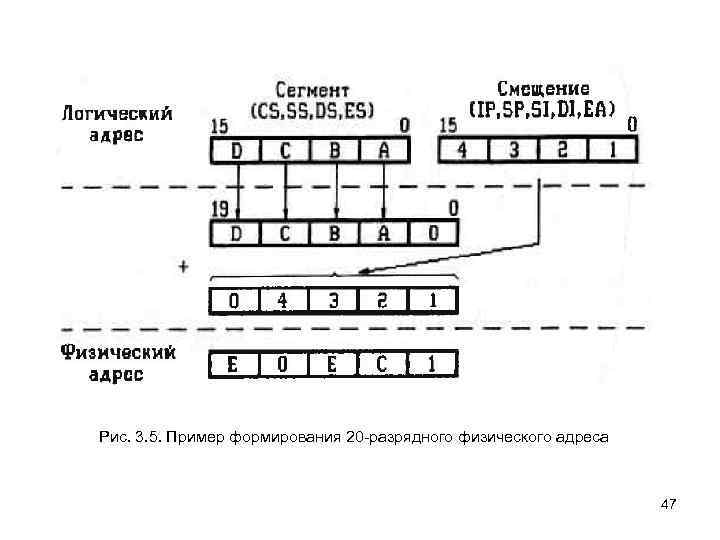

Рис. 3. 5. Пример формирования 20 разрядного физического адреса 47

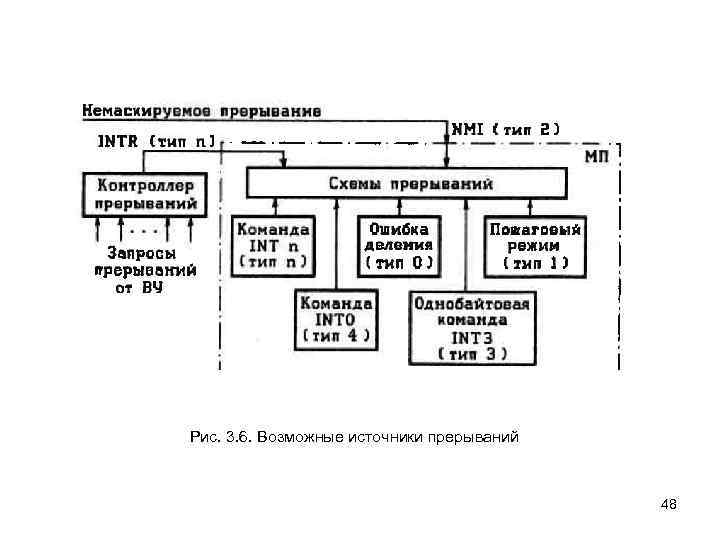

Рис. 3. 6. Возможные источники прерываний 48

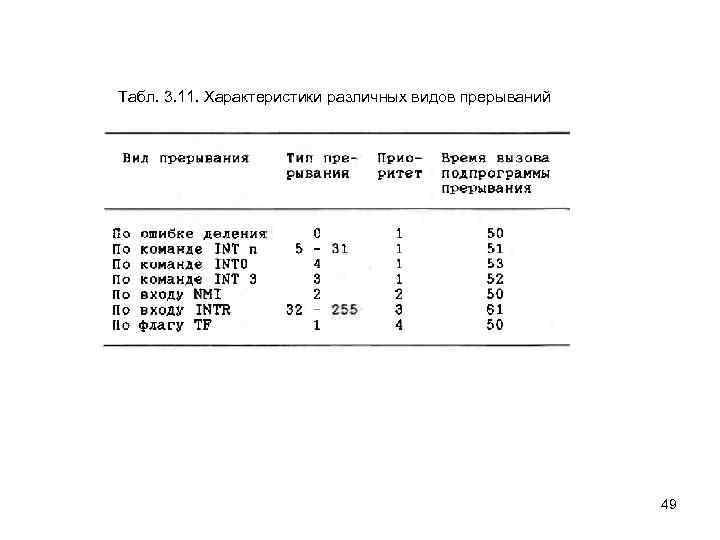

Табл. 3. 11. Характеристики различных видов прерываний 49

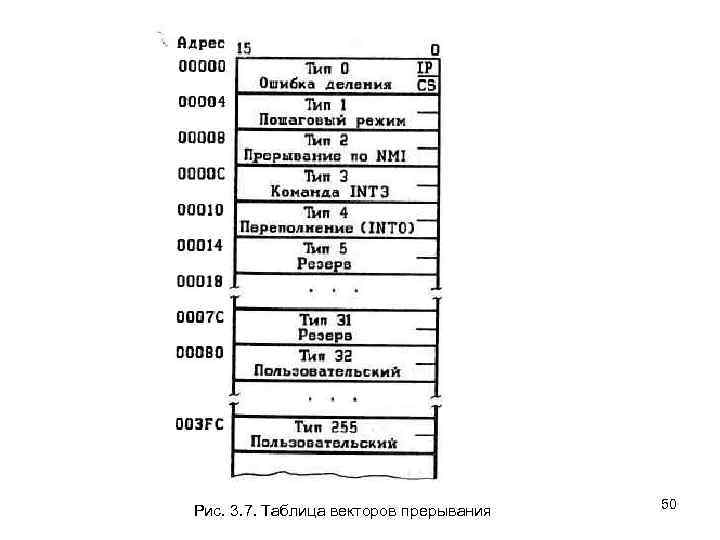

Рис. 3. 7. Таблица векторов прерывания 50

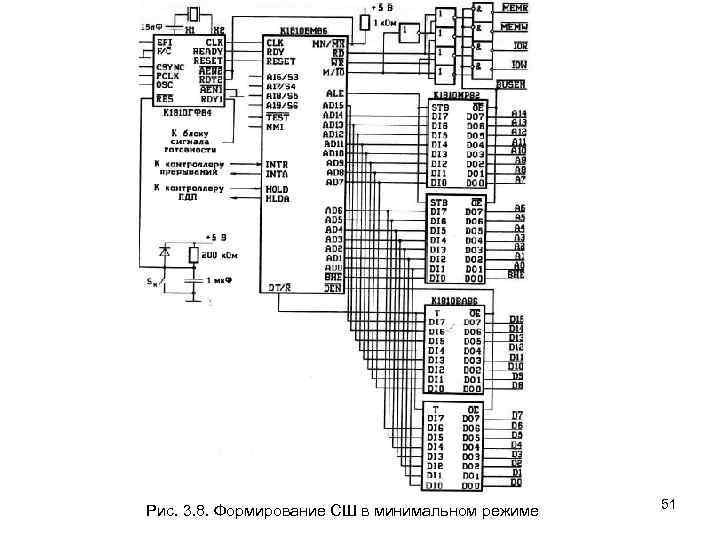

Рис. 3. 8. Формирование СШ в минимальном режиме 51

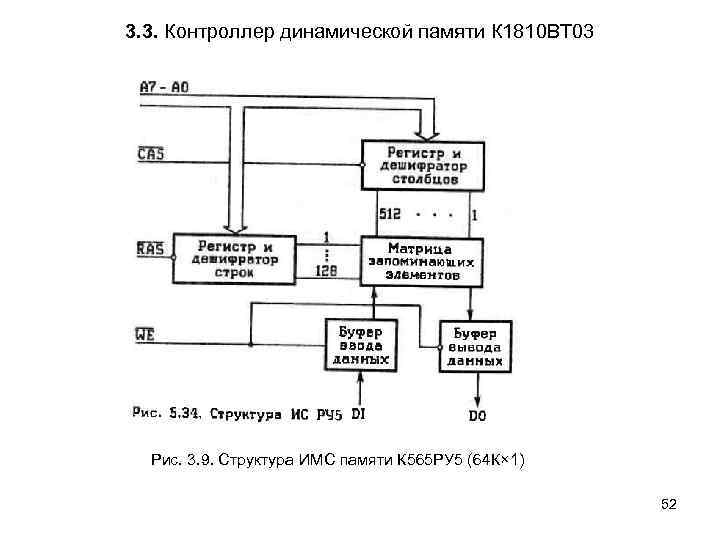

3. 3. Контроллер динамической памяти К 1810 ВТ 03 Рис. 3. 9. Структура ИМС памяти К 565 РУ 5 (64 К× 1) 52

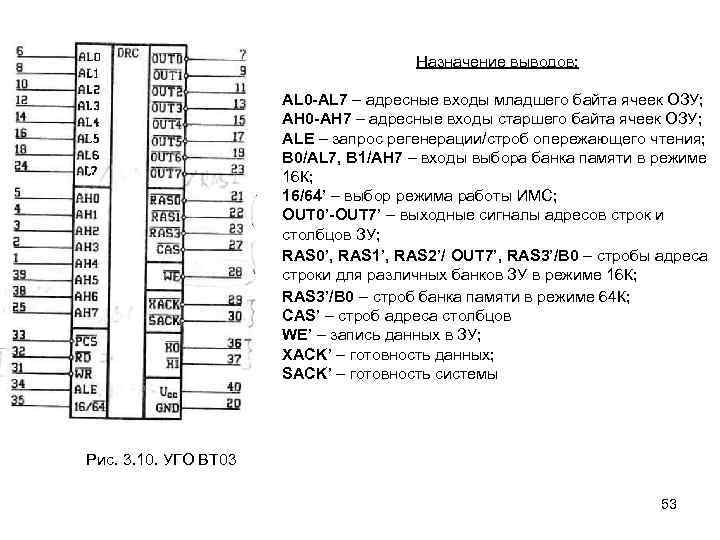

Назначение выводов: AL 0 -AL 7 – адресные входы младшего байта ячеек ОЗУ; AH 0 -AH 7 – адресные входы старшего байта ячеек ОЗУ; ALE – запрос регенерации/строб опережающего чтения; В 0/AL 7, В 1/AH 7 – входы выбора банка памяти в режиме 16 К; 16/64’ – выбор режима работы ИМС; OUT 0’-OUT 7’ – выходные сигналы адресов строк и столбцов ЗУ; RAS 0’, RAS 1’, RAS 2’/ OUT 7’, RAS 3’/В 0 – стробы адреса строки для различных банков ЗУ в режиме 16 К; RAS 3’/В 0 – строб банка памяти в режиме 64 К; CAS’ – строб адреса столбцов WE’ – запись данных в ЗУ; XACK’ – готовность данных; SACK’ – готовность системы Рис. 3. 10. УГО ВТ 03 53

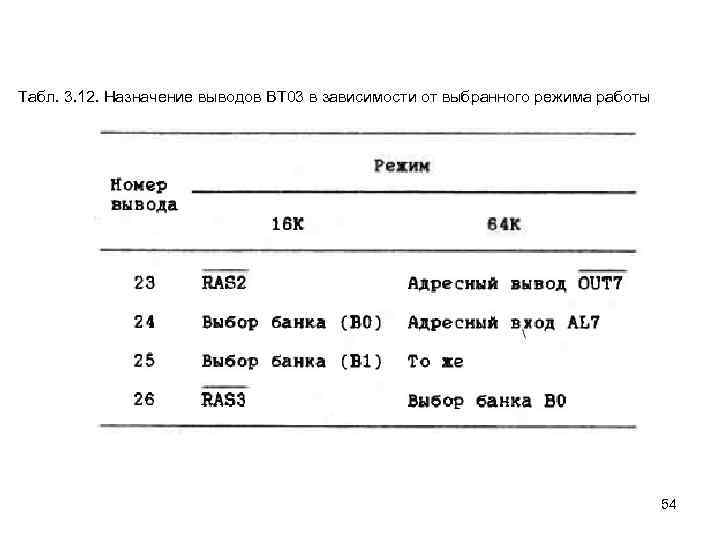

Табл. 3. 12. Назначение выводов ВТ 03 в зависимости от выбранного режима работы 54

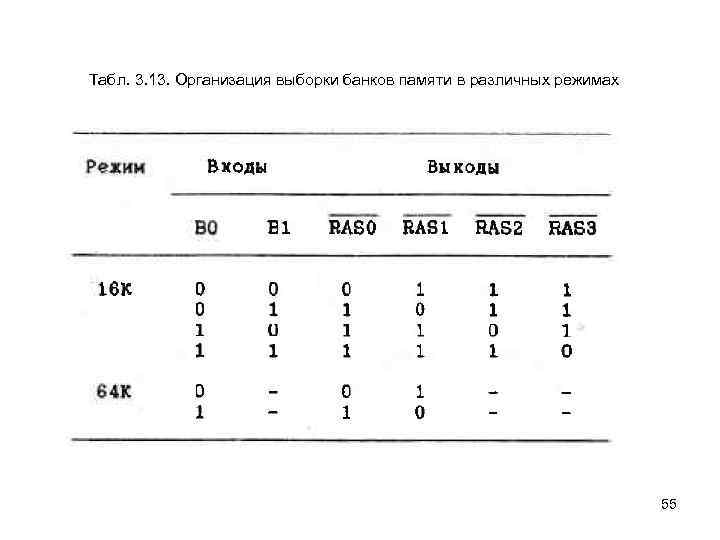

Табл. 3. 13. Организация выборки банков памяти в различных режимах 55

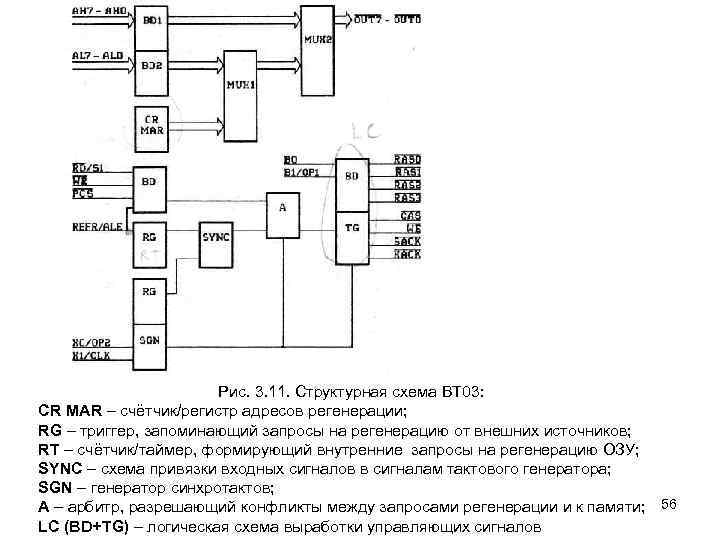

Рис. 3. 11. Структурная схема ВТ 03: CR MAR – счётчик/регистр адресов регенерации; RG – триггер, запоминающий запросы на регенерацию от внешних источников; RT – счётчик/таймер, формирующий внутренние запросы на регенерацию ОЗУ; SYNC – схема привязки входных сигналов в сигналам тактового генератора; SGN – генератор синхротактов; А – арбитр, разрешающий конфликты между запросами регенерации и к памяти; 56 LC (BD+TG) – логическая схема выработки управляющих сигналов

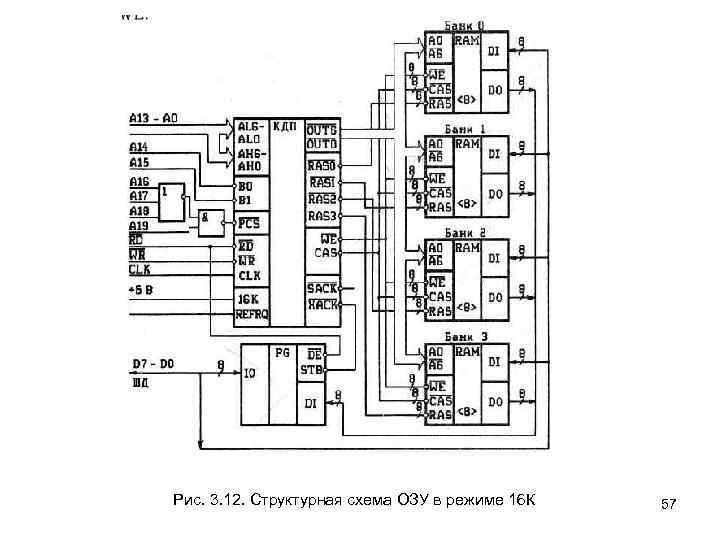

Рис. 3. 12. Структурная схема ОЗУ в режиме 16 К 57

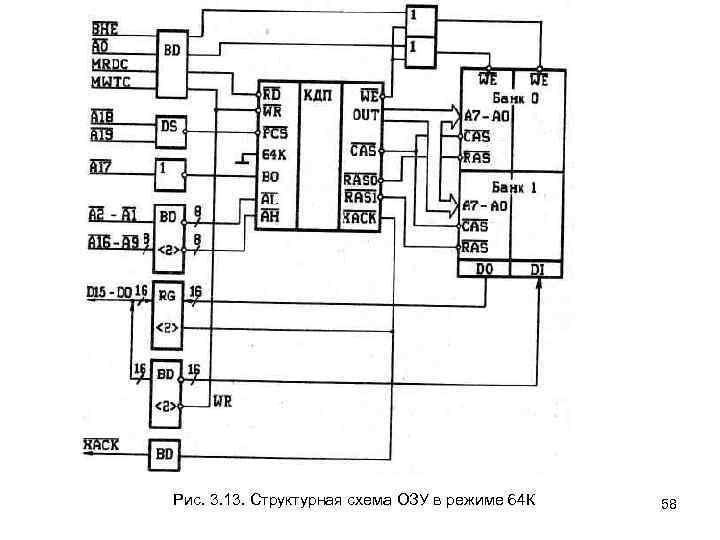

Рис. 3. 13. Структурная схема ОЗУ в режиме 64 К 58

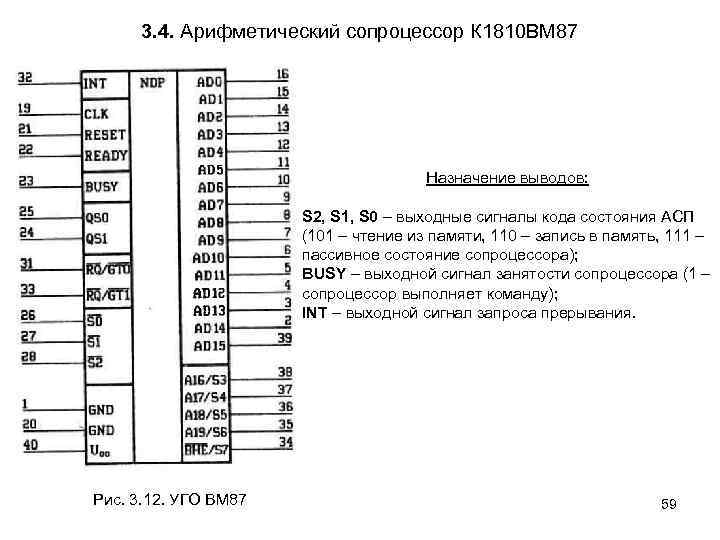

3. 4. Арифметический сопроцессор К 1810 ВМ 87 Назначение выводов: S 2, S 1, S 0 – выходные сигналы кода состояния АСП (101 – чтение из памяти, 110 – запись в память, 111 – пассивное состояние сопроцессора); BUSY – выходной сигнал занятости сопроцессора (1 – сопроцессор выполняет команду); INT – выходной сигнал запроса прерывания. Рис. 3. 12. УГО ВМ 87 59

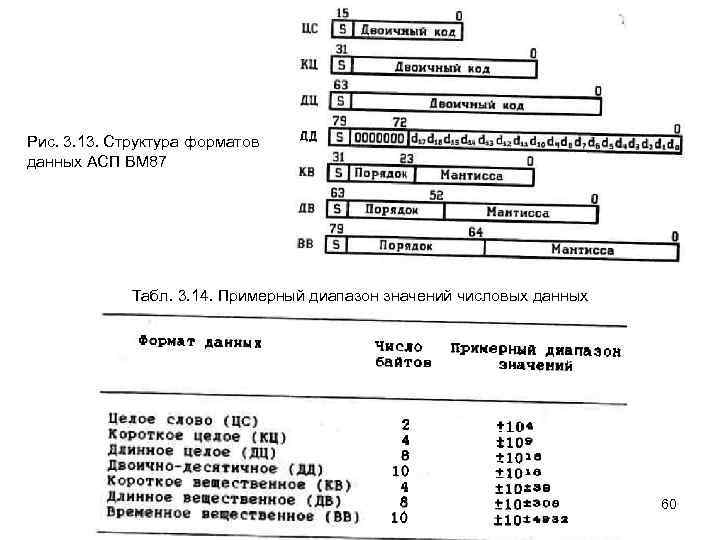

Рис. 3. 13. Структура форматов данных АСП ВМ 87 Табл. 3. 14. Примерный диапазон значений числовых данных 60

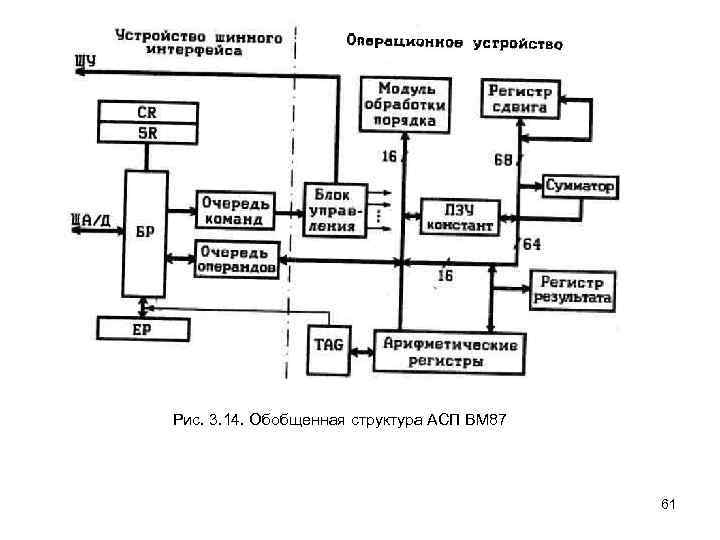

Рис. 3. 14. Обобщенная структура АСП ВМ 87 61

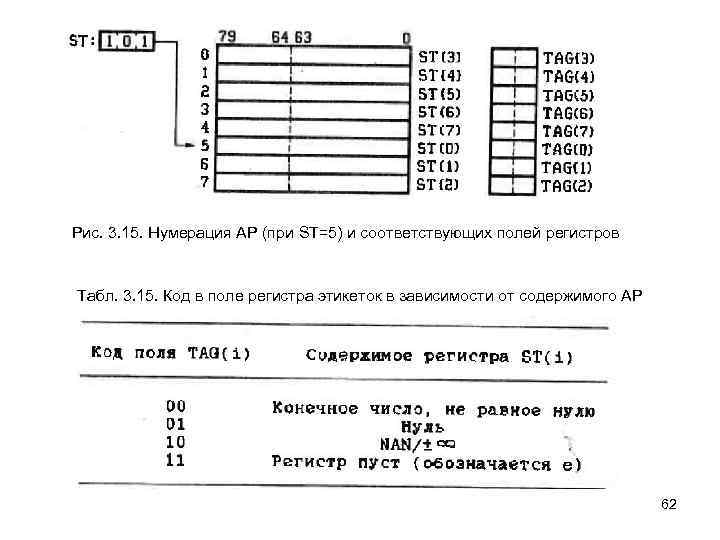

Рис. 3. 15. Нумерация АР (при ST=5) и соответствующих полей регистров Табл. 3. 15. Код в поле регистра этикеток в зависимости от содержимого АР 62

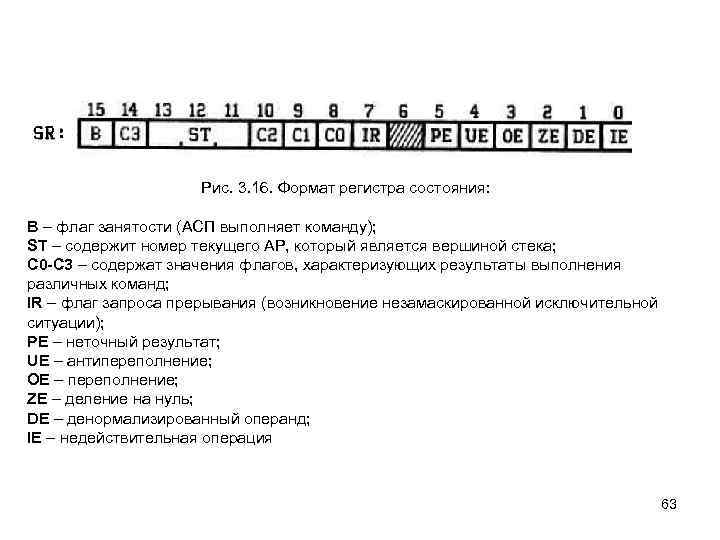

Рис. 3. 16. Формат регистра состояния: В – флаг занятости (АСП выполняет команду); ST – содержит номер текущего АР, который является вершиной стека; C 0 -C 3 – содержат значения флагов, характеризующих результаты выполнения различных команд; IR – флаг запроса прерывания (возникновение незамаскированной исключительной ситуации); PE – неточный результат; UE – антипереполнение; OE – переполнение; ZE – деление на нуль; DE – денормализированный операнд; IE – недействительная операция 63

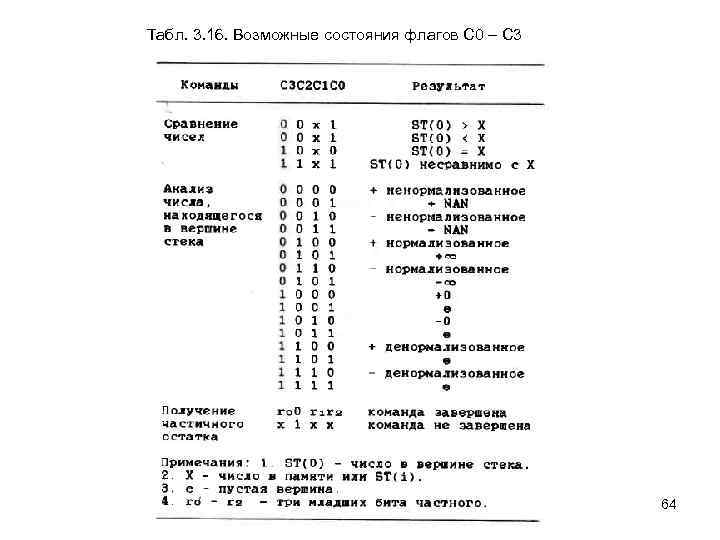

Табл. 3. 16. Возможные состояния флагов С 0 – С 3 64

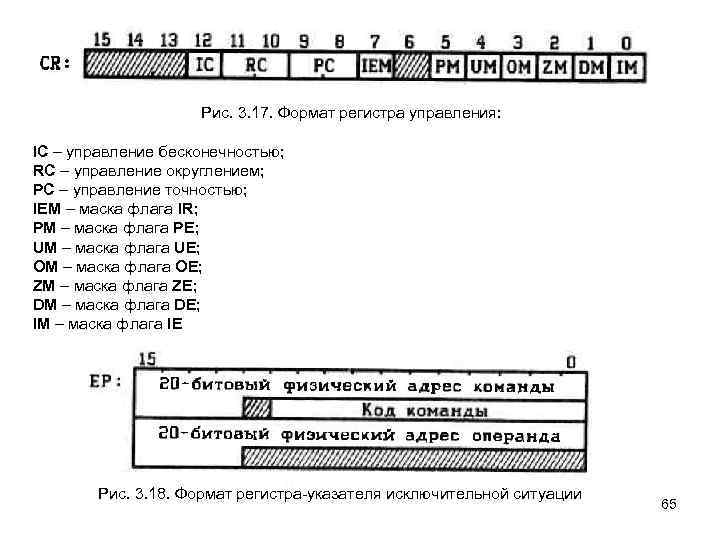

Рис. 3. 17. Формат регистра управления: IC – управление бесконечностью; RC – управление округлением; PC – управление точностью; IEM – маска флага IR; PM – маска флага PE; UM – маска флага UE; OM – маска флага OE; ZM – маска флага ZE; DM – маска флага DE; IM – маска флага IE Рис. 3. 18. Формат регистра указателя исключительной ситуации 65

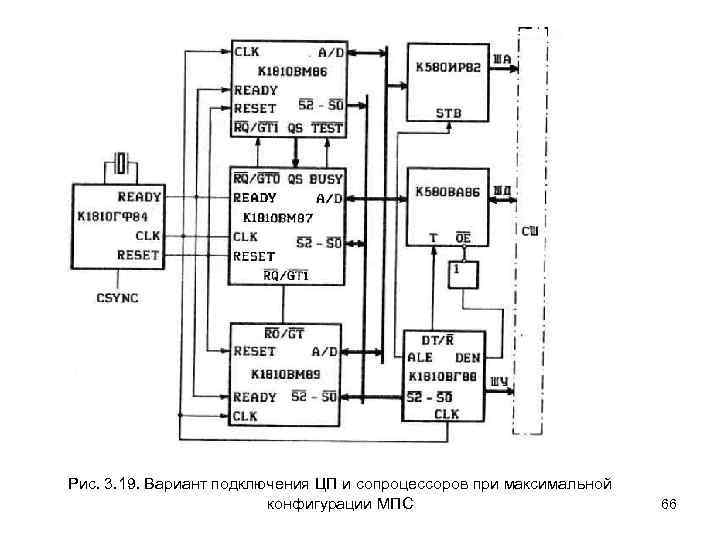

Рис. 3. 19. Вариант подключения ЦП и сопроцессоров при максимальной конфигурации МПС 66

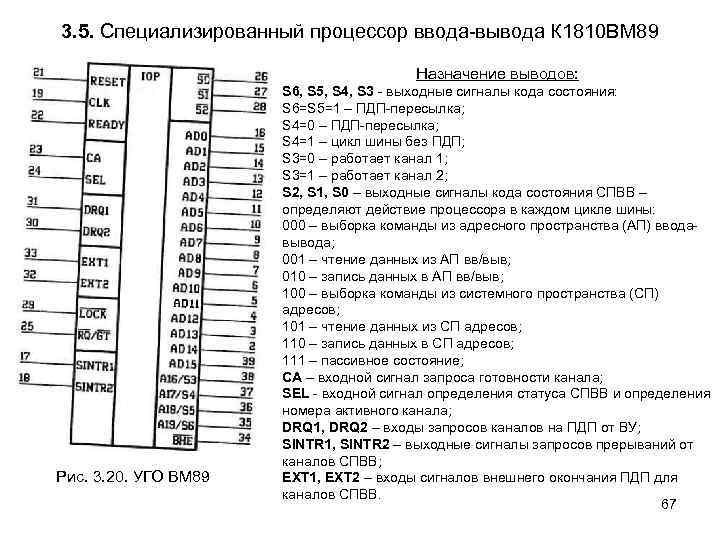

3. 5. Специализированный процессор ввода вывода К 1810 ВМ 89 Назначение выводов: Рис. 3. 20. УГО ВМ 89 S 6, S 5, S 4, S 3 выходные сигналы кода состояния: S 6=S 5=1 – ПДП пересылка; S 4=0 – ПДП пересылка; S 4=1 – цикл шины без ПДП; S 3=0 – работает канал 1; S 3=1 – работает канал 2; S 2, S 1, S 0 – выходные сигналы кода состояния СПВВ – определяют действие процессора в каждом цикле шины: 000 – выборка команды из адресного пространства (АП) ввода вывода; 001 – чтение данных из АП вв/выв; 010 – запись данных в АП вв/выв; 100 – выборка команды из системного пространства (СП) адресов; 101 – чтение данных из СП адресов; 110 – запись данных в СП адресов; 111 – пассивное состояние; СА – входной сигнал запроса готовности канала; SEL входной сигнал определения статуса СПВВ и определения номера активного канала; DRQ 1, DRQ 2 – входы запросов каналов на ПДП от ВУ; SINTR 1, SINTR 2 – выходные сигналы запросов прерываний от каналов СПВВ; EXT 1, EXT 2 – входы сигналов внешнего окончания ПДП для каналов СПВВ. 67

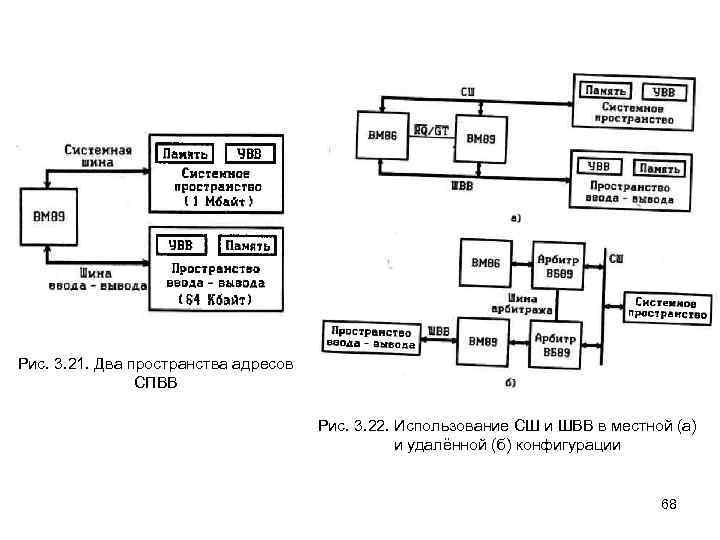

Рис. 3. 21. Два пространства адресов СПВВ Рис. 3. 22. Использование СШ и ШВВ в местной (а) и удалённой (б) конфигурации 68

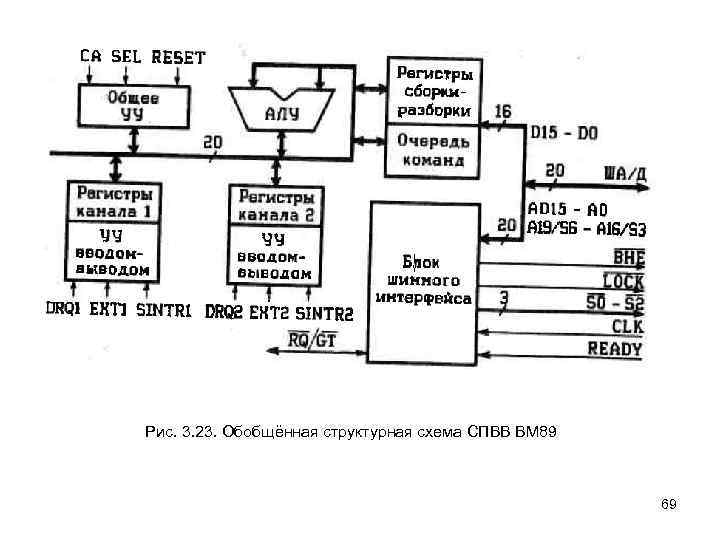

Рис. 3. 23. Обобщённая структурная схема СПВВ ВМ 89 69

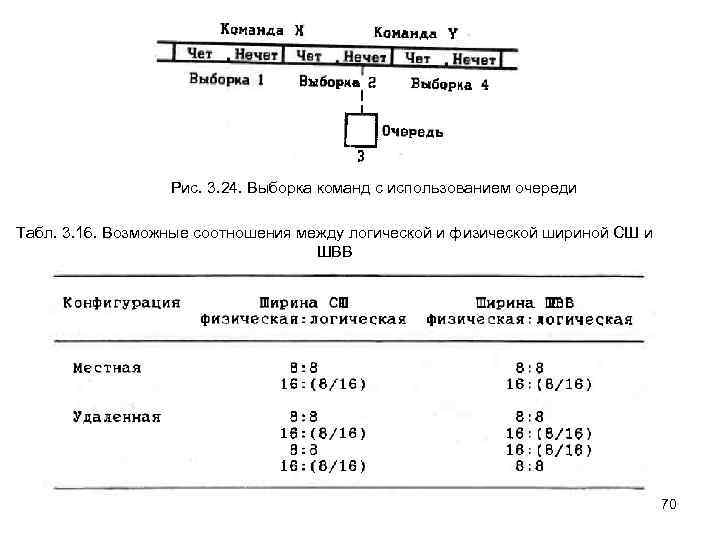

Рис. 3. 24. Выборка команд с использованием очереди Табл. 3. 16. Возможные соотношения между логической и физической шириной СШ и ШВВ 70

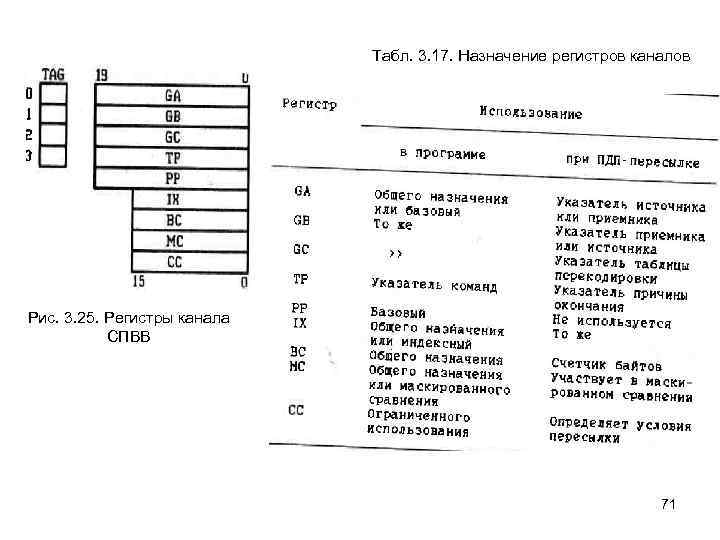

Табл. 3. 17. Назначение регистров каналов Рис. 3. 25. Регистры канала СПВВ 71

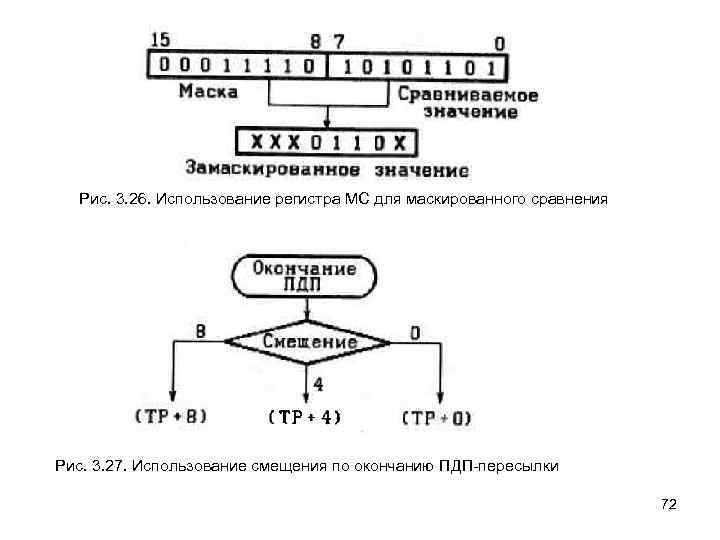

Рис. 3. 26. Использование регистра МС для маскированного сравнения Рис. 3. 27. Использование смещения по окончанию ПДП пересылки 72

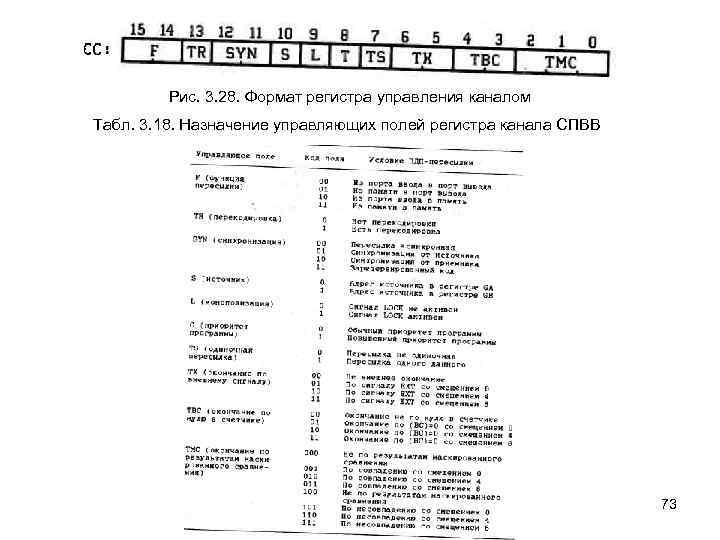

Рис. 3. 28. Формат регистра управления каналом Табл. 3. 18. Назначение управляющих полей регистра канала СПВВ 73

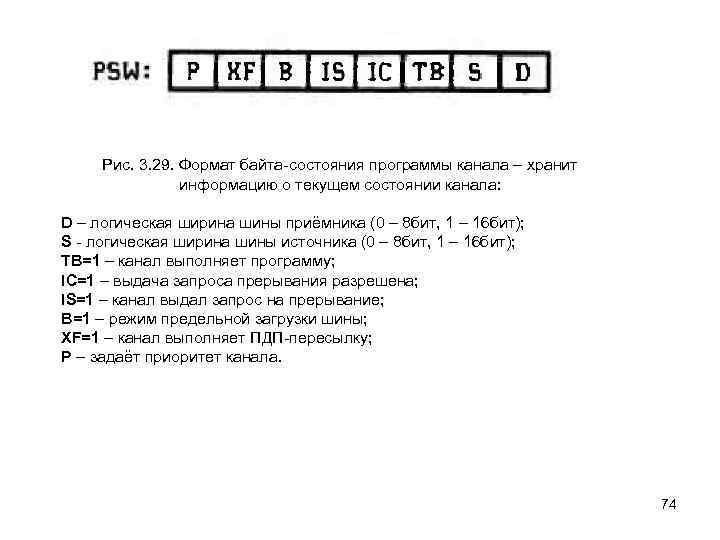

Рис. 3. 29. Формат байта состояния программы канала – хранит информацию о текущем состоянии канала: D – логическая ширина шины приёмника (0 – 8 бит, 1 – 16 бит); S логическая ширина шины источника (0 – 8 бит, 1 – 16 бит); TB=1 – канал выполняет программу; IC=1 – выдача запроса прерывания разрешена; IS=1 – канал выдал запрос на прерывание; В=1 – режим предельной загрузки шины; XF=1 – канал выполняет ПДП пересылку; Р – задаёт приоритет канала. 74

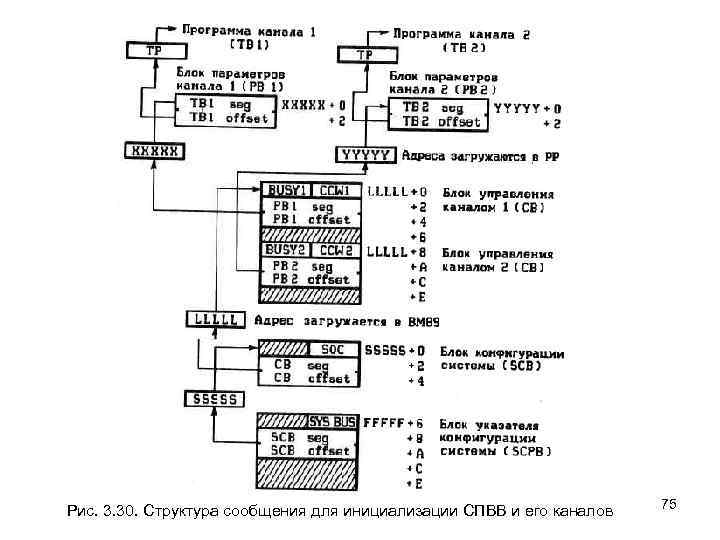

Рис. 3. 30. Структура сообщения для инициализации СПВВ и его каналов 75

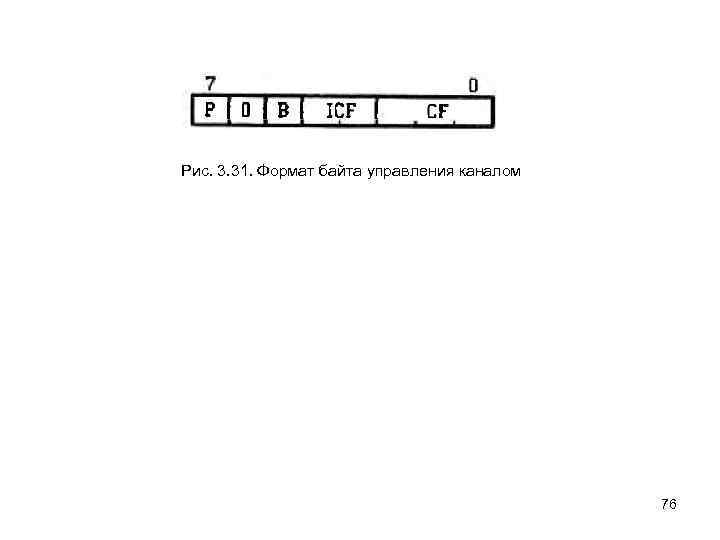

Рис. 3. 31. Формат байта управления каналом 76

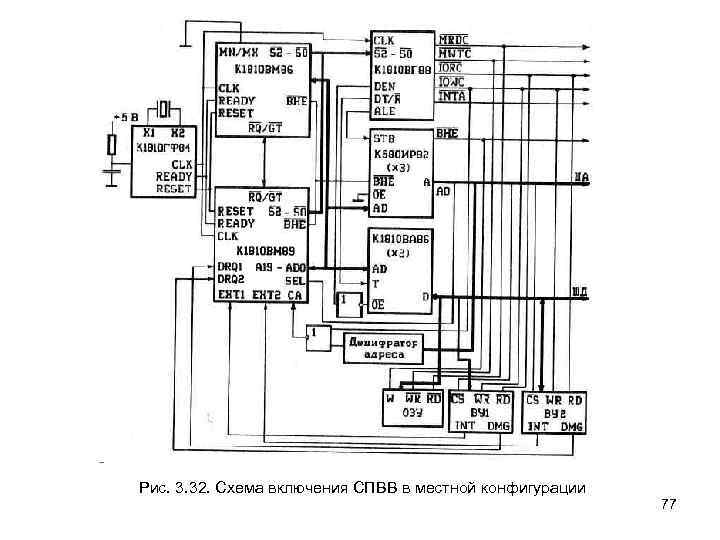

Рис. 3. 32. Схема включения СПВВ в местной конфигурации 77

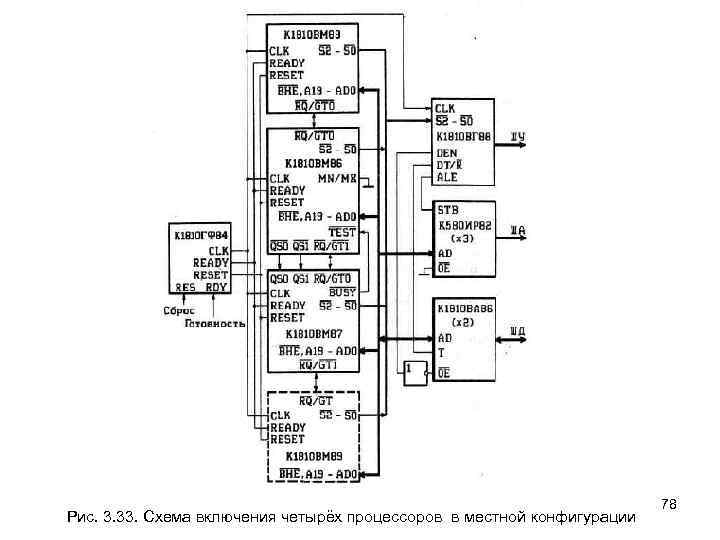

Рис. 3. 33. Схема включения четырёх процессоров в местной конфигурации 78

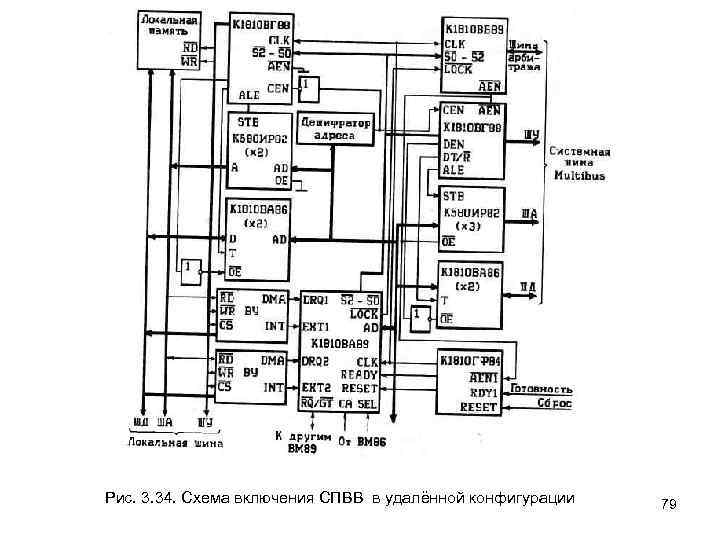

Рис. 3. 34. Схема включения СПВВ в удалённой конфигурации 79

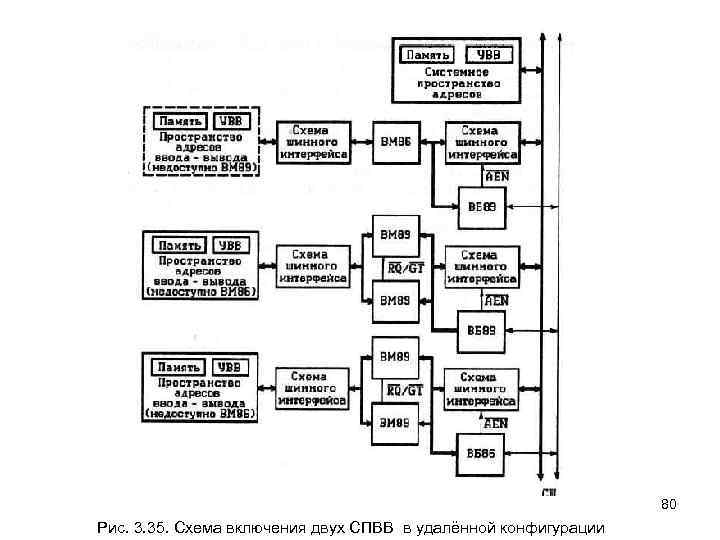

80 Рис. 3. 35. Схема включения двух СПВВ в удалённой конфигурации

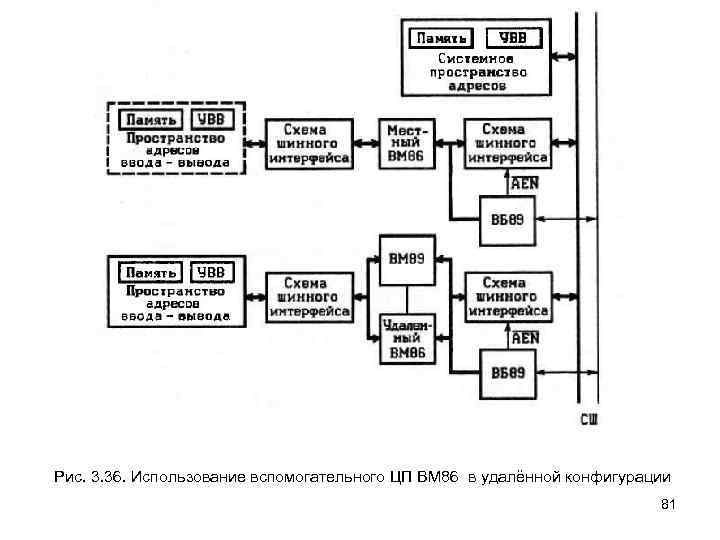

Рис. 3. 36. Использование вспомогательного ЦП ВМ 86 в удалённой конфигурации 81