5af10a8e00309666ecb95a907d8814ef.ppt

- Количество слайдов: 31

Lidor Pergament & Omer Cohen Mr. Adam Teman, Dr. Alexander Fish

Lidor Pergament & Omer Cohen Mr. Adam Teman, Dr. Alexander Fish

Lecture Contents • • • Introduction SRAM Overview Novel SRAM bitcell Test Chip Architecture Summary Introduction 6 T SRAM Bitcell Design Architecture Summary

Lecture Contents • • • Introduction SRAM Overview Novel SRAM bitcell Test Chip Architecture Summary Introduction 6 T SRAM Bitcell Design Architecture Summary

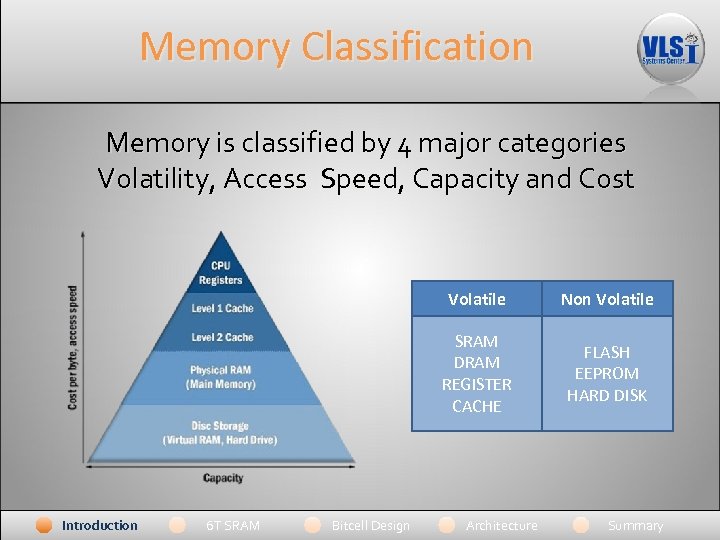

Memory Classification Memory is classified by 4 major categories Volatility, Access Speed, Capacity and Cost Volatile SRAM DRAM REGISTER CACHE Introduction 6 T SRAM Bitcell Design Non Volatile FLASH EEPROM HARD DISK Architecture Summary

Memory Classification Memory is classified by 4 major categories Volatility, Access Speed, Capacity and Cost Volatile SRAM DRAM REGISTER CACHE Introduction 6 T SRAM Bitcell Design Non Volatile FLASH EEPROM HARD DISK Architecture Summary

Motivation & Goal • Minimum energy point in digital circuits is achieved at subthreshold voltages (Vdd < Vt). • Low-voltage operation of SRAM memories in the subthreshold region offers substantial power and energy savings at the cost of speed. • This project focuses on the design and implementation of a novel SRAM bitcell for use in the subthreshold region. Introduction 6 T SRAM Bitcell Design Architecture Summary

Motivation & Goal • Minimum energy point in digital circuits is achieved at subthreshold voltages (Vdd < Vt). • Low-voltage operation of SRAM memories in the subthreshold region offers substantial power and energy savings at the cost of speed. • This project focuses on the design and implementation of a novel SRAM bitcell for use in the subthreshold region. Introduction 6 T SRAM Bitcell Design Architecture Summary

SRAM OVERVIEW Introduction 6 T SRAM Bitcell Design Architecture Summary

SRAM OVERVIEW Introduction 6 T SRAM Bitcell Design Architecture Summary

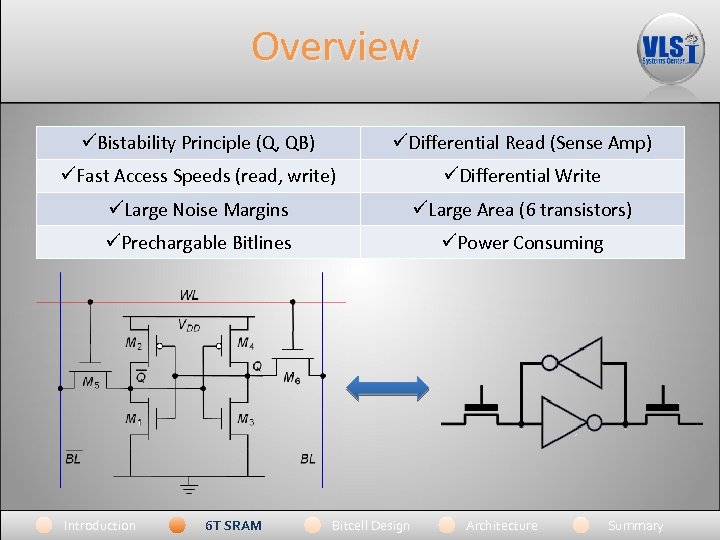

Overview üBistability Principle (Q, QB) üDifferential Read (Sense Amp) üFast Access Speeds (read, write) üDifferential Write üLarge Noise Margins üLarge Area (6 transistors) üPrechargable Bitlines üPower Consuming Introduction 6 T SRAM Bitcell Design Architecture Summary

Overview üBistability Principle (Q, QB) üDifferential Read (Sense Amp) üFast Access Speeds (read, write) üDifferential Write üLarge Noise Margins üLarge Area (6 transistors) üPrechargable Bitlines üPower Consuming Introduction 6 T SRAM Bitcell Design Architecture Summary

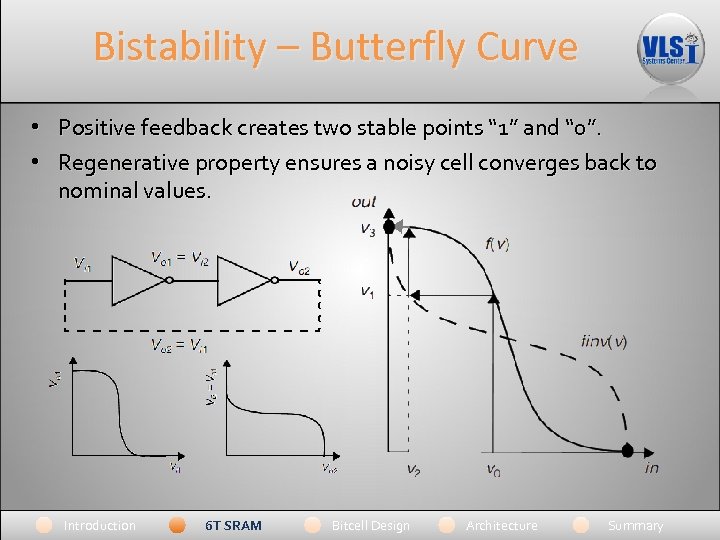

Bistability – Butterfly Curve • Positive feedback creates two stable points “ 1” and “ 0”. • Regenerative property ensures a noisy cell converges back to nominal values. Introduction 6 T SRAM Bitcell Design Architecture Summary

Bistability – Butterfly Curve • Positive feedback creates two stable points “ 1” and “ 0”. • Regenerative property ensures a noisy cell converges back to nominal values. Introduction 6 T SRAM Bitcell Design Architecture Summary

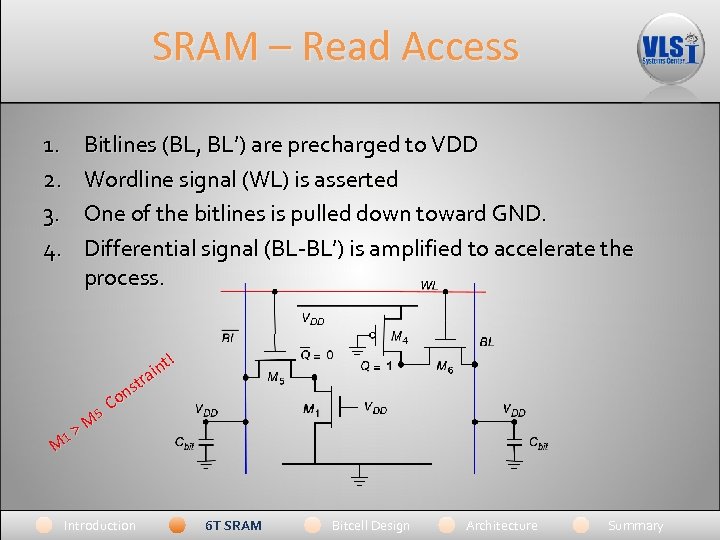

SRAM – Read Access 1. 2. 3. 4. Bitlines (BL, BL’) are precharged to VDD Wordline signal (WL) is asserted One of the bitlines is pulled down toward GND. Differential signal (BL-BL’) is amplified to accelerate the process. 5 1 M >M ! int a str n Co Introduction 6 T SRAM Bitcell Design Architecture Summary

SRAM – Read Access 1. 2. 3. 4. Bitlines (BL, BL’) are precharged to VDD Wordline signal (WL) is asserted One of the bitlines is pulled down toward GND. Differential signal (BL-BL’) is amplified to accelerate the process. 5 1 M >M ! int a str n Co Introduction 6 T SRAM Bitcell Design Architecture Summary

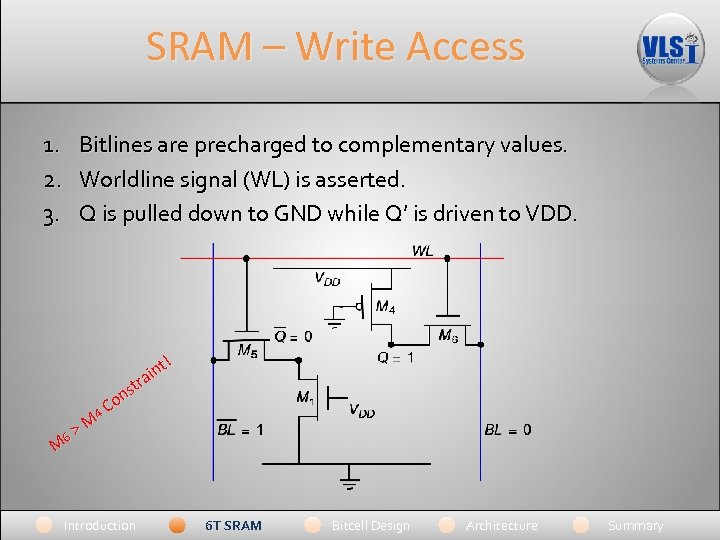

SRAM – Write Access 1. Bitlines are precharged to complementary values. 2. Worldline signal (WL) is asserted. 3. Q is pulled down to GND while Q’ is driven to VDD. 6 M ! int a str n Co 4 M > Introduction 6 T SRAM Bitcell Design Architecture Summary

SRAM – Write Access 1. Bitlines are precharged to complementary values. 2. Worldline signal (WL) is asserted. 3. Q is pulled down to GND while Q’ is driven to VDD. 6 M ! int a str n Co 4 M > Introduction 6 T SRAM Bitcell Design Architecture Summary

SRAM – Subthreshold Challenges • In general, ratioed digital circuits are more likely to fail in subthreshold voltages. • 6 T Bitcells cannot operate below 600 m. V – 700 m. V. • Read SNM problem - degraded read noise margins decrease bitcell stability. • Write fails under 600 m. V due to the increase of the p. MOS drive in sub-threshold. Introduction 6 T SRAM Bitcell Design Architecture Summary

SRAM – Subthreshold Challenges • In general, ratioed digital circuits are more likely to fail in subthreshold voltages. • 6 T Bitcells cannot operate below 600 m. V – 700 m. V. • Read SNM problem - degraded read noise margins decrease bitcell stability. • Write fails under 600 m. V due to the increase of the p. MOS drive in sub-threshold. Introduction 6 T SRAM Bitcell Design Architecture Summary

NOVEL 9 T SRAM BITCELL Introduction 6 T SRAM Bitcell Design Architecture Summary

NOVEL 9 T SRAM BITCELL Introduction 6 T SRAM Bitcell Design Architecture Summary

The Research Work • Numerous novel low-power SRAM memories have been proposed in recent years. • We studied analyzed many of the important proposals which include : 6 T, 7 T, 8 T, 9 T, 10 T bitcells, Virtual VDD, Virtual GND, DCVSL, Voltage Boost, Read Buffer, Read Assist, Voltage Boost, and more ……. Introduction 6 T SRAM Bitcell Design Architecture Summary

The Research Work • Numerous novel low-power SRAM memories have been proposed in recent years. • We studied analyzed many of the important proposals which include : 6 T, 7 T, 8 T, 9 T, 10 T bitcells, Virtual VDD, Virtual GND, DCVSL, Voltage Boost, Read Buffer, Read Assist, Voltage Boost, and more ……. Introduction 6 T SRAM Bitcell Design Architecture Summary

Brain Storming Introduction 6 T SRAM Bitcell Design Architecture Summary

Brain Storming Introduction 6 T SRAM Bitcell Design Architecture Summary

Major Achievements • Two innovative SRAM 9 T bitcells, named PSRAM and SFSRAM , aimed at eliminating static power consumption and operated in the subthreshold region were fully designed analyzed. • Three types of 8 -kb 40 nm SRAM test chips, nicknamed RAMBO, were designed for operation at 600 m. V and below. • We are the first academic research team in Israel to fully design and fabricate a state-of-the-art 40 nm CMOS silicon chip. Introduction 6 T SRAM Bitcell Design Architecture Summary

Major Achievements • Two innovative SRAM 9 T bitcells, named PSRAM and SFSRAM , aimed at eliminating static power consumption and operated in the subthreshold region were fully designed analyzed. • Three types of 8 -kb 40 nm SRAM test chips, nicknamed RAMBO, were designed for operation at 600 m. V and below. • We are the first academic research team in Israel to fully design and fabricate a state-of-the-art 40 nm CMOS silicon chip. Introduction 6 T SRAM Bitcell Design Architecture Summary

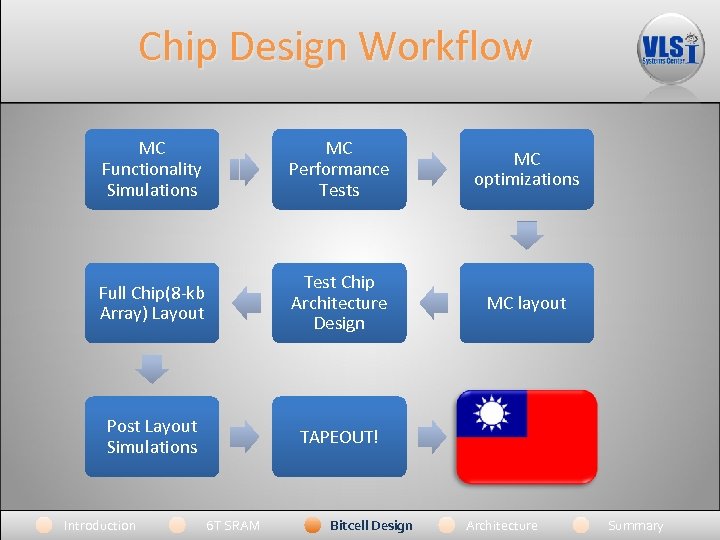

Chip Design Workflow MC Functionality Simulations MC Performance Tests MC optimizations Full Chip(8 -kb Array) Layout Test Chip Architecture Design MC layout Post Layout Simulations TAPEOUT! Introduction 6 T SRAM Bitcell Design Architecture Summary

Chip Design Workflow MC Functionality Simulations MC Performance Tests MC optimizations Full Chip(8 -kb Array) Layout Test Chip Architecture Design MC layout Post Layout Simulations TAPEOUT! Introduction 6 T SRAM Bitcell Design Architecture Summary

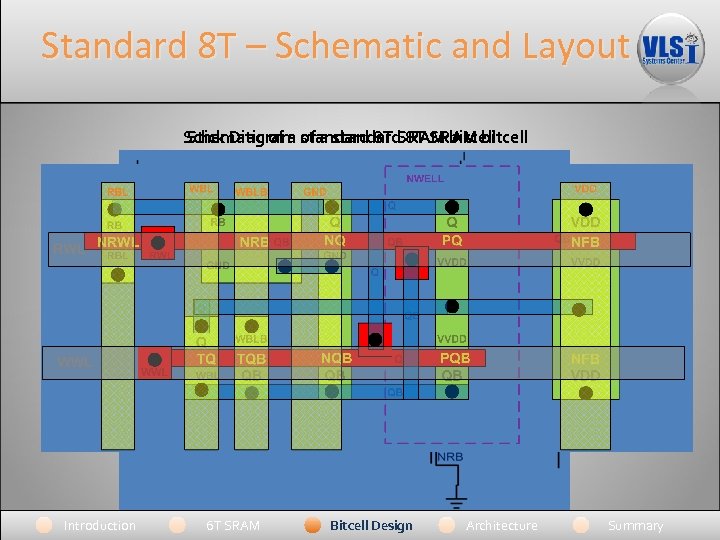

Standard 8 T – Schematic and Layout Schematic of a standard 8 T SRAM bitcell Stick Diagram standard 8 T SRAM bitcell Introduction 6 T SRAM Bitcell Design Architecture Summary

Standard 8 T – Schematic and Layout Schematic of a standard 8 T SRAM bitcell Stick Diagram standard 8 T SRAM bitcell Introduction 6 T SRAM Bitcell Design Architecture Summary

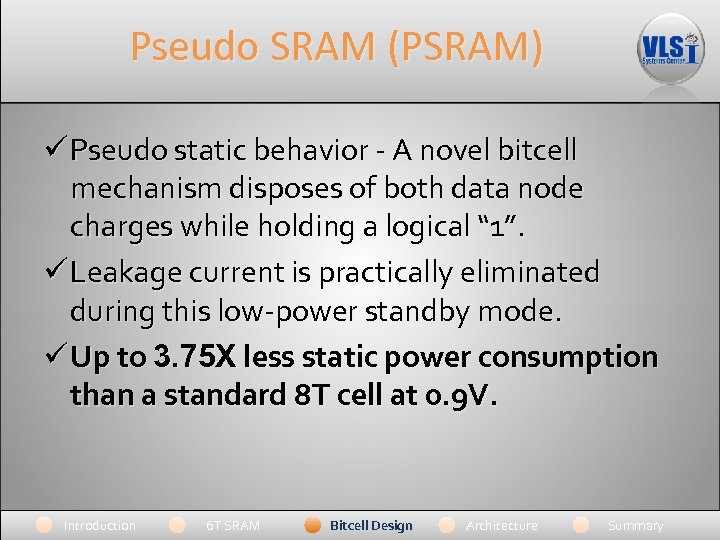

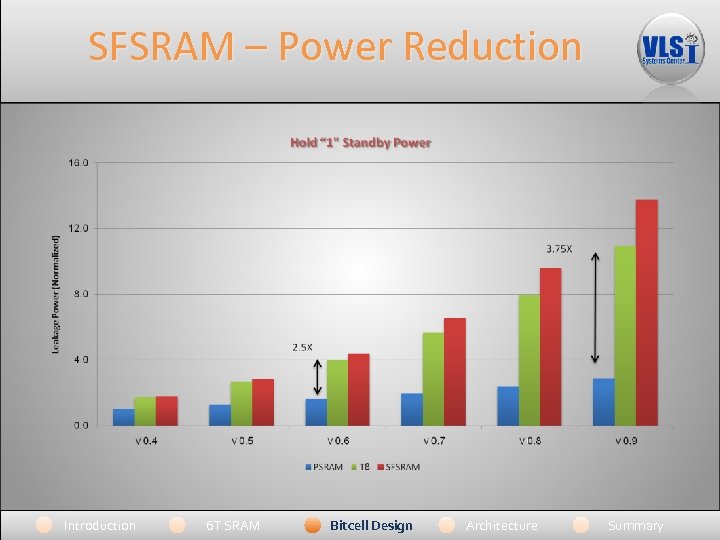

Pseudo SRAM (PSRAM) ü Pseudo static behavior - A novel bitcell mechanism disposes of both data node charges while holding a logical “ 1”. ü Leakage current is practically eliminated during this low-power standby mode. ü Up to 3. 75 X less static power consumption than a standard 8 T cell at 0. 9 V. Introduction 6 T SRAM Bitcell Design Architecture Summary

Pseudo SRAM (PSRAM) ü Pseudo static behavior - A novel bitcell mechanism disposes of both data node charges while holding a logical “ 1”. ü Leakage current is practically eliminated during this low-power standby mode. ü Up to 3. 75 X less static power consumption than a standard 8 T cell at 0. 9 V. Introduction 6 T SRAM Bitcell Design Architecture Summary

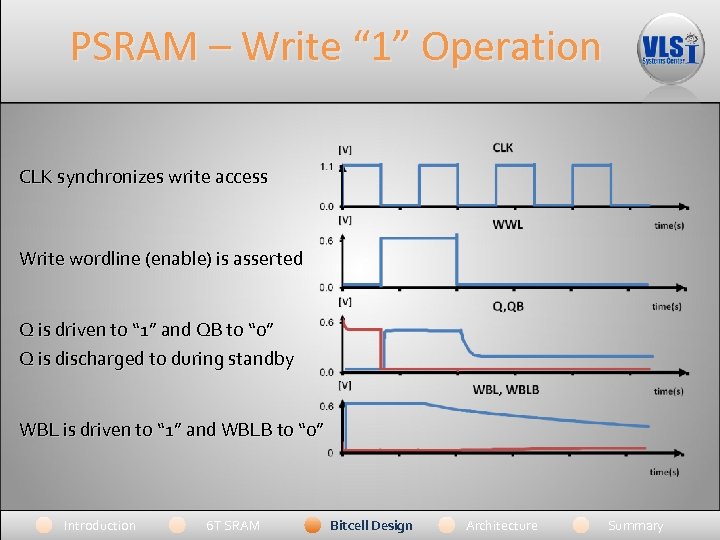

PSRAM – Write “ 1” Operation CLK synchronizes write access Write wordline (enable) is asserted Q is driven to “ 1” and QB to “ 0” Q is discharged to during standby WBL is driven to “ 1” and WBLB to “ 0” Introduction 6 T SRAM Bitcell Design Architecture Summary

PSRAM – Write “ 1” Operation CLK synchronizes write access Write wordline (enable) is asserted Q is driven to “ 1” and QB to “ 0” Q is discharged to during standby WBL is driven to “ 1” and WBLB to “ 0” Introduction 6 T SRAM Bitcell Design Architecture Summary

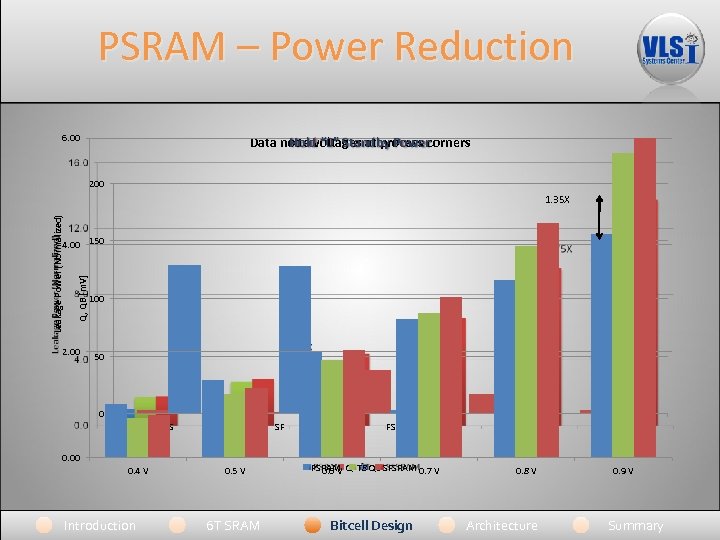

PSRAM – Power Reduction 6. 00 Data node voltages at process corners Hold “ 0" Standby Power 200 Leakage Power (Normalized) 1. 35 X Q, QB [m. V] 4. 00 150 2. 00 100 50 0 SS SF 0. 00 0. 4 V Introduction 0. 5 V 6 T SRAM FS PSRAM Q T 8 QB SFSRAM 0. 7 V 0. 6 V Bitcell Design FF TT 0. 8 V Architecture 0. 9 V Summary

PSRAM – Power Reduction 6. 00 Data node voltages at process corners Hold “ 0" Standby Power 200 Leakage Power (Normalized) 1. 35 X Q, QB [m. V] 4. 00 150 2. 00 100 50 0 SS SF 0. 00 0. 4 V Introduction 0. 5 V 6 T SRAM FS PSRAM Q T 8 QB SFSRAM 0. 7 V 0. 6 V Bitcell Design FF TT 0. 8 V Architecture 0. 9 V Summary

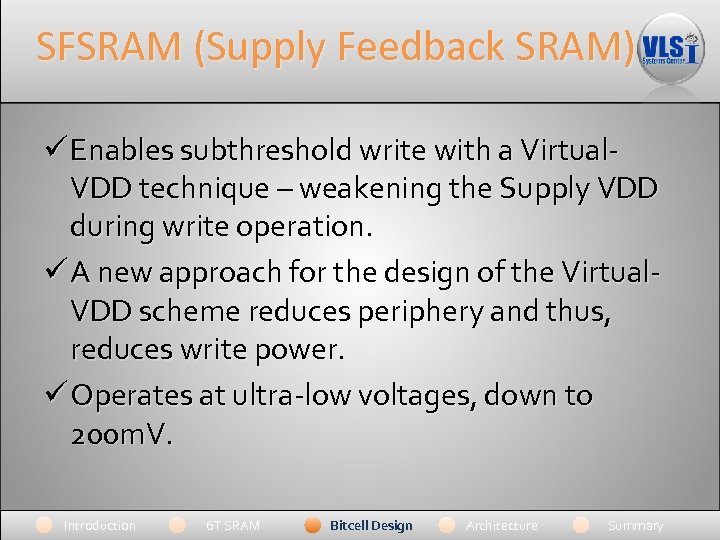

SFSRAM (Supply Feedback SRAM) ü Enables subthreshold write with a Virtual. VDD technique – weakening the Supply VDD during write operation. ü A new approach for the design of the Virtual. VDD scheme reduces periphery and thus, reduces write power. ü Operates at ultra-low voltages, down to 200 m. V. Introduction 6 T SRAM Bitcell Design Architecture Summary

SFSRAM (Supply Feedback SRAM) ü Enables subthreshold write with a Virtual. VDD technique – weakening the Supply VDD during write operation. ü A new approach for the design of the Virtual. VDD scheme reduces periphery and thus, reduces write power. ü Operates at ultra-low voltages, down to 200 m. V. Introduction 6 T SRAM Bitcell Design Architecture Summary

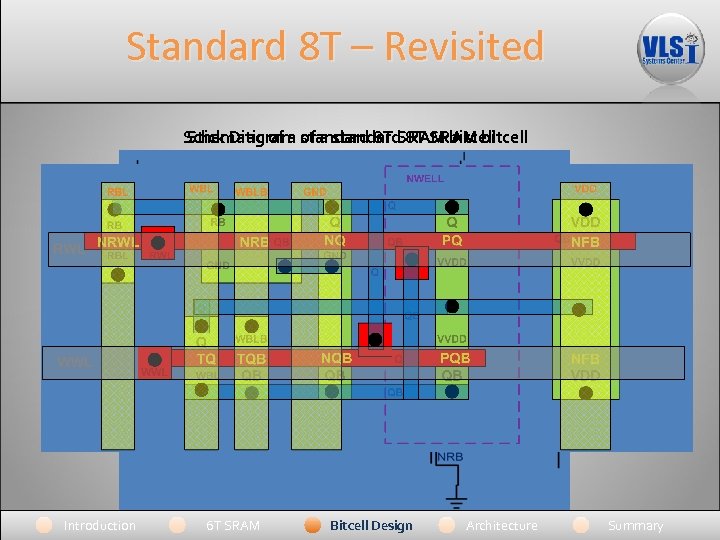

Standard 8 T – Revisited Schematic of a standard 8 T SRAM bitcell Stick Diagram standard 8 T SRAM bitcell Introduction 6 T SRAM Bitcell Design Architecture Summary

Standard 8 T – Revisited Schematic of a standard 8 T SRAM bitcell Stick Diagram standard 8 T SRAM bitcell Introduction 6 T SRAM Bitcell Design Architecture Summary

SFSRAM – Power Reduction Introduction 6 T SRAM Bitcell Design Architecture Summary

SFSRAM – Power Reduction Introduction 6 T SRAM Bitcell Design Architecture Summary

40 NM TEST CHIP Introduction 6 T SRAM Bitcell Design Architecture Summary

40 NM TEST CHIP Introduction 6 T SRAM Bitcell Design Architecture Summary

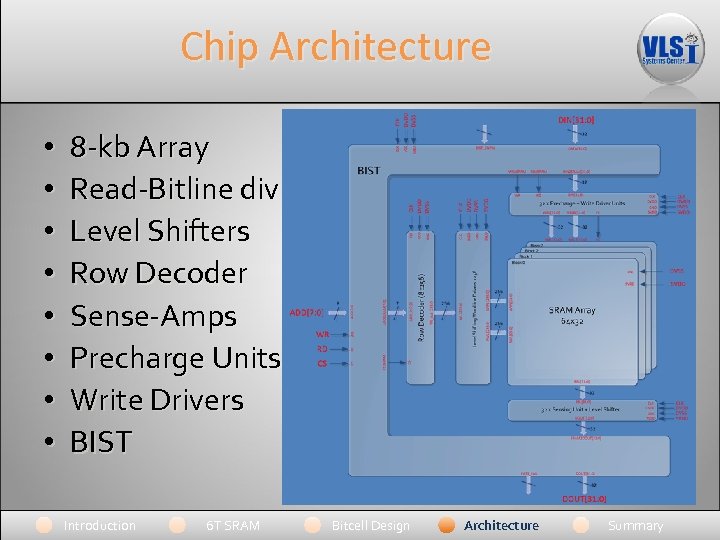

Chip Architecture • • 8 -kb Array Read-Bitline division Level Shifters Row Decoder Sense-Amps Precharge Units Write Drivers BIST Introduction 6 T SRAM Bitcell Design Architecture Summary

Chip Architecture • • 8 -kb Array Read-Bitline division Level Shifters Row Decoder Sense-Amps Precharge Units Write Drivers BIST Introduction 6 T SRAM Bitcell Design Architecture Summary

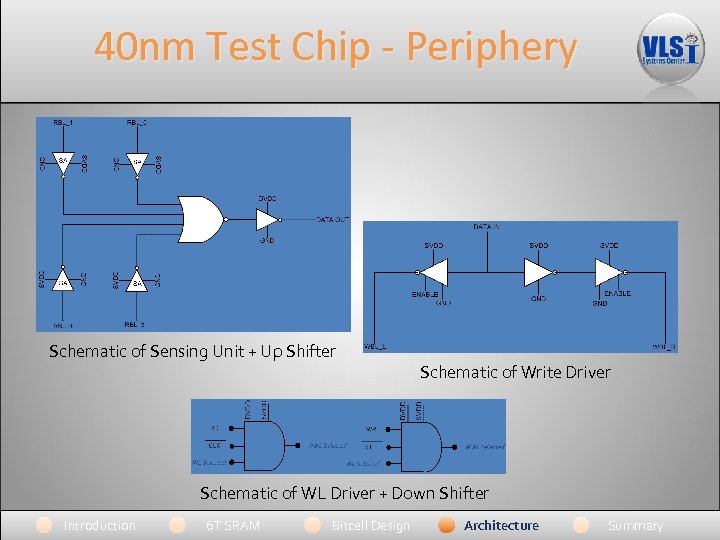

40 nm Test Chip - Periphery Schematic of Sensing Unit + Up Shifter Schematic of Write Driver Schematic of WL Driver + Down Shifter Introduction 6 T SRAM Bitcell Design Architecture Summary

40 nm Test Chip - Periphery Schematic of Sensing Unit + Up Shifter Schematic of Write Driver Schematic of WL Driver + Down Shifter Introduction 6 T SRAM Bitcell Design Architecture Summary

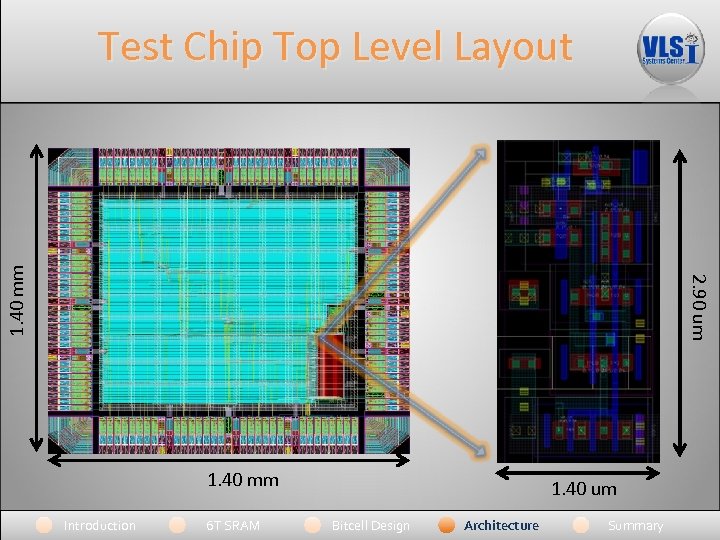

2. 90 um 1. 40 mm Test Chip Top Level Layout 1. 40 mm Introduction 6 T SRAM 1. 40 um Bitcell Design Architecture Summary

2. 90 um 1. 40 mm Test Chip Top Level Layout 1. 40 mm Introduction 6 T SRAM 1. 40 um Bitcell Design Architecture Summary

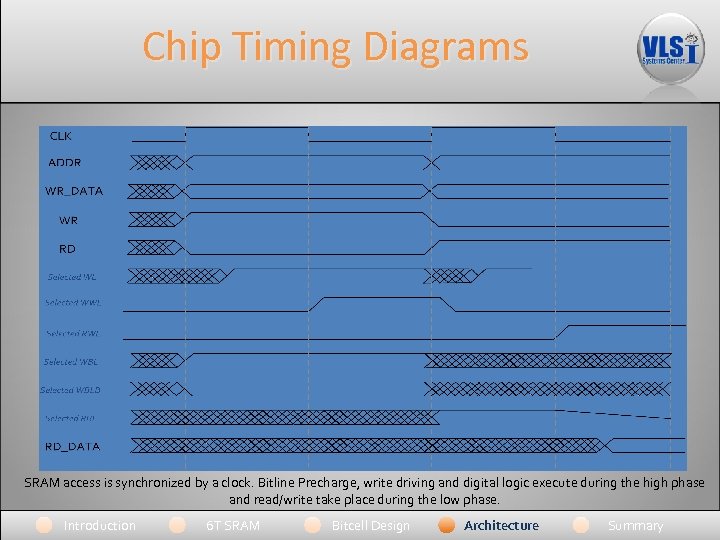

Chip Timing Diagrams SRAM access is synchronized by a clock. Bitline Precharge, write driving and digital logic execute during the high phase and read/write take place during the low phase. Introduction 6 T SRAM Bitcell Design Architecture Summary

Chip Timing Diagrams SRAM access is synchronized by a clock. Bitline Precharge, write driving and digital logic execute during the high phase and read/write take place during the low phase. Introduction 6 T SRAM Bitcell Design Architecture Summary

SUMMARY Introduction 6 T SRAM Bitcell Design Architecture Summary

SUMMARY Introduction 6 T SRAM Bitcell Design Architecture Summary

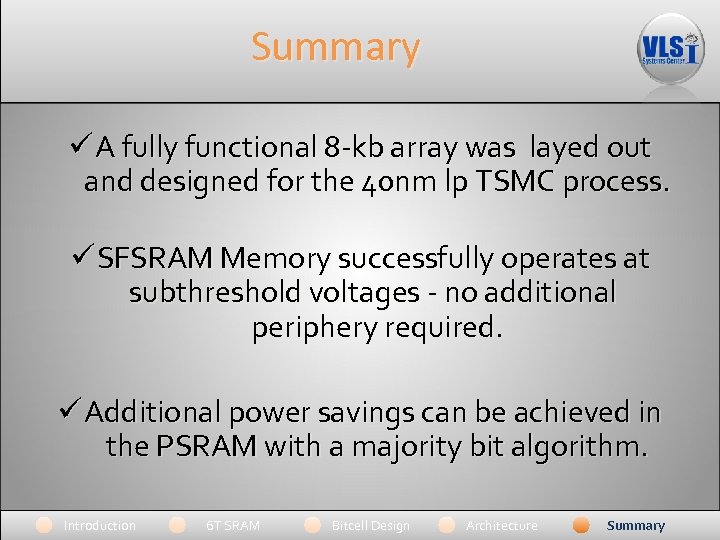

Summary ü A fully functional 8 -kb array was layed out and designed for the 40 nm lp TSMC process. ü SFSRAM Memory successfully operates at subthreshold voltages - no additional periphery required. ü Additional power savings can be achieved in the PSRAM with a majority bit algorithm. Introduction 6 T SRAM Bitcell Design Architecture Summary

Summary ü A fully functional 8 -kb array was layed out and designed for the 40 nm lp TSMC process. ü SFSRAM Memory successfully operates at subthreshold voltages - no additional periphery required. ü Additional power savings can be achieved in the PSRAM with a majority bit algorithm. Introduction 6 T SRAM Bitcell Design Architecture Summary

Summary – Continued ü PSRAM consumes up to 3. 75 X less static power than a standard 8 T cell. ü We Are The first academic research team in Israel to fully design and fabricate a state-of-the-art 40 nm chip. Introduction 6 T SRAM Bitcell Design Architecture Summary

Summary – Continued ü PSRAM consumes up to 3. 75 X less static power than a standard 8 T cell. ü We Are The first academic research team in Israel to fully design and fabricate a state-of-the-art 40 nm chip. Introduction 6 T SRAM Bitcell Design Architecture Summary

Questions? ? Chocolate Chip Digital Chip Introduction 6 T SRAM Bitcell Design Architecture Summary

Questions? ? Chocolate Chip Digital Chip Introduction 6 T SRAM Bitcell Design Architecture Summary