0b049f0e7bcf2b4852272493b3a4ff4d.ppt

- Количество слайдов: 24

LHC Upgrade Workshop CERN, April 2008 SPI – Serial Powering Interface M. Trimpl, Fermilab - SPI Motivation, powering schemes - Chip architecture and features - Assembly, heat dissipation issues - Interface controller, ADC, shunt, Over. Power Protection - Summary and Outlook Joint effort with RAL (M. Weber, G. Villani), UPenn (M. Newcomer, N. Dressnandt) LHC Power Workshop, CERN, 07. 04. 2008 1 Marcel Trimpl, Fermilab

LHC Upgrade Workshop CERN, April 2008 SPI – Serial Powering Interface M. Trimpl, Fermilab - SPI Motivation, powering schemes - Chip architecture and features - Assembly, heat dissipation issues - Interface controller, ADC, shunt, Over. Power Protection - Summary and Outlook Joint effort with RAL (M. Weber, G. Villani), UPenn (M. Newcomer, N. Dressnandt) LHC Power Workshop, CERN, 07. 04. 2008 1 Marcel Trimpl, Fermilab

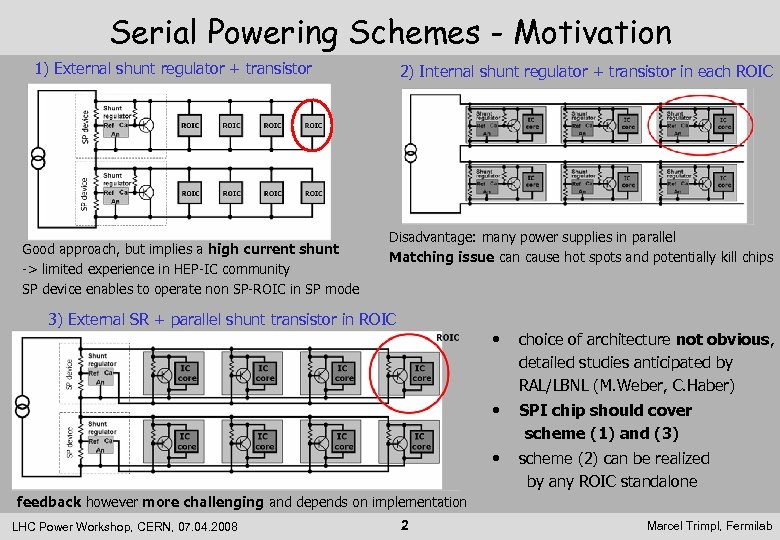

Serial Powering Schemes - Motivation 1) External shunt regulator + transistor Good approach, but implies a high current shunt -> limited experience in HEP-IC community SP device enables to operate non SP-ROIC in SP mode 2) Internal shunt regulator + transistor in each ROIC Disadvantage: many power supplies in parallel Matching issue can cause hot spots and potentially kill chips 3) External SR + parallel shunt transistor in ROIC • choice of architecture not obvious, detailed studies anticipated by RAL/LBNL (M. Weber, C. Haber) • SPI chip should cover scheme (1) and (3) • scheme (2) can be realized by any ROIC standalone feedback however more challenging and depends on implementation LHC Power Workshop, CERN, 07. 04. 2008 2 Marcel Trimpl, Fermilab

Serial Powering Schemes - Motivation 1) External shunt regulator + transistor Good approach, but implies a high current shunt -> limited experience in HEP-IC community SP device enables to operate non SP-ROIC in SP mode 2) Internal shunt regulator + transistor in each ROIC Disadvantage: many power supplies in parallel Matching issue can cause hot spots and potentially kill chips 3) External SR + parallel shunt transistor in ROIC • choice of architecture not obvious, detailed studies anticipated by RAL/LBNL (M. Weber, C. Haber) • SPI chip should cover scheme (1) and (3) • scheme (2) can be realized by any ROIC standalone feedback however more challenging and depends on implementation LHC Power Workshop, CERN, 07. 04. 2008 2 Marcel Trimpl, Fermilab

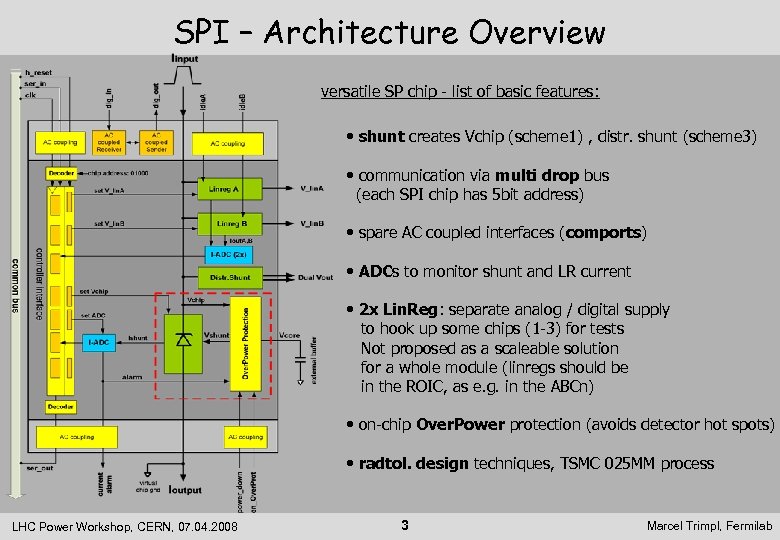

SPI – Architecture Overview versatile SP chip - list of basic features: • shunt creates Vchip (scheme 1) , distr. shunt (scheme 3) • communication via multi drop bus (each SPI chip has 5 bit address) • spare AC coupled interfaces (comports) • ADCs to monitor shunt and LR current • 2 x Lin. Reg: separate analog / digital supply to hook up some chips (1 -3) for tests Not proposed as a scaleable solution for a whole module (linregs should be in the ROIC, as e. g. in the ABCn) • on-chip Over. Power protection (avoids detector hot spots) • radtol. design techniques, TSMC 025 MM process LHC Power Workshop, CERN, 07. 04. 2008 3 Marcel Trimpl, Fermilab

SPI – Architecture Overview versatile SP chip - list of basic features: • shunt creates Vchip (scheme 1) , distr. shunt (scheme 3) • communication via multi drop bus (each SPI chip has 5 bit address) • spare AC coupled interfaces (comports) • ADCs to monitor shunt and LR current • 2 x Lin. Reg: separate analog / digital supply to hook up some chips (1 -3) for tests Not proposed as a scaleable solution for a whole module (linregs should be in the ROIC, as e. g. in the ABCn) • on-chip Over. Power protection (avoids detector hot spots) • radtol. design techniques, TSMC 025 MM process LHC Power Workshop, CERN, 07. 04. 2008 3 Marcel Trimpl, Fermilab

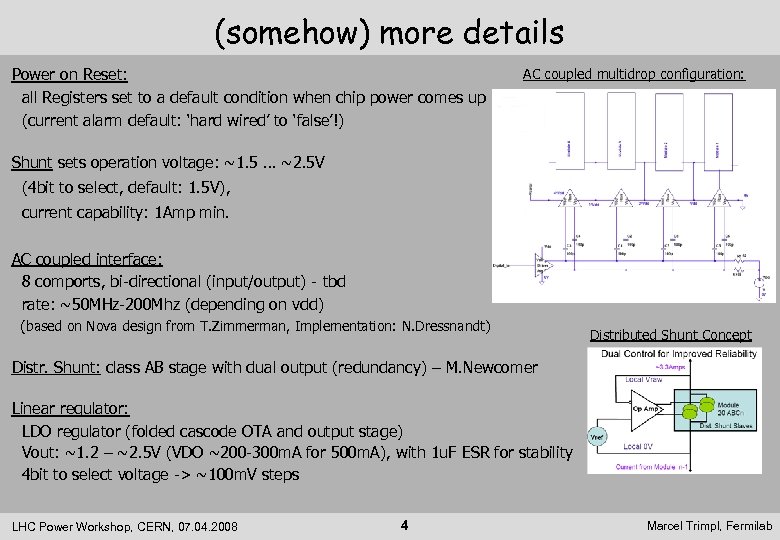

(somehow) more details Power on Reset: all Registers set to a default condition when chip power comes up (current alarm default: ‘hard wired’ to ‘false’!) AC coupled multidrop configuration: Shunt sets operation voltage: ~1. 5 … ~2. 5 V (4 bit to select, default: 1. 5 V), current capability: 1 Amp min. AC coupled interface: 8 comports, bi-directional (input/output) - tbd rate: ~50 MHz-200 Mhz (depending on vdd) (based on Nova design from T. Zimmerman, Implementation: N. Dressnandt) Distributed Shunt Concept Distr. Shunt: class AB stage with dual output (redundancy) – M. Newcomer Linear regulator: LDO regulator (folded cascode OTA and output stage) Vout: ~1. 2 – ~2. 5 V (VDO ~200 -300 m. A for 500 m. A), with 1 u. F ESR for stability 4 bit to select voltage -> ~100 m. V steps LHC Power Workshop, CERN, 07. 04. 2008 4 Marcel Trimpl, Fermilab

(somehow) more details Power on Reset: all Registers set to a default condition when chip power comes up (current alarm default: ‘hard wired’ to ‘false’!) AC coupled multidrop configuration: Shunt sets operation voltage: ~1. 5 … ~2. 5 V (4 bit to select, default: 1. 5 V), current capability: 1 Amp min. AC coupled interface: 8 comports, bi-directional (input/output) - tbd rate: ~50 MHz-200 Mhz (depending on vdd) (based on Nova design from T. Zimmerman, Implementation: N. Dressnandt) Distributed Shunt Concept Distr. Shunt: class AB stage with dual output (redundancy) – M. Newcomer Linear regulator: LDO regulator (folded cascode OTA and output stage) Vout: ~1. 2 – ~2. 5 V (VDO ~200 -300 m. A for 500 m. A), with 1 u. F ESR for stability 4 bit to select voltage -> ~100 m. V steps LHC Power Workshop, CERN, 07. 04. 2008 4 Marcel Trimpl, Fermilab

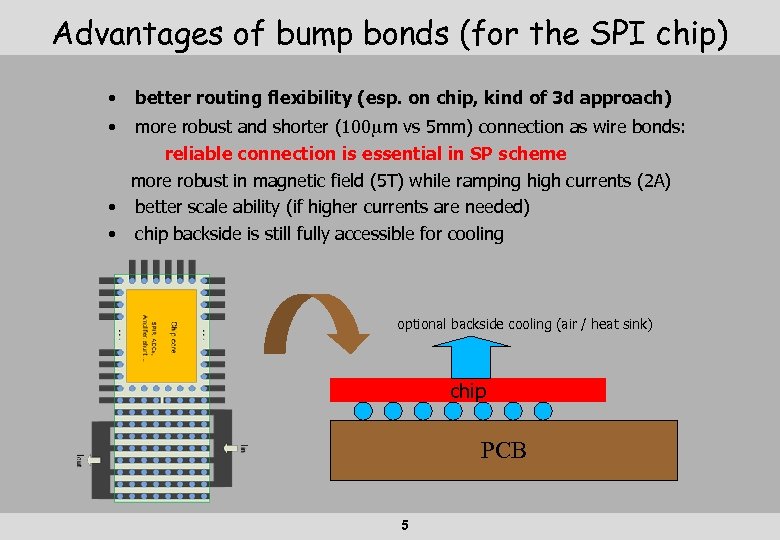

Advantages of bump bonds (for the SPI chip) • better routing flexibility (esp. on chip, kind of 3 d approach) • more robust and shorter (100 mm vs 5 mm) connection as wire bonds: reliable connection is essential in SP scheme more robust in magnetic field (5 T) while ramping high currents (2 A) • better scale ability (if higher currents are needed) • chip backside is still fully accessible for cooling optional backside cooling (air / heat sink) chip PCB 5

Advantages of bump bonds (for the SPI chip) • better routing flexibility (esp. on chip, kind of 3 d approach) • more robust and shorter (100 mm vs 5 mm) connection as wire bonds: reliable connection is essential in SP scheme more robust in magnetic field (5 T) while ramping high currents (2 A) • better scale ability (if higher currents are needed) • chip backside is still fully accessible for cooling optional backside cooling (air / heat sink) chip PCB 5

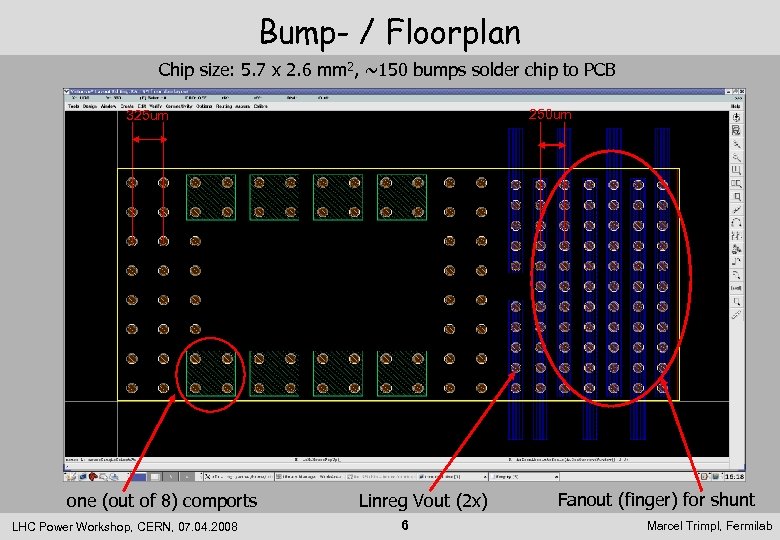

Bump- / Floorplan Chip size: 5. 7 x 2. 6 mm 2, ~150 bumps solder chip to PCB 250 um 325 um one (out of 8) comports LHC Power Workshop, CERN, 07. 04. 2008 Linreg Vout (2 x) 6 Fanout (finger) for shunt Marcel Trimpl, Fermilab

Bump- / Floorplan Chip size: 5. 7 x 2. 6 mm 2, ~150 bumps solder chip to PCB 250 um 325 um one (out of 8) comports LHC Power Workshop, CERN, 07. 04. 2008 Linreg Vout (2 x) 6 Fanout (finger) for shunt Marcel Trimpl, Fermilab

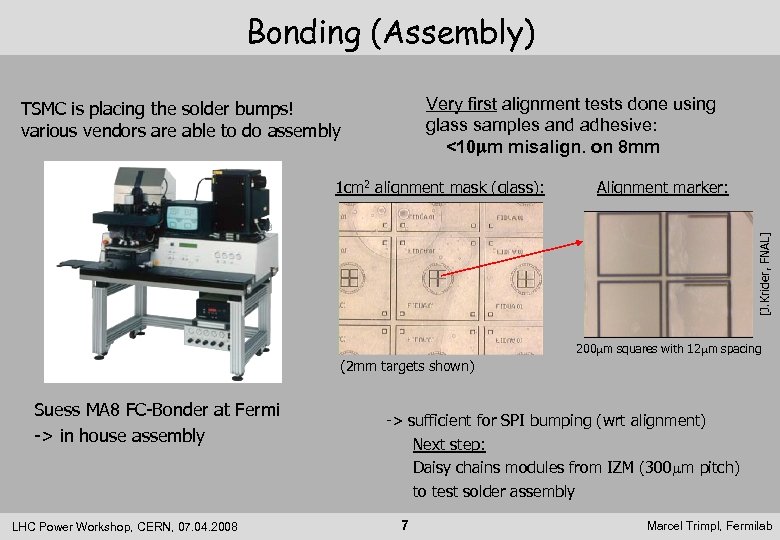

Bonding (Assembly) Very first alignment tests done using glass samples and adhesive: <10 mm misalign. on 8 mm TSMC is placing the solder bumps! various vendors are able to do assembly Alignment marker: [J. Krider, FNAL] 1 cm 2 alignment mask (glass): 200 mm squares with 12 mm spacing (2 mm targets shown) Suess MA 8 FC-Bonder at Fermi -> in house assembly LHC Power Workshop, CERN, 07. 04. 2008 -> sufficient for SPI bumping (wrt alignment) Next step: Daisy chains modules from IZM (300 mm pitch) to test solder assembly 7 Marcel Trimpl, Fermilab

Bonding (Assembly) Very first alignment tests done using glass samples and adhesive: <10 mm misalign. on 8 mm TSMC is placing the solder bumps! various vendors are able to do assembly Alignment marker: [J. Krider, FNAL] 1 cm 2 alignment mask (glass): 200 mm squares with 12 mm spacing (2 mm targets shown) Suess MA 8 FC-Bonder at Fermi -> in house assembly LHC Power Workshop, CERN, 07. 04. 2008 -> sufficient for SPI bumping (wrt alignment) Next step: Daisy chains modules from IZM (300 mm pitch) to test solder assembly 7 Marcel Trimpl, Fermilab

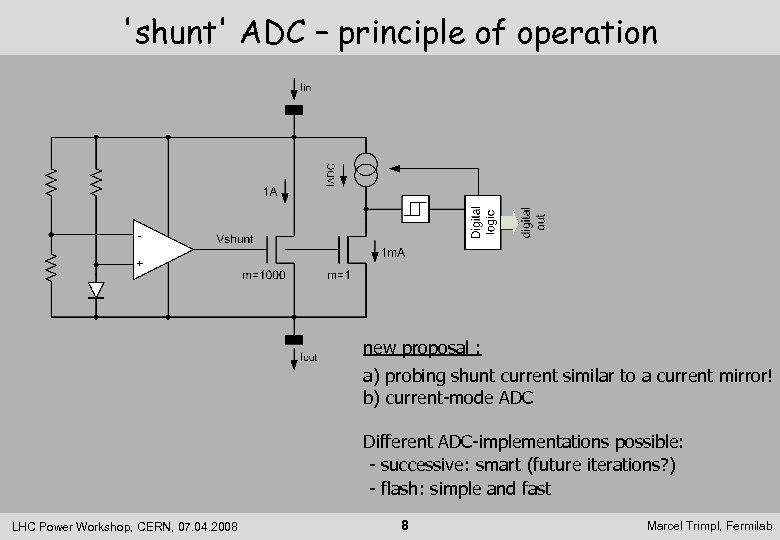

'shunt' ADC – principle of operation new proposal : a) probing shunt current similar to a current mirror! b) current-mode ADC Different ADC-implementations possible: - successive: smart (future iterations? ) - flash: simple and fast LHC Power Workshop, CERN, 07. 04. 2008 8 Marcel Trimpl, Fermilab

'shunt' ADC – principle of operation new proposal : a) probing shunt current similar to a current mirror! b) current-mode ADC Different ADC-implementations possible: - successive: smart (future iterations? ) - flash: simple and fast LHC Power Workshop, CERN, 07. 04. 2008 8 Marcel Trimpl, Fermilab

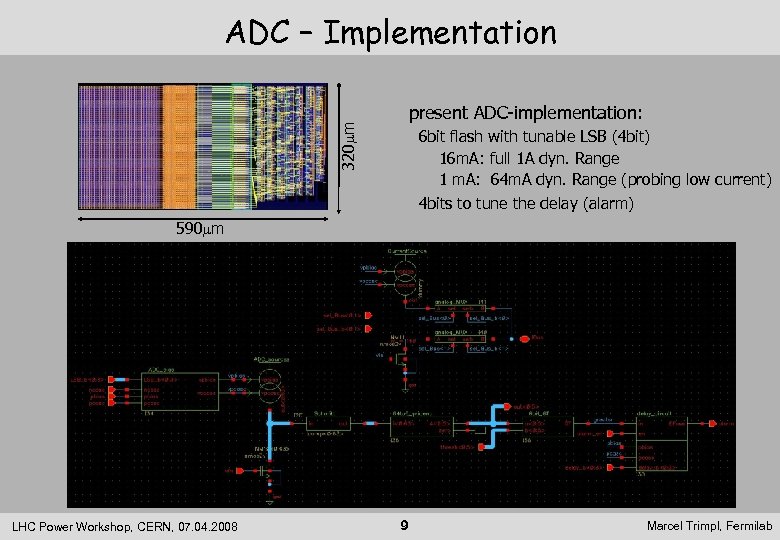

320 mm ADC – Implementation present ADC-implementation: 6 bit flash with tunable LSB (4 bit) 16 m. A: full 1 A dyn. Range 1 m. A: 64 m. A dyn. Range (probing low current) 4 bits to tune the delay (alarm) 590 mm LHC Power Workshop, CERN, 07. 04. 2008 9 Marcel Trimpl, Fermilab

320 mm ADC – Implementation present ADC-implementation: 6 bit flash with tunable LSB (4 bit) 16 m. A: full 1 A dyn. Range 1 m. A: 64 m. A dyn. Range (probing low current) 4 bits to tune the delay (alarm) 590 mm LHC Power Workshop, CERN, 07. 04. 2008 9 Marcel Trimpl, Fermilab

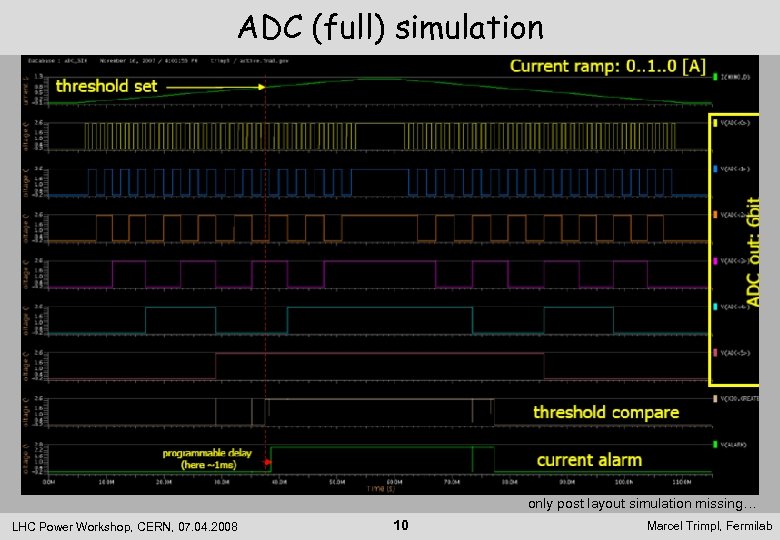

ADC (full) simulation only post layout simulation missing… LHC Power Workshop, CERN, 07. 04. 2008 10 Marcel Trimpl, Fermilab

ADC (full) simulation only post layout simulation missing… LHC Power Workshop, CERN, 07. 04. 2008 10 Marcel Trimpl, Fermilab

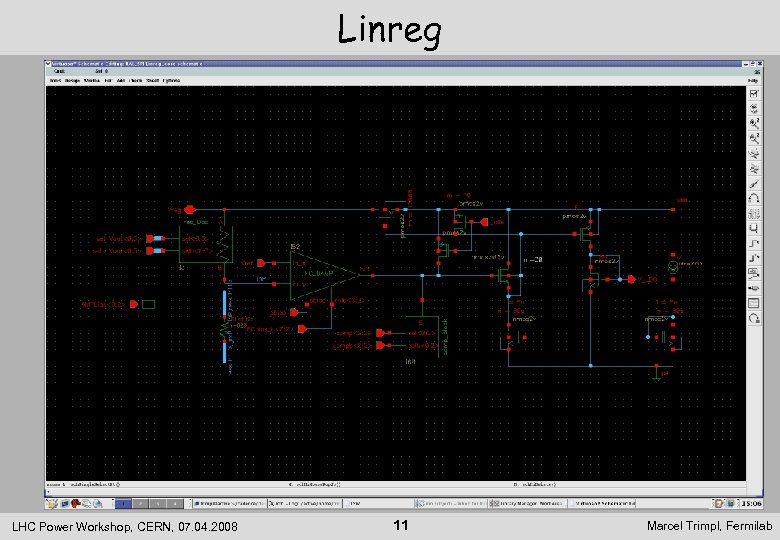

Linreg LHC Power Workshop, CERN, 07. 04. 2008 11 Marcel Trimpl, Fermilab

Linreg LHC Power Workshop, CERN, 07. 04. 2008 11 Marcel Trimpl, Fermilab

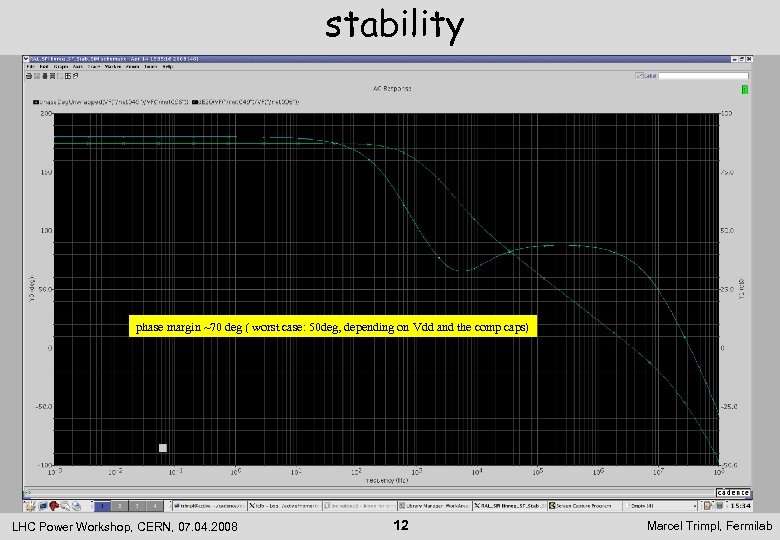

stability phase margin ~70 deg ( worst case: 50 deg, depending on Vdd and the comp caps) LHC Power Workshop, CERN, 07. 04. 2008 12 Marcel Trimpl, Fermilab

stability phase margin ~70 deg ( worst case: 50 deg, depending on Vdd and the comp caps) LHC Power Workshop, CERN, 07. 04. 2008 12 Marcel Trimpl, Fermilab

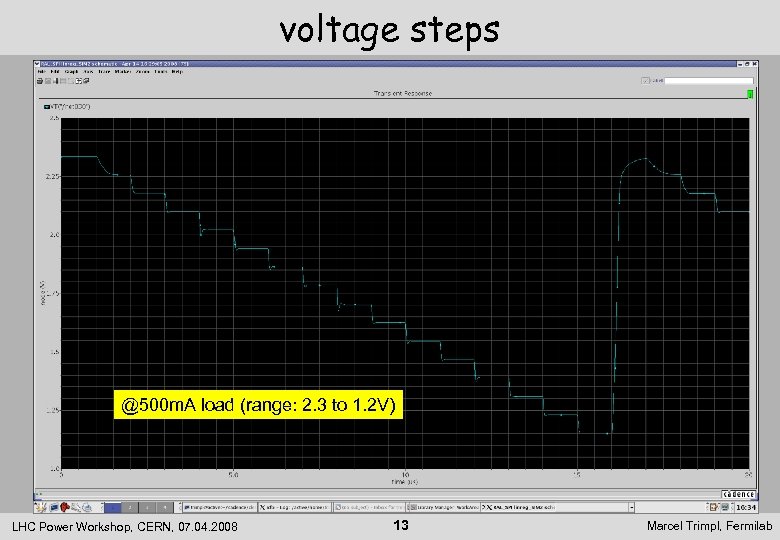

voltage steps @500 m. A load (range: 2. 3 to 1. 2 V) LHC Power Workshop, CERN, 07. 04. 2008 13 Marcel Trimpl, Fermilab

voltage steps @500 m. A load (range: 2. 3 to 1. 2 V) LHC Power Workshop, CERN, 07. 04. 2008 13 Marcel Trimpl, Fermilab

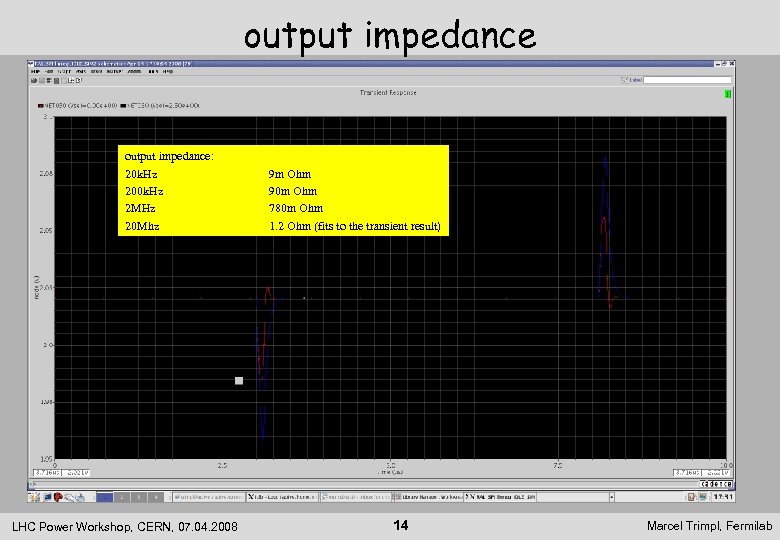

output impedance: 20 k. Hz 200 k. Hz 2 MHz 20 Mhz LHC Power Workshop, CERN, 07. 04. 2008 9 m Ohm 90 m Ohm 780 m Ohm 1. 2 Ohm (fits to the transient result) 14 Marcel Trimpl, Fermilab

output impedance: 20 k. Hz 200 k. Hz 2 MHz 20 Mhz LHC Power Workshop, CERN, 07. 04. 2008 9 m Ohm 90 m Ohm 780 m Ohm 1. 2 Ohm (fits to the transient result) 14 Marcel Trimpl, Fermilab

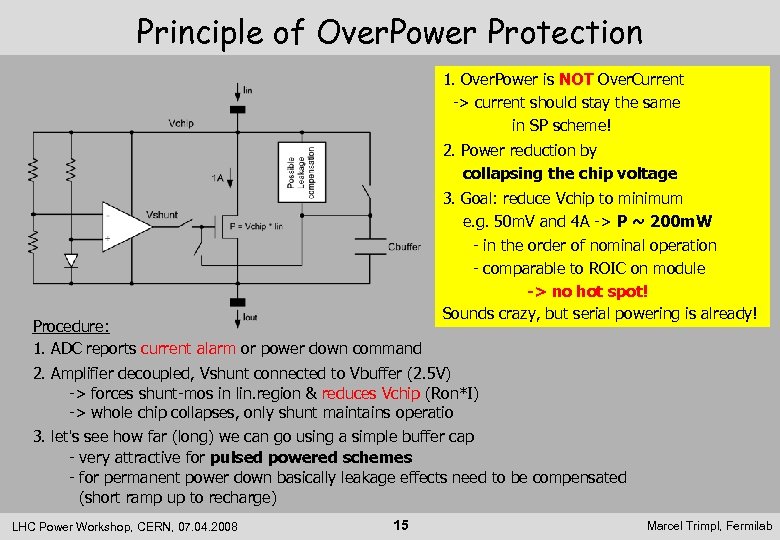

Principle of Over. Power Protection 1. Over. Power is NOT Over. Current -> current should stay the same in SP scheme! 2. Power reduction by collapsing the chip voltage Procedure: 1. ADC reports current alarm or power down command 3. Goal: reduce Vchip to minimum e. g. 50 m. V and 4 A -> P ~ 200 m. W - in the order of nominal operation - comparable to ROIC on module -> no hot spot! Sounds crazy, but serial powering is already! 2. Amplifier decoupled, Vshunt connected to Vbuffer (2. 5 V) -> forces shunt-mos in lin. region & reduces Vchip (Ron*I) -> whole chip collapses, only shunt maintains operatio 3. let's see how far (long) we can go using a simple buffer cap - very attractive for pulsed powered schemes - for permanent power down basically leakage effects need to be compensated (short ramp up to recharge) LHC Power Workshop, CERN, 07. 04. 2008 15 Marcel Trimpl, Fermilab

Principle of Over. Power Protection 1. Over. Power is NOT Over. Current -> current should stay the same in SP scheme! 2. Power reduction by collapsing the chip voltage Procedure: 1. ADC reports current alarm or power down command 3. Goal: reduce Vchip to minimum e. g. 50 m. V and 4 A -> P ~ 200 m. W - in the order of nominal operation - comparable to ROIC on module -> no hot spot! Sounds crazy, but serial powering is already! 2. Amplifier decoupled, Vshunt connected to Vbuffer (2. 5 V) -> forces shunt-mos in lin. region & reduces Vchip (Ron*I) -> whole chip collapses, only shunt maintains operatio 3. let's see how far (long) we can go using a simple buffer cap - very attractive for pulsed powered schemes - for permanent power down basically leakage effects need to be compensated (short ramp up to recharge) LHC Power Workshop, CERN, 07. 04. 2008 15 Marcel Trimpl, Fermilab

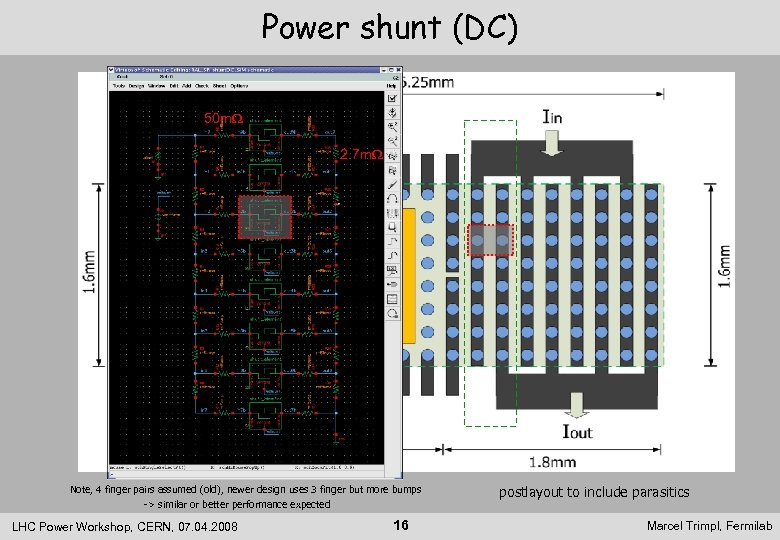

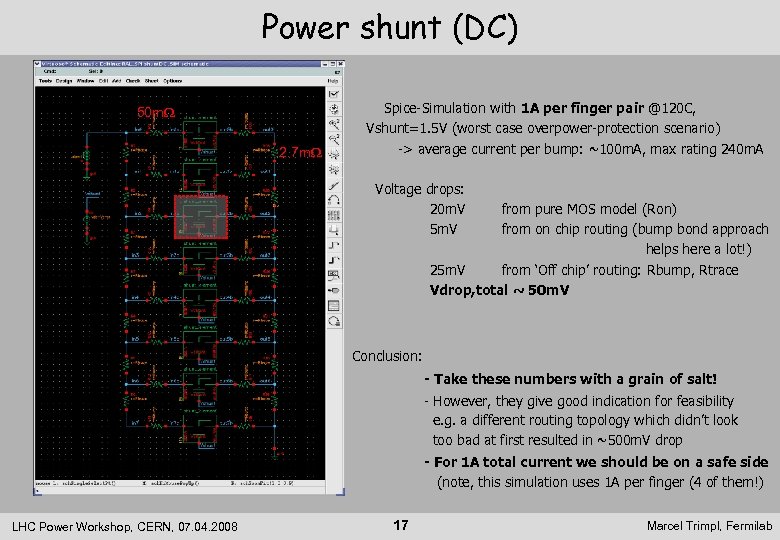

Power shunt (DC) 50 m. W 2. 7 m. W Note, 4 finger pairs assumed (old), newer design uses 3 finger but more bumps -> similar or better performance expected LHC Power Workshop, CERN, 07. 04. 2008 16 postlayout to include parasitics Marcel Trimpl, Fermilab

Power shunt (DC) 50 m. W 2. 7 m. W Note, 4 finger pairs assumed (old), newer design uses 3 finger but more bumps -> similar or better performance expected LHC Power Workshop, CERN, 07. 04. 2008 16 postlayout to include parasitics Marcel Trimpl, Fermilab

Power shunt (DC) 50 m. W 2. 7 m. W Spice-Simulation with 1 A per finger pair @120 C, Vshunt=1. 5 V (worst case overpower-protection scenario) -> average current per bump: ~100 m. A, max rating 240 m. A Voltage drops: 20 m. V 5 m. V from pure MOS model (Ron) from on chip routing (bump bond approach helps here a lot!) 25 m. V from ‘Off chip’ routing: Rbump, Rtrace Vdrop, total ~ 50 m. V Conclusion: - Take these numbers with a grain of salt! - However, they give good indication for feasibility e. g. a different routing topology which didn’t look too bad at first resulted in ~500 m. V drop - For 1 A total current we should be on a safe side (note, this simulation uses 1 A per finger (4 of them!) LHC Power Workshop, CERN, 07. 04. 2008 17 Marcel Trimpl, Fermilab

Power shunt (DC) 50 m. W 2. 7 m. W Spice-Simulation with 1 A per finger pair @120 C, Vshunt=1. 5 V (worst case overpower-protection scenario) -> average current per bump: ~100 m. A, max rating 240 m. A Voltage drops: 20 m. V 5 m. V from pure MOS model (Ron) from on chip routing (bump bond approach helps here a lot!) 25 m. V from ‘Off chip’ routing: Rbump, Rtrace Vdrop, total ~ 50 m. V Conclusion: - Take these numbers with a grain of salt! - However, they give good indication for feasibility e. g. a different routing topology which didn’t look too bad at first resulted in ~500 m. V drop - For 1 A total current we should be on a safe side (note, this simulation uses 1 A per finger (4 of them!) LHC Power Workshop, CERN, 07. 04. 2008 17 Marcel Trimpl, Fermilab

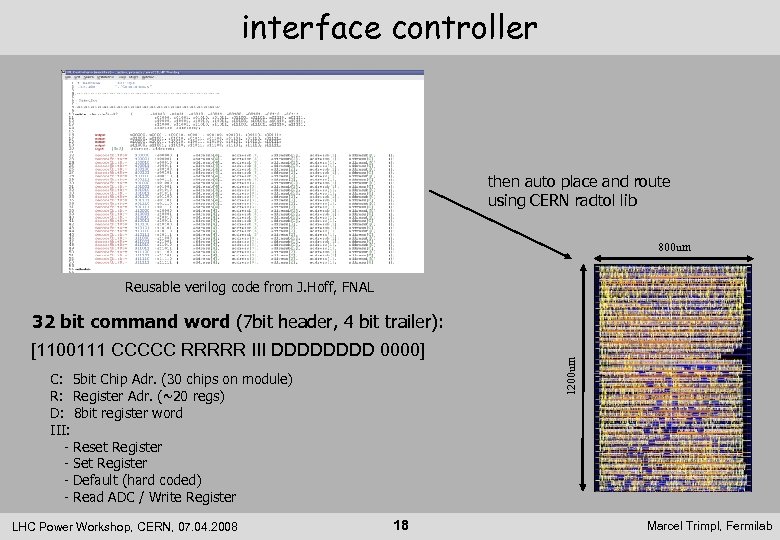

interface controller then auto place and route using CERN radtol lib 800 um Reusable verilog code from J. Hoff, FNAL [1100111 CCCCC RRRRR III DDDD 0000] C: 5 bit Chip Adr. (30 chips on module) R: Register Adr. (~20 regs) D: 8 bit register word III: - Reset Register - Set Register - Default (hard coded) - Read ADC / Write Register LHC Power Workshop, CERN, 07. 04. 2008 18 1200 um 32 bit command word (7 bit header, 4 bit trailer): Marcel Trimpl, Fermilab

interface controller then auto place and route using CERN radtol lib 800 um Reusable verilog code from J. Hoff, FNAL [1100111 CCCCC RRRRR III DDDD 0000] C: 5 bit Chip Adr. (30 chips on module) R: Register Adr. (~20 regs) D: 8 bit register word III: - Reset Register - Set Register - Default (hard coded) - Read ADC / Write Register LHC Power Workshop, CERN, 07. 04. 2008 18 1200 um 32 bit command word (7 bit header, 4 bit trailer): Marcel Trimpl, Fermilab

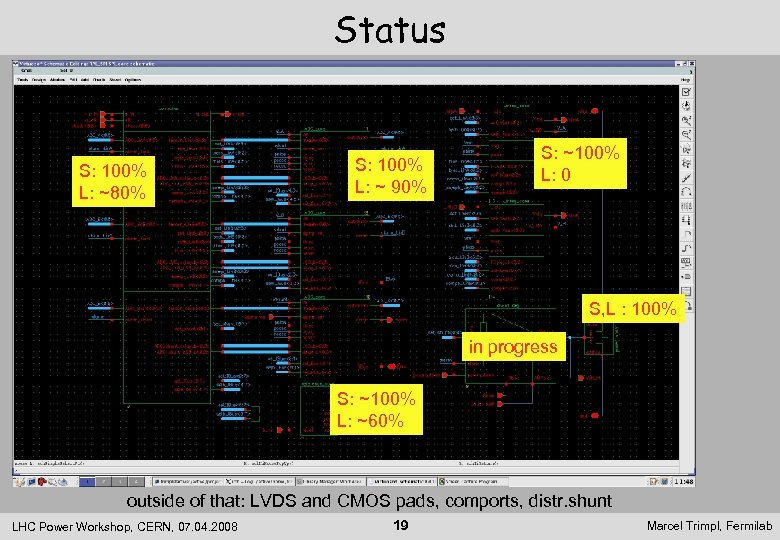

Status S: 100% L: ~80% S: 100% L: ~ 90% S: ~100% L: 0 S, L : 100% in progress S: ~100% L: ~60% outside of that: LVDS and CMOS pads, comports, distr. shunt LHC Power Workshop, CERN, 07. 04. 2008 19 Marcel Trimpl, Fermilab

Status S: 100% L: ~80% S: 100% L: ~ 90% S: ~100% L: 0 S, L : 100% in progress S: ~100% L: ~60% outside of that: LVDS and CMOS pads, comports, distr. shunt LHC Power Workshop, CERN, 07. 04. 2008 19 Marcel Trimpl, Fermilab

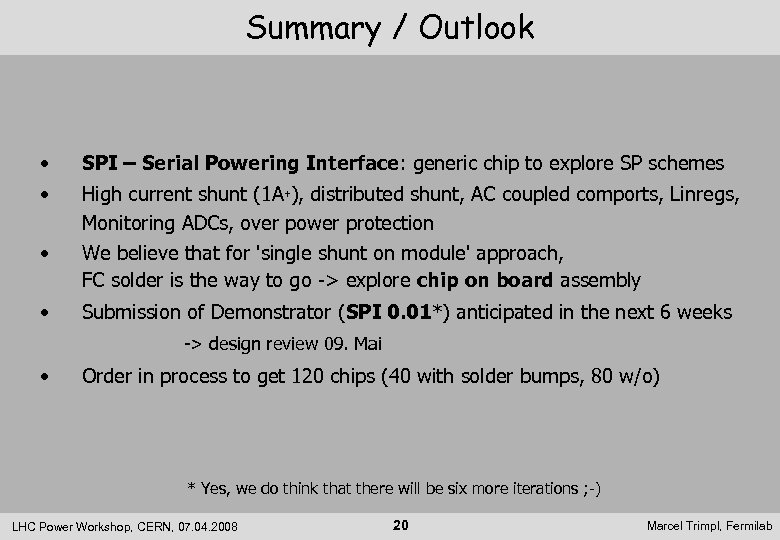

Summary / Outlook • SPI – Serial Powering Interface: generic chip to explore SP schemes • High current shunt (1 A+), distributed shunt, AC coupled comports, Linregs, Monitoring ADCs, over power protection We believe that for 'single shunt on module' approach, FC solder is the way to go -> explore chip on board assembly • • Submission of Demonstrator (SPI 0. 01*) anticipated in the next 6 weeks -> design review 09. Mai • Order in process to get 120 chips (40 with solder bumps, 80 w/o) * Yes, we do think that there will be six more iterations ; -) LHC Power Workshop, CERN, 07. 04. 2008 20 Marcel Trimpl, Fermilab

Summary / Outlook • SPI – Serial Powering Interface: generic chip to explore SP schemes • High current shunt (1 A+), distributed shunt, AC coupled comports, Linregs, Monitoring ADCs, over power protection We believe that for 'single shunt on module' approach, FC solder is the way to go -> explore chip on board assembly • • Submission of Demonstrator (SPI 0. 01*) anticipated in the next 6 weeks -> design review 09. Mai • Order in process to get 120 chips (40 with solder bumps, 80 w/o) * Yes, we do think that there will be six more iterations ; -) LHC Power Workshop, CERN, 07. 04. 2008 20 Marcel Trimpl, Fermilab

Backup Slides LHC Power Workshop, CERN, 07. 04. 2008 21 Marcel Trimpl, Fermilab

Backup Slides LHC Power Workshop, CERN, 07. 04. 2008 21 Marcel Trimpl, Fermilab

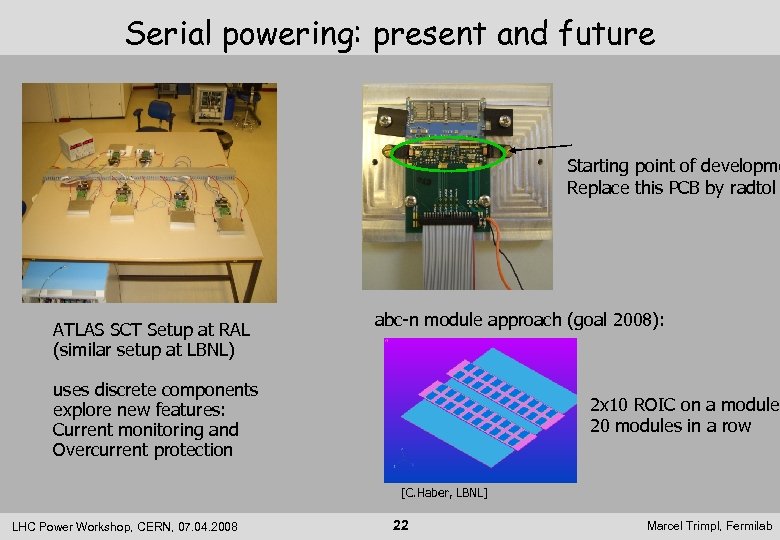

Serial powering: present and future Starting point of developme Replace this PCB by radtol ATLAS SCT Setup at RAL (similar setup at LBNL) abc-n module approach (goal 2008): uses discrete components explore new features: Current monitoring and Overcurrent protection 2 x 10 ROIC on a module 20 modules in a row [C. Haber, LBNL] LHC Power Workshop, CERN, 07. 04. 2008 22 Marcel Trimpl, Fermilab

Serial powering: present and future Starting point of developme Replace this PCB by radtol ATLAS SCT Setup at RAL (similar setup at LBNL) abc-n module approach (goal 2008): uses discrete components explore new features: Current monitoring and Overcurrent protection 2 x 10 ROIC on a module 20 modules in a row [C. Haber, LBNL] LHC Power Workshop, CERN, 07. 04. 2008 22 Marcel Trimpl, Fermilab

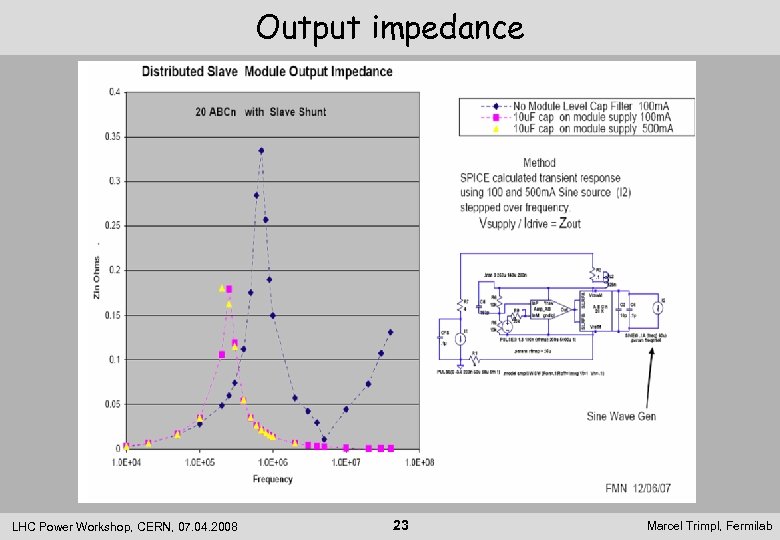

Output impedance LHC Power Workshop, CERN, 07. 04. 2008 23 Marcel Trimpl, Fermilab

Output impedance LHC Power Workshop, CERN, 07. 04. 2008 23 Marcel Trimpl, Fermilab

Some numbers… - Lorentz Force: B=5 T, L(bump)=100 um, Imax = 2 A / 20 = 100 m. A Fmax = q v B = L I B = 50 u. N - Thermal conductivity: Si: 150, Sn: 67, Pb: 35, Au: 320, Ag: 430 [W per m and K] LHC Power Workshop, CERN, 07. 04. 2008 24 Marcel Trimpl, Fermilab

Some numbers… - Lorentz Force: B=5 T, L(bump)=100 um, Imax = 2 A / 20 = 100 m. A Fmax = q v B = L I B = 50 u. N - Thermal conductivity: Si: 150, Sn: 67, Pb: 35, Au: 320, Ag: 430 [W per m and K] LHC Power Workshop, CERN, 07. 04. 2008 24 Marcel Trimpl, Fermilab