S_T.ppt

- Количество слайдов: 34

Лекція СКЕЗ S/T-модуль (просторовочасова– комутація)

Лекція СКЕЗ S/T-модуль (просторовочасова– комутація)

S/T-МОДУЛЬ • БЛОК ЩО РЕАЛІЗУЄ ПРОСТОРОВОЧАСОВЕ ПЕРЕТВОРЕННЯ КООРДИНАТ ЦИФРОВОГО СИГНАЛУ, НАЗИВАЄТЬСЯ S/T-МОДУЛЕМ. (ступнею просторово-часової– комутації)

S/T-МОДУЛЬ • БЛОК ЩО РЕАЛІЗУЄ ПРОСТОРОВОЧАСОВЕ ПЕРЕТВОРЕННЯ КООРДИНАТ ЦИФРОВОГО СИГНАЛУ, НАЗИВАЄТЬСЯ S/T-МОДУЛЕМ. (ступнею просторово-часової– комутації)

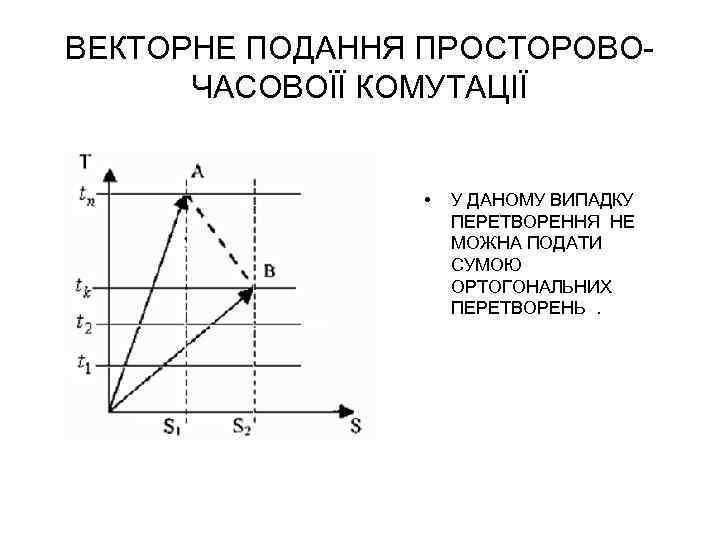

ВЕКТОРНЕ ПОДАННЯ ПРОСТОРОВОЧАСОВОЇЇ КОМУТАЦІЇ • У ДАНОМУ ВИПАДКУ ПЕРЕТВОРЕННЯ НЕ МОЖНА ПОДАТИ СУМОЮ ОРТОГОНАЛЬНИХ ПЕРЕТВОРЕНЬ .

ВЕКТОРНЕ ПОДАННЯ ПРОСТОРОВОЧАСОВОЇЇ КОМУТАЦІЇ • У ДАНОМУ ВИПАДКУ ПЕРЕТВОРЕННЯ НЕ МОЖНА ПОДАТИ СУМОЮ ОРТОГОНАЛЬНИХ ПЕРЕТВОРЕНЬ .

ІЛЮСТРАЦІЯ ПРИНЦИПУ ПРОСТОРОВОЧАСОВОЇ КОМУТАЦІЇ

ІЛЮСТРАЦІЯ ПРИНЦИПУ ПРОСТОРОВОЧАСОВОЇ КОМУТАЦІЇ

ПРИНЦИП ПРОСТОРОВОЧАСОВОЇ КОМУТАЦІЇ • Усі сигнали ІКМ ліній синхронізовані по циклах. Відповідно до адресної інформації, що надходить в керуючий пристрій блоку в шістнадцятому канальному інтервалі, необхідно встановити з'єднання абонента А з абонентом В. В адресі зазначено, що мовна інформація від абонента А передається в i-му канальному інтервалі ІКМ лінії 1, а абоненту В наданий j-й канальний інтервал ІКМ лінії 2. Принцип просторово-часової комутації канальних інтервалів і в прямому і зворотному напрямках ілюструє рисунок плакат 3. Як видно з рисунка для передавання інформації з i-го канального інтервалу ІКМ лінії 1 в j-й канальний інтервал ІКМ лінії 2 (від абонента А до абоненту В) необхідно затримати цю інформацію на час У той же час, сигнал переданий у j-му канальному інтервалі лінії 2, повинний бути затриманий на час • і переданий у i-му канальному інтервалі наступного циклу лінії 1. Таким чином, передача мовної інформації в прямому і зворотному напрямках повинна відбуватися в різних циклах.

ПРИНЦИП ПРОСТОРОВОЧАСОВОЇ КОМУТАЦІЇ • Усі сигнали ІКМ ліній синхронізовані по циклах. Відповідно до адресної інформації, що надходить в керуючий пристрій блоку в шістнадцятому канальному інтервалі, необхідно встановити з'єднання абонента А з абонентом В. В адресі зазначено, що мовна інформація від абонента А передається в i-му канальному інтервалі ІКМ лінії 1, а абоненту В наданий j-й канальний інтервал ІКМ лінії 2. Принцип просторово-часової комутації канальних інтервалів і в прямому і зворотному напрямках ілюструє рисунок плакат 3. Як видно з рисунка для передавання інформації з i-го канального інтервалу ІКМ лінії 1 в j-й канальний інтервал ІКМ лінії 2 (від абонента А до абоненту В) необхідно затримати цю інформацію на час У той же час, сигнал переданий у j-му канальному інтервалі лінії 2, повинний бути затриманий на час • і переданий у i-му канальному інтервалі наступного циклу лінії 1. Таким чином, передача мовної інформації в прямому і зворотному напрямках повинна відбуватися в різних циклах.

СТРУКТУРНІ ПАРАМЕТРИ • Структурними параметрами S/T-модуля є число n вхідних цифрових ліній із с1 часовими канальними інтервалами кожна, а також число m вихідних цифрових ліній із с2 часовими канальними інтервалами кожна – S/T: (n/c 1) x (m/c 2). • Можливі кілька способів побудови S/T-модулів. Найбільш часто застосовуються три основних: координатний спосіб побудови; використання мультиплексорів і демультиплексорів; використання кільцевих з'єднувачів.

СТРУКТУРНІ ПАРАМЕТРИ • Структурними параметрами S/T-модуля є число n вхідних цифрових ліній із с1 часовими канальними інтервалами кожна, а також число m вихідних цифрових ліній із с2 часовими канальними інтервалами кожна – S/T: (n/c 1) x (m/c 2). • Можливі кілька способів побудови S/T-модулів. Найбільш часто застосовуються три основних: координатний спосіб побудови; використання мультиплексорів і демультиплексорів; використання кільцевих з'єднувачів.

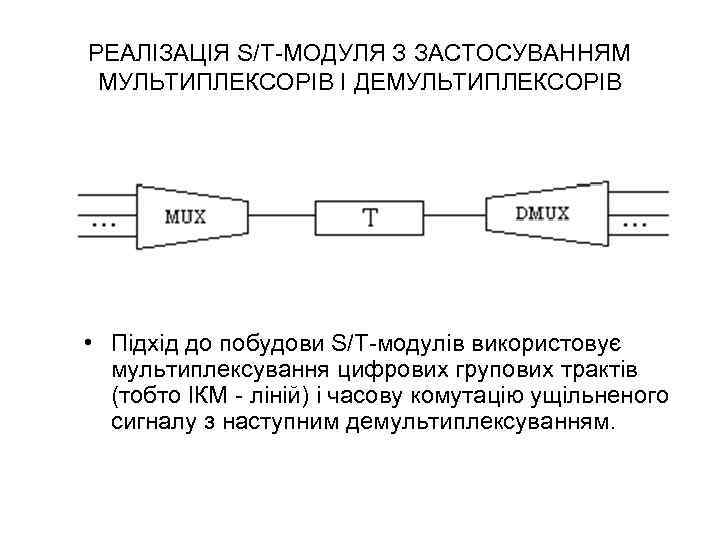

РЕАЛІЗАЦІЯ S/T-МОДУЛЯ З ЗАСТОСУВАННЯМ МУЛЬТИПЛЕКСОРІВ І ДЕМУЛЬТИПЛЕКСОРІВ • Підхід до побудови S/T-модулів використовує мультиплексування цифрових групових трактів (тобто ІКМ - ліній) і часову комутацію ущільненого сигналу з наступним демультиплексуванням.

РЕАЛІЗАЦІЯ S/T-МОДУЛЯ З ЗАСТОСУВАННЯМ МУЛЬТИПЛЕКСОРІВ І ДЕМУЛЬТИПЛЕКСОРІВ • Підхід до побудови S/T-модулів використовує мультиплексування цифрових групових трактів (тобто ІКМ - ліній) і часову комутацію ущільненого сигналу з наступним демультиплексуванням.

Использование мультиплексоров и демультиплексоров • Примером такого подхода в построении S/Т-ступени является БИС, разработанная итальянскими специалистами для цифровой системы PROTEL UT и получившая название интегрального коммутационного элемента (ECI). • ECI является S/T-ступенью с параметрами S/Т: (8132)х(8132) Микросхема ЕСI может прямо подключаться к шине 8 -битового процессора и является для него стандартным периферийным устройством.

Использование мультиплексоров и демультиплексоров • Примером такого подхода в построении S/Т-ступени является БИС, разработанная итальянскими специалистами для цифровой системы PROTEL UT и получившая название интегрального коммутационного элемента (ECI). • ECI является S/T-ступенью с параметрами S/Т: (8132)х(8132) Микросхема ЕСI может прямо подключаться к шине 8 -битового процессора и является для него стандартным периферийным устройством.

Структурная схема интегрального коммутационного элемента (ECI). • • В схеме ЕСI можно выделить следующие функциональные блоки: синхронизирующее устройство (ТВ); преобразователи последовательного кода ИКМ кодового слова в параллельный и наоборот (s/р и р/s); речевое ЗУ (SM); управляющее ЗУ (СМ); логический интерфейс микропроцессора (m. PLI); мультиплексоры (мультиплексор адреса Управляющей памяти — MUX SM ADDR, мультиплексор внутренней ИКМ шины — MUX IB, мультиплексор адреса речевой памяти — MUX СМ ADDR). Синхронизирующее устройство ТВ генерирует и формирует все необходимые синхронизирующие сигналы, используя два внешних сигнала — 4 к. Гц и 4, 096 МГц. В частности, устройство задает два счетчика (входной и выходной) для преобразователей s/р и р/s. Кроме того, из синхросигнала 4 к. Гц схема ТВ задает три счетчика: СТ 1, СТ 2 и СТЗ.

Структурная схема интегрального коммутационного элемента (ECI). • • В схеме ЕСI можно выделить следующие функциональные блоки: синхронизирующее устройство (ТВ); преобразователи последовательного кода ИКМ кодового слова в параллельный и наоборот (s/р и р/s); речевое ЗУ (SM); управляющее ЗУ (СМ); логический интерфейс микропроцессора (m. PLI); мультиплексоры (мультиплексор адреса Управляющей памяти — MUX SM ADDR, мультиплексор внутренней ИКМ шины — MUX IB, мультиплексор адреса речевой памяти — MUX СМ ADDR). Синхронизирующее устройство ТВ генерирует и формирует все необходимые синхронизирующие сигналы, используя два внешних сигнала — 4 к. Гц и 4, 096 МГц. В частности, устройство задает два счетчика (входной и выходной) для преобразователей s/р и р/s. Кроме того, из синхросигнала 4 к. Гц схема ТВ задает три счетчика: СТ 1, СТ 2 и СТЗ.

Схема интегрального коммутационного элемента (ECI). • • • Первый счетчик (СТ 1) формирует отсчет длительности одного канального интервала (примерно 4 мкс). Второй и третий счетчики (СТ 2 и СТЗ) работают синхронно со счетчиком СТ 1 и вырабатывают последовательные канальные адреса для чтения из управляющего ЗУ и записи в речевое ЗУ соответственно. Речевое ЗУ организовано в виде 8 полей по 32 строки и 8 столбцов. Каждое поле соответствует номеру бита в кодовом слове, каждая строка — номеру канального интервала в структуре цикла ИКМ-ЗО, а каждый столбец — номеру входящей ИКМ линии. Рабочий цикл ЗУ (около 4 мкс) — разделен на два подинтервала по 2 мкс каждый. Первый подинтервал содержит восемь циклов длительностью 250 нс каждый. В первом цикле в речевое ЗУ записываются по соответствующим адресам 8 бит из каждой линии ИКМ-30. Остальные циклы используются для связи с логическим интерфейсом микропроцессора и приема адреса считывания из управляющего ЗУ. Во втором подинтервале осуществляется считывание 8 бит кодовых слов согласно адресам, полученным из управляющего ЗУ.

Схема интегрального коммутационного элемента (ECI). • • • Первый счетчик (СТ 1) формирует отсчет длительности одного канального интервала (примерно 4 мкс). Второй и третий счетчики (СТ 2 и СТЗ) работают синхронно со счетчиком СТ 1 и вырабатывают последовательные канальные адреса для чтения из управляющего ЗУ и записи в речевое ЗУ соответственно. Речевое ЗУ организовано в виде 8 полей по 32 строки и 8 столбцов. Каждое поле соответствует номеру бита в кодовом слове, каждая строка — номеру канального интервала в структуре цикла ИКМ-ЗО, а каждый столбец — номеру входящей ИКМ линии. Рабочий цикл ЗУ (около 4 мкс) — разделен на два подинтервала по 2 мкс каждый. Первый подинтервал содержит восемь циклов длительностью 250 нс каждый. В первом цикле в речевое ЗУ записываются по соответствующим адресам 8 бит из каждой линии ИКМ-30. Остальные циклы используются для связи с логическим интерфейсом микропроцессора и приема адреса считывания из управляющего ЗУ. Во втором подинтервале осуществляется считывание 8 бит кодовых слов согласно адресам, полученным из управляющего ЗУ.

Управляющее ЗУ • • Управляющее ЗУ имеет 9 полей по 32 строки и 8 столбцов. Каждое поле соответствует номеру канального интервала в структуре цикла ИКМ-30 (одно поле для проверочных бит). Адреса записаны в управляющем ЗУ так же, как и в речевом. Рабочий цикл управляющего ЗУ организован аналогично рабочему циклу речевого ЗУ, Во время первого подинтервала ЗУ связано с микропроцессором для получения управляющих сигналов. Во втором подинтервале по сигналам счетчиков СТ 1 и СТ 2 восемь раз производится считывание адресов для управления речевым ЗУ, которые состоят из адресов считывания в речевом ЗУ ((1. . . 8)-й биты) и одного проверочного бита для управления работой внутренней ИКМ линии. Логический интерфейс микропроцессора обеспечивает связь ECI с микропроцессором типа Z-80, из которого приходят сигналы для записи и считывания информации в ECI.

Управляющее ЗУ • • Управляющее ЗУ имеет 9 полей по 32 строки и 8 столбцов. Каждое поле соответствует номеру канального интервала в структуре цикла ИКМ-30 (одно поле для проверочных бит). Адреса записаны в управляющем ЗУ так же, как и в речевом. Рабочий цикл управляющего ЗУ организован аналогично рабочему циклу речевого ЗУ, Во время первого подинтервала ЗУ связано с микропроцессором для получения управляющих сигналов. Во втором подинтервале по сигналам счетчиков СТ 1 и СТ 2 восемь раз производится считывание адресов для управления речевым ЗУ, которые состоят из адресов считывания в речевом ЗУ ((1. . . 8)-й биты) и одного проверочного бита для управления работой внутренней ИКМ линии. Логический интерфейс микропроцессора обеспечивает связь ECI с микропроцессором типа Z-80, из которого приходят сигналы для записи и считывания информации в ECI.

схема интегрального коммутационного элемента (ECI). • Входы А 1, Sl, А 2, S 2 позволяют включить в единую коммутационную схему несколько ECI. Например, для получения емкости ступени 1024 х1024 канальных интервалов необходимо объединить восемь ECI. • Преимущества специализированных БИС для ступеней коммутации - возможность построения коммутационного поля с меньшими значениями величины блокировок, чем при реализации на интегральных схемах (ИС) общего пользования, а также повышением надежности благодаря реализации оборудования коммутационного поля с помощью меньшего числа элементов и их взаимных связей, и дальнейшим снижением стоимости оборудования коммутационного поля, обусловленным большими объемами выпуска специализированных БИС ограниченного числа типов.

схема интегрального коммутационного элемента (ECI). • Входы А 1, Sl, А 2, S 2 позволяют включить в единую коммутационную схему несколько ECI. Например, для получения емкости ступени 1024 х1024 канальных интервалов необходимо объединить восемь ECI. • Преимущества специализированных БИС для ступеней коммутации - возможность построения коммутационного поля с меньшими значениями величины блокировок, чем при реализации на интегральных схемах (ИС) общего пользования, а также повышением надежности благодаря реализации оборудования коммутационного поля с помощью меньшего числа элементов и их взаимных связей, и дальнейшим снижением стоимости оборудования коммутационного поля, обусловленным большими объемами выпуска специализированных БИС ограниченного числа типов.

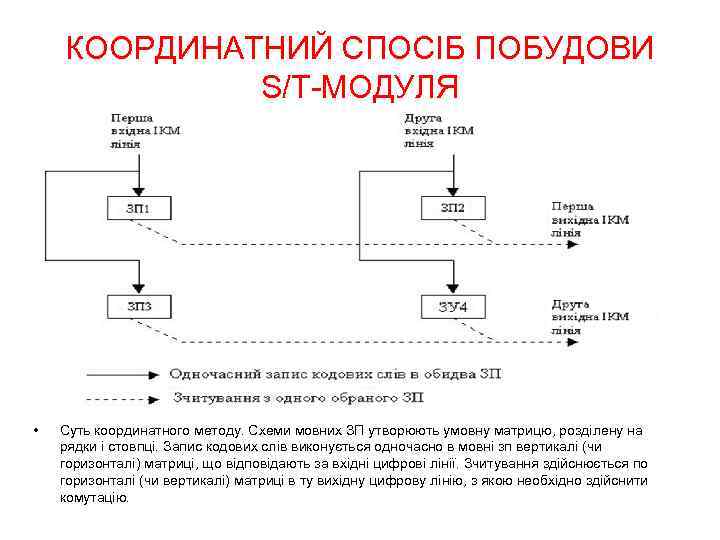

КООРДИНАТНИЙ СПОСІБ ПОБУДОВИ S/T-МОДУЛЯ • Суть координатного методу. Схеми мовних ЗП утворюють умовну матрицю, розділену на рядки і стовпці. Запис кодових слів виконується одночасно в мовні зп вертикалі (чи горизонталі) матриці, що відповідають за вхідні цифрові лінії. Зчитування здійснюється по горизонталі (чи вертикалі) матриці в ту вихідну цифрову лінію, з якою необхідно здійснити комутацію.

КООРДИНАТНИЙ СПОСІБ ПОБУДОВИ S/T-МОДУЛЯ • Суть координатного методу. Схеми мовних ЗП утворюють умовну матрицю, розділену на рядки і стовпці. Запис кодових слів виконується одночасно в мовні зп вертикалі (чи горизонталі) матриці, що відповідають за вхідні цифрові лінії. Зчитування здійснюється по горизонталі (чи вертикалі) матриці в ту вихідну цифрову лінію, з якою необхідно здійснити комутацію.

Координатный способ • Координатный способ предполагает использование речевого ЗУ, которое состоит из ячеек памяти, условно разделенных на столбцы и строки, при этом каждый столбец соответствует номеру входной ИКМ линии, а каждая - строка номеру КИ. За один цикл работы производится запись кодовых слов в ячейки речевого ЗУ с последующим их считыванием в другом цикле. • Суть метода. Схемы речевых ЗУ образуют условную матрицу, разделенную на строки и столбцы, Запись кодовых слов производится одновременно в речевые ЗУ вертикали (или горизонтали) матрицы, отвечающие за входящие цифровые линии. Считывание осуществляется по горизонтали (или вертикали) матрицы в ту исходящую цифровую линию, с которой необходимо осуществить коммутацию. • Структурная схема имеет вид похожий на структуру Т - ступени. В модуле приёма происходит преобразование из последовательной в параллельную форму и преобразование кода (из квазитроичного НDВЗ кода в двоичный код ). •

Координатный способ • Координатный способ предполагает использование речевого ЗУ, которое состоит из ячеек памяти, условно разделенных на столбцы и строки, при этом каждый столбец соответствует номеру входной ИКМ линии, а каждая - строка номеру КИ. За один цикл работы производится запись кодовых слов в ячейки речевого ЗУ с последующим их считыванием в другом цикле. • Суть метода. Схемы речевых ЗУ образуют условную матрицу, разделенную на строки и столбцы, Запись кодовых слов производится одновременно в речевые ЗУ вертикали (или горизонтали) матрицы, отвечающие за входящие цифровые линии. Считывание осуществляется по горизонтали (или вертикали) матрицы в ту исходящую цифровую линию, с которой необходимо осуществить коммутацию. • Структурная схема имеет вид похожий на структуру Т - ступени. В модуле приёма происходит преобразование из последовательной в параллельную форму и преобразование кода (из квазитроичного НDВЗ кода в двоичный код ). •

Реализация S/T ступени координатным способом

Реализация S/T ступени координатным способом

Запись и считывание кодовых слов • • • Содержимое ячеек памяти управляющего ЗУ считывается поочередно. При этом считывание информации в каждую исходящую ИКМ линию происходит в строго определенный момент времени, в течение которого сдержимое управляющего ЗУ определяет, информация какого временного канала приема переключается на данный временной интервал передачи. Кодовая последовательность временного интервала приема, считанная из речевого ЗУ, передается на модуль передачи, где преобразуется из последовательной формы в параллельную и размещается в выбранном временном интервале передачи. Этот процесс повторяется до тех пор, пока УУ не запишет в управляющее ЗУ данные для установления нового соединения. Запись и считывание кодовых слов в модуль приема, речевое ЗУ и модуль передачи разнесены во времени таким образом, что блокировок при записи/считывании не возникает. S/T – ступени получили широкое распространение в начале 80 -х годов благодаря созданию специализированных БИС.

Запись и считывание кодовых слов • • • Содержимое ячеек памяти управляющего ЗУ считывается поочередно. При этом считывание информации в каждую исходящую ИКМ линию происходит в строго определенный момент времени, в течение которого сдержимое управляющего ЗУ определяет, информация какого временного канала приема переключается на данный временной интервал передачи. Кодовая последовательность временного интервала приема, считанная из речевого ЗУ, передается на модуль передачи, где преобразуется из последовательной формы в параллельную и размещается в выбранном временном интервале передачи. Этот процесс повторяется до тех пор, пока УУ не запишет в управляющее ЗУ данные для установления нового соединения. Запись и считывание кодовых слов в модуль приема, речевое ЗУ и модуль передачи разнесены во времени таким образом, что блокировок при записи/считывании не возникает. S/T – ступени получили широкое распространение в начале 80 -х годов благодаря созданию специализированных БИС.

КООРДИНАТНИЙ СПОСІБ ПОБУДОВИ S/T-МОДУЛЯ • В качестве примера реализации S/T-ступени по координатному принципу рассмотрим блок пространственно-временной коммутации цифровой ЭАТС 200 (в технической документации ступень названа блоком временной коммутации).

КООРДИНАТНИЙ СПОСІБ ПОБУДОВИ S/T-МОДУЛЯ • В качестве примера реализации S/T-ступени по координатному принципу рассмотрим блок пространственно-временной коммутации цифровой ЭАТС 200 (в технической документации ступень названа блоком временной коммутации).

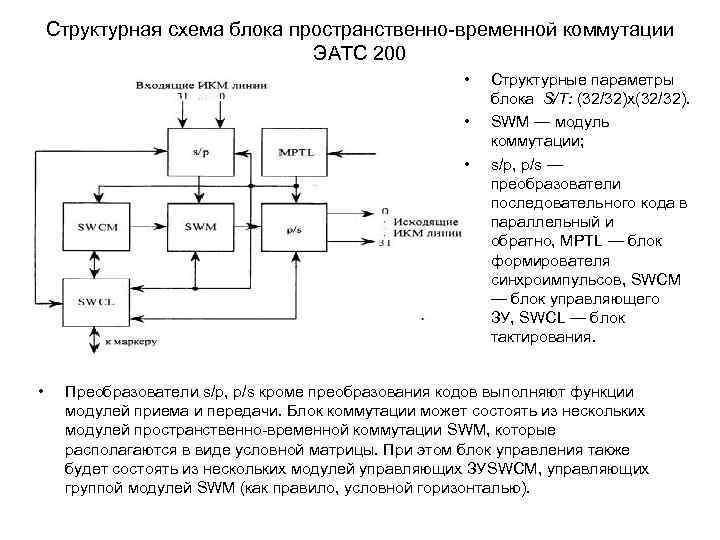

Структурная схема блока пространственно-временной коммутации ЭАТС 200 • • Структурные параметры блока S/Т: (32/32)x(32/32). SWM — модуль коммутации; s/р, р/s — преобразователи последовательного кода в параллельный и обратно, MPTL — блок формирователя синхроимпульсов, SWCM — блок управляющего ЗУ, SWCL — блок тактирования. Преобразователи s/р, р/s кроме преобразования кодов выполняют функции модулей приема и передачи. Блок коммутации может состоять из нескольких модулей пространственно-временной коммутации SWM, которые располагаются в виде условной матрицы. При этом блок управления также будет состоять из нескольких модулей управляющих ЗУSWCM, управляющих группой модулей SWM (как правило, условной горизонталью).

Структурная схема блока пространственно-временной коммутации ЭАТС 200 • • Структурные параметры блока S/Т: (32/32)x(32/32). SWM — модуль коммутации; s/р, р/s — преобразователи последовательного кода в параллельный и обратно, MPTL — блок формирователя синхроимпульсов, SWCM — блок управляющего ЗУ, SWCL — блок тактирования. Преобразователи s/р, р/s кроме преобразования кодов выполняют функции модулей приема и передачи. Блок коммутации может состоять из нескольких модулей пространственно-временной коммутации SWM, которые располагаются в виде условной матрицы. При этом блок управления также будет состоять из нескольких модулей управляющих ЗУSWCM, управляющих группой модулей SWM (как правило, условной горизонталью).

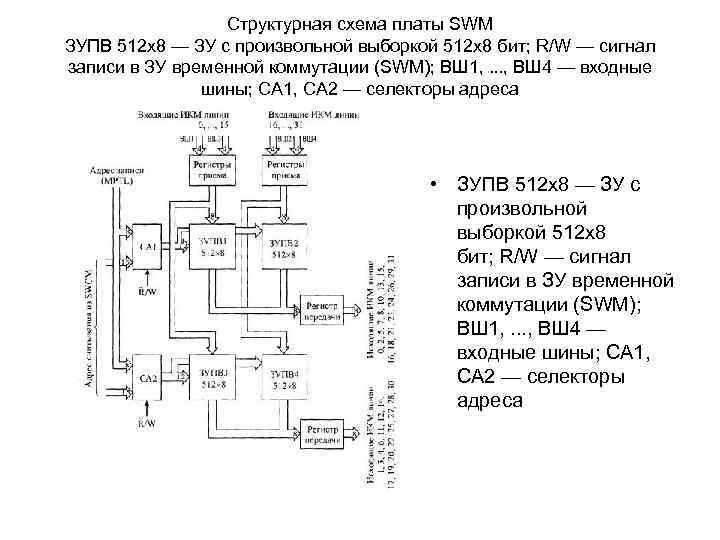

Структурная схема платы SWM ЗУПВ 512 x 8 — ЗУ с произвольной выборкой 512 x 8 бит; R/W — сигнал записи в ЗУ временной коммутации (SWM); ВШ 1, . . . , ВШ 4 — входные шины; СА 1, СА 2 — селекторы адреса • ЗУПВ 512 x 8 — ЗУ с произвольной выборкой 512 x 8 бит; R/W — сигнал записи в ЗУ временной коммутации (SWM); ВШ 1, . . . , ВШ 4 — входные шины; СА 1, СА 2 — селекторы адреса

Структурная схема платы SWM ЗУПВ 512 x 8 — ЗУ с произвольной выборкой 512 x 8 бит; R/W — сигнал записи в ЗУ временной коммутации (SWM); ВШ 1, . . . , ВШ 4 — входные шины; СА 1, СА 2 — селекторы адреса • ЗУПВ 512 x 8 — ЗУ с произвольной выборкой 512 x 8 бит; R/W — сигнал записи в ЗУ временной коммутации (SWM); ВШ 1, . . . , ВШ 4 — входные шины; СА 1, СА 2 — селекторы адреса

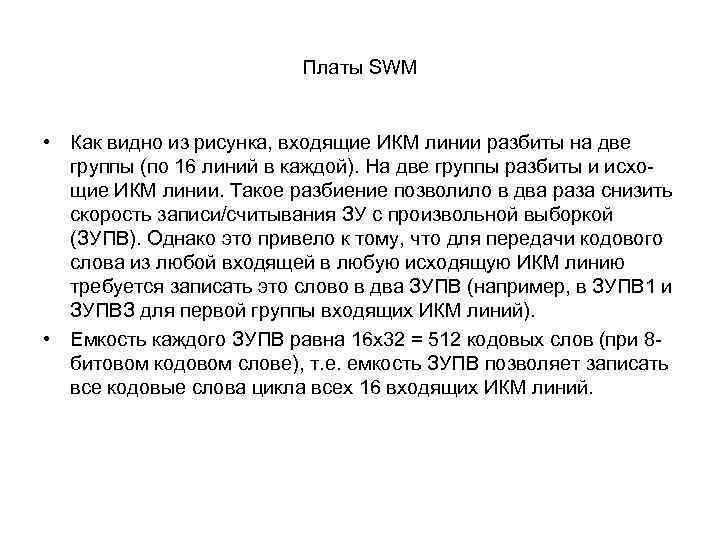

Платы SWM • Как видно из рисунка, входящие ИКМ линии разбиты на две группы (по 16 линий в каждой). На две группы разбиты и исхощие ИКМ линии. Такое разбиение позволило в два раза снизить скорость записи/считывания ЗУ с произвольной выборкой (ЗУПВ). Однако это привело к тому, что для передачи кодового слова из любой входящей в любую исходящую ИКМ линию требуется записать это слово в два ЗУПВ (например, в ЗУПВ 1 и ЗУПВЗ для первой группы входящих ИКМ линий). • Емкость каждого ЗУПВ равна 16 x 32 = 512 кодовых слов (при 8 битовом кодовом слове), т. е. емкость ЗУПВ позволяет записать все кодовые слова цикла всех 16 входящих ИКМ линий.

Платы SWM • Как видно из рисунка, входящие ИКМ линии разбиты на две группы (по 16 линий в каждой). На две группы разбиты и исхощие ИКМ линии. Такое разбиение позволило в два раза снизить скорость записи/считывания ЗУ с произвольной выборкой (ЗУПВ). Однако это привело к тому, что для передачи кодового слова из любой входящей в любую исходящую ИКМ линию требуется записать это слово в два ЗУПВ (например, в ЗУПВ 1 и ЗУПВЗ для первой группы входящих ИКМ линий). • Емкость каждого ЗУПВ равна 16 x 32 = 512 кодовых слов (при 8 битовом кодовом слове), т. е. емкость ЗУПВ позволяет записать все кодовые слова цикла всех 16 входящих ИКМ линий.

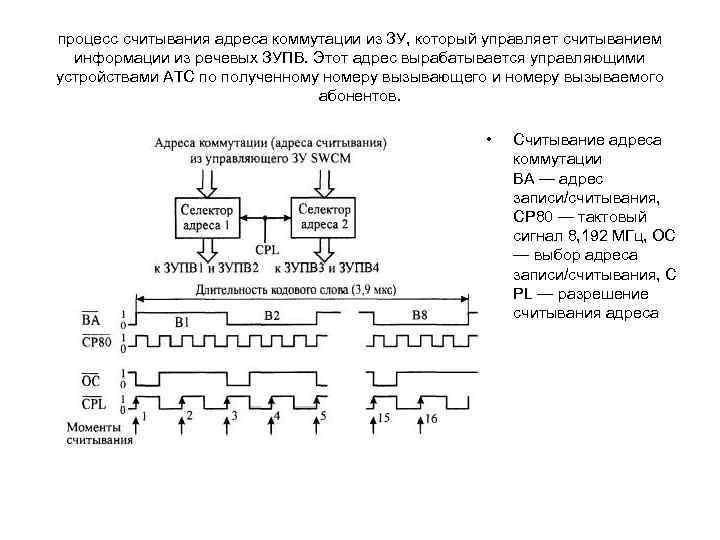

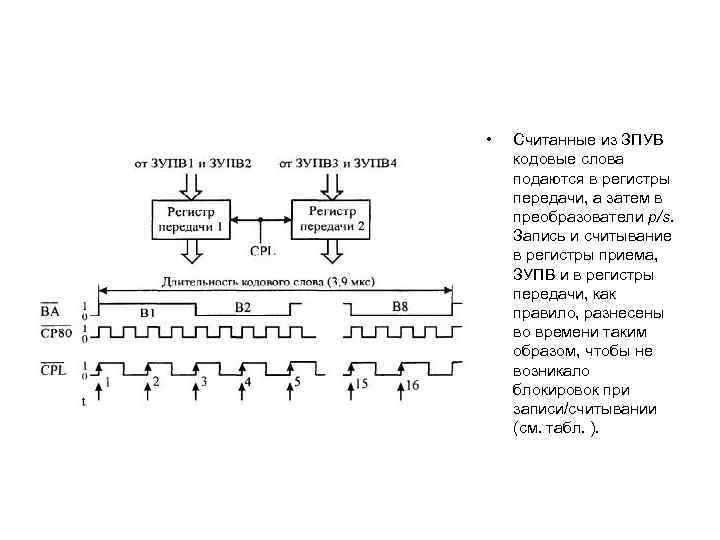

процесс считывания адреса коммутации из ЗУ, который управляет считыванием информации из речевых ЗУПВ. Этот адрес вырабатывается управляющими устройствами АТС по полученному номеру вызывающего и номеру вызываемого абонентов. • Считывание адреса коммутации ВА — адрес записи/считывания, CP 80 — тактовый сигнал 8, 192 МГц, ОС — выбор адреса записи/считывания, C PL — разрешение считывания адреса

процесс считывания адреса коммутации из ЗУ, который управляет считыванием информации из речевых ЗУПВ. Этот адрес вырабатывается управляющими устройствами АТС по полученному номеру вызывающего и номеру вызываемого абонентов. • Считывание адреса коммутации ВА — адрес записи/считывания, CP 80 — тактовый сигнал 8, 192 МГц, ОС — выбор адреса записи/считывания, C PL — разрешение считывания адреса

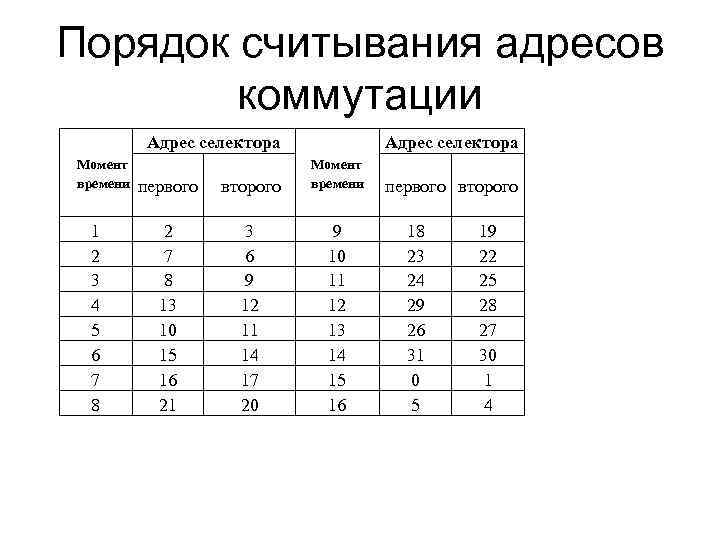

Порядок считывания адресов коммутации Адрес селектора Момент времени 1 2 3 4 5 6 7 8 Адрес селектора первого второго Момент времени 2 7 8 13 10 15 16 21 3 6 9 12 11 14 17 20 9 10 11 12 13 14 15 16 первого второго 18 23 24 29 26 31 0 5 19 22 25 28 27 30 1 4

Порядок считывания адресов коммутации Адрес селектора Момент времени 1 2 3 4 5 6 7 8 Адрес селектора первого второго Момент времени 2 7 8 13 10 15 16 21 3 6 9 12 11 14 17 20 9 10 11 12 13 14 15 16 первого второго 18 23 24 29 26 31 0 5 19 22 25 28 27 30 1 4

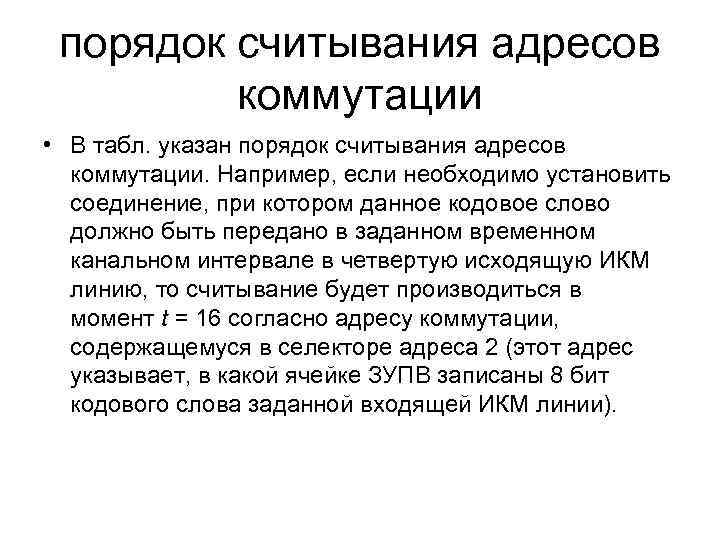

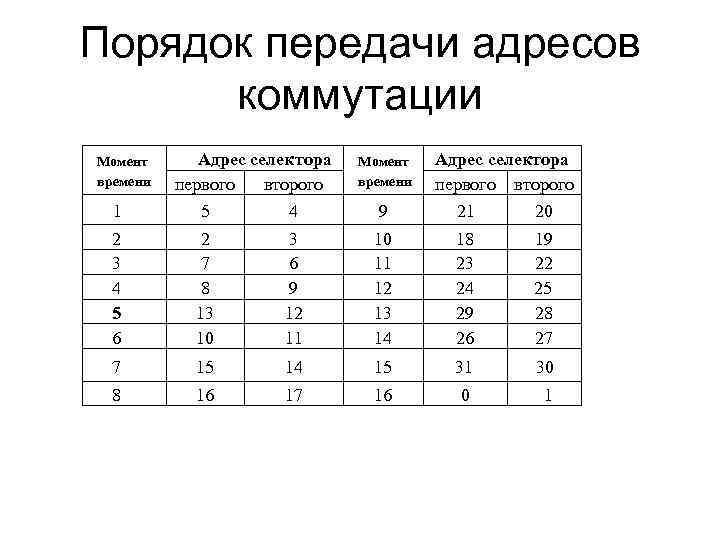

порядок считывания адресов коммутации • В табл. указан порядок считывания адресов коммутации. Например, если необходимо установить соединение, при котором данное кодовое слово должно быть передано в заданном временном канальном интервале в четвертую исходящую ИКМ линию, то считывание будет производиться в момент t = 16 согласно адресу коммутации, содержащемуся в селекторе адреса 2 (этот адрес указывает, в какой ячейке ЗУПВ записаны 8 бит кодового слова заданной входящей ИКМ линии).

порядок считывания адресов коммутации • В табл. указан порядок считывания адресов коммутации. Например, если необходимо установить соединение, при котором данное кодовое слово должно быть передано в заданном временном канальном интервале в четвертую исходящую ИКМ линию, то считывание будет производиться в момент t = 16 согласно адресу коммутации, содержащемуся в селекторе адреса 2 (этот адрес указывает, в какой ячейке ЗУПВ записаны 8 бит кодового слова заданной входящей ИКМ линии).

• Считанные из ЗПУВ кодовые слова подаются в регистры передачи, а затем в преобразователи p/s. Запись и считывание в регистры приема, ЗУПВ и в регистры передачи, как правило, разнесены во времени таким образом, чтобы не возникало блокировок при записи/считывании (см. табл. ).

• Считанные из ЗПУВ кодовые слова подаются в регистры передачи, а затем в преобразователи p/s. Запись и считывание в регистры приема, ЗУПВ и в регистры передачи, как правило, разнесены во времени таким образом, чтобы не возникало блокировок при записи/считывании (см. табл. ).

Порядок передачи адресов коммутации Момент времени Адрес селектора первого второго 1 5 4 9 21 20 2 3 4 5 6 2 7 8 13 10 3 6 9 12 11 10 11 12 13 14 18 23 24 29 26 19 22 25 28 27 7 15 14 15 31 30 8 16 17 16 0 1

Порядок передачи адресов коммутации Момент времени Адрес селектора первого второго 1 5 4 9 21 20 2 3 4 5 6 2 7 8 13 10 3 6 9 12 11 10 11 12 13 14 18 23 24 29 26 19 22 25 28 27 7 15 14 15 31 30 8 16 17 16 0 1

КІЛЬЦЕВИЙ S/T-МОДУЛЬ ІЗ ЗАТРИМКОЮ НА ½ ПЕРІОДУ

КІЛЬЦЕВИЙ S/T-МОДУЛЬ ІЗ ЗАТРИМКОЮ НА ½ ПЕРІОДУ

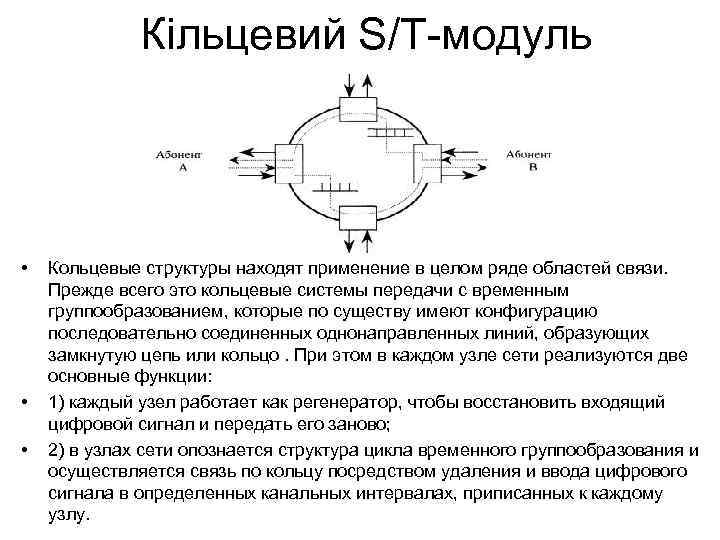

Кільцевий S/T-модуль • • • Кольцевые структуры находят применение в целом ряде областей связи. Прежде всего это кольцевые системы передачи с временным группообразованием, которые по существу имеют конфигурацию последовательно соединенных однонаправленных линий, образующих замкнутую цепь или кольцо. При этом в каждом узле сети реализуются две основные функции: 1) каждый узел работает как регенератор, чтобы восстановить входящий цифровой сигнал и передать его заново; 2) в узлах сети опознается структура цикла временного группообразования и осуществляется связь по кольцу посредством удаления и ввода цифрового сигнала в определенных канальных интервалах, приписанных к каждому узлу.

Кільцевий S/T-модуль • • • Кольцевые структуры находят применение в целом ряде областей связи. Прежде всего это кольцевые системы передачи с временным группообразованием, которые по существу имеют конфигурацию последовательно соединенных однонаправленных линий, образующих замкнутую цепь или кольцо. При этом в каждом узле сети реализуются две основные функции: 1) каждый узел работает как регенератор, чтобы восстановить входящий цифровой сигнал и передать его заново; 2) в узлах сети опознается структура цикла временного группообразования и осуществляется связь по кольцу посредством удаления и ввода цифрового сигнала в определенных канальных интервалах, приписанных к каждому узлу.

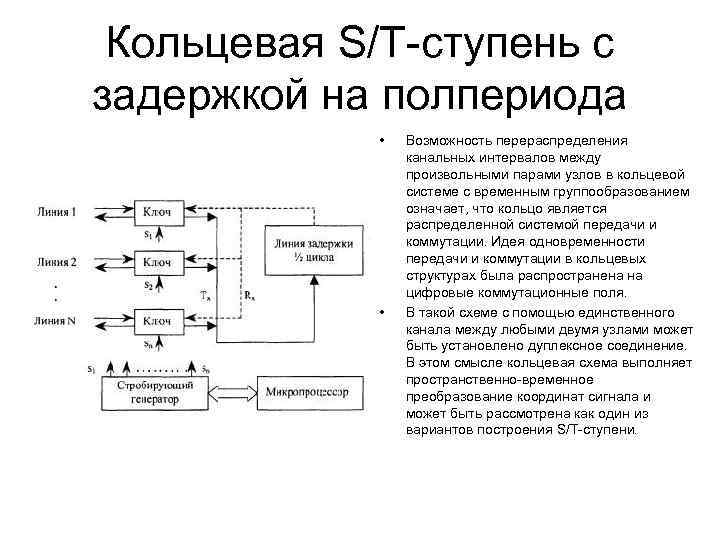

Кольцевая S/Т-ступень с задержкой на полпериода • • Возможность перераспределения канальных интервалов между произвольными парами узлов в кольцевой системе с временным группообразованием означает, что кольцо является распределенной системой передачи и коммутации. Идея одновременности передачи и коммутации в кольцевых структурах была распространена на цифровые коммутационные поля. В такой схеме с помощью единственного канала между любыми двумя узлами может быть установлено дуплексное соединение. В этом смысле кольцевая схема выполняет пространственно-временное преобразование координат сигнала и может быть рассмотрена как один из вариантов построения S/Т-ступени.

Кольцевая S/Т-ступень с задержкой на полпериода • • Возможность перераспределения канальных интервалов между произвольными парами узлов в кольцевой системе с временным группообразованием означает, что кольцо является распределенной системой передачи и коммутации. Идея одновременности передачи и коммутации в кольцевых структурах была распространена на цифровые коммутационные поля. В такой схеме с помощью единственного канала между любыми двумя узлами может быть установлено дуплексное соединение. В этом смысле кольцевая схема выполняет пространственно-временное преобразование координат сигнала и может быть рассмотрена как один из вариантов построения S/Т-ступени.

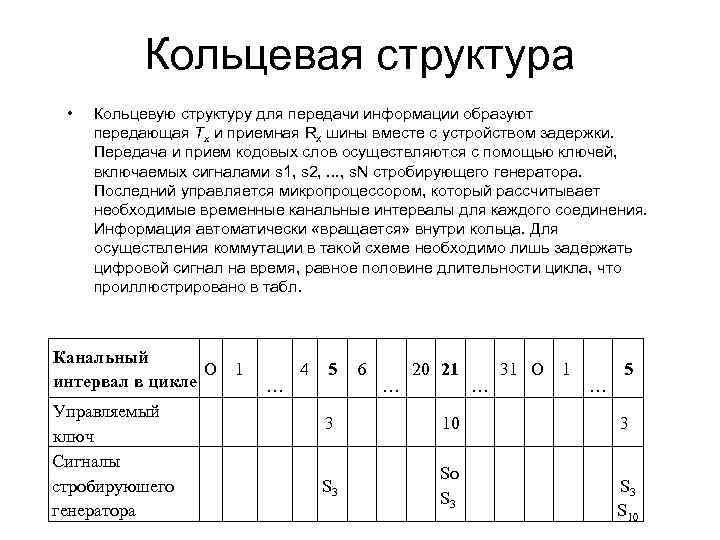

Кольцевая структура • Кольцевую структуру для передачи информации образуют передающая Тx и приемная Rx шины вместе с устройством задержки. Передача и прием кодовых слов осуществляются с помощью ключей, включаемых сигналами s 1, s 2, . . . , s. N стробирующего генератора. Последний управляется микропроцессором, который рассчитывает необходимые временные канальные интервалы для каждого соединения. Информация автоматически «вращается» внутри кольца. Для осуществления коммутации в такой схеме необходимо лишь задержать цифровой сигнал на время, равное половине длительности цикла, что проиллюстрировано в табл. Канальный О интервал в цикле Управляемый ключ Сигналы стробируюшего генератора 1 … 4 5 3 6 … 20 21 S 3 10 Sо S 3 … 31 О 1 … 5 3 S 10

Кольцевая структура • Кольцевую структуру для передачи информации образуют передающая Тx и приемная Rx шины вместе с устройством задержки. Передача и прием кодовых слов осуществляются с помощью ключей, включаемых сигналами s 1, s 2, . . . , s. N стробирующего генератора. Последний управляется микропроцессором, который рассчитывает необходимые временные канальные интервалы для каждого соединения. Информация автоматически «вращается» внутри кольца. Для осуществления коммутации в такой схеме необходимо лишь задержать цифровой сигнал на время, равное половине длительности цикла, что проиллюстрировано в табл. Канальный О интервал в цикле Управляемый ключ Сигналы стробируюшего генератора 1 … 4 5 3 6 … 20 21 S 3 10 Sо S 3 … 31 О 1 … 5 3 S 10

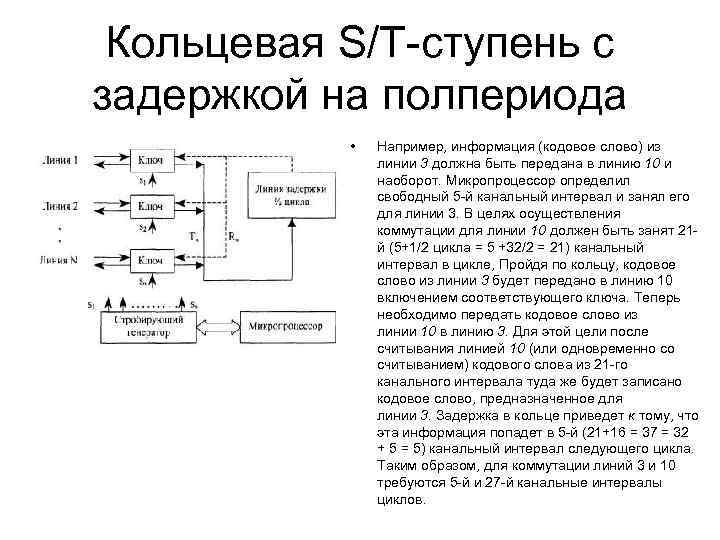

Кольцевая S/Т-ступень с задержкой на полпериода • Например, информация (кодовое слово) из линии 3 должна быть передана в линию 10 и наоборот. Микропроцессор определил свободный 5 -й канальный интервал и занял его для линии 3. В целях осуществления коммутации для линии 10 должен быть занят 21 й (5+1/2 цикла = 5 +32/2 = 21) канальный интервал в цикле, Пройдя по кольцу, кодовое слово из линии 3 будет передано в линию 10 включением соответствующего ключа. Теперь необходимо передать кодовое слово из линии 10 в линию 3. Для этой цели после считывания линией 10 (или одновременно со считыванием) кодового слова из 21 -го канального интервала туда же будет записано кодовое слово, предназначенное для линии 3. Задержка в кольце приведет к тому, что эта информация попадет в 5 -й (21+16 = 37 = 32 + 5 = 5) канальный интервал следующего цикла. Таким образом, для коммутации линий 3 и 10 требуются 5 -й и 27 -й канальные интервалы циклов.

Кольцевая S/Т-ступень с задержкой на полпериода • Например, информация (кодовое слово) из линии 3 должна быть передана в линию 10 и наоборот. Микропроцессор определил свободный 5 -й канальный интервал и занял его для линии 3. В целях осуществления коммутации для линии 10 должен быть занят 21 й (5+1/2 цикла = 5 +32/2 = 21) канальный интервал в цикле, Пройдя по кольцу, кодовое слово из линии 3 будет передано в линию 10 включением соответствующего ключа. Теперь необходимо передать кодовое слово из линии 10 в линию 3. Для этой цели после считывания линией 10 (или одновременно со считыванием) кодового слова из 21 -го канального интервала туда же будет записано кодовое слово, предназначенное для линии 3. Задержка в кольце приведет к тому, что эта информация попадет в 5 -й (21+16 = 37 = 32 + 5 = 5) канальный интервал следующего цикла. Таким образом, для коммутации линий 3 и 10 требуются 5 -й и 27 -й канальные интервалы циклов.

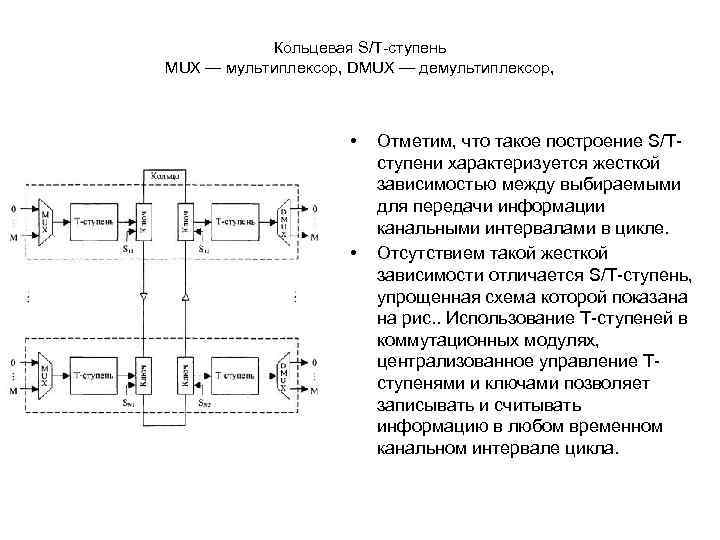

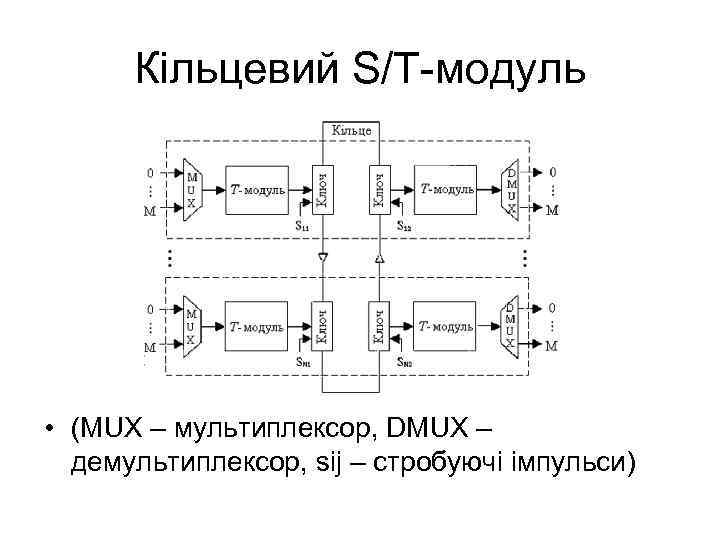

Кольцевая S/Т-ступень MUX — мультиплексор, DMUX — демультиплексор, • • Отметим, что такое построение S/Тступени характеризуется жесткой зависимостью между выбираемыми для передачи информации канальными интервалами в цикле. Отсутствием такой жесткой зависимости отличается S/Т-ступень, упрощенная схема которой показана на рис. . Использование Т-ступеней в коммутационных модулях, централизованное управление Тступенями и ключами позволяет записывать и считывать информацию в любом временном канальном интервале цикла.

Кольцевая S/Т-ступень MUX — мультиплексор, DMUX — демультиплексор, • • Отметим, что такое построение S/Тступени характеризуется жесткой зависимостью между выбираемыми для передачи информации канальными интервалами в цикле. Отсутствием такой жесткой зависимости отличается S/Т-ступень, упрощенная схема которой показана на рис. . Использование Т-ступеней в коммутационных модулях, централизованное управление Тступенями и ключами позволяет записывать и считывать информацию в любом временном канальном интервале цикла.

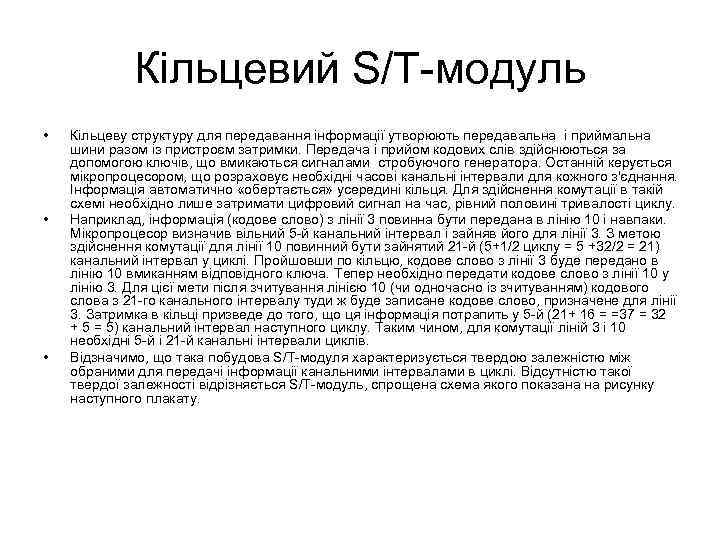

Кільцевий S/T-модуль • • • Кільцеву структуру для передавання інформації утворюють передавальна і приймальна шини разом із пристроєм затримки. Передача і прийом кодових слів здійснюються за допомогою ключів, що вмикаються сигналами стробуючого генератора. Останній керується мікропроцесором, що розраховує необхідні часові канальні інтервали для кожного з'єднання. Інформація автоматично «обертається» усередині кільця. Для здійснення комутації в такій схемі необхідно лише затримати цифровий сигнал на час, рівний половині тривалості циклу. Наприклад, інформація (кодове слово) з лінії 3 повинна бути передана в лінію 10 і навпаки. Мікропроцесор визначив вільний 5 -й канальний інтервал і зайняв його для лінії 3. З метою здійснення комутації для лінії 10 повинний бути зайнятий 21 -й (5+1/2 циклу = 5 +32/2 = 21) канальний інтервал у циклі. Пройшовши по кільцю, кодове слово з лінії 3 буде передано в лінію 10 вмиканням відповідного ключа. Тепер необхідно передати кодове слово з лінії 10 у лінію 3. Для цієї мети після зчитування лінією 10 (чи одночасно із зчитуванням) кодового слова з 21 -го канального інтервалу туди ж буде записане кодове слово, призначене для лінії 3. Затримка в кільці призведе до того, що ця інформація потрапить у 5 -й (21+ 16 = =37 = 32 + 5 = 5) канальний інтервал наступного циклу. Таким чином, для комутації ліній 3 і 10 необхідні 5 -й і 21 -й канальні інтервали циклів. Відзначимо, що така побудова S/T-модуля характеризується твердою залежністю між обраними для передачі інформації канальними інтервалами в циклі. Відсутністю такої твердої залежності відрізняється S/Т-модуль, спрощена схема якого показана на рисунку наступного плакату.

Кільцевий S/T-модуль • • • Кільцеву структуру для передавання інформації утворюють передавальна і приймальна шини разом із пристроєм затримки. Передача і прийом кодових слів здійснюються за допомогою ключів, що вмикаються сигналами стробуючого генератора. Останній керується мікропроцесором, що розраховує необхідні часові канальні інтервали для кожного з'єднання. Інформація автоматично «обертається» усередині кільця. Для здійснення комутації в такій схемі необхідно лише затримати цифровий сигнал на час, рівний половині тривалості циклу. Наприклад, інформація (кодове слово) з лінії 3 повинна бути передана в лінію 10 і навпаки. Мікропроцесор визначив вільний 5 -й канальний інтервал і зайняв його для лінії 3. З метою здійснення комутації для лінії 10 повинний бути зайнятий 21 -й (5+1/2 циклу = 5 +32/2 = 21) канальний інтервал у циклі. Пройшовши по кільцю, кодове слово з лінії 3 буде передано в лінію 10 вмиканням відповідного ключа. Тепер необхідно передати кодове слово з лінії 10 у лінію 3. Для цієї мети після зчитування лінією 10 (чи одночасно із зчитуванням) кодового слова з 21 -го канального інтервалу туди ж буде записане кодове слово, призначене для лінії 3. Затримка в кільці призведе до того, що ця інформація потрапить у 5 -й (21+ 16 = =37 = 32 + 5 = 5) канальний інтервал наступного циклу. Таким чином, для комутації ліній 3 і 10 необхідні 5 -й і 21 -й канальні інтервали циклів. Відзначимо, що така побудова S/T-модуля характеризується твердою залежністю між обраними для передачі інформації канальними інтервалами в циклі. Відсутністю такої твердої залежності відрізняється S/Т-модуль, спрощена схема якого показана на рисунку наступного плакату.

Кільцевий S/T-модуль • (MUX – мультиплексор, DMUX – демультиплексор, sij – стробуючі імпульси)

Кільцевий S/T-модуль • (MUX – мультиплексор, DMUX – демультиплексор, sij – стробуючі імпульси)

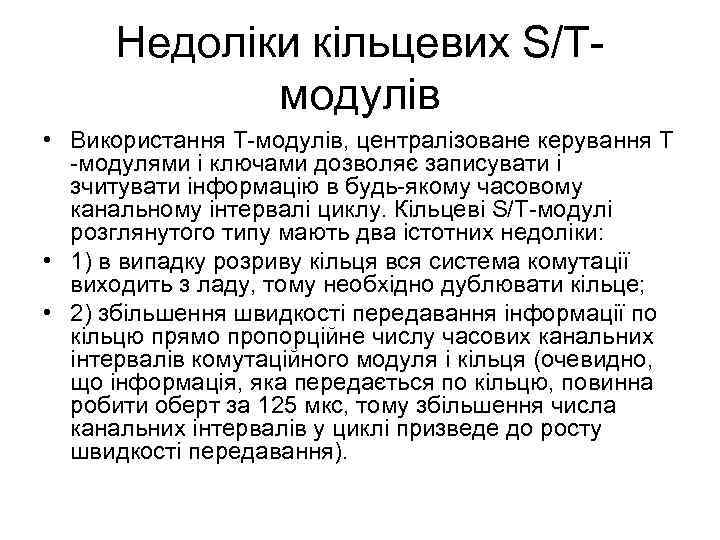

Недоліки кільцевих S/Tмодулів • Використання Т-модулів, централізоване керування Т -модулями і ключами дозволяє записувати і зчитувати інформацію в будь-якому часовому канальному інтервалі циклу. Кільцеві S/T-модулі розглянутого типу мають два істотних недоліки: • 1) в випадку розриву кільця вся система комутації виходить з ладу, тому необхідно дублювати кільце; • 2) збільшення швидкості передавання інформації по кільцю прямо пропорційне числу часових канальних інтервалів комутаційного модуля і кільця (очевидно, що інформація, яка передається по кільцю, повинна робити оберт за 125 мкс, тому збільшення числа канальних інтервалів у циклі призведе до росту швидкості передавання).

Недоліки кільцевих S/Tмодулів • Використання Т-модулів, централізоване керування Т -модулями і ключами дозволяє записувати і зчитувати інформацію в будь-якому часовому канальному інтервалі циклу. Кільцеві S/T-модулі розглянутого типу мають два істотних недоліки: • 1) в випадку розриву кільця вся система комутації виходить з ладу, тому необхідно дублювати кільце; • 2) збільшення швидкості передавання інформації по кільцю прямо пропорційне числу часових канальних інтервалів комутаційного модуля і кільця (очевидно, що інформація, яка передається по кільцю, повинна робити оберт за 125 мкс, тому збільшення числа канальних інтервалів у циклі призведе до росту швидкості передавання).