APMK_L8_AVR_Matem_l3(2).ppt

- Количество слайдов: 33

Лекція 8: Основи машинної арифметики 1. 2. 3. 4. 5. Форми чисел у пам’яті ОМК. Способи кодування цілих чисел і правила їх використання для додавання. Команди додавання і віднімання в AVR Виявлення переповнення розрядної сітки при додаванні чисел. Особливості використання двійково-десяткових кодів. Способи множення і ділення чисел. Література. За підручником: с. 330 -342. За навчальним посібником: c. 158 -170. 1

Лекція 8: Основи машинної арифметики 1. 2. 3. 4. 5. Форми чисел у пам’яті ОМК. Способи кодування цілих чисел і правила їх використання для додавання. Команди додавання і віднімання в AVR Виявлення переповнення розрядної сітки при додаванні чисел. Особливості використання двійково-десяткових кодів. Способи множення і ділення чисел. Література. За підручником: с. 330 -342. За навчальним посібником: c. 158 -170. 1

2

2

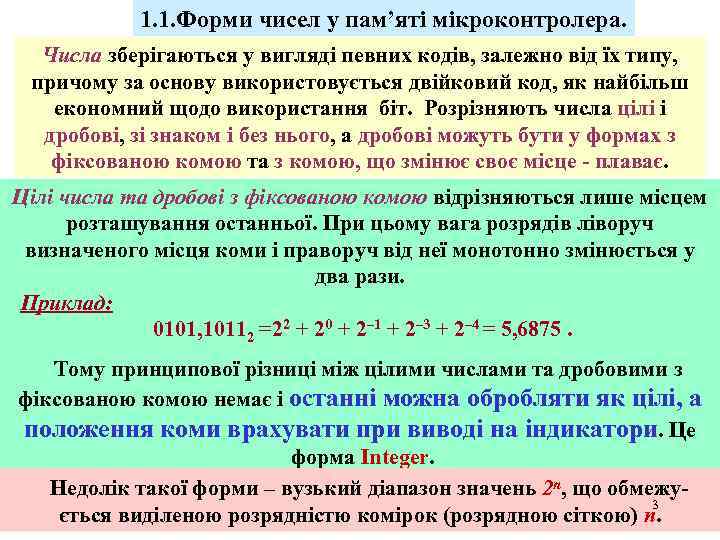

1. 1. Форми чисел у пам’яті мікроконтролера. Числа зберігаються у вигляді певних кодів, залежно від їх типу, причому за основу використовується двійковий код, як найбільш економний щодо використання біт. Розрізняють числа цілі і дробові, зі знаком і без нього, а дробові можуть бути у формах з фіксованою комою та з комою, що змінює своє місце - плаває. Цілі числа та дробові з фіксованою комою відрізняються лише місцем розташування останньої. При цьому вага розрядів ліворуч визначеного місця коми і праворуч від неї монотонно змінюється у два рази. Приклад: 0101, 10112 =22 + 20 + 2– 1 + 2– 3 + 2– 4 = 5, 6875. Тому принципової різниці між цілими числами та дробовими з фіксованою комою немає і останні можна обробляти як цілі, а положення коми врахувати при виводі на індикатори. Це форма Integer. Недолік такої форми – вузький діапазон значень 2 n, що обмежу3 ється виділеною розрядністю комірок (розрядною сіткою) n.

1. 1. Форми чисел у пам’яті мікроконтролера. Числа зберігаються у вигляді певних кодів, залежно від їх типу, причому за основу використовується двійковий код, як найбільш економний щодо використання біт. Розрізняють числа цілі і дробові, зі знаком і без нього, а дробові можуть бути у формах з фіксованою комою та з комою, що змінює своє місце - плаває. Цілі числа та дробові з фіксованою комою відрізняються лише місцем розташування останньої. При цьому вага розрядів ліворуч визначеного місця коми і праворуч від неї монотонно змінюється у два рази. Приклад: 0101, 10112 =22 + 20 + 2– 1 + 2– 3 + 2– 4 = 5, 6875. Тому принципової різниці між цілими числами та дробовими з фіксованою комою немає і останні можна обробляти як цілі, а положення коми врахувати при виводі на індикатори. Це форма Integer. Недолік такої форми – вузький діапазон значень 2 n, що обмежу3 ється виділеною розрядністю комірок (розрядною сіткою) n.

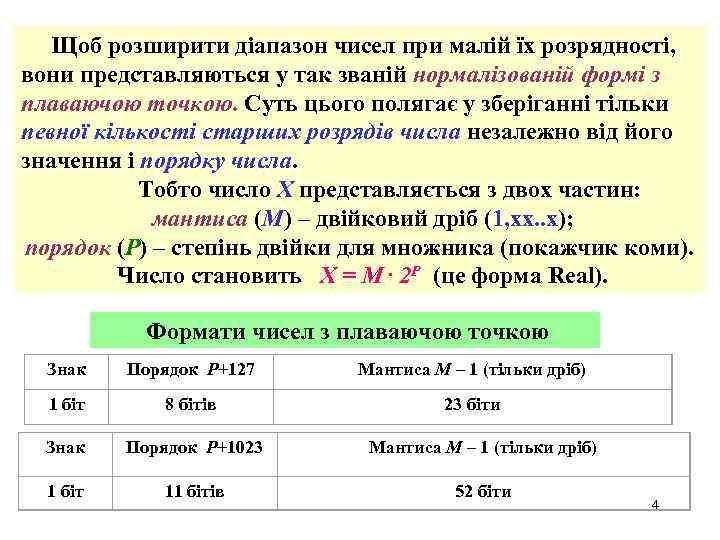

Щоб розширити діапазон чисел при малій їх розрядності, вони представляються у так званій нормалізованій формі з плаваючою точкою. Суть цього полягає у зберіганні тільки певної кількості старших розрядів числа незалежно від його значення і порядку числа. Тобто число Х представляється з двох частин: мантиса (М) – двійковий дріб (1, хх. . х); порядок (Р) – степінь двійки для множника (покажчик коми). Число становить Х = М. 2 Р (це форма Real). Формати чисел з плаваючою точкою Знак Порядок Р+127 Мантиса М – 1 (тільки дріб) 1 біт 8 бітів 23 біти Знак Порядок Р+1023 Мантиса М – 1 (тільки дріб) 1 біт 11 бітів 52 біти 4

Щоб розширити діапазон чисел при малій їх розрядності, вони представляються у так званій нормалізованій формі з плаваючою точкою. Суть цього полягає у зберіганні тільки певної кількості старших розрядів числа незалежно від його значення і порядку числа. Тобто число Х представляється з двох частин: мантиса (М) – двійковий дріб (1, хх. . х); порядок (Р) – степінь двійки для множника (покажчик коми). Число становить Х = М. 2 Р (це форма Real). Формати чисел з плаваючою точкою Знак Порядок Р+127 Мантиса М – 1 (тільки дріб) 1 біт 8 бітів 23 біти Знак Порядок Р+1023 Мантиса М – 1 (тільки дріб) 1 біт 11 бітів 52 біти 4

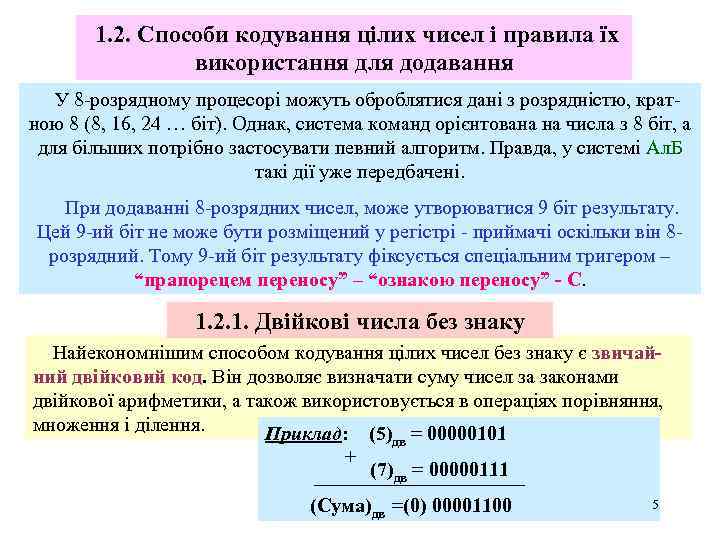

1. 2. Способи кодування цілих чисел і правила їх використання для додавання У 8 -розрядному процесорі можуть оброблятися дані з розрядністю, кратною 8 (8, 16, 24 … біт). Однак, система команд орієнтована на числа з 8 біт, а для більших потрібно застосувати певний алгоритм. Правда, у системі Ал. Б такі дії уже передбачені. При додаванні 8 -розрядних чисел, може утворюватися 9 біт результату. Цей 9 -ий біт не може бути розміщений у регістрі - приймачі оскільки він 8 розрядний. Тому 9 -ий біт результату фіксується спеціальним тригером – “прапорецем переносу” – “ознакою переносу” - С. 1. 2. 1. Двійкові числа без знаку Найекономнішим способом кодування цілих чисел без знаку є звичайний двійковий код. Він дозволяє визначати суму чисел за законами двійкової арифметики, а також використовується в операціях порівняння, множення і ділення. Приклад: (5) = 00000101 + дв (7)дв = 00000111 (Cума)дв =(0) 00001100 5

1. 2. Способи кодування цілих чисел і правила їх використання для додавання У 8 -розрядному процесорі можуть оброблятися дані з розрядністю, кратною 8 (8, 16, 24 … біт). Однак, система команд орієнтована на числа з 8 біт, а для більших потрібно застосувати певний алгоритм. Правда, у системі Ал. Б такі дії уже передбачені. При додаванні 8 -розрядних чисел, може утворюватися 9 біт результату. Цей 9 -ий біт не може бути розміщений у регістрі - приймачі оскільки він 8 розрядний. Тому 9 -ий біт результату фіксується спеціальним тригером – “прапорецем переносу” – “ознакою переносу” - С. 1. 2. 1. Двійкові числа без знаку Найекономнішим способом кодування цілих чисел без знаку є звичайний двійковий код. Він дозволяє визначати суму чисел за законами двійкової арифметики, а також використовується в операціях порівняння, множення і ділення. Приклад: (5) = 00000101 + дв (7)дв = 00000111 (Cума)дв =(0) 00001100 5

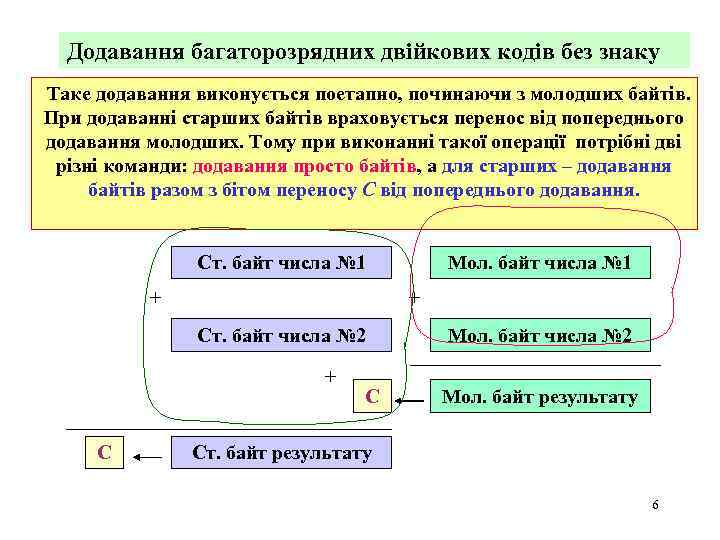

Додавання багаторозрядних двійкових кодів без знаку Таке додавання виконується поетапно, починаючи з молодших байтів. При додаванні старших байтів враховується перенос від попереднього додавання молодших. Тому при виконанні такої операції потрібні дві різні команди: додавання просто байтів, а для старших – додавання байтів разом з бітом переносу С від попереднього додавання. Ст. байт числа № 1 + + Ст. байт числа № 2 + С Мол. байт числа № 1 С Мол. байт числа № 2 Мол. байт результату Ст. байт результату 6

Додавання багаторозрядних двійкових кодів без знаку Таке додавання виконується поетапно, починаючи з молодших байтів. При додаванні старших байтів враховується перенос від попереднього додавання молодших. Тому при виконанні такої операції потрібні дві різні команди: додавання просто байтів, а для старших – додавання байтів разом з бітом переносу С від попереднього додавання. Ст. байт числа № 1 + + Ст. байт числа № 2 + С Мол. байт числа № 1 С Мол. байт числа № 2 Мол. байт результату Ст. байт результату 6

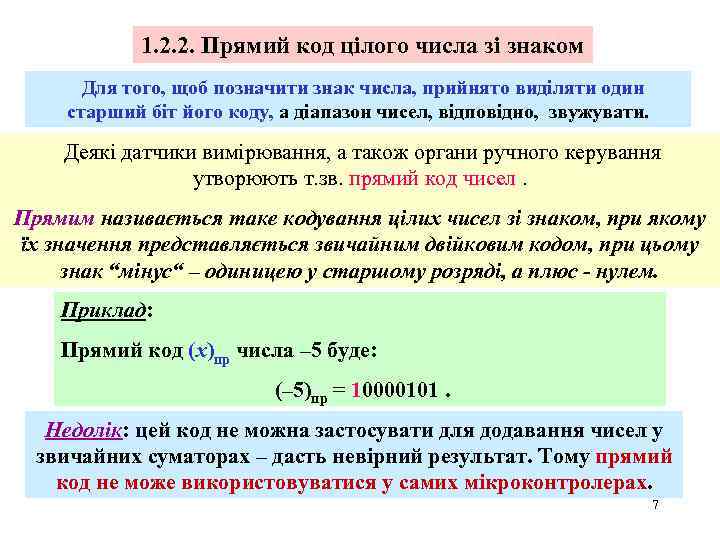

1. 2. 2. Прямий код цілого числа зі знаком Для того, щоб позначити знак числа, прийнято виділяти один старший біт його коду, а діапазон чисел, відповідно, звужувати. Деякі датчики вимірювання, а також органи ручного керування утворюють т. зв. прямий код чисел. Прямим називається таке кодування цілих чисел зі знаком, при якому їх значення представляється звичайним двійковим кодом, при цьому знак “мінус“ – одиницею у старшому розряді, а плюс - нулем. Приклад: Прямий код (х)пр числа – 5 буде: (– 5)пр = 10000101. Недолік: цей код не можна застосувати для додавання чисел у звичайних суматорах – дасть невірний результат. Тому прямий код не може використовуватися у самих мікроконтролерах. 7

1. 2. 2. Прямий код цілого числа зі знаком Для того, щоб позначити знак числа, прийнято виділяти один старший біт його коду, а діапазон чисел, відповідно, звужувати. Деякі датчики вимірювання, а також органи ручного керування утворюють т. зв. прямий код чисел. Прямим називається таке кодування цілих чисел зі знаком, при якому їх значення представляється звичайним двійковим кодом, при цьому знак “мінус“ – одиницею у старшому розряді, а плюс - нулем. Приклад: Прямий код (х)пр числа – 5 буде: (– 5)пр = 10000101. Недолік: цей код не можна застосувати для додавання чисел у звичайних суматорах – дасть невірний результат. Тому прямий код не може використовуватися у самих мікроконтролерах. 7

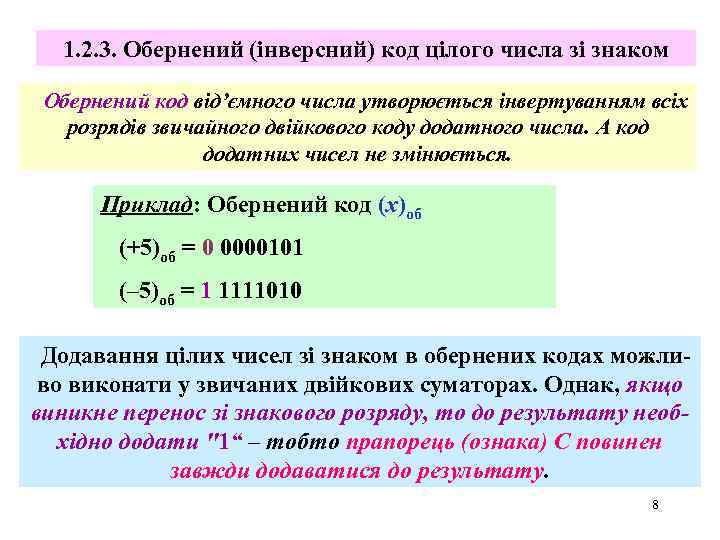

1. 2. 3. Обернений (інверсний) код цілого числа зі знаком Обернений код від’ємного числа утворюється інвертуванням всіх розрядів звичайного двійкового коду додатного числа. А код додатних чисел не змінюється. Приклад: Обернений код (х)об (+5)об = 0 0000101 (– 5)об = 1 1111010 Додавання цілих чисел зі знаком в обернених кодах можливо виконати у звичаних двійкових суматорах. Однак, якщо виникне перенос зі знакового розряду, то до результату необхідно додати "1“ – тобто прапорець (ознака) С повинен завжди додаватися до результату. 8

1. 2. 3. Обернений (інверсний) код цілого числа зі знаком Обернений код від’ємного числа утворюється інвертуванням всіх розрядів звичайного двійкового коду додатного числа. А код додатних чисел не змінюється. Приклад: Обернений код (х)об (+5)об = 0 0000101 (– 5)об = 1 1111010 Додавання цілих чисел зі знаком в обернених кодах можливо виконати у звичаних двійкових суматорах. Однак, якщо виникне перенос зі знакового розряду, то до результату необхідно додати "1“ – тобто прапорець (ознака) С повинен завжди додаватися до результату. 8

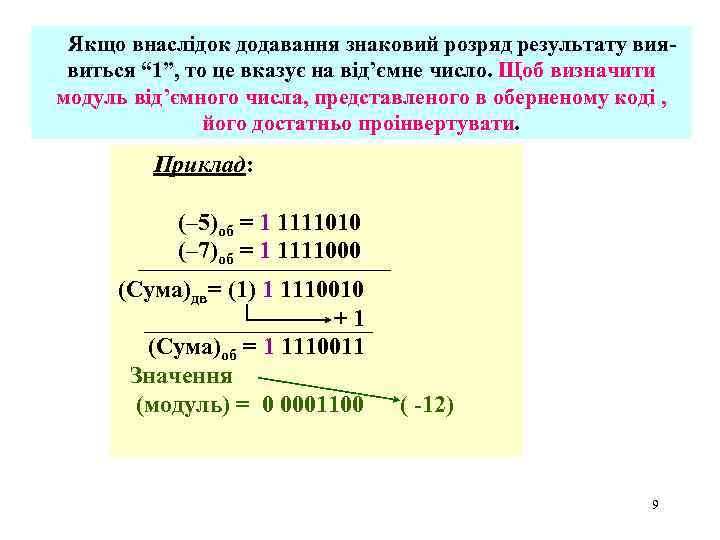

Якщо внаслідок додавання знаковий розряд результату виявиться “ 1”, то це вказує на від’ємне число. Щоб визначити модуль від’ємного числа, представленого в оберненому коді , його достатньо проінвертувати. Приклад: (– 5)об = 1 1111010 (– 7)об = 1 1111000 (Cума)дв= (1) 1 1110010 +1 (Сума)об = 1 1110011 Значення (модуль) = 0 0001100 ( -12) 9

Якщо внаслідок додавання знаковий розряд результату виявиться “ 1”, то це вказує на від’ємне число. Щоб визначити модуль від’ємного числа, представленого в оберненому коді , його достатньо проінвертувати. Приклад: (– 5)об = 1 1111010 (– 7)об = 1 1111000 (Cума)дв= (1) 1 1110010 +1 (Сума)об = 1 1110011 Значення (модуль) = 0 0001100 ( -12) 9

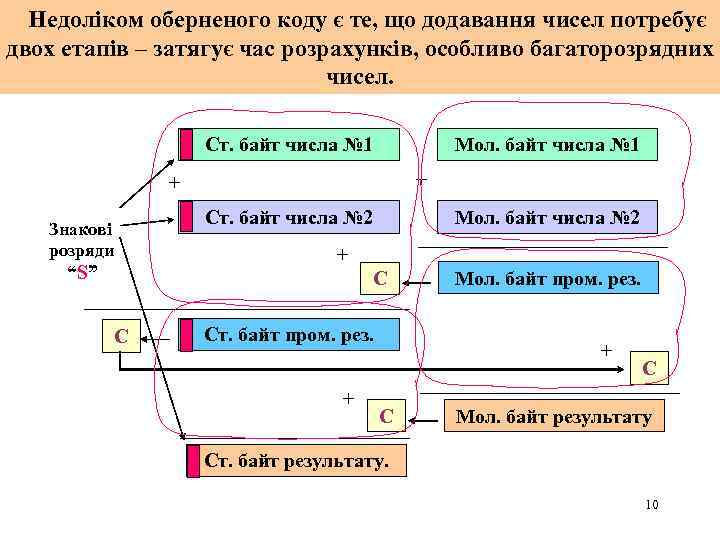

Недоліком оберненого коду є те, що додавання чисел потребує двох етапів – затягує час розрахунків, особливо багаторозрядних чисел. Ст. байт числа № 1 Мол. байт числа № 1 + + Знакові розряди “S” Ст. байт числа № 2 Мол. байт числа № 2 + С С Ст. байт пром. рез. + Мол. байт пром. рез. + С С Мол. байт результату Ст. байт результату. 10

Недоліком оберненого коду є те, що додавання чисел потребує двох етапів – затягує час розрахунків, особливо багаторозрядних чисел. Ст. байт числа № 1 Мол. байт числа № 1 + + Знакові розряди “S” Ст. байт числа № 2 Мол. байт числа № 2 + С С Ст. байт пром. рез. + Мол. байт пром. рез. + С С Мол. байт результату Ст. байт результату. 10

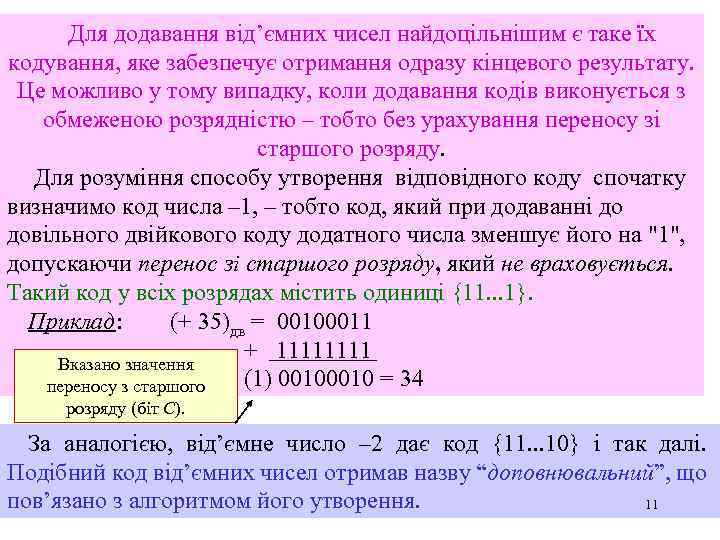

Для додавання від’ємних чисел найдоцільнішим є таке їх кодування, яке забезпечує отримання одразу кінцевого результату. Це можливо у тому випадку, коли додавання кодів виконується з обмеженою розрядністю – тобто без урахування переносу зі старшого розряду. Для розуміння способу утворення відповідного коду cпочатку визначимо код числа – 1, – тобто код, який при додаванні до довільного двійкового коду додатного числа зменшує його на "1", допускаючи перенос зі старшого розряду, який не враховується. Такий код у всіх розрядах містить одиниці {11. . . 1}. Приклад: (+ 35)дв = 00100011 + 1111 Вказано значення (1) 0010 = 34 переносу з старшого розряду (біт С). За аналогією, від’ємне число – 2 дає код {11. . . 10} і так далі. Подібний код від’ємних чисел отримав назву “доповнювальний”, що пов’язано з алгоритмом його утворення. 11

Для додавання від’ємних чисел найдоцільнішим є таке їх кодування, яке забезпечує отримання одразу кінцевого результату. Це можливо у тому випадку, коли додавання кодів виконується з обмеженою розрядністю – тобто без урахування переносу зі старшого розряду. Для розуміння способу утворення відповідного коду cпочатку визначимо код числа – 1, – тобто код, який при додаванні до довільного двійкового коду додатного числа зменшує його на "1", допускаючи перенос зі старшого розряду, який не враховується. Такий код у всіх розрядах містить одиниці {11. . . 1}. Приклад: (+ 35)дв = 00100011 + 1111 Вказано значення (1) 0010 = 34 переносу з старшого розряду (біт С). За аналогією, від’ємне число – 2 дає код {11. . . 10} і так далі. Подібний код від’ємних чисел отримав назву “доповнювальний”, що пов’язано з алгоритмом його утворення. 11

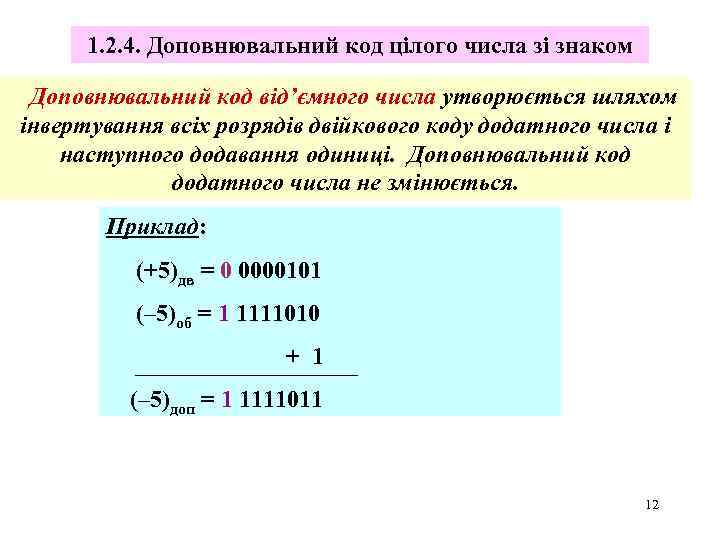

1. 2. 4. Доповнювальний код цілого числа зі знаком Доповнювальний код від’ємного числа утворюється шляхом інвертування всіх розрядів двійкового коду додатного числа і наступного додавання одиниці. Доповнювальний код додатного числа не змінюється. Приклад: (+5)дв = 0 0000101 (– 5)об = 1 1111010 + 1 (– 5)доп = 1 1111011 12

1. 2. 4. Доповнювальний код цілого числа зі знаком Доповнювальний код від’ємного числа утворюється шляхом інвертування всіх розрядів двійкового коду додатного числа і наступного додавання одиниці. Доповнювальний код додатного числа не змінюється. Приклад: (+5)дв = 0 0000101 (– 5)об = 1 1111010 + 1 (– 5)доп = 1 1111011 12

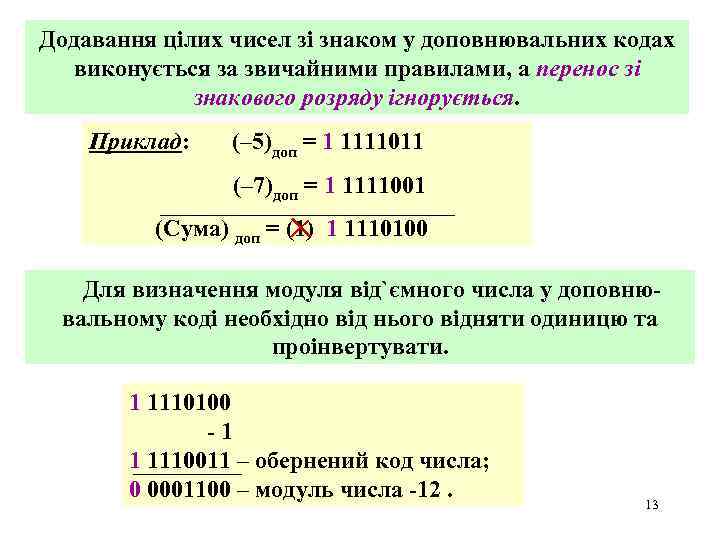

Додавання цілих чисел зі знаком у доповнювальних кодах виконується за звичайними правилами, а перенос зі знакового розряду ігнорується. Приклад: (– 5)доп = 1 1111011 (– 7)доп = 1 1111001 (Cума) доп = (1) 1 1110100 Для визначення модуля від`ємного числа у доповнювальному коді необхідно від нього відняти одиницю та проінвертувати. 1 1110100 -1 1 1110011 – обернений код числа; 0 0001100 – модуль числа -12. 13

Додавання цілих чисел зі знаком у доповнювальних кодах виконується за звичайними правилами, а перенос зі знакового розряду ігнорується. Приклад: (– 5)доп = 1 1111011 (– 7)доп = 1 1111001 (Cума) доп = (1) 1 1110100 Для визначення модуля від`ємного числа у доповнювальному коді необхідно від нього відняти одиницю та проінвертувати. 1 1110100 -1 1 1110011 – обернений код числа; 0 0001100 – модуль числа -12. 13

Приклад побайтного додавання багаторозрядних чисел у доповнювальних кодах Ст. байт числа № 1 + + Ст. байт числа № 2 Знакові розряди Мол. байт числа № 1 Мол. байт числа № 2 + С С Мол. байт результату Ст. байт результату. Перенос зі знакового розряду ігнорується. Висновок: за основу кодування цілих чисел зі знаком вибраний 14 доповнювальний код і всі процесори орієнтовані на його

Приклад побайтного додавання багаторозрядних чисел у доповнювальних кодах Ст. байт числа № 1 + + Ст. байт числа № 2 Знакові розряди Мол. байт числа № 1 Мол. байт числа № 2 + С С Мол. байт результату Ст. байт результату. Перенос зі знакового розряду ігнорується. Висновок: за основу кодування цілих чисел зі знаком вибраний 14 доповнювальний код і всі процесори орієнтовані на його

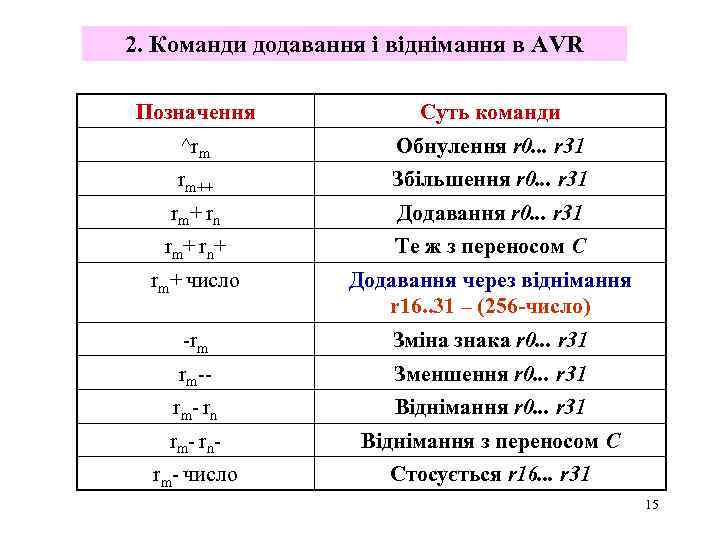

2. Команди додавання і віднімання в AVR Позначення Суть команди ^rm Обнулення r 0. . . r 31 rm++ Збільшення r 0. . . r 31 r m + r n Додавання r 0. . . r 31 rm+ rn+ Те ж з переносом С rm+ число Додавання через віднімання r 16. . 31 – (256 -число) -rm Зміна знака r 0. . . r 31 rm-- Зменшення r 0. . . r 31 r m - r n Віднімання r 0. . . r 31 rm- rn- Віднімання з переносом С rm- число Стосується r 16. . . r 31 15

2. Команди додавання і віднімання в AVR Позначення Суть команди ^rm Обнулення r 0. . . r 31 rm++ Збільшення r 0. . . r 31 r m + r n Додавання r 0. . . r 31 rm+ rn+ Те ж з переносом С rm+ число Додавання через віднімання r 16. . 31 – (256 -число) -rm Зміна знака r 0. . . r 31 rm-- Зменшення r 0. . . r 31 r m - r n Віднімання r 0. . . r 31 rm- rn- Віднімання з переносом С rm- число Стосується r 16. . . r 31 15

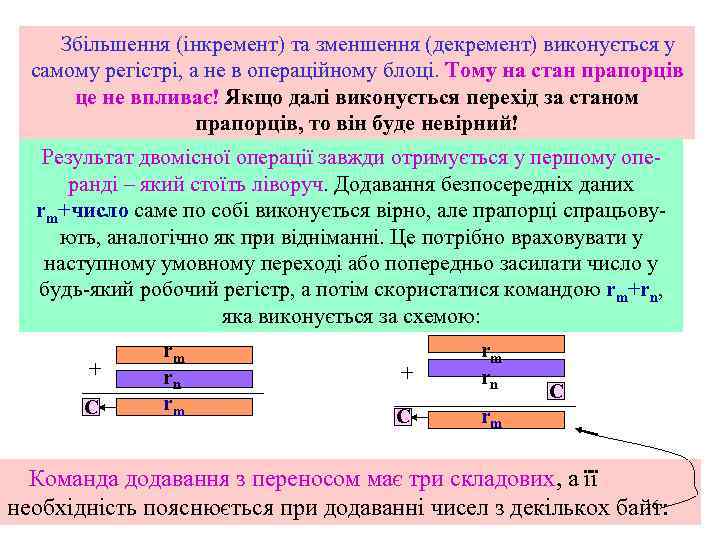

Збільшення (інкремент) та зменшення (декремент) виконується у самому регістрі, а не в операційному блоці. Тому на стан прапорців це не впливає! Якщо далі виконується перехід за станом прапорців, то він буде невірний! Результат двомісної операції завжди отримується у першому операнді – який стоїть ліворуч. Додавання безпосередніх даних rm+число саме по собі виконується вірно, але прапорці спрацьовують, аналогічно як при відніманні. Це потрібно враховувати у наступному умовному переході або попередньо засилати число у будь-який робочий регістр, а потім скористатися командою rm+rn, яка виконується за схемою: + С rm rn rm + rm rn С rm С Команда додавання з переносом має три складових, а її 16 необхідність пояснюється при додаванні чисел з декількох байт:

Збільшення (інкремент) та зменшення (декремент) виконується у самому регістрі, а не в операційному блоці. Тому на стан прапорців це не впливає! Якщо далі виконується перехід за станом прапорців, то він буде невірний! Результат двомісної операції завжди отримується у першому операнді – який стоїть ліворуч. Додавання безпосередніх даних rm+число саме по собі виконується вірно, але прапорці спрацьовують, аналогічно як при відніманні. Це потрібно враховувати у наступному умовному переході або попередньо засилати число у будь-який робочий регістр, а потім скористатися командою rm+rn, яка виконується за схемою: + С rm rn rm + rm rn С rm С Команда додавання з переносом має три складових, а її 16 необхідність пояснюється при додаванні чисел з декількох байт:

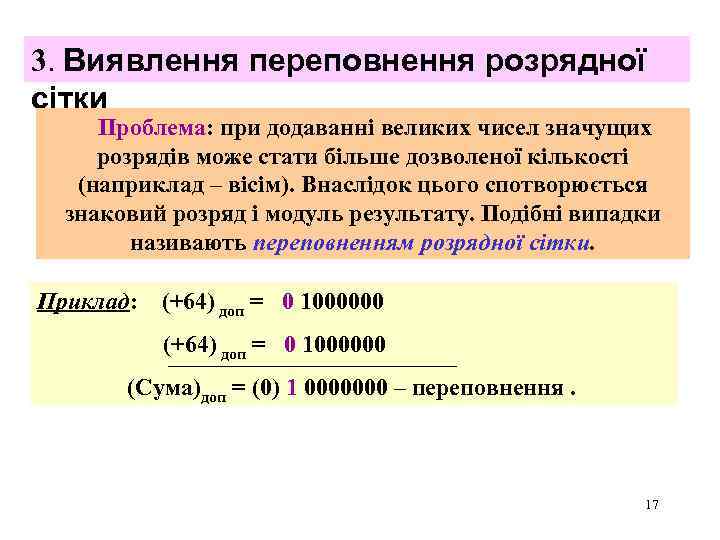

3. Виявлення переповнення розрядної сітки Проблема: при додаванні великих чисел значущих розрядів може стати більше дозволеної кількості (наприклад – вісім). Внаслідок цього спотворюється знаковий розряд і модуль результату. Подібні випадки називають переповненням розрядної сітки. Приклад: (+64) доп = 0 1000000 (Сума)доп = (0) 1 0000000 – переповнення. 17

3. Виявлення переповнення розрядної сітки Проблема: при додаванні великих чисел значущих розрядів може стати більше дозволеної кількості (наприклад – вісім). Внаслідок цього спотворюється знаковий розряд і модуль результату. Подібні випадки називають переповненням розрядної сітки. Приклад: (+64) доп = 0 1000000 (Сума)доп = (0) 1 0000000 – переповнення. 17

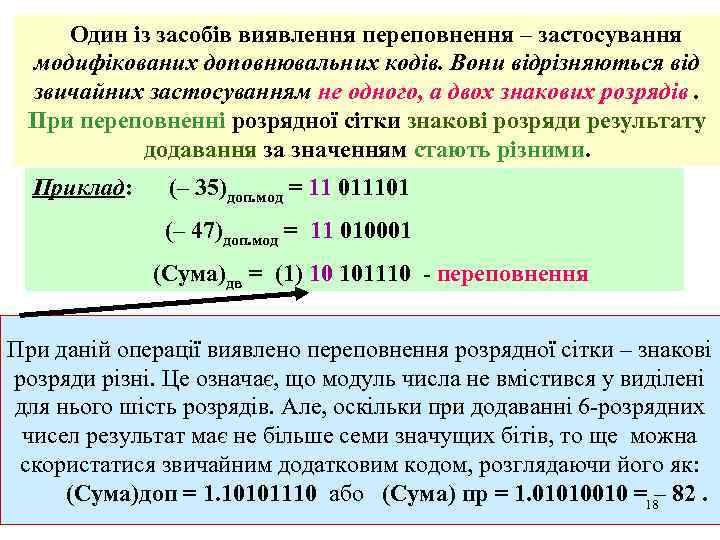

Один із засобів виявлення переповнення – застосування модифікованих доповнювальних кодів. Вони відрізняються від звичайних застосуванням не одного, а двох знакових розрядів. При переповненні розрядної сітки знакові розряди результату додавання за значенням стають різними. Приклад: (– 35)доп. мод = 11 011101 (– 47)доп. мод = 11 010001 (Cума)дв = (1) 10 101110 - переповнення При даній операції виявлено переповнення розрядної сітки – знакові розряди різні. Це означає, що модуль числа не вмістився у виділені для нього шість розрядів. Але, оскільки при додаванні 6 -розрядних чисел результат має не більше семи значущих бітів, то ще можна скористатися звичайним додатковим кодом, розглядаючи його як: (Сума)доп = 1. 10101110 або (Сума) пр = 1. 01010010 =18– 82.

Один із засобів виявлення переповнення – застосування модифікованих доповнювальних кодів. Вони відрізняються від звичайних застосуванням не одного, а двох знакових розрядів. При переповненні розрядної сітки знакові розряди результату додавання за значенням стають різними. Приклад: (– 35)доп. мод = 11 011101 (– 47)доп. мод = 11 010001 (Cума)дв = (1) 10 101110 - переповнення При даній операції виявлено переповнення розрядної сітки – знакові розряди різні. Це означає, що модуль числа не вмістився у виділені для нього шість розрядів. Але, оскільки при додаванні 6 -розрядних чисел результат має не більше семи значущих бітів, то ще можна скористатися звичайним додатковим кодом, розглядаючи його як: (Сума)доп = 1. 10101110 або (Сума) пр = 1. 01010010 =18– 82.

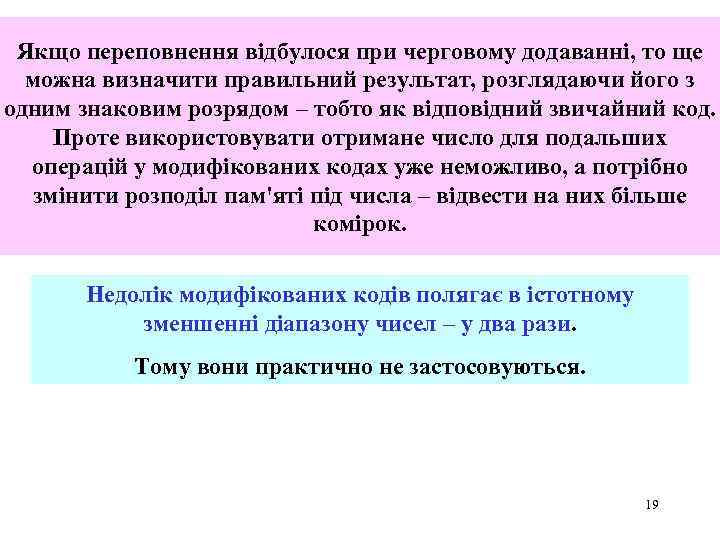

Якщо переповнення відбулося при черговому додаванні, то ще можна визначити правильний результат, розглядаючи його з одним знаковим розрядом – тобто як відповідний звичайний код. Проте використовувати отримане число для подальших операцій у модифікованих кодах уже неможливо, а потрібно змінити розподіл пам'яті під числа – відвести на них більше комірок. Недолік модифікованих кодів полягає в істотному зменшенні діапазону чисел – у два рази. Тому вони практично не застосовуються. 19

Якщо переповнення відбулося при черговому додаванні, то ще можна визначити правильний результат, розглядаючи його з одним знаковим розрядом – тобто як відповідний звичайний код. Проте використовувати отримане число для подальших операцій у модифікованих кодах уже неможливо, а потрібно змінити розподіл пам'яті під числа – відвести на них більше комірок. Недолік модифікованих кодів полягає в істотному зменшенні діапазону чисел – у два рази. Тому вони практично не застосовуються. 19

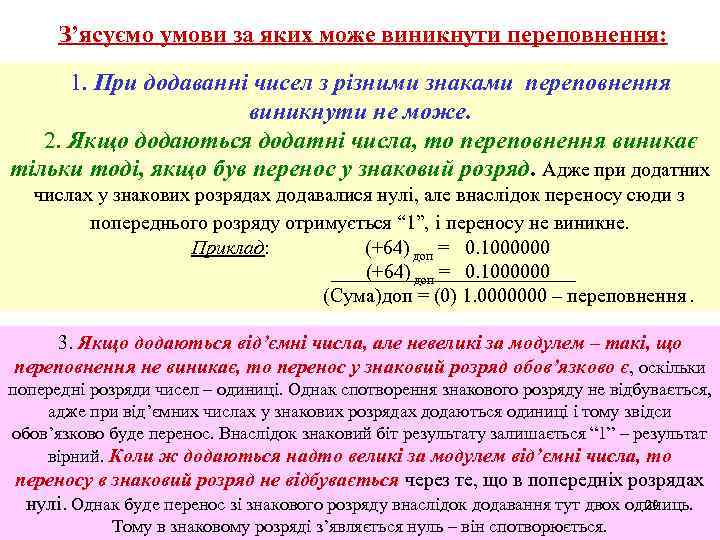

З’ясуємо умови за яких може виникнути переповнення: 1. При додаванні чисел з різними знаками переповнення виникнути не може. 2. Якщо додаються додатні числа, то переповнення виникає тільки тоді, якщо був перенос у знаковий розряд. Адже при додатних числах у знакових розрядах додавалися нулі, але внаслідок переносу сюди з попереднього розряду отримується “ 1”, і переносу не виникне. Приклад: (+64) доп = 0. 1000000 (Сума)доп = (0) 1. 0000000 – переповнення. 3. Якщо додаються від’ємні числа, але невеликі за модулем – такі, що переповнення не виникає, то перенос у знаковий розряд обов’язково є, оскільки попередні розряди чисел – одиниці. Однак спотворення знакового розряду не відбувається, адже при від’ємних числах у знакових розрядах додаються одиниці і тому звідси обов’язково буде перенос. Внаслідок знаковий біт результату залишається “ 1” – результат вірний. Коли ж додаються надто великі за модулем від’ємні числа, то переносу в знаковий розряд не відбувається через те, що в попередніх розрядах 20 нулі. Однак буде перенос зі знакового розряду внаслідок додавання тут двох одиниць. Тому в знаковому розряді з’являється нуль – він спотворюється.

З’ясуємо умови за яких може виникнути переповнення: 1. При додаванні чисел з різними знаками переповнення виникнути не може. 2. Якщо додаються додатні числа, то переповнення виникає тільки тоді, якщо був перенос у знаковий розряд. Адже при додатних числах у знакових розрядах додавалися нулі, але внаслідок переносу сюди з попереднього розряду отримується “ 1”, і переносу не виникне. Приклад: (+64) доп = 0. 1000000 (Сума)доп = (0) 1. 0000000 – переповнення. 3. Якщо додаються від’ємні числа, але невеликі за модулем – такі, що переповнення не виникає, то перенос у знаковий розряд обов’язково є, оскільки попередні розряди чисел – одиниці. Однак спотворення знакового розряду не відбувається, адже при від’ємних числах у знакових розрядах додаються одиниці і тому звідси обов’язково буде перенос. Внаслідок знаковий біт результату залишається “ 1” – результат вірний. Коли ж додаються надто великі за модулем від’ємні числа, то переносу в знаковий розряд не відбувається через те, що в попередніх розрядах 20 нулі. Однак буде перенос зі знакового розряду внаслідок додавання тут двох одиниць. Тому в знаковому розряді з’являється нуль – він спотворюється.

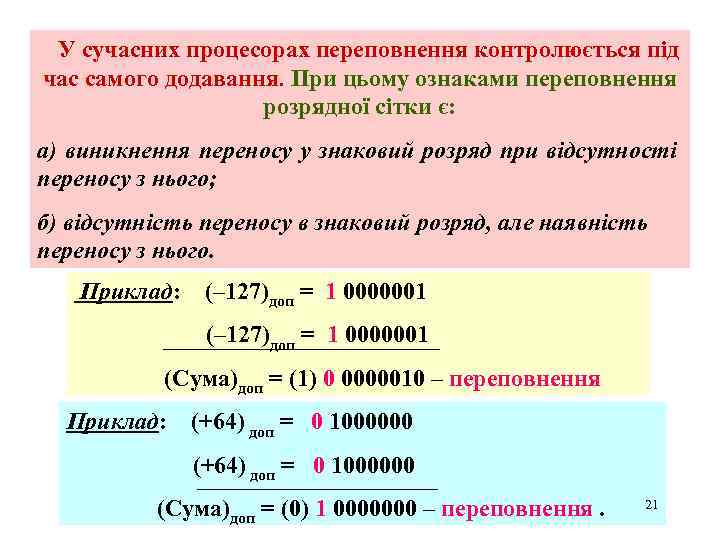

У сучасних процесорах переповнення контролюється під час самого додавання. При цьому ознаками переповнення розрядної сітки є: a) виникнення переносу у знаковий розряд при відсутності переносу з нього; б) відсутність переносу в знаковий розряд, але наявність переносу з нього. Приклад: (– 127)доп = 1 0000001 (Сума)доп = (1) 0 0000010 – переповнення Приклад: (+64) доп = 0 1000000 (Сума)доп = (0) 1 0000000 – переповнення. 21

У сучасних процесорах переповнення контролюється під час самого додавання. При цьому ознаками переповнення розрядної сітки є: a) виникнення переносу у знаковий розряд при відсутності переносу з нього; б) відсутність переносу в знаковий розряд, але наявність переносу з нього. Приклад: (– 127)доп = 1 0000001 (Сума)доп = (1) 0 0000010 – переповнення Приклад: (+64) доп = 0 1000000 (Сума)доп = (0) 1 0000000 – переповнення. 21

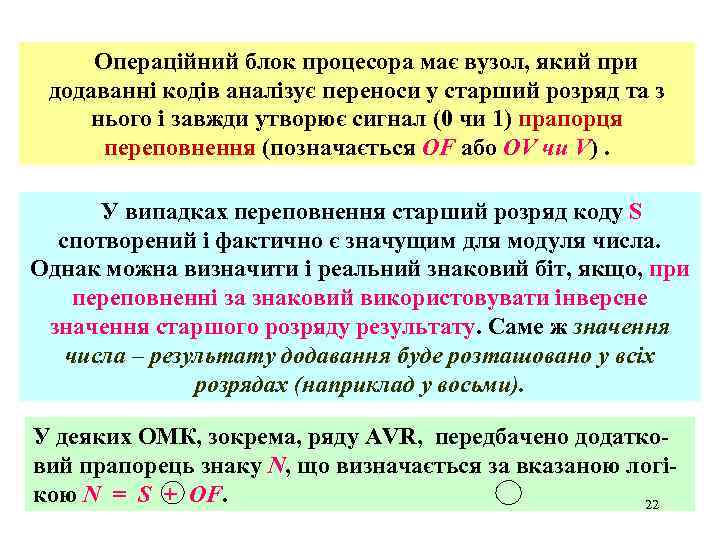

Операційний блок процесора має вузол, який при додаванні кодів аналізує переноси у старший розряд та з нього і завжди утворює сигнал (0 чи 1) прапорця переповнення (позначається OF або OV чи V). У випадках переповнення старший розряд коду S спотворений і фактично є значущим для модуля числа. Однак можна визначити і реальний знаковий біт, якщо, при переповненні за знаковий використовувати інверсне значення старшого розряду результату. Саме ж значення числа – результату додавання буде розташовано у всіх розрядах (наприклад у восьми). У деяких ОМК, зокрема, ряду AVR, передбачено додатковий прапорець знаку N, що визначається за вказаною логікою N = S + OF. 22

Операційний блок процесора має вузол, який при додаванні кодів аналізує переноси у старший розряд та з нього і завжди утворює сигнал (0 чи 1) прапорця переповнення (позначається OF або OV чи V). У випадках переповнення старший розряд коду S спотворений і фактично є значущим для модуля числа. Однак можна визначити і реальний знаковий біт, якщо, при переповненні за знаковий використовувати інверсне значення старшого розряду результату. Саме ж значення числа – результату додавання буде розташовано у всіх розрядах (наприклад у восьми). У деяких ОМК, зокрема, ряду AVR, передбачено додатковий прапорець знаку N, що визначається за вказаною логікою N = S + OF. 22

4. Особливості використання двійководесяткових кодів цілих чисел без знаку Двійково-десяткові коди чисел необхідні при їх виводі на індикатори з дешифраторами. Вони представляють собою четвірки розрядів, що в свою чергу представляють окремі цифри десяткового числа. В пам’яті ОМК ці значення можуть розташовуватися в окремих комірках (неупакована форма) або по дві тетради на байтову комірку. Зазвичай, тетрада може приймати значення лише у межах 0. . . 9. Приклад: (+ 35)дв. дес = 0011 0101 З такими кодами теж можуть виконуватися операції додавання у звичайних суматорах, але при відповідній корекції результату. 23

4. Особливості використання двійководесяткових кодів цілих чисел без знаку Двійково-десяткові коди чисел необхідні при їх виводі на індикатори з дешифраторами. Вони представляють собою четвірки розрядів, що в свою чергу представляють окремі цифри десяткового числа. В пам’яті ОМК ці значення можуть розташовуватися в окремих комірках (неупакована форма) або по дві тетради на байтову комірку. Зазвичай, тетрада може приймати значення лише у межах 0. . . 9. Приклад: (+ 35)дв. дес = 0011 0101 З такими кодами теж можуть виконуватися операції додавання у звичайних суматорах, але при відповідній корекції результату. 23

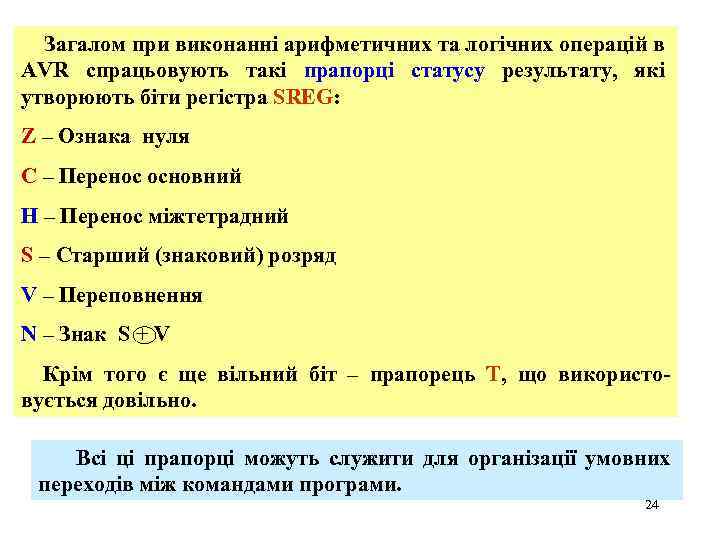

Загалом при виконанні арифметичних та логічних операцій в AVR спрацьовують такі прапорці статусу результату, які утворюють біти регістра SREG: Z – Ознака нуля C – Перенос основний H – Перенос міжтетрадний S – Старший (знаковий) розряд V – Переповнення N – Знак S + V Крім того є ще вільний біт – прапорець Т, що використовується довільно. Всі ці прапорці можуть служити для організації умовних переходів між командами програми. 24

Загалом при виконанні арифметичних та логічних операцій в AVR спрацьовують такі прапорці статусу результату, які утворюють біти регістра SREG: Z – Ознака нуля C – Перенос основний H – Перенос міжтетрадний S – Старший (знаковий) розряд V – Переповнення N – Знак S + V Крім того є ще вільний біт – прапорець Т, що використовується довільно. Всі ці прапорці можуть служити для організації умовних переходів між командами програми. 24

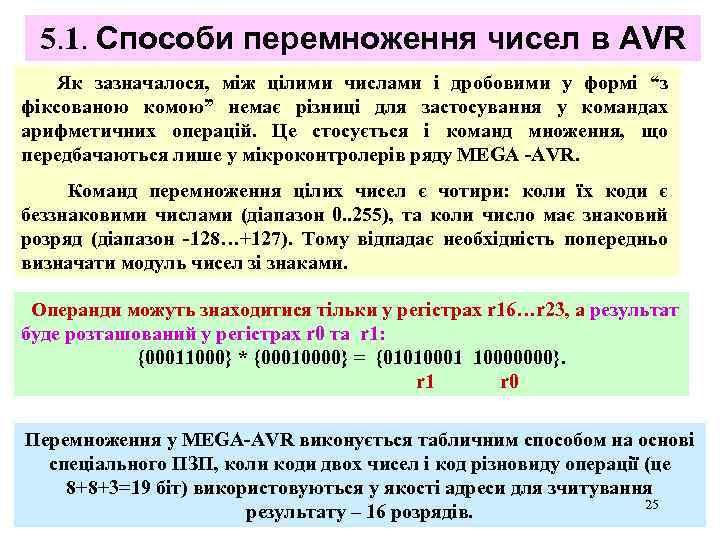

5. 1. Способи перемноження чисел в AVR Як зазначалося, між цілими числами і дробовими у формі “з фіксованою комою” немає різниці для застосування у командах арифметичних операцій. Це стосується і команд множення, що передбачаються лише у мікроконтролерів ряду MEGA -AVR. Команд перемноження цілих чисел є чотири: коли їх коди є беззнаковими числами (діапазон 0. . 255), та коли число має знаковий розряд (діапазон -128…+127). Тому відпадає необхідність попередньо визначати модуль чисел зі знаками. Операнди можуть знаходитися тільки у регістрах r 16…r 23, а результат буде розташований у регістрах r 0 та r 1: {00011000} * {00010000} = {01010001 10000000}. r 1 r 0 Перемноження у MEGA-AVR виконується табличним способом на основі спеціального ПЗП, коли коди двох чисел і код різновиду операції (це 8+8+3=19 біт) використовуються у якості адреси для зчитування 25 результату – 16 розрядів.

5. 1. Способи перемноження чисел в AVR Як зазначалося, між цілими числами і дробовими у формі “з фіксованою комою” немає різниці для застосування у командах арифметичних операцій. Це стосується і команд множення, що передбачаються лише у мікроконтролерів ряду MEGA -AVR. Команд перемноження цілих чисел є чотири: коли їх коди є беззнаковими числами (діапазон 0. . 255), та коли число має знаковий розряд (діапазон -128…+127). Тому відпадає необхідність попередньо визначати модуль чисел зі знаками. Операнди можуть знаходитися тільки у регістрах r 16…r 23, а результат буде розташований у регістрах r 0 та r 1: {00011000} * {00010000} = {01010001 10000000}. r 1 r 0 Перемноження у MEGA-AVR виконується табличним способом на основі спеціального ПЗП, коли коди двох чисел і код різновиду операції (це 8+8+3=19 біт) використовуються у якості адреси для зчитування 25 результату – 16 розрядів.

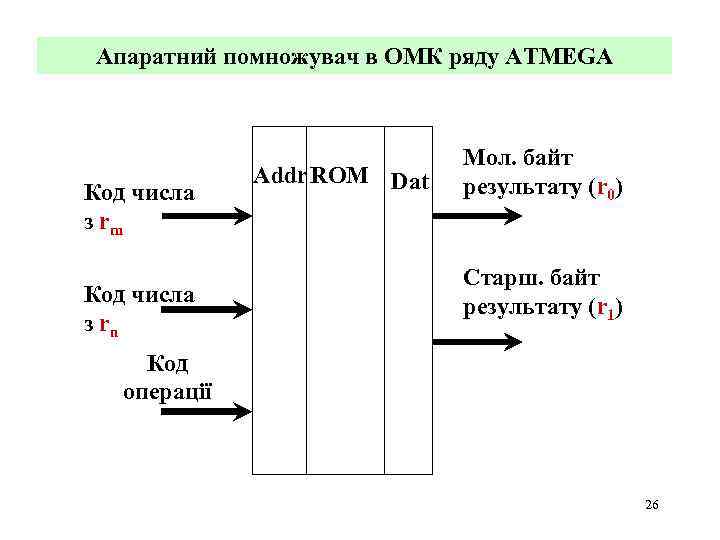

Апаратний помножувач в ОМК ряду ATMEGA Код числа з rm Код числа з rn Addr ROM Dat Мол. байт результату (r 0) Старш. байт результату (r 1) Код операції 26

Апаратний помножувач в ОМК ряду ATMEGA Код числа з rm Код числа з rn Addr ROM Dat Мол. байт результату (r 0) Старш. байт результату (r 1) Код операції 26

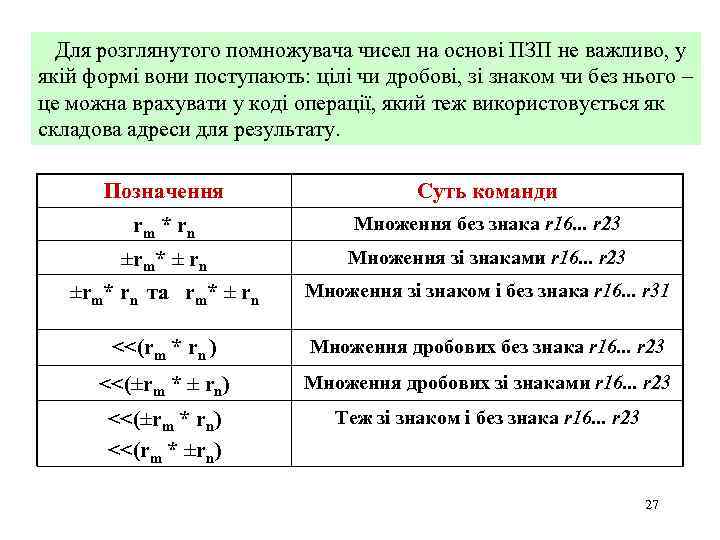

Для розглянутого помножувача чисел на основі ПЗП не важливо, у якій формі вони поступають: цілі чи дробові, зі знаком чи без нього – це можна врахувати у коді операції, який теж використовується як складова адреси для результату. Позначення Суть команди rm * rn Множення без знака r 16. . . r 23 ±rm* ± rn Множення зі знаками r 16. . . r 23 ±rm* rn та rm* ± rn Множення зі знаком і без знака r 16. . . r 31 <<(rm * rn ) Множення дробових без знака r 16. . . r 23 <<(±rm * ± rn) Множення дробових зі знаками r 16. . . r 23 <<(±rm * rn) <<(rm * ±rn) Теж зі знаком і без знака r 16. . . r 23 27

Для розглянутого помножувача чисел на основі ПЗП не важливо, у якій формі вони поступають: цілі чи дробові, зі знаком чи без нього – це можна врахувати у коді операції, який теж використовується як складова адреси для результату. Позначення Суть команди rm * rn Множення без знака r 16. . . r 23 ±rm* ± rn Множення зі знаками r 16. . . r 23 ±rm* rn та rm* ± rn Множення зі знаком і без знака r 16. . . r 31 <<(rm * rn ) Множення дробових без знака r 16. . . r 23 <<(±rm * ± rn) Множення дробових зі знаками r 16. . . r 23 <<(±rm * rn) <<(rm * ±rn) Теж зі знаком і без знака r 16. . . r 23 27

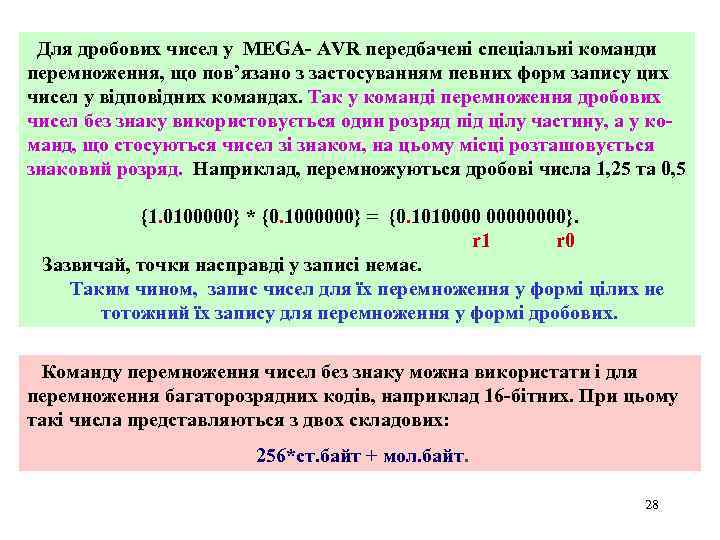

Для дробових чисел у MEGA- AVR передбачені спеціальні команди перемноження, що пов’язано з застосуванням певних форм запису цих чисел у відповідних командах. Так у команді перемноження дробових чисел без знаку використовується один розряд під цілу частину, а у команд, що стосуються чисел зі знаком, на цьому місці розташовується знаковий розряд. Наприклад, перемножуються дробові числа 1, 25 та 0, 5 {1. 0100000} * {0. 1000000} = {0. 1010000}. r 1 r 0 Зазвичай, точки насправді у записі немає. Таким чином, запис чисел для їх перемноження у формі цілих не тотожний їх запису для перемноження у формі дробових. Команду перемноження чисел без знаку можна використати і для перемноження багаторозрядних кодів, наприклад 16 -бітних. При цьому такі числа представляються з двох складових: 256*ст. байт + мол. байт. 28

Для дробових чисел у MEGA- AVR передбачені спеціальні команди перемноження, що пов’язано з застосуванням певних форм запису цих чисел у відповідних командах. Так у команді перемноження дробових чисел без знаку використовується один розряд під цілу частину, а у команд, що стосуються чисел зі знаком, на цьому місці розташовується знаковий розряд. Наприклад, перемножуються дробові числа 1, 25 та 0, 5 {1. 0100000} * {0. 1000000} = {0. 1010000}. r 1 r 0 Зазвичай, точки насправді у записі немає. Таким чином, запис чисел для їх перемноження у формі цілих не тотожний їх запису для перемноження у формі дробових. Команду перемноження чисел без знаку можна використати і для перемноження багаторозрядних кодів, наприклад 16 -бітних. При цьому такі числа представляються з двох складових: 256*ст. байт + мол. байт. 28

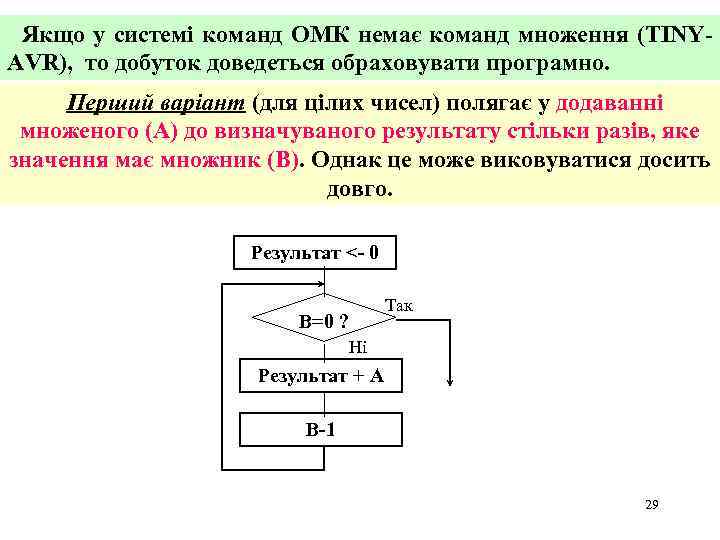

Якщо у системі команд ОМК немає команд множення (TINYAVR), то добуток доведеться обраховувати програмно. Перший варіант (для цілих чисел) полягає у додаванні множеного (А) до визначуваного результату стільки разів, яке значення має множник (В). Однак це може виковуватися досить довго. Результат <- 0 Так В=0 ? Ні Результат + А В-1 29

Якщо у системі команд ОМК немає команд множення (TINYAVR), то добуток доведеться обраховувати програмно. Перший варіант (для цілих чисел) полягає у додаванні множеного (А) до визначуваного результату стільки разів, яке значення має множник (В). Однак це може виковуватися досить довго. Результат <- 0 Так В=0 ? Ні Результат + А В-1 29

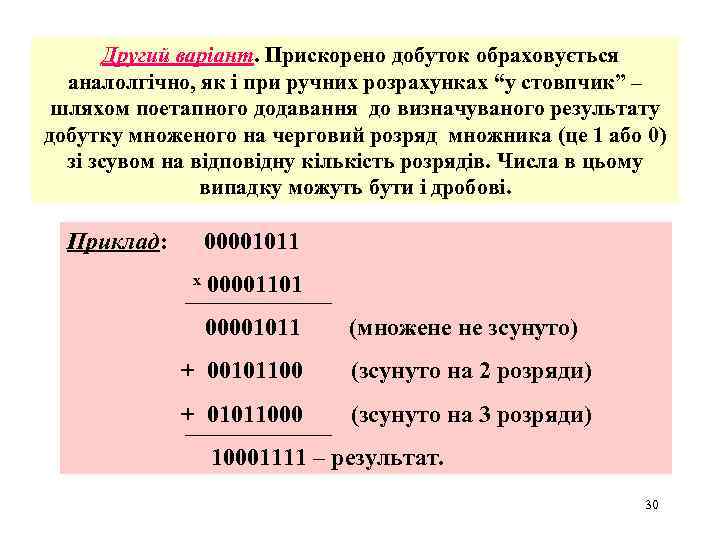

Другий варіант. Прискорено добуток обраховується аналолгічно, як і при ручних розрахунках “у стовпчик” – шляхом поетапного додавання до визначуваного результату добутку множеного на черговий розряд множника (це 1 або 0) зі зсувом на відповідну кількість розрядів. Числа в цьому випадку можуть бути і дробові. Приклад: 00001011 х 00001101 00001011 (множене не зсунуто) + 00101100 (зсунуто на 2 розряди) + 01011000 (зсунуто на 3 розряди) 10001111 – результат. 30

Другий варіант. Прискорено добуток обраховується аналолгічно, як і при ручних розрахунках “у стовпчик” – шляхом поетапного додавання до визначуваного результату добутку множеного на черговий розряд множника (це 1 або 0) зі зсувом на відповідну кількість розрядів. Числа в цьому випадку можуть бути і дробові. Приклад: 00001011 х 00001101 00001011 (множене не зсунуто) + 00101100 (зсунуто на 2 розряди) + 01011000 (зсунуто на 3 розряди) 10001111 – результат. 30

Третій варіант. Найшвидше отримати результат добутку чисел можна табличним способом на основі відповідного комбінаційного вузла чи ПЗП. В останньому випадку коди обох операндів разом використовуються за адресу комірки ПЗП, що містить результат. При 8 -розрядних операндах такий ПЗП повинен мати значний обсяг пам’яті: 216 х 16 біт = 128 Кбайт. Тому доцільно використовувати спеціалізований комбінаційний вузол. Важливо, що при перемноженні операндів розрядність результату є сумою їх розрядностей, а тому для його утримання потрібні комірки загалом подвійної розрядності. 31

Третій варіант. Найшвидше отримати результат добутку чисел можна табличним способом на основі відповідного комбінаційного вузла чи ПЗП. В останньому випадку коди обох операндів разом використовуються за адресу комірки ПЗП, що містить результат. При 8 -розрядних операндах такий ПЗП повинен мати значний обсяг пам’яті: 216 х 16 біт = 128 Кбайт. Тому доцільно використовувати спеціалізований комбінаційний вузол. Важливо, що при перемноженні операндів розрядність результату є сумою їх розрядностей, а тому для його утримання потрібні комірки загалом подвійної розрядності. 31

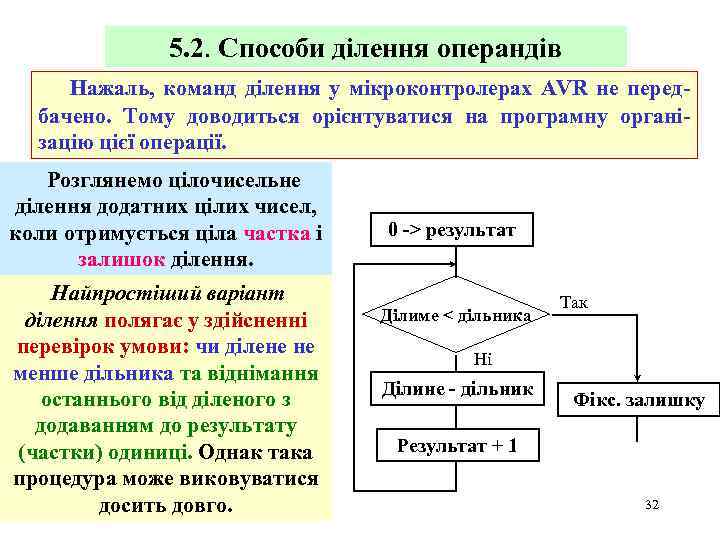

5. 2. Способи ділення операндів Нажаль, команд ділення у мікроконтролерах AVR не передбачено. Тому доводиться орієнтуватися на програмну організацію цієї операції. Розглянемо цілочисельне ділення додатних цілих чисел, коли отримується ціла частка і залишок ділення. Найпростіший варіант ділення полягає у здійсненні перевірок умови: чи ділене не менше дільника та віднімання останнього від діленого з додаванням до результату (частки) одиниці. Однак така процедура може виковуватися досить довго. 0 -> результат Ділиме < дільника Так Ні Ділине - дільник Фікс. залишку Результат + 1 32

5. 2. Способи ділення операндів Нажаль, команд ділення у мікроконтролерах AVR не передбачено. Тому доводиться орієнтуватися на програмну організацію цієї операції. Розглянемо цілочисельне ділення додатних цілих чисел, коли отримується ціла частка і залишок ділення. Найпростіший варіант ділення полягає у здійсненні перевірок умови: чи ділене не менше дільника та віднімання останнього від діленого з додаванням до результату (частки) одиниці. Однак така процедура може виковуватися досить довго. 0 -> результат Ділиме < дільника Так Ні Ділине - дільник Фікс. залишку Результат + 1 32

Прискорено ділення може полягати у поетапному відніманні дільника від діленого, починаючи з його старших розрядів, подібно ручній операції. Попередньо перевіряється перевищення діленого над дільником. Далі виконується зсув дільника ліворуч до вирівнювання кількості значущих розрядів з діленим. Потім дії циклічно повторюються. Загалом при організації обчислень необхідно: 1) вибрати форму кодування відповідних чисел в пам'яті МПП; 2) вибрати алгоритм виконання обчислювальних операцій; 3) спираючись на існуючі команди процесора МПП, скласти програму виконання необхідних дій алгоритму. Стосовно арифметичних операцій AVR то необхідно враховувати пректуванні програмного забезпечення, що ОМК мають суттєві обмеження, особливо TINY-AVR. 33

Прискорено ділення може полягати у поетапному відніманні дільника від діленого, починаючи з його старших розрядів, подібно ручній операції. Попередньо перевіряється перевищення діленого над дільником. Далі виконується зсув дільника ліворуч до вирівнювання кількості значущих розрядів з діленим. Потім дії циклічно повторюються. Загалом при організації обчислень необхідно: 1) вибрати форму кодування відповідних чисел в пам'яті МПП; 2) вибрати алгоритм виконання обчислювальних операцій; 3) спираючись на існуючі команди процесора МПП, скласти програму виконання необхідних дій алгоритму. Стосовно арифметичних операцій AVR то необхідно враховувати пректуванні програмного забезпечення, що ОМК мають суттєві обмеження, особливо TINY-AVR. 33