л7 Основные цифровые логические схемы.pptx

- Количество слайдов: 18

Лекция 7 Основные цифровые логические схемы

Лекция 7 Основные цифровые логические схемы

Логический вентиль — базовый элемент цифровой схемы, выполняющий элементарную логическую операцию, преобразуя таким образом множество входных логических сигналов в выходной логический сигнал. Логика работы вентиля основана на битовых операциях с входными цифровыми сигналами в качестве операндов.

Логический вентиль — базовый элемент цифровой схемы, выполняющий элементарную логическую операцию, преобразуя таким образом множество входных логических сигналов в выходной логический сигнал. Логика работы вентиля основана на битовых операциях с входными цифровыми сигналами в качестве операндов.

Интегральные схемы Вентили производятся и продаются не по отдельности, а в модулях, которые называются интегральными схемами (ИС), или микросхемами. Интегральная схема представляет собой квадратный кусок кремния размером примерно 5 x 5 мм, на котором располагаются несколько вентилей. Маленькие интегральные схемы обычно помещаются в прямоугольные пластиковые или керамические корпуса размером от 5 до 15 мм в ширину и от 20 до 50 мм в длину. Вдоль длинных сторон располагается два параллельных ряда выводов около 5 мм в длину, которые можно вставлять в разъемы или впаивать в печатную плату. Каждый вывод соединяется с входом или выходом какогонибудь вентиля, с источником питания или с «землей»

Интегральные схемы Вентили производятся и продаются не по отдельности, а в модулях, которые называются интегральными схемами (ИС), или микросхемами. Интегральная схема представляет собой квадратный кусок кремния размером примерно 5 x 5 мм, на котором располагаются несколько вентилей. Маленькие интегральные схемы обычно помещаются в прямоугольные пластиковые или керамические корпуса размером от 5 до 15 мм в ширину и от 20 до 50 мм в длину. Вдоль длинных сторон располагается два параллельных ряда выводов около 5 мм в длину, которые можно вставлять в разъемы или впаивать в печатную плату. Каждый вывод соединяется с входом или выходом какогонибудь вентиля, с источником питания или с «землей»

Интегральные схемы Микросхемы можно разделить на несколько классов с точки зрения количества вентилей, которые они содержат: - МИС (малая интегральная схема) — от 1 до 10 вентилей; - СИС (средняя интегральная схема) — от 10 до 100 вентилей; - БИС (большая интегральная схема) — от 100 до 100 000 вентилей; - СБИС (сверхбольшая интегральная схема) — более 100 000 вентилей. Эти схемы имеют различные свойства и используются для различных целей.

Интегральные схемы Микросхемы можно разделить на несколько классов с точки зрения количества вентилей, которые они содержат: - МИС (малая интегральная схема) — от 1 до 10 вентилей; - СИС (средняя интегральная схема) — от 10 до 100 вентилей; - БИС (большая интегральная схема) — от 100 до 100 000 вентилей; - СБИС (сверхбольшая интегральная схема) — более 100 000 вентилей. Эти схемы имеют различные свойства и используются для различных целей.

Интегральные схемы МИС обычно содержит от двух до шести независимых вентилей, каждый из которых может использоваться отдельно. На рисунке изображена обычная МИС, содержащая четыре вентиля НЕ-И. Каждый из этих вентилей имеет два входа и один выход, что требует 12 выводов. Кроме того, микросхеме требуются питание (Vcc) и земля. Они общие для всех вентилей. На корпусе рядом с выводом 1 обычно имеется паз, чтобы можно было определить, что это вывод 1. Чтобы избежать путаницы на диаграмме, по соглашению не показываются неиспользованные вентили, источник питания и земля.

Интегральные схемы МИС обычно содержит от двух до шести независимых вентилей, каждый из которых может использоваться отдельно. На рисунке изображена обычная МИС, содержащая четыре вентиля НЕ-И. Каждый из этих вентилей имеет два входа и один выход, что требует 12 выводов. Кроме того, микросхеме требуются питание (Vcc) и земля. Они общие для всех вентилей. На корпусе рядом с выводом 1 обычно имеется паз, чтобы можно было определить, что это вывод 1. Чтобы избежать путаницы на диаграмме, по соглашению не показываются неиспользованные вентили, источник питания и земля.

Интегральные схемы В настоящее время стало возможным помещать десятки миллионов транзисторов на одну микросхему. Так как любая схема может быть сконструирована из вентилей НЕ-И, может попробовать изготовить микросхему, содержащую 5 млн вентилей НЕ-И. Для создания такой микросхемы потребуется 15 000 002 выводов (Стандартный вывод занимает 0, 2 мм, соответственно, микросхема будет иметь в длину более 10 км). Для того, чтобы использовать преимущество данной технологии, нужно разработать такие схемы, в которых количество вентилей значительно превышает количество выводов (для вычисления той или иной функции несколько вентилей соединяются определенным образом между собой, что позволяет уменьшить число внешних выводов).

Интегральные схемы В настоящее время стало возможным помещать десятки миллионов транзисторов на одну микросхему. Так как любая схема может быть сконструирована из вентилей НЕ-И, может попробовать изготовить микросхему, содержащую 5 млн вентилей НЕ-И. Для создания такой микросхемы потребуется 15 000 002 выводов (Стандартный вывод занимает 0, 2 мм, соответственно, микросхема будет иметь в длину более 10 км). Для того, чтобы использовать преимущество данной технологии, нужно разработать такие схемы, в которых количество вентилей значительно превышает количество выводов (для вычисления той или иной функции несколько вентилей соединяются определенным образом между собой, что позволяет уменьшить число внешних выводов).

Комбинаторные схемы Многие применения цифровой логики требуют наличия схем с несколькими входами и несколькими выходами, в которых выходные сигналы определяются текущими входными сигналами. Такая схема называется комбинаторной. Мультиплексоры На цифровом логическом уровне мультиплексор представляет собой схему с входами, одним выходом и линиями управления, которые позволяют выбрать один из n входов. Выбранный вход соединяется с выходом. На рисунке изображена схема восьмивходового мультиплексора. Три линии управления, A, В и С, кодируют 3 -разрядное число, которое указывает, какая из восьми входных линий должна соединяться с вентилем ИЛИ и, следовательно, с выходом.

Комбинаторные схемы Многие применения цифровой логики требуют наличия схем с несколькими входами и несколькими выходами, в которых выходные сигналы определяются текущими входными сигналами. Такая схема называется комбинаторной. Мультиплексоры На цифровом логическом уровне мультиплексор представляет собой схему с входами, одним выходом и линиями управления, которые позволяют выбрать один из n входов. Выбранный вход соединяется с выходом. На рисунке изображена схема восьмивходового мультиплексора. Три линии управления, A, В и С, кодируют 3 -разрядное число, которое указывает, какая из восьми входных линий должна соединяться с вентилем ИЛИ и, следовательно, с выходом.

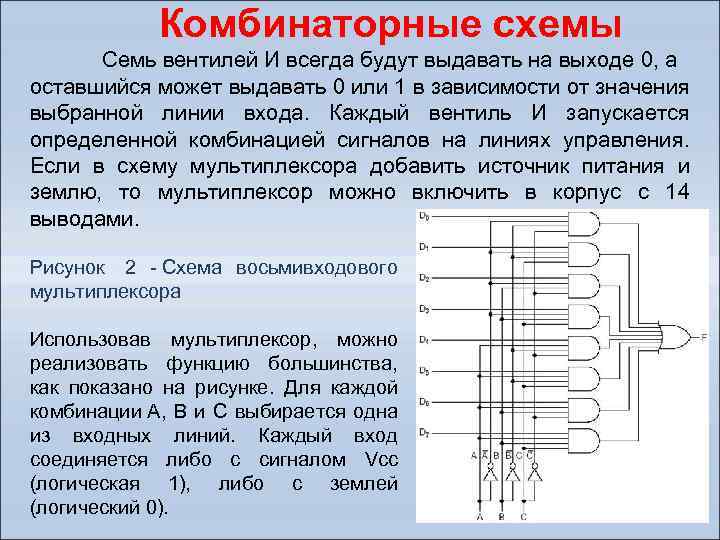

Комбинаторные схемы Семь вентилей И всегда будут выдавать на выходе 0, а оставшийся может выдавать 0 или 1 в зависимости от значения выбранной линии входа. Каждый вентиль И запускается определенной комбинацией сигналов на линиях управления. Если в схему мультиплексора добавить источник питания и землю, то мультиплексор можно включить в корпус с 14 выводами. Рисунок 2 - Схема восьмивходового мультиплексора Использовав мультиплексор, можно реализовать функцию большинства, как показано на рисунке. Для каждой комбинации A, В и С выбирается одна из входных линий. Каждый вход соединяется либо с сигналом Vcc (логическая 1), либо с землей (логический 0).

Комбинаторные схемы Семь вентилей И всегда будут выдавать на выходе 0, а оставшийся может выдавать 0 или 1 в зависимости от значения выбранной линии входа. Каждый вентиль И запускается определенной комбинацией сигналов на линиях управления. Если в схему мультиплексора добавить источник питания и землю, то мультиплексор можно включить в корпус с 14 выводами. Рисунок 2 - Схема восьмивходового мультиплексора Использовав мультиплексор, можно реализовать функцию большинства, как показано на рисунке. Для каждой комбинации A, В и С выбирается одна из входных линий. Каждый вход соединяется либо с сигналом Vcc (логическая 1), либо с землей (логический 0).

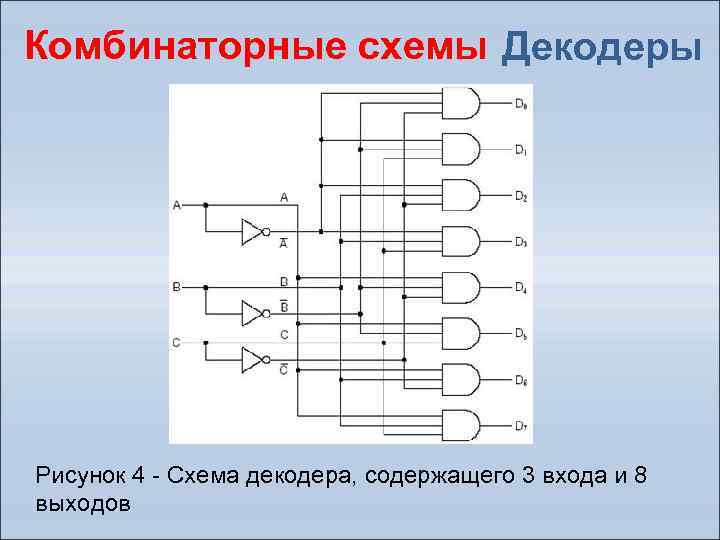

Комбинаторные схемы Декодеры Схема, которая получает на входе n-рядное число и использует его для того, чтобы выбрать (то есть установить в значение 1) одну из выходных линий, называется декодером. Пример декодера для n = 3 показан на рисунке. Пример использования декодера: Дана память, состоящая из 8 микросхем, каждая из которых содержит 1 Мбайт. Микросхема 0 имеет адреса от 0 до 1 Мбайт, микросхема 1 — адреса от 1 Мбайт до 2 Мбайт и т. д. Три старших двоичных разряда адреса используются для выбора одной из восьми микросхем. На рисунке эти три бита — три входа А, В и С. В зависимости от входных сигналов ровно одна из восьми выходных линий ( , . . . , ) принимает значение 1; остальные линии принимают значение 0. Каждая выходная линия запускает одну из восьми микросхем памяти. Поскольку только одна линия принимает значение 1, запускается только одна микросхема.

Комбинаторные схемы Декодеры Схема, которая получает на входе n-рядное число и использует его для того, чтобы выбрать (то есть установить в значение 1) одну из выходных линий, называется декодером. Пример декодера для n = 3 показан на рисунке. Пример использования декодера: Дана память, состоящая из 8 микросхем, каждая из которых содержит 1 Мбайт. Микросхема 0 имеет адреса от 0 до 1 Мбайт, микросхема 1 — адреса от 1 Мбайт до 2 Мбайт и т. д. Три старших двоичных разряда адреса используются для выбора одной из восьми микросхем. На рисунке эти три бита — три входа А, В и С. В зависимости от входных сигналов ровно одна из восьми выходных линий ( , . . . , ) принимает значение 1; остальные линии принимают значение 0. Каждая выходная линия запускает одну из восьми микросхем памяти. Поскольку только одна линия принимает значение 1, запускается только одна микросхема.

Комбинаторные схемы Декодеры Рисунок 4 - Схема декодера, содержащего 3 входа и 8 выходов

Комбинаторные схемы Декодеры Рисунок 4 - Схема декодера, содержащего 3 входа и 8 выходов

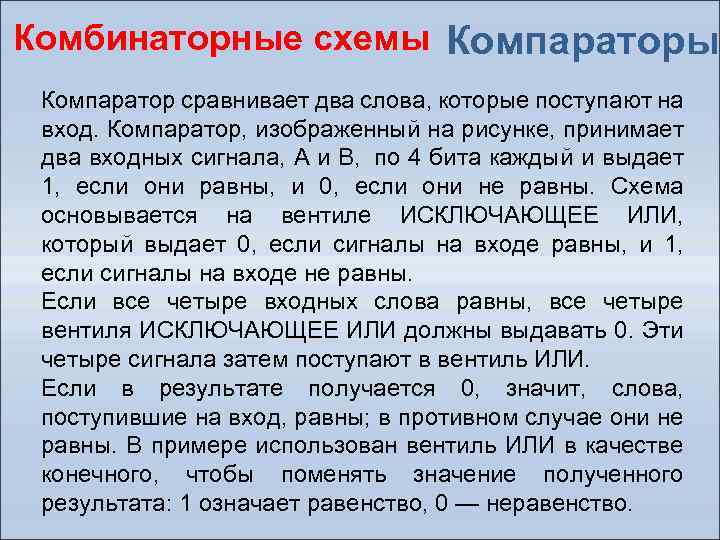

Комбинаторные схемы Компаратор сравнивает два слова, которые поступают на вход. Компаратор, изображенный на рисунке, принимает два входных сигнала, А и В, по 4 бита каждый и выдает 1, если они равны, и 0, если они не равны. Схема основывается на вентиле ИСКЛЮЧАЮЩЕЕ ИЛИ, который выдает 0, если сигналы на входе равны, и 1, если сигналы на входе не равны. Если все четыре входных слова равны, все четыре вентиля ИСКЛЮЧАЮЩЕЕ ИЛИ должны выдавать 0. Эти четыре сигнала затем поступают в вентиль ИЛИ. Если в результате получается 0, значит, слова, поступившие на вход, равны; в противном случае они не равны. В примере использован вентиль ИЛИ в качестве конечного, чтобы поменять значение полученного результата: 1 означает равенство, 0 — неравенство.

Комбинаторные схемы Компаратор сравнивает два слова, которые поступают на вход. Компаратор, изображенный на рисунке, принимает два входных сигнала, А и В, по 4 бита каждый и выдает 1, если они равны, и 0, если они не равны. Схема основывается на вентиле ИСКЛЮЧАЮЩЕЕ ИЛИ, который выдает 0, если сигналы на входе равны, и 1, если сигналы на входе не равны. Если все четыре входных слова равны, все четыре вентиля ИСКЛЮЧАЮЩЕЕ ИЛИ должны выдавать 0. Эти четыре сигнала затем поступают в вентиль ИЛИ. Если в результате получается 0, значит, слова, поступившие на вход, равны; в противном случае они не равны. В примере использован вентиль ИЛИ в качестве конечного, чтобы поменять значение полученного результата: 1 означает равенство, 0 — неравенство.

Комбинаторные схемы Компараторы Рисунок 5. 4 -х разрядный компаратор

Комбинаторные схемы Компараторы Рисунок 5. 4 -х разрядный компаратор

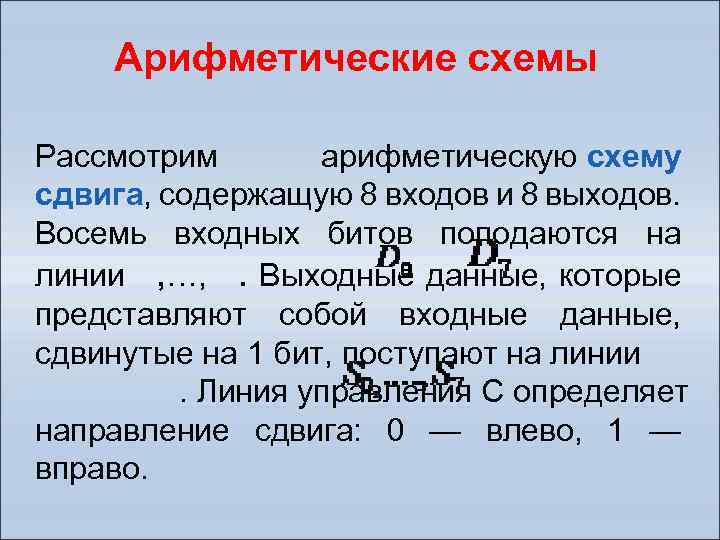

Арифметические схемы Рассмотрим арифметическую схему сдвига, содержащую 8 входов и 8 выходов. Восемь входных битов поподаются на линии , …, . Выходные данные, которые представляют собой входные данные, сдвинутые на 1 бит, поступают на линии . Линия управления С определяет направление сдвига: 0 — влево, 1 — вправо.

Арифметические схемы Рассмотрим арифметическую схему сдвига, содержащую 8 входов и 8 выходов. Восемь входных битов поподаются на линии , …, . Выходные данные, которые представляют собой входные данные, сдвинутые на 1 бит, поступают на линии . Линия управления С определяет направление сдвига: 0 — влево, 1 — вправо.

Арифметические схемы Рисунок 7 - Схема сдвига Рассмотрим пары вентилей И (кроме крайних). Если C=1, правый член каждой пары включается, пропуская через себя соответствующий бит. Так как правый вентиль И соединен с входом вентиля ИЛИ, который расположен справа от этого вентиля И, происходит сдвиг вправо. Если C=0, включается левый вентиль И из пары, и тогда происходит сдвиг влево.

Арифметические схемы Рисунок 7 - Схема сдвига Рассмотрим пары вентилей И (кроме крайних). Если C=1, правый член каждой пары включается, пропуская через себя соответствующий бит. Так как правый вентиль И соединен с входом вентиля ИЛИ, который расположен справа от этого вентиля И, происходит сдвиг вправо. Если C=0, включается левый вентиль И из пары, и тогда происходит сдвиг влево.

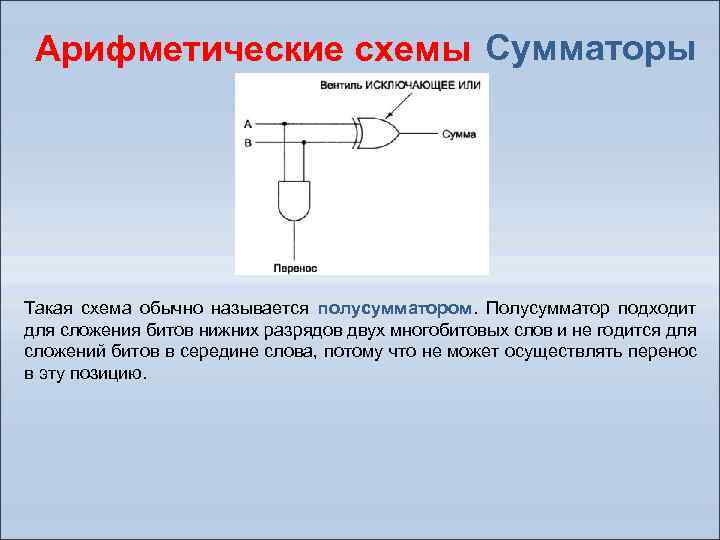

Арифметические схемы Сумматоры Схема выполнения операций сложения является существенной частью любого процессора. Таблица истинности для сложения одноразрядных целых чисел: Здесь имеется два результата: сумма входных переменных А и В и перенос на следующую (левую) позицию. Схема для вычисления бита суммы и бита переноса:

Арифметические схемы Сумматоры Схема выполнения операций сложения является существенной частью любого процессора. Таблица истинности для сложения одноразрядных целых чисел: Здесь имеется два результата: сумма входных переменных А и В и перенос на следующую (левую) позицию. Схема для вычисления бита суммы и бита переноса:

Арифметические схемы Сумматоры Такая схема обычно называется полусумматором. Полусумматор подходит для сложения битов нижних разрядов двух многобитовых слов и не годится для сложений битов в середине слова, потому что не может осуществлять перенос в эту позицию.

Арифметические схемы Сумматоры Такая схема обычно называется полусумматором. Полусумматор подходит для сложения битов нижних разрядов двух многобитовых слов и не годится для сложений битов в середине слова, потому что не может осуществлять перенос в эту позицию.

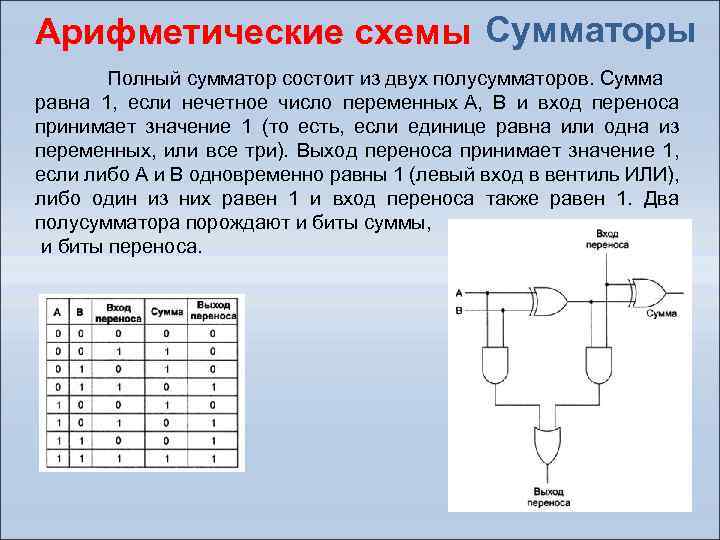

Арифметические схемы Сумматоры Полный сумматор состоит из двух полусумматоров. Сумма равна 1, если нечетное число переменных A, В и вход переноса принимает значение 1 (то есть, если единице равна или одна из переменных, или все три). Выход переноса принимает значение 1, если либо А и В одновременно равны 1 (левый вход в вентиль ИЛИ), либо один из них равен 1 и вход переноса также равен 1. Два полусумматора порождают и биты суммы, и биты переноса.

Арифметические схемы Сумматоры Полный сумматор состоит из двух полусумматоров. Сумма равна 1, если нечетное число переменных A, В и вход переноса принимает значение 1 (то есть, если единице равна или одна из переменных, или все три). Выход переноса принимает значение 1, если либо А и В одновременно равны 1 (левый вход в вентиль ИЛИ), либо один из них равен 1 и вход переноса также равен 1. Два полусумматора порождают и биты суммы, и биты переноса.

Арифметические схемы Сумматоры 16 -разрядный сумматор Чтобы построить сумматор для двух 16 разрядных слов, нужно 16 раз продублировать схему полного сумматора. Перенос производится в левый соседний бит. Перенос в самый правый бит соединен с 0. Такой сумматор называется сумматором со сквозным переносом. Прибавление 1 к числу 111. . . 111 не осуществится до тех пор, пока перенос не пройдет весь путь от самого правого бита к самому левому.

Арифметические схемы Сумматоры 16 -разрядный сумматор Чтобы построить сумматор для двух 16 разрядных слов, нужно 16 раз продублировать схему полного сумматора. Перенос производится в левый соседний бит. Перенос в самый правый бит соединен с 0. Такой сумматор называется сумматором со сквозным переносом. Прибавление 1 к числу 111. . . 111 не осуществится до тех пор, пока перенос не пройдет весь путь от самого правого бита к самому левому.