Lektsia_5_Programmiruemaya_logicheskaya_matritsa-dlya_studentov.ppt

- Количество слайдов: 25

ЛЕКЦИЯ № 5 Тема: Программируемые логические схемы Текст лекции по дисциплине «Цифровые устройства и микропроцессоры» 1

ЛЕКЦИЯ № 5 Тема: Программируемые логические схемы Текст лекции по дисциплине «Цифровые устройства и микропроцессоры» 1

УЧЕБНЫЕ ВОПРОСЫ: 1. Программируемая логическая матрица (ПЛМ) 2. Программируемые логические интегральные схемы (ПЛИС) 3. Методика и средства проектирования ЦУ ЛИТЕРАТУРА: Основная Л. 1. А. К. Нарышкин «Цифровые устройств и микропроцессоры» : учеб. пособие для студ. Высш. Учебн. Заведений/ А. К. Нарышкин, 2 – е изд. Издательский центр «Академия» , 2008 г. с. 131 138, 264 267 Л. 2. Ю. Ф. Опадчий, О. П. Глудкин, А. И. Гуров «Аналоговая и цифровая электроника» , М. Горячая линия Телеком, 2000 г. с. 728 736 Дополнительная литература Л. 5. Е. П. Угрюмов «Цифровая схемотехника» , Санкт Петербург, 2000 г. с. 357 368, 302 306 Л 6. Ю. А. Браммер. И. Н. Пашук «Импульсные и цифровые устройства» , М. Высшая школа, 1999 г. с. 306 307 2

УЧЕБНЫЕ ВОПРОСЫ: 1. Программируемая логическая матрица (ПЛМ) 2. Программируемые логические интегральные схемы (ПЛИС) 3. Методика и средства проектирования ЦУ ЛИТЕРАТУРА: Основная Л. 1. А. К. Нарышкин «Цифровые устройств и микропроцессоры» : учеб. пособие для студ. Высш. Учебн. Заведений/ А. К. Нарышкин, 2 – е изд. Издательский центр «Академия» , 2008 г. с. 131 138, 264 267 Л. 2. Ю. Ф. Опадчий, О. П. Глудкин, А. И. Гуров «Аналоговая и цифровая электроника» , М. Горячая линия Телеком, 2000 г. с. 728 736 Дополнительная литература Л. 5. Е. П. Угрюмов «Цифровая схемотехника» , Санкт Петербург, 2000 г. с. 357 368, 302 306 Л 6. Ю. А. Браммер. И. Н. Пашук «Импульсные и цифровые устройства» , М. Высшая школа, 1999 г. с. 306 307 2

Контрольные вопросы Записать аналитическое выражение логической операции, нарисовать условно графическое обозначение логического элемента, реализующего логическую функцию. 1 вариант ИЛИ 2 вариант И-НЕ 3 вариант И 4 вариант ИЛИ-НЕ 3

Контрольные вопросы Записать аналитическое выражение логической операции, нарисовать условно графическое обозначение логического элемента, реализующего логическую функцию. 1 вариант ИЛИ 2 вариант И-НЕ 3 вариант И 4 вариант ИЛИ-НЕ 3

1. Программируемая логическая матрица (ПЛМ) 4

1. Программируемая логическая матрица (ПЛМ) 4

Основные понятия и определения Программируемая логическая матрица представляет собой сетку ортогональных проводников (шин), в местах пересечения которых могут быть установлены полупроводниковые элементы с односторонней проводимостью (ЭОП) диоды или транзисторы. Назначение. ПЛМ служит для построения цифровых узлов, выполняющих различные логические функции. 5

Основные понятия и определения Программируемая логическая матрица представляет собой сетку ортогональных проводников (шин), в местах пересечения которых могут быть установлены полупроводниковые элементы с односторонней проводимостью (ЭОП) диоды или транзисторы. Назначение. ПЛМ служит для построения цифровых узлов, выполняющих различные логические функции. 5

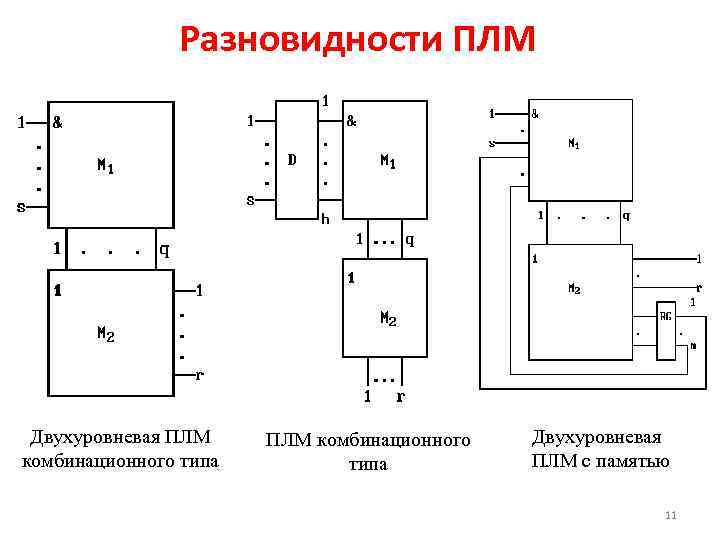

Классификация 1. По способу программирования ПЛМ делят на: матрицы, настраиваемые (программируемые) предприятием изготовителем (М-матрицы); матрицы, настраиваемые (программируемые) пользователем (Пматрицы); матрицы, репрограммируемые, то есть многократно настраиваемые (Р-матрицы). 2. В зависимости от внутренней организации ПЛМ делят на: ПЛМ комбинационной логики; • двухуровневые ПЛМ комбинационного типа; • трехуровневые ПЛМ комбинационного типа; ПЛМ с памятью; • двухуровневые ПЛМ с памятью; • трехуровневые ПЛМ с памятью. 6

Классификация 1. По способу программирования ПЛМ делят на: матрицы, настраиваемые (программируемые) предприятием изготовителем (М-матрицы); матрицы, настраиваемые (программируемые) пользователем (Пматрицы); матрицы, репрограммируемые, то есть многократно настраиваемые (Р-матрицы). 2. В зависимости от внутренней организации ПЛМ делят на: ПЛМ комбинационной логики; • двухуровневые ПЛМ комбинационного типа; • трехуровневые ПЛМ комбинационного типа; ПЛМ с памятью; • двухуровневые ПЛМ с памятью; • трехуровневые ПЛМ с памятью. 6

Условное графическое обозначение 7

Условное графическое обозначение 7

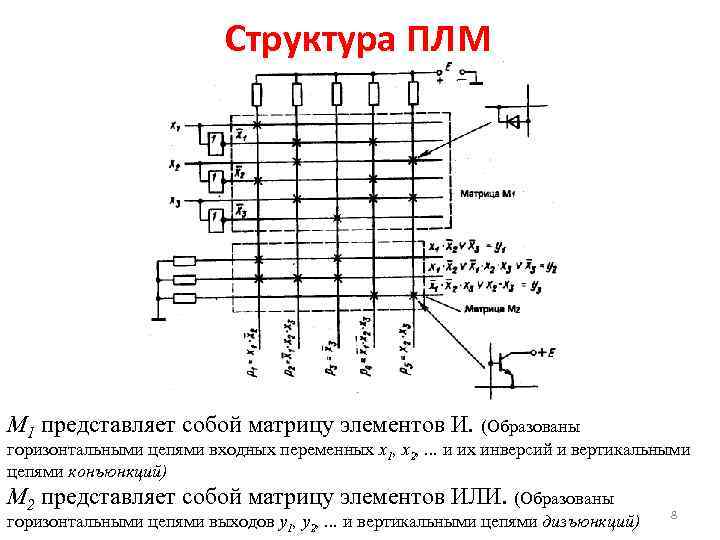

Структура ПЛМ М 1 представляет собой матрицу элементов И. (Образованы горизонтальными цепями входных переменных x 1, x 2, . . . и их инверсий и вертикальными цепями конъюнкций) М 2 представляет собой матрицу элементов ИЛИ. (Образованы горизонтальными цепями выходов у1, у2, . . . и вертикальными цепями дизъюнкций) 8

Структура ПЛМ М 1 представляет собой матрицу элементов И. (Образованы горизонтальными цепями входных переменных x 1, x 2, . . . и их инверсий и вертикальными цепями конъюнкций) М 2 представляет собой матрицу элементов ИЛИ. (Образованы горизонтальными цепями выходов у1, у2, . . . и вертикальными цепями дизъюнкций) 8

Принцип действия ПЛМ В отдельных узлах матрицы М 1 между ее вертикальными и горизонтальными цепями включены диоды. На вертикальной цепи образуется высокий потенциал (уровень лог. 1) в том случае, когда на всех входах, идущих к узлам, содержащим диоды, действует высокий потенциал (уровень лог. 1), закрывающий диоды. Если хотя бы на одном из таких входов будет низкий потенциал (уровень лог. 0), диод открывается и уровень лог. 0 с этого входа через открытый диод передается на вертикальную цепь матрицы. Т. о. вертикальные цепи формируют конъюнкции p 1 , р2, …. 9

Принцип действия ПЛМ В отдельных узлах матрицы М 1 между ее вертикальными и горизонтальными цепями включены диоды. На вертикальной цепи образуется высокий потенциал (уровень лог. 1) в том случае, когда на всех входах, идущих к узлам, содержащим диоды, действует высокий потенциал (уровень лог. 1), закрывающий диоды. Если хотя бы на одном из таких входов будет низкий потенциал (уровень лог. 0), диод открывается и уровень лог. 0 с этого входа через открытый диод передается на вертикальную цепь матрицы. Т. о. вертикальные цепи формируют конъюнкции p 1 , р2, …. 9

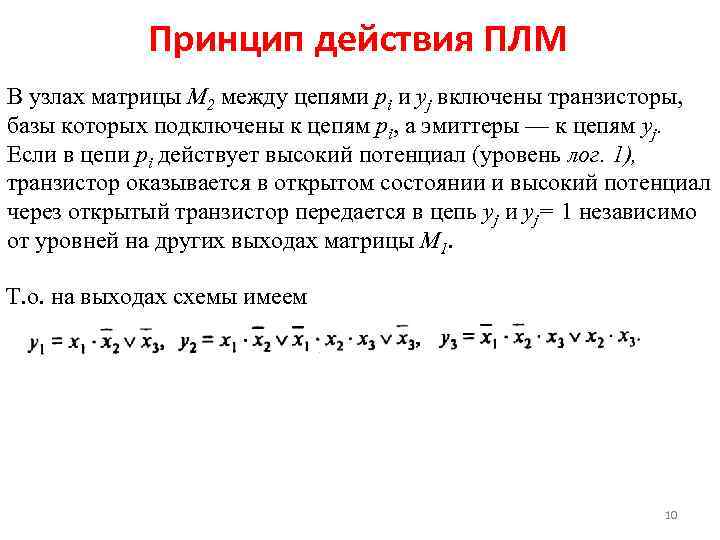

Принцип действия ПЛМ В узлах матрицы М 2 между цепями рi и уj включены транзисторы, базы которых подключены к цепям pi, а эмиттеры — к цепям уj. Если в цепи рi действует высокий потенциал (уровень лог. 1), транзистор оказывается в открытом состоянии и высокий потенциал через открытый транзистор передается в цепь уj и уj= 1 независимо от уровней на других выходах матрицы М 1. Т. о. на выходах схемы имеем 10

Принцип действия ПЛМ В узлах матрицы М 2 между цепями рi и уj включены транзисторы, базы которых подключены к цепям pi, а эмиттеры — к цепям уj. Если в цепи рi действует высокий потенциал (уровень лог. 1), транзистор оказывается в открытом состоянии и высокий потенциал через открытый транзистор передается в цепь уj и уj= 1 независимо от уровней на других выходах матрицы М 1. Т. о. на выходах схемы имеем 10

Разновидности ПЛМ Двухуровневая ПЛМ комбинационного типа Двухуровневая ПЛМ с памятью 11

Разновидности ПЛМ Двухуровневая ПЛМ комбинационного типа Двухуровневая ПЛМ с памятью 11

Вывод по 1 вопросу 1. ПЛМ является универсальным цифровым устройством, позволяющим реализовать логические функции различной сложности 12

Вывод по 1 вопросу 1. ПЛМ является универсальным цифровым устройством, позволяющим реализовать логические функции различной сложности 12

2. Программируемые логические интегральные схемы (ПЛИС) 13

2. Программируемые логические интегральные схемы (ПЛИС) 13

Основные понятия и определения ПЛИС — это матричные большие интегральные схемы Назначение. ПЛИС позволяют программно скомпоновать в одном корпусе электронную схему, эквивалентную схеме, включающей от нескольких десятков до нескольких сотен ИС стандарт ной логики. 14

Основные понятия и определения ПЛИС — это матричные большие интегральные схемы Назначение. ПЛИС позволяют программно скомпоновать в одном корпусе электронную схему, эквивалентную схеме, включающей от нескольких десятков до нескольких сотен ИС стандарт ной логики. 14

Классификация ПЛИС. 1. По типу программируемых элементов: • однократно программируемые (транзисторы с перемычками типа antifuse, с программированием плавающих затворов); • Репрограммируемые; а) с ультрафиолетовым стиранием (EPROM), б) с электрическим стиранием (EEPROM, FLASH), в) с триггерной памятью конфигурации (SRAM based)). 2. По архитектуре: • микросхемы с архитектурой EPLD (EPROM technology bazed complex Programmable Logic Device) — многократно программируемые; • микросхемы с архитектурой FPGA (Field Programmable Gate Array) — многократно реконфигурируемые. 15

Классификация ПЛИС. 1. По типу программируемых элементов: • однократно программируемые (транзисторы с перемычками типа antifuse, с программированием плавающих затворов); • Репрограммируемые; а) с ультрафиолетовым стиранием (EPROM), б) с электрическим стиранием (EEPROM, FLASH), в) с триггерной памятью конфигурации (SRAM based)). 2. По архитектуре: • микросхемы с архитектурой EPLD (EPROM technology bazed complex Programmable Logic Device) — многократно программируемые; • микросхемы с архитектурой FPGA (Field Programmable Gate Array) — многократно реконфигурируемые. 15

Устройство (особенности конструкции) Микросхема ПЛИС имеет в своём составе • память для хранения конфигурации (в ПЛИС EPLD использует ся ППЗУ с ультрафиолетовым стиранием, а у ПЛИС FPGA — статическое ОЗУ); • поля логических блоков (Логический блок — один из базовых элементов архитектуры ПЛИС FPGA, может выполнять любую логическую функцию в соответствии с заданной бито вой последовательностью (их называют. SLC – Simple Logic Cells)); • поля блоков ввода/вывода (могут быть настроены на выполнение любого электрического соединения реализованной внутри ПЛИС схемы с внешними устройствами через соответствующий контакт микросхемы. Содержат программно доступные ячейки памяти, логические элементы, триггеры, программируемые мультиплексоры. Имеют два канала – для ввода сигналов и для вывода); 16 • коммутационные блоки.

Устройство (особенности конструкции) Микросхема ПЛИС имеет в своём составе • память для хранения конфигурации (в ПЛИС EPLD использует ся ППЗУ с ультрафиолетовым стиранием, а у ПЛИС FPGA — статическое ОЗУ); • поля логических блоков (Логический блок — один из базовых элементов архитектуры ПЛИС FPGA, может выполнять любую логическую функцию в соответствии с заданной бито вой последовательностью (их называют. SLC – Simple Logic Cells)); • поля блоков ввода/вывода (могут быть настроены на выполнение любого электрического соединения реализованной внутри ПЛИС схемы с внешними устройствами через соответствующий контакт микросхемы. Содержат программно доступные ячейки памяти, логические элементы, триггеры, программируемые мультиплексоры. Имеют два канала – для ввода сигналов и для вывода); 16 • коммутационные блоки.

Производители ПЛИС • серии ХС 7200 и ХС 7300 — типа EPLD. Содержат от 18 до 144 многовходовых макроячеек, представляющих собой программируемое 1 разрядное. Ячейки объединяются матричным коммутатором. ИС могут быть использованы для нестан дартных АЛУ, дешифраторов, счетчиков и т. п. ; • серии ХС 2000, ХСЗ 000 — типа FPGA. Содержат от 2000 до 9000 экви валентных вентилей. Включают до 320 конфигурируемых логических блоков (КЛБ); • серия ХС 9500 — типа CPLD. Многократно перепрограммируемые (до 10000 раз) непосредственно на рабочем устройстве микросхемы. Со держат от 800 до 6400 рабочих ячеек или от 36 до 288 макроячеек, ана логичных серии ХС 7300. Рабочая частота — до 150 МГц. Все серии компании XILINX имеют высочайшую степень защиты от копи рования. 17

Производители ПЛИС • серии ХС 7200 и ХС 7300 — типа EPLD. Содержат от 18 до 144 многовходовых макроячеек, представляющих собой программируемое 1 разрядное. Ячейки объединяются матричным коммутатором. ИС могут быть использованы для нестан дартных АЛУ, дешифраторов, счетчиков и т. п. ; • серии ХС 2000, ХСЗ 000 — типа FPGA. Содержат от 2000 до 9000 экви валентных вентилей. Включают до 320 конфигурируемых логических блоков (КЛБ); • серия ХС 9500 — типа CPLD. Многократно перепрограммируемые (до 10000 раз) непосредственно на рабочем устройстве микросхемы. Со держат от 800 до 6400 рабочих ячеек или от 36 до 288 макроячеек, ана логичных серии ХС 7300. Рабочая частота — до 150 МГц. Все серии компании XILINX имеют высочайшую степень защиты от копи рования. 17

Вывод по 2 вопросу 1. Технология ПЛИС обес печивает рекордно короткий проектно технологический цикл (от нескольких часов до нескольких дней), минимальные затраты на проектирование, макси мальную гибкость при необходимости модификации аппаратуры. 2. На основе одной или нескольких микросхем FPGA можно создать реконфигурируемый процессор, обладающий преимуществами спецпро цессора на "жесткой" логике, но способного путем изменения содержимого ста тической памяти решать любые задачи, подобно универсальному процессору. 18

Вывод по 2 вопросу 1. Технология ПЛИС обес печивает рекордно короткий проектно технологический цикл (от нескольких часов до нескольких дней), минимальные затраты на проектирование, макси мальную гибкость при необходимости модификации аппаратуры. 2. На основе одной или нескольких микросхем FPGA можно создать реконфигурируемый процессор, обладающий преимуществами спецпро цессора на "жесткой" логике, но способного путем изменения содержимого ста тической памяти решать любые задачи, подобно универсальному процессору. 18

3. Методика и средства проектирования ЦУ 19

3. Методика и средства проектирования ЦУ 19

Основные понятия и определения Проектирование — разработка технической документации, позволяющей изготовить заданное устройство в заданных условиях. Стратегия проектирования — функциональная декомпозиция. • Для системы в целом и ее блоков используется концепция "черного ящика". • Для "черного ящика" разрабатывается функциональная спецификация, включающая внешнее описание блока (входы и выходы) и внутреннее описание — функ цию или алгоритм работы: F= Ф (X, t), где Х — вектор входных величин; F — вектор выходных величин; t — время. • Функция Ф разбивается на более простые функции Ф 1 Фк, между которыми должны быть установлены определенные связи, соответствующие принятому алго ритму реализации функции Ф. • В результате разбиения в конечном счете по лучается структура. 20 Переход от функции к структуре называется синтез.

Основные понятия и определения Проектирование — разработка технической документации, позволяющей изготовить заданное устройство в заданных условиях. Стратегия проектирования — функциональная декомпозиция. • Для системы в целом и ее блоков используется концепция "черного ящика". • Для "черного ящика" разрабатывается функциональная спецификация, включающая внешнее описание блока (входы и выходы) и внутреннее описание — функ цию или алгоритм работы: F= Ф (X, t), где Х — вектор входных величин; F — вектор выходных величин; t — время. • Функция Ф разбивается на более простые функции Ф 1 Фк, между которыми должны быть установлены определенные связи, соответствующие принятому алго ритму реализации функции Ф. • В результате разбиения в конечном счете по лучается структура. 20 Переход от функции к структуре называется синтез.

Основные понятия и определения • Выбор наилучшего варианта при синтезе осуществляется по ре зультатам анализа(проверяется правильность работы и некоторые по казатели, характеризующие устройство). • Декомпозиция функций блоков выполняется до тех пор, пока не получатся типовые функции, каждая из которых может быть реализована той или иной микросхемой. • Процесс проектирования — многошаговый и итерационный, с возвратами назад и пересмотром ранее принятых решений. • Декомпозиция заканчивается при получении типовых функций, которые соответствуют тем или иным микросхемам или элементам функциональных библиотек программируемых БИС/СБИС. • Характер проектирования существенно зависит от вида применяемой элементной базы. 21

Основные понятия и определения • Выбор наилучшего варианта при синтезе осуществляется по ре зультатам анализа(проверяется правильность работы и некоторые по казатели, характеризующие устройство). • Декомпозиция функций блоков выполняется до тех пор, пока не получатся типовые функции, каждая из которых может быть реализована той или иной микросхемой. • Процесс проектирования — многошаговый и итерационный, с возвратами назад и пересмотром ранее принятых решений. • Декомпозиция заканчивается при получении типовых функций, которые соответствуют тем или иным микросхемам или элементам функциональных библиотек программируемых БИС/СБИС. • Характер проектирования существенно зависит от вида применяемой элементной базы. 21

Классификация цифровых ИС с точки зрения методов проектирования 22

Классификация цифровых ИС с точки зрения методов проектирования 22

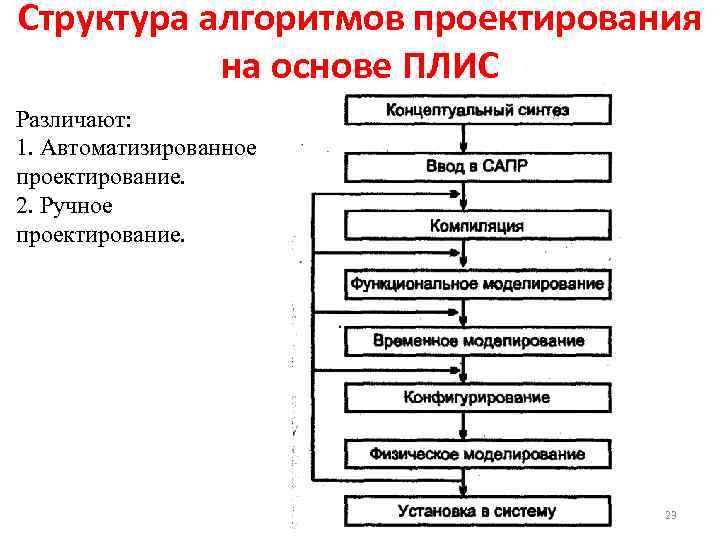

Структура алгоритмов проектирования на основе ПЛИС Различают: 1. Автоматизированное проектирование. 2. Ручное проектирование. 23

Структура алгоритмов проектирования на основе ПЛИС Различают: 1. Автоматизированное проектирование. 2. Ручное проектирование. 23

Вывод по 3 вопросу 1. При проектировании цифрового устройства либо ручным либо автоматизированным способом всегда придерживаются определённого алгоритма 24

Вывод по 3 вопросу 1. При проектировании цифрового устройства либо ручным либо автоматизированным способом всегда придерживаются определённого алгоритма 24

Заключение 1. ПЛМ служит для построения цифровых узлов, аппаратно реализующих быстрые алгоритмы логики управления. 2. Шинные формирователи предназначены для согласования входов выходов других цифровых устройств в узлах передачи данных и для управления направлением передачи данных в шинах. 3. Технология ПЛИС обес печивает рекордно короткий проектно технологический цикл, минимальные затраты на проектирование, макси мальную гибкость при необходимости модификации аппаратуры. 4. При проектировании цифрового устройства независимо от способа всегда придерживаются определённого алгоритма. 25

Заключение 1. ПЛМ служит для построения цифровых узлов, аппаратно реализующих быстрые алгоритмы логики управления. 2. Шинные формирователи предназначены для согласования входов выходов других цифровых устройств в узлах передачи данных и для управления направлением передачи данных в шинах. 3. Технология ПЛИС обес печивает рекордно короткий проектно технологический цикл, минимальные затраты на проектирование, макси мальную гибкость при необходимости модификации аппаратуры. 4. При проектировании цифрового устройства независимо от способа всегда придерживаются определённого алгоритма. 25