Цифровая схемотехника 2013 Лекция 02 VHDL.ppt

- Количество слайдов: 49

Лекция 2 ОБЩЕЕ ПОНЯТИЕ О ЯЗЫКЕ VHDL.

Языки описания аппаратуры VHDL – VHSIC (Very High Speed Integrated Circuit) Hardware Description Language. IEEE Std 1076, 2008 Edition Verilog HDL – Verilog Hardware Description Language. IEEE Std 1364, 2005 Edition ◦ System. Verilog, Verilog-ASM AHDL – внутренний язык компании Altera Abel – внутренний язык компании Xilinx System. C, … IEEE – Institute of Electrical and Electronics Engineers 2

Какой язык учить? Английский! http: //lingualeo. com 3

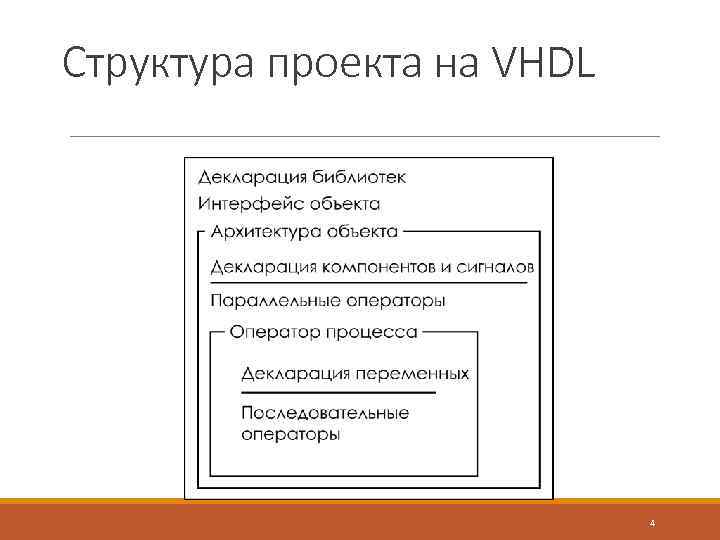

Структура проекта на VHDL 4

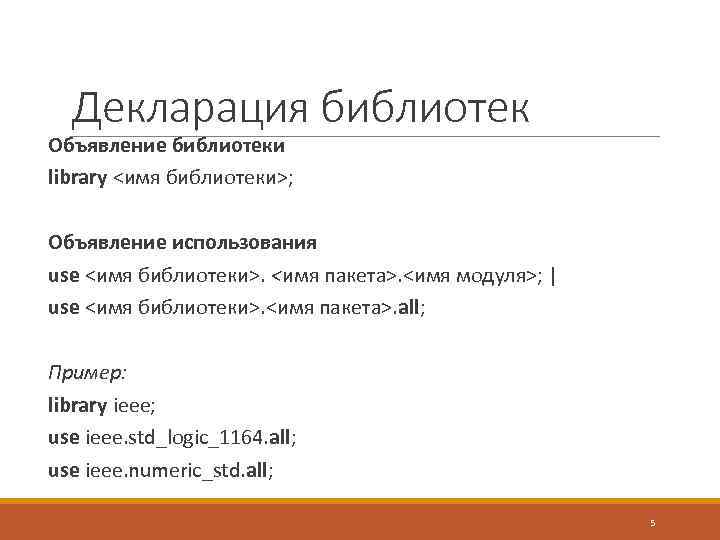

Декларация библиотек Объявление библиотеки library <имя библиотеки>; Объявление использования use <имя библиотеки>. <имя пакета>. <имя модуля>; | use <имя библиотеки>. <имя пакета>. all; Пример: library ieee; use ieee. std_logic_1164. all; use ieee. numeric_std. all; 5

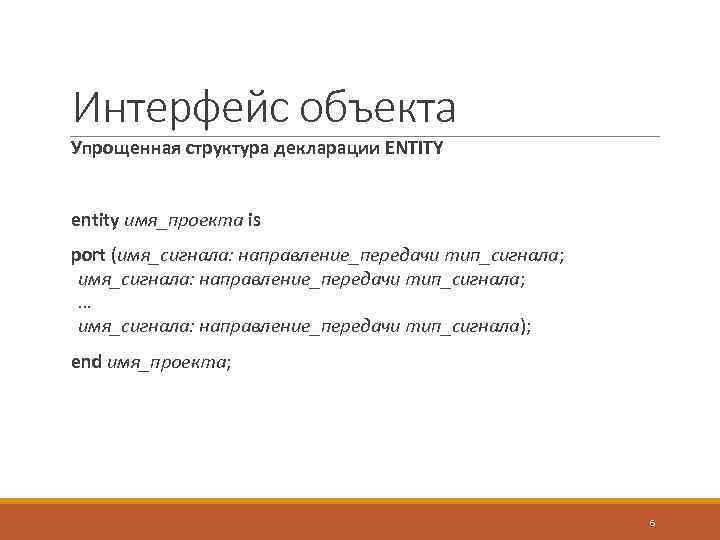

Интерфейс объекта Упрощенная структура декларации ENTITY entity имя_проекта is port (имя_сигнала: направление_передачи тип_сигнала; … имя_сигнала: направление_передачи тип_сигнала); end имя_проекта; 6

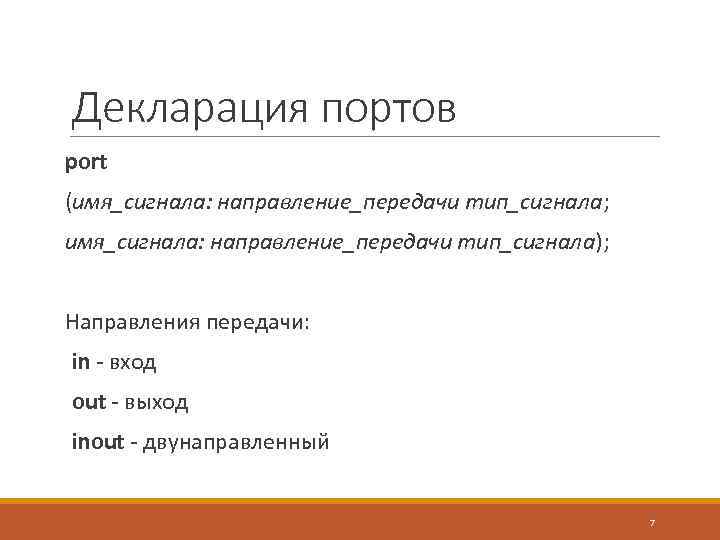

Декларация портов port (имя_сигнала: направление_передачи тип_сигнала; имя_сигнала: направление_передачи тип_сигнала); Направления передачи: in - вход out - выход inout - двунаправленный 7

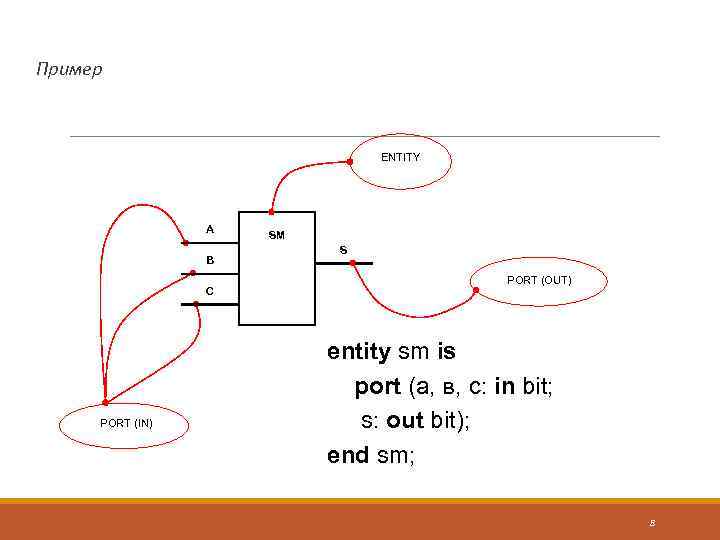

Пример ENTITY А В С PORT (IN) SM S PORT (OUT) entity sm is port (а, в, с: in bit; s: out bit); end sm; 8

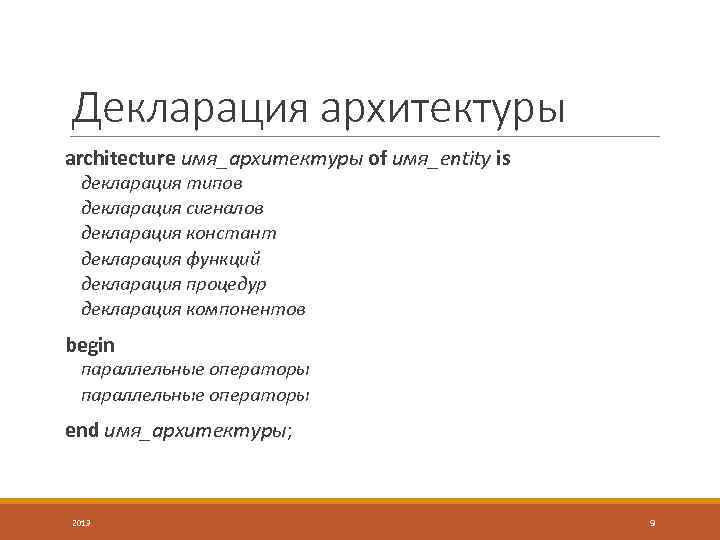

Декларация архитектуры architecture имя_архитектуры of имя_entity is декларация типов декларация сигналов декларация констант декларация функций декларация процедур декларация компонентов begin параллельные операторы end имя_архитектуры; 2013 9

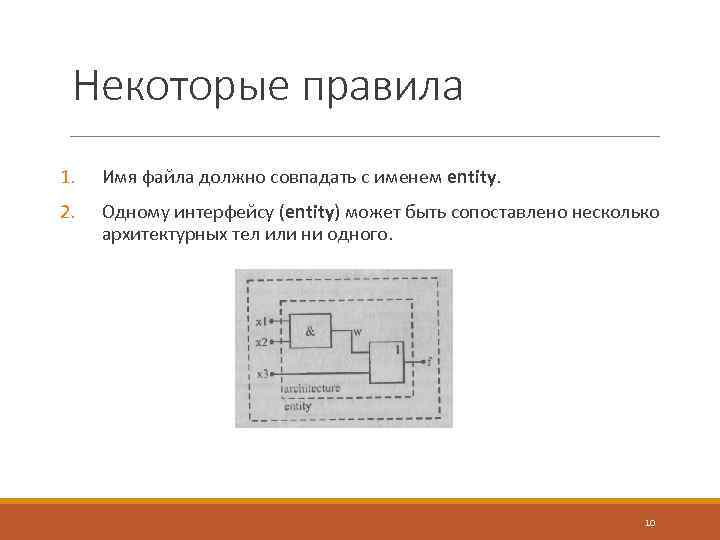

Некоторые правила 1. Имя файла должно совпадать с именем entity. 2. Одному интерфейсу (entity) может быть сопоставлено несколько архитектурных тел или ни одного. 10

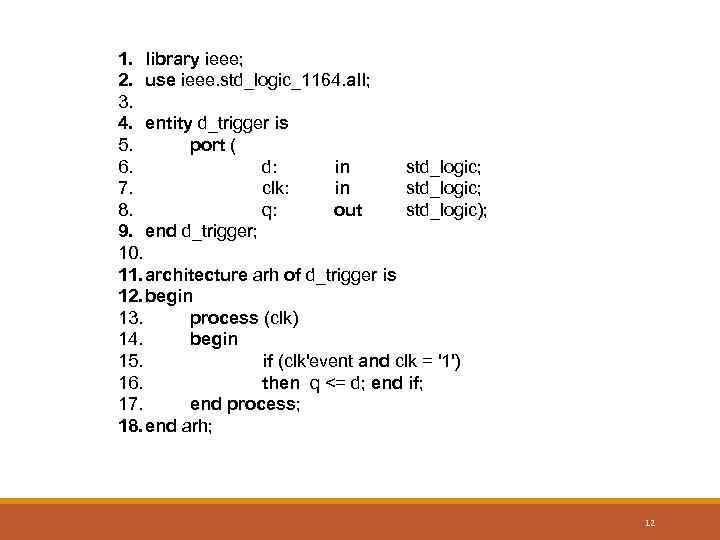

Простеший пример 11

1. library ieee; 2. use ieee. std_logic_1164. all; 3. 4. entity d_trigger is 5. port ( 6. d: in std_logic; 7. clk: in std_logic; 8. q: out std_logic); 9. end d_trigger; 10. 11. architecture arh of d_trigger is 12. begin 13. process (clk) 14. begin 15. if (clk'event and clk = '1') 16. then q <= d; end if; 17. end process; 18. end arh; 12

Объекты языка VHDL 13

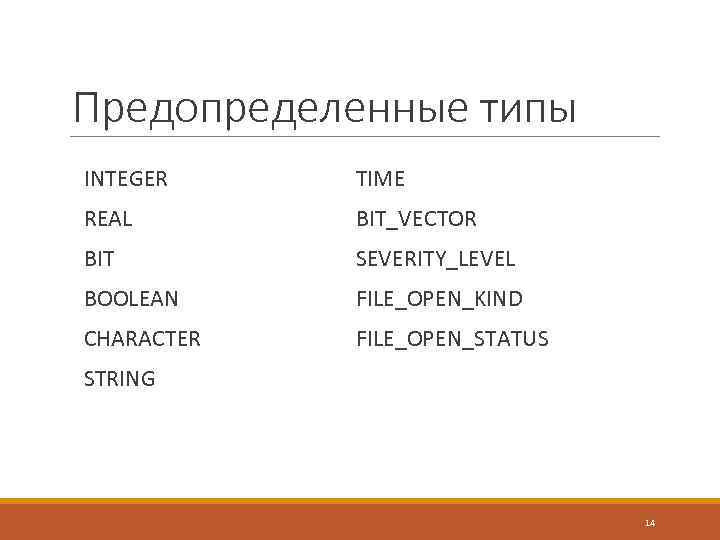

Предопределенные типы INTEGER TIME REAL BIT_VECTOR BIT SEVERITY_LEVEL BOOLEAN FILE_OPEN_KIND CHARACTER FILE_OPEN_STATUS STRING 14

Типы BIT и BOOLEAN BIT значения {'0', '1'}. BOOLEAN значения {TRUE, FALSE}. 15

Разница BIT и BOOLEAN SELECT определена как BIT: ◦ IF select THEN. . . – неправильно ◦ IF select = '1' THEN. . . – правильно SELECT определена как BOOLEAN ◦ IF select THEN. . . – правильно ◦ IF select = '1' THEN. . . – неправильно '0' AND TRUE – недопустимо 16

Ограничение длинны типа type базовый_тип is диапазон; range граница_1 направление граница_2 Направление: dоwntо и tо. signal y: bit_vector (0 to 3); signal z: bit_vector (7 downto 0); 17

Тип BIT_VECTOR Это массив битов. ENTITY part 2 IS PORT ( x, y: IN BIT_VECTOR (3 DOWNTO 0); sel: IN BIT; m : OUT BIT_VECTOR (3 DOWNTO 0)); END part 2; 18

Примеры присваиваний Типы bit и bit_vector. x <= ‘ 1’; y <= “ 0111”; z <= “ 0001”; MSB, LSB 19

Операции для типа bit и integer Самостоятельно. 20

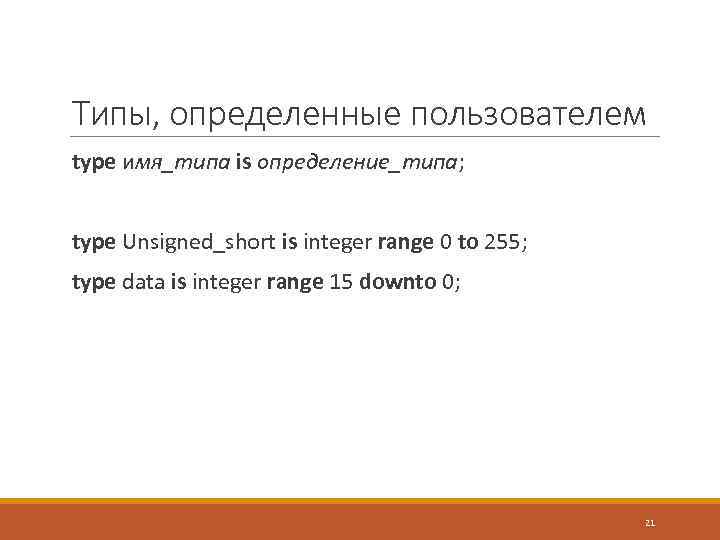

Типы, определенные пользователем type имя_типа is определение_типа; type Unsigned_short is integer range 0 to 255; type data is integer range 15 downto 0; 21

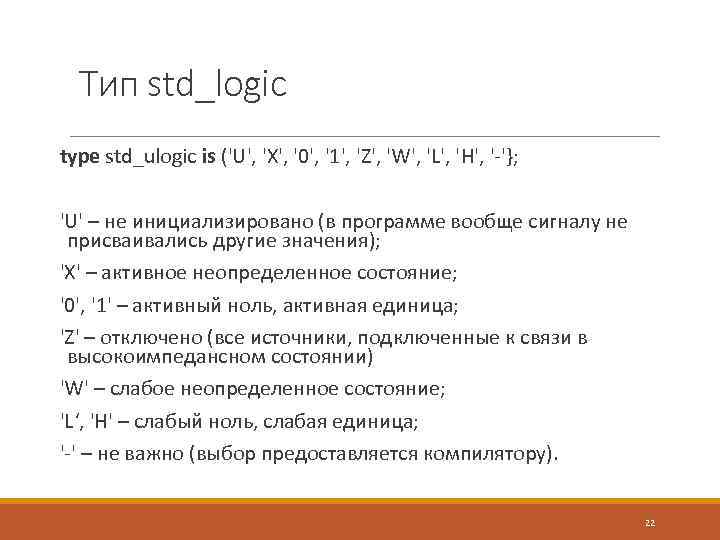

Тип std_logic type std_ulogic is ('U', 'X', '0', '1', 'Z', 'W', 'L', 'Н', '-'}; 'U' – не инициализировано (в программе вообще сигналу не присваивались другие значения); 'X' – активное неопределенное состояние; '0', '1' – активный ноль, активная единица; 'Z' – отключено (все источники, подключенные к связи в высокоимпедансном состоянии) 'W' – слабое неопределенное состояние; 'L‘, 'H' – слабый ноль, слабая единица; '-' – не важно (выбор предоставляется компилятору). 22

Использование std_logic library IEEE; use IEEE. std_logic_1164. all; Расположение библиотеки: C: altera91quartuslibrariesvhdlieeestd_1164. vhd 23

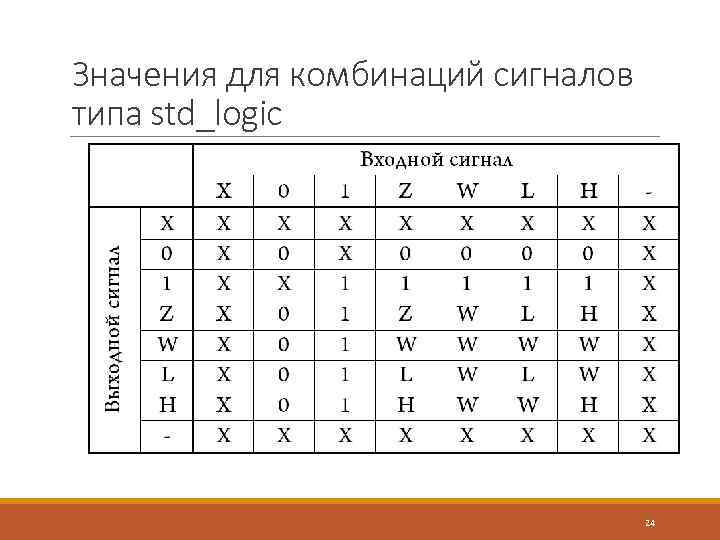

Значения для комбинаций сигналов типа std_logic 24

BIT против STD_LOGIC Оба типа – стандартные, поддерживаются всеми системами проектирования. std_logic поддерживает Z-состояние, которое может синтезироваться. std_logic поддерживает «слабые» и «сильные» сигналы, что необходимо при моделировании. 25

Другие типы, определенные пользователем Типы, полученные из STD_LOGIC ◦ UNSIGNED – тип для представления беззнаковых чисел. ◦ SIGNED – тип для представления знаковых чисел. Определяются как массивы типа STD_LOGIC Описаны в библиотеке numeric_std 26

INTEGER vs SIGNED INTEGER – число, SIGNED – вектор. Оба типа обрабатываются как знаковые числа. Оба типа синтезируются в схему. 27

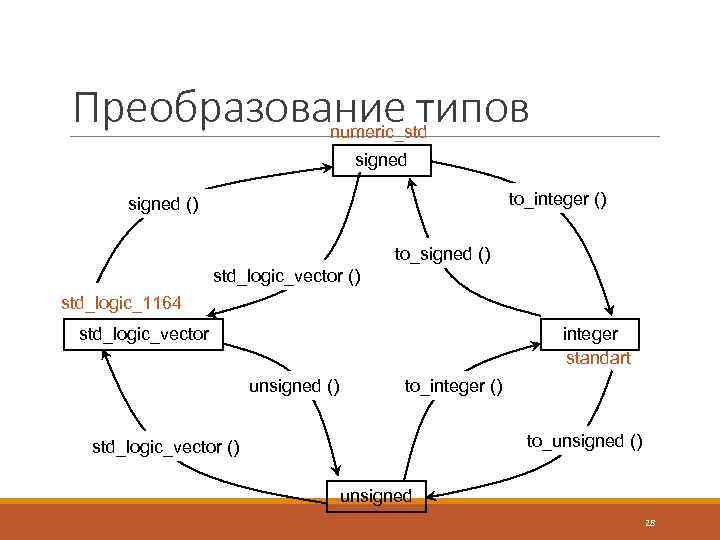

Преобразование типов numeric_std signed to_integer () signed () to_signed () std_logic_vector () std_logic_1164 std_logic_vector integer standart unsigned () to_integer () to_unsigned () std_logic_vector () unsigned numeric_std 28

Преобразование типов TO_INTEGER - преобразование UNSIGNED или SIGNED в INTEGER. TO_UNSIGNED – преобразование неотрицательного INTEGER в вектор типа UNSIGNED заданного размера. TO_SIGNED – преобразование неотрицательного INTEGER в вектор типа SIGNED заданного размера. 29

30

![Десятичные литералы <целое>[. <целое>] [<экспонента>] Целое: 21, 0, 1 Е 2, 3 е 4, Десятичные литералы <целое>[. <целое>] [<экспонента>] Целое: 21, 0, 1 Е 2, 3 е 4,](https://present5.com/presentation/-111587969_437408869/image-31.jpg)

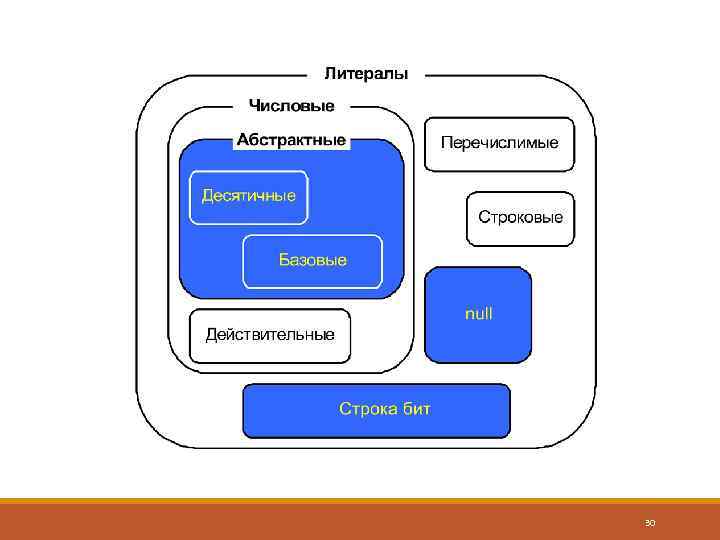

Десятичные литералы <целое>[. <целое>] [<экспонента>] Целое: 21, 0, 1 Е 2, 3 е 4, 452_150 Вещественное: 11. 0, 0. 476, 3. 14_15_926 Вещественное с экспонентой: 1. 34 Е-12, 1. 0 Е+6, 3. 042 е+15 31

![Базовые литералы (13. 4. 2) <базис>#[<число в базисе>] #[<экспонента>] Базис (система счисления) – целое Базовые литералы (13. 4. 2) <базис>#[<число в базисе>] #[<экспонента>] Базис (система счисления) – целое](https://present5.com/presentation/-111587969_437408869/image-32.jpg)

Базовые литералы (13. 4. 2) <базис>#[<число в базисе>] #[<экспонента>] Базис (система счисления) – целое число. Двоичная 2#1111_1100# Шестнадцатиричная 16#fc# Шестнадцатиричная 016#0 FC# Десятичная 10#252# Семиричная 7#510# Эти литералы имеют значение 252 32

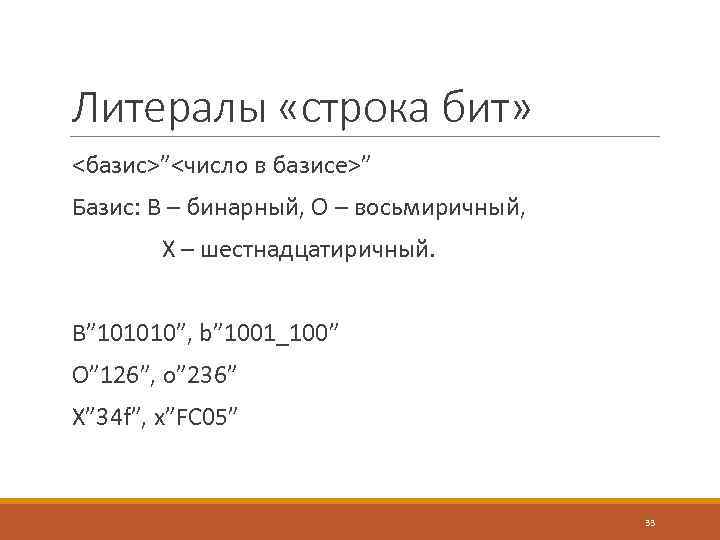

Литералы «строка бит» <базис>”<число в базисе>” Базис: В – бинарный, О – восьмиричный, Х – шестнадцатиричный. B” 101010”, b” 1001_100” O” 126”, o” 236” X” 34 f”, x”FC 05” 33

Разница между строкой бит и базовым литералом Базовый литерал – число, записанное в определенном базисе. Строка бит – совокупность отдельных битов, не связанных в единое целое. B” 01001000” ≠ 2#0100_1000# 34

Константа constant список_констант: тип : =выражение; constant PI: real: = 3. 14159; constant WIDTH: integer: = 32; constant DEFAULT: bit_vector (0 to 3): = "0101"; 35

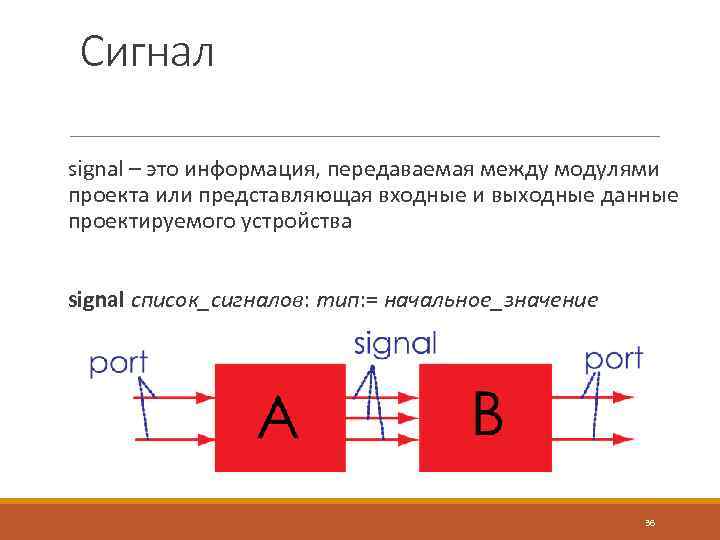

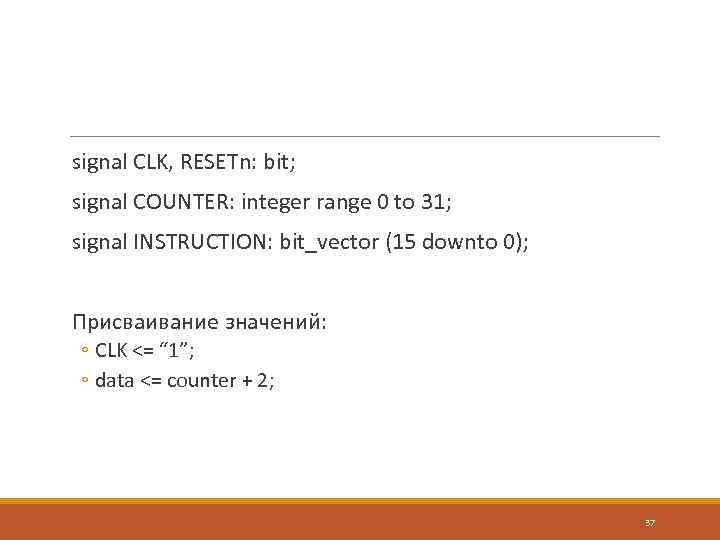

Сигнал signal – это информация, передаваемая между модулями проекта или представляющая входные и выходные данные проектируемого устройства signal список_сигналов: тип: = начальное_значение 36

signal CLK, RESETn: bit; signal COUNTER: integer range 0 to 31; signal INSTRUCTION: bit_vector (15 downto 0); Присваивание значений: ◦ CLK <= “ 1”; ◦ data <= counter + 2; 37

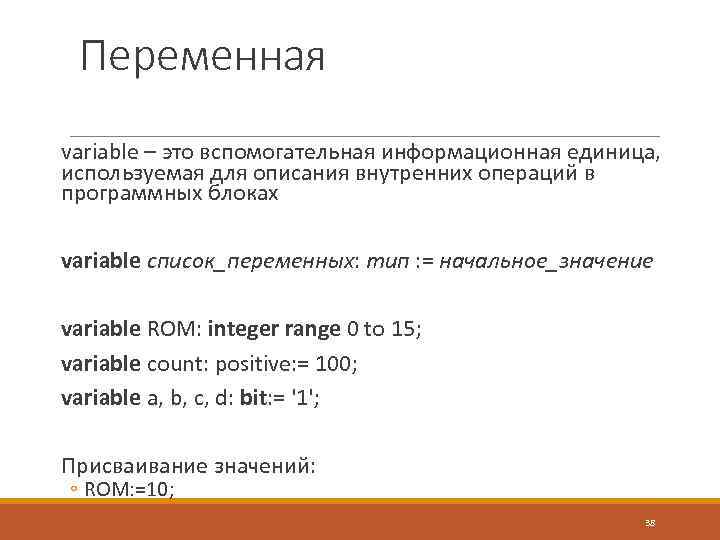

Переменная variable – это вспомогательная информационная единица, используемая для описания внутренних операций в программных блоках variable список_переменных: тип : = начальное_значение variable ROM: integer range 0 to 15; variable count: positive: = 100; variable a, b, c, d: bit: = '1'; Присваивание значений: ◦ ROM: =10; 38

Атрибуты сигналов Атрибуты записываются в следующем формате: <имя объекта> ' <имя атрибута> 39

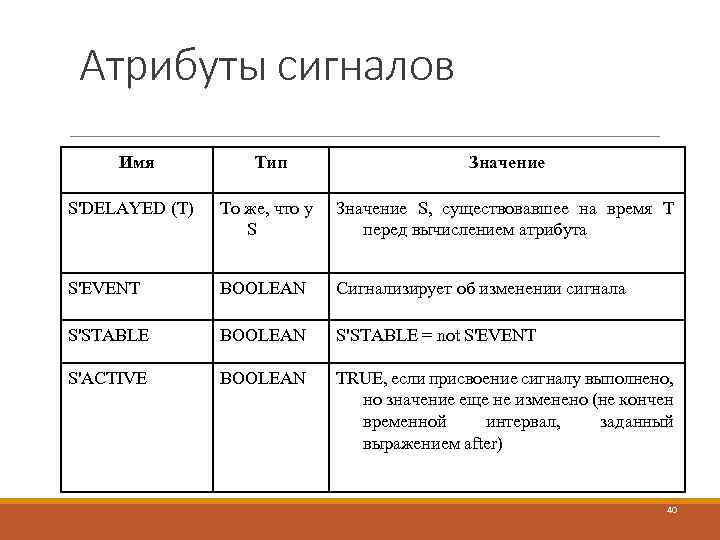

Атрибуты сигналов Имя Тип Значение S'DELAYED (T) То же, что у S Значение S, существовавшее на время T перед вычислением атрибута S'EVENT BOOLEAN Сигнализирует об изменении сигнала S'STABLE BOOLEAN S'STABLE = not S'EVENT S'ACTIVE BOOLEAN TRUE, если присвоение сигналу выполнено, но значение еще не изменено (не кончен временной интервал, заданный выражением after) 40

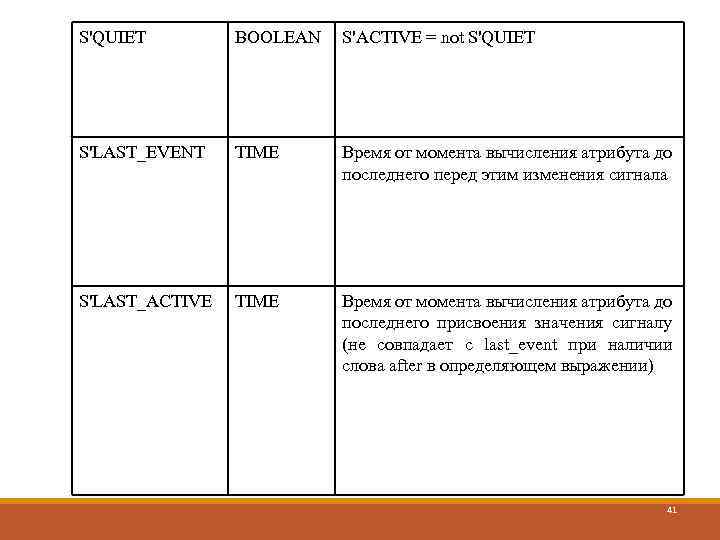

S'QUIET BOOLEAN S'ACTIVE = not S'QUIET S'LAST_EVENT TIME Время от момента вычисления атрибута до последнего перед этим изменения сигнала S'LAST_ACTIVE TIME Время от момента вычисления атрибута до последнего присвоения значения сигналу (не совпадает с last_event при наличии слова after в определяющем выражении) 41

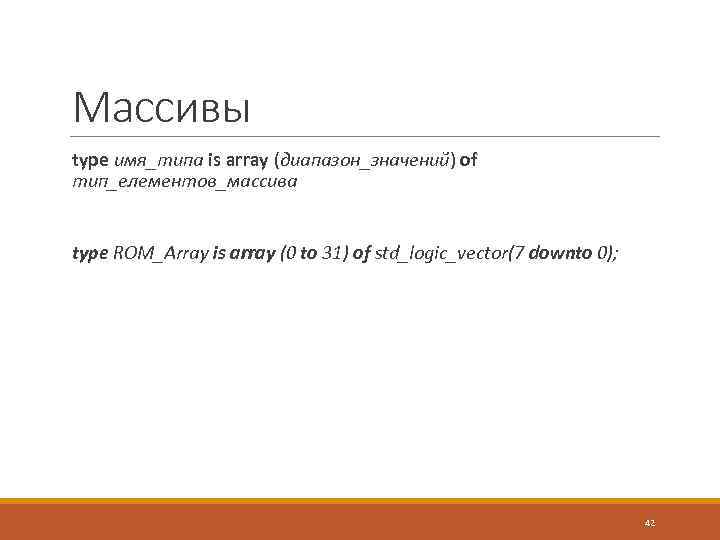

Массивы type имя_типа is array (диапазон_значений) of тип_елементов_массива type ROM_Array is array (0 to 31) of std_logic_vector(7 downto 0); 42

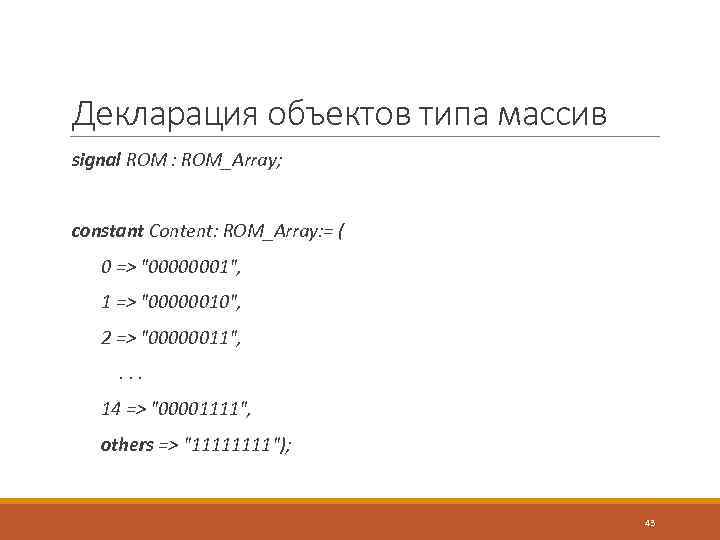

Декларация объектов типа массив signal ROM : ROM_Array; constant Content: ROM_Array: = ( 0 => "00000001", 1 => "00000010", 2 => "00000011", . . . 14 => "00001111", others => "1111"); 43

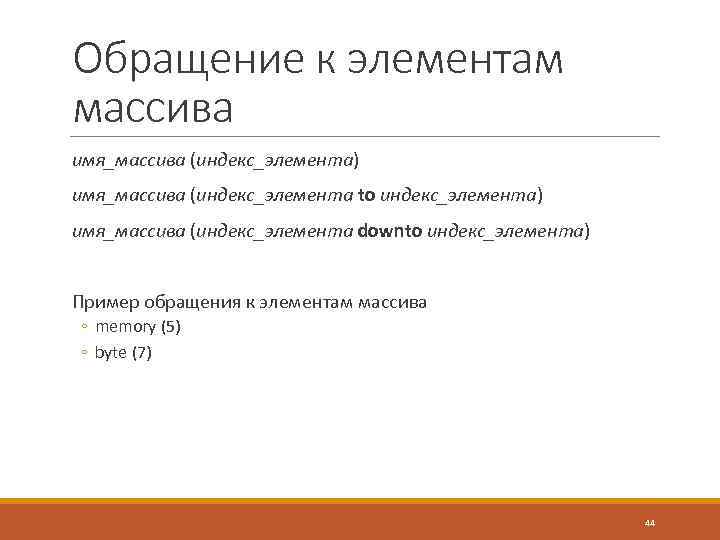

Обращение к элементам массива имя_массива (индекс_элемента) имя_массива (индекс_элемента to индекс_элемента) имя_массива (индекс_элемента downto индекс_элемента) Пример обращения к элементам массива ◦ memory (5) ◦ byte (7) 44

Обращение к элементам массива Обращение к нескольким элементам: ◦ memory (5 to 7) ◦ byte (7 downto 5) Обращение к элементу многомерного массива: ◦ ram_instance (2, 3) : = 5; 45

Конкатенация элементов массива а: = "1001"; b<= "1101" & а; Тут а и b – строки или битовые вектора а – переменная, b – сигнал. 46

Операции сдвига имя_массива символ_операции_сдвига целое Логические сдвиги влево и вправо sll, srl, Арифметические операции сдвига влево и вправо sla, sra, Циклические сдвиги влево и вправо rol, rоr. 47

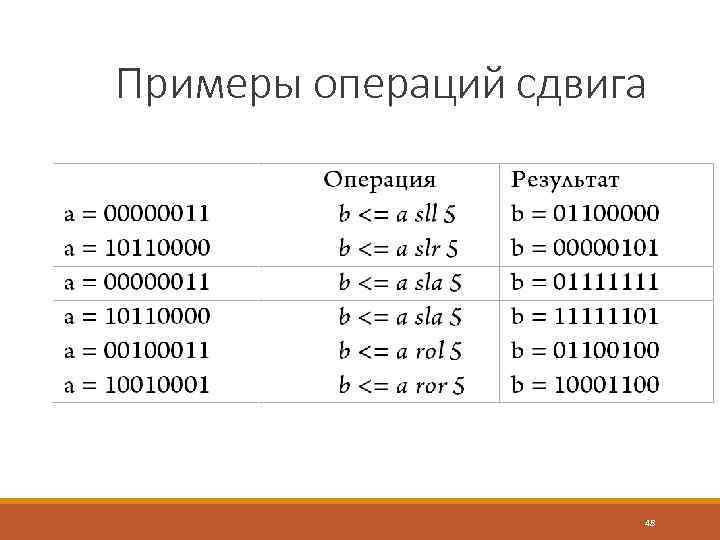

Примеры операций сдвига 48

Внеклассное чтение И. Каршенбойм Краткий курс HDL-кодирования. Часть 3. О написании кода «вообще» . /Компоненты и технологии, № 7. - 2008 г. ◦ http: //iosifk. narod. ru/hdl_coding_5_kit_7_08. pdf http: //lifehacker. ru 49

Цифровая схемотехника 2013 Лекция 02 VHDL.ppt