Лекция 19 ЦИФРОВЫЕ УСТРОЙСТВА Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 1

Лекция 19 ЦИФРОВЫЕ УСТРОЙСТВА Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 1

Содержание лекции • Цифровые сигналы • Устройство цифровых микросхем • Типы логических устройств – – – – Простые логические элементы Составные логические элементы Триггеры Счетчики Регистры Мультиплексоры Сумматоры • ПЛИС Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 2

Содержание лекции • Цифровые сигналы • Устройство цифровых микросхем • Типы логических устройств – – – – Простые логические элементы Составные логические элементы Триггеры Счетчики Регистры Мультиплексоры Сумматоры • ПЛИС Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 2

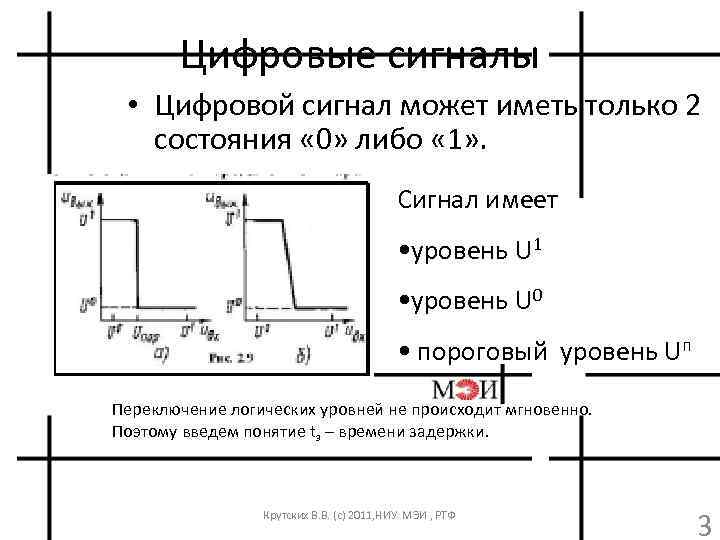

Цифровые сигналы • Цифровой сигнал может иметь только 2 состояния « 0» либо « 1» . Сигнал имеет • уровень U 1 • уровень U 0 • пороговый уровень Uп Переключение логических уровней не происходит мгновенно. Поэтому введем понятие tз – времени задержки. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 3

Цифровые сигналы • Цифровой сигнал может иметь только 2 состояния « 0» либо « 1» . Сигнал имеет • уровень U 1 • уровень U 0 • пороговый уровень Uп Переключение логических уровней не происходит мгновенно. Поэтому введем понятие tз – времени задержки. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 3

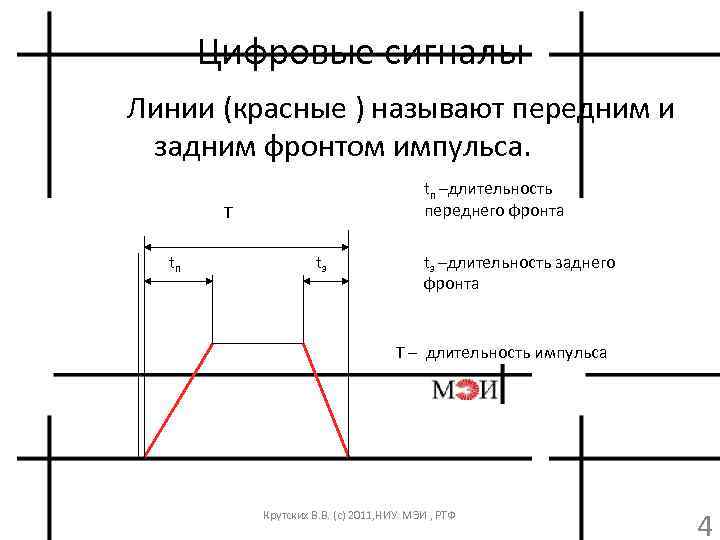

Цифровые сигналы Линии (красные ) называют передним и задним фронтом импульса. tп –длительность переднего фронта T tп tз tз –длительность заднего фронта T – длительность импульса Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 4

Цифровые сигналы Линии (красные ) называют передним и задним фронтом импульса. tп –длительность переднего фронта T tп tз tз –длительность заднего фронта T – длительность импульса Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 4

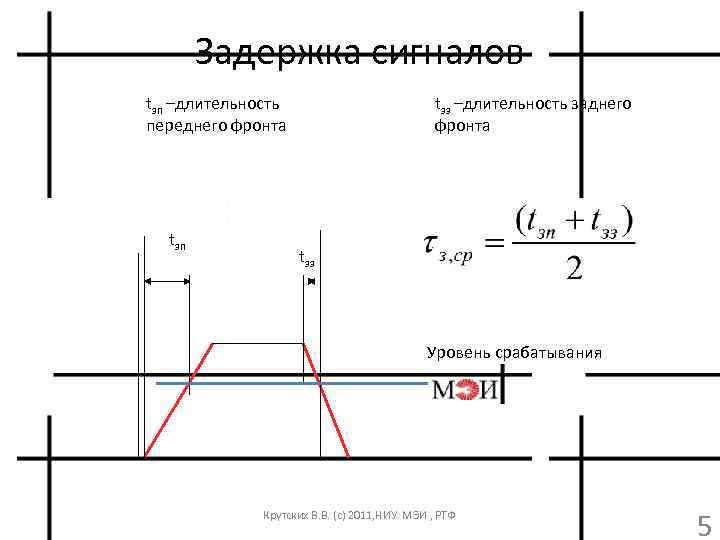

Задержка сигналов tзп –длительность переднего фронта tзп tзз –длительность заднего фронта tзз Уровень срабатывания Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 5

Задержка сигналов tзп –длительность переднего фронта tзп tзз –длительность заднего фронта tзз Уровень срабатывания Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 5

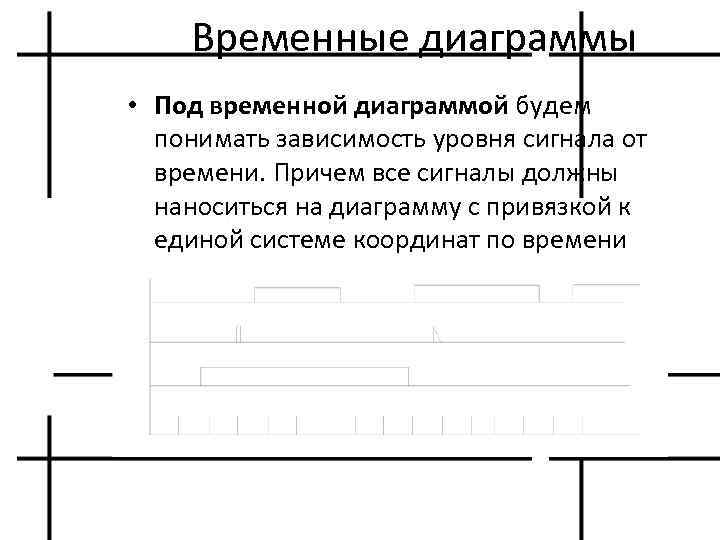

Временные диаграммы • Под временной диаграммой будем понимать зависимость уровня сигнала от времени. Причем все сигналы должны наноситься на диаграмму с привязкой к единой системе координат по времени

Временные диаграммы • Под временной диаграммой будем понимать зависимость уровня сигнала от времени. Причем все сигналы должны наноситься на диаграмму с привязкой к единой системе координат по времени

4 Устройство цифровых микросхем Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 7

4 Устройство цифровых микросхем Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 7

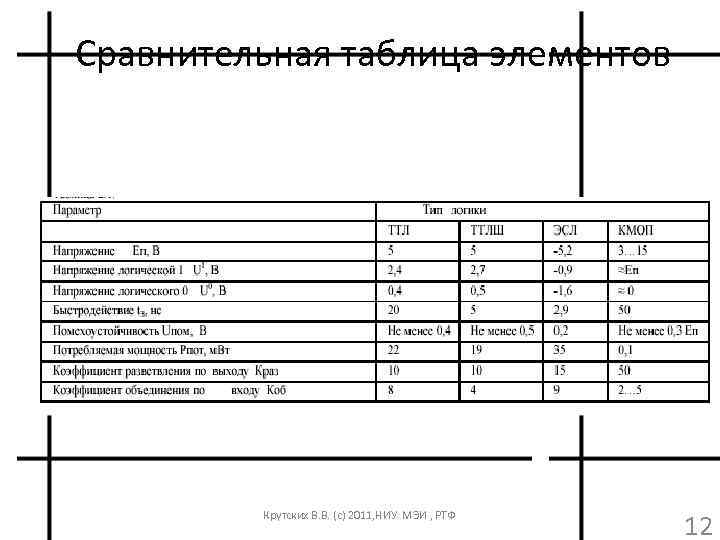

Типы цифровых устройств (ЦУ) • ЦУ классифицируются по типам используемой логики. Существуют: – ТТЛ –транзисторно-теристорная логика – ТТЛШ - транзисторно-теристорная логика с барьером шотки – ЭСЛ – эмиторно-связная логика – КМОП – комплементарные полевые транзисторы со структурой металл-окисел-полупроводник Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 8

Типы цифровых устройств (ЦУ) • ЦУ классифицируются по типам используемой логики. Существуют: – ТТЛ –транзисторно-теристорная логика – ТТЛШ - транзисторно-теристорная логика с барьером шотки – ЭСЛ – эмиторно-связная логика – КМОП – комплементарные полевые транзисторы со структурой металл-окисел-полупроводник Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 8

ТТЛ (Ш) • Интегральные микросхемы семейства ТТЛ обладают сравнительно высоким быстродействием при относительно большой потребляемой мощности, высокой помехоустойчивостью и большой нагрузочной способностью. • Промышленность выпускает несколько разновидностей ТТЛ ИМС, в том числе ИМС с диодами Шоттки (ТТЛШ) повышенного быстродействия (но большей мощности потребления) и маломощные (но с меньшим быстродействием). Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 9

ТТЛ (Ш) • Интегральные микросхемы семейства ТТЛ обладают сравнительно высоким быстродействием при относительно большой потребляемой мощности, высокой помехоустойчивостью и большой нагрузочной способностью. • Промышленность выпускает несколько разновидностей ТТЛ ИМС, в том числе ИМС с диодами Шоттки (ТТЛШ) повышенного быстродействия (но большей мощности потребления) и маломощные (но с меньшим быстродействием). Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 9

ЭСЛ Микросхемы ЭСЛ-типа являются наиболее быстродействующими. Транзисторы элемента работают в активном режиме, чем исключается время выхода из насыщения; перезарядка нагружающих вывод емкостей происходит достаточно быстро через малое выходное сопротивление эмиттерных повторителей. Наряду с высоким быстродействием и большой нагрузочной способностью ЭСЛ-элемент отличается меньшей, чем ТТЛ-элемент, помехоустойчивостью (ввиду того, что для его переключения достаточен небольшой перепад входного напряжения), а также относительно большим потреблением энергии Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 10

ЭСЛ Микросхемы ЭСЛ-типа являются наиболее быстродействующими. Транзисторы элемента работают в активном режиме, чем исключается время выхода из насыщения; перезарядка нагружающих вывод емкостей происходит достаточно быстро через малое выходное сопротивление эмиттерных повторителей. Наряду с высоким быстродействием и большой нагрузочной способностью ЭСЛ-элемент отличается меньшей, чем ТТЛ-элемент, помехоустойчивостью (ввиду того, что для его переключения достаточен небольшой перепад входного напряжения), а также относительно большим потреблением энергии Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 10

КМОП Микросхемы КМОП-типа отличаются исключительно малым потреблением энергии, за счет чего температура кристалла не превышает допустимой при большом количестве компонентов на нем. Это позволяет изготовлять большие интегральные схемы (БИС) КМОП-типа с наивысшей в настоящее время степенью интеграции. Малая потребляемая мощность позволяет использовать аппаратуру на КМОП ИМС при ограниченных возможностях источников питания. КМОП ИМС отличают высокая помехозащищенность и большое входное сопротивление, следствием чего является высокая нагрузочная способность (большой коэффициент разветвления по выходу). Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 11

КМОП Микросхемы КМОП-типа отличаются исключительно малым потреблением энергии, за счет чего температура кристалла не превышает допустимой при большом количестве компонентов на нем. Это позволяет изготовлять большие интегральные схемы (БИС) КМОП-типа с наивысшей в настоящее время степенью интеграции. Малая потребляемая мощность позволяет использовать аппаратуру на КМОП ИМС при ограниченных возможностях источников питания. КМОП ИМС отличают высокая помехозащищенность и большое входное сопротивление, следствием чего является высокая нагрузочная способность (большой коэффициент разветвления по выходу). Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 11

Сравнительная таблица элементов Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 12

Сравнительная таблица элементов Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 12

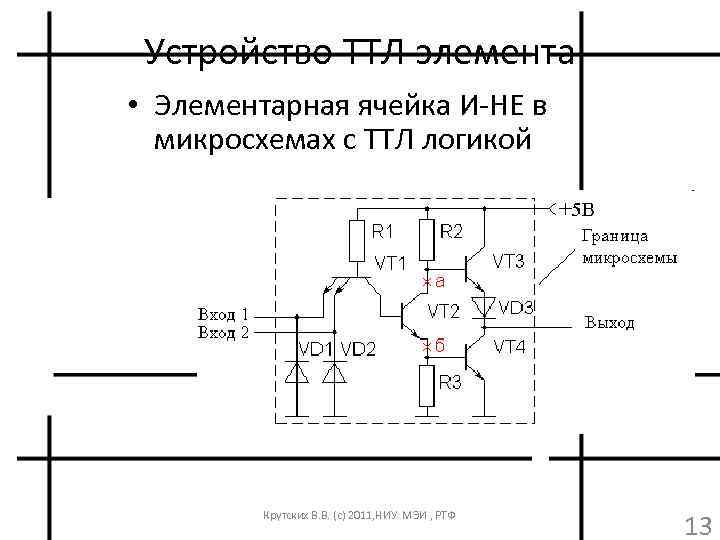

Устройство ТТЛ элемента • Элементарная ячейка И-НЕ в микросхемах с ТТЛ логикой Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 13

Устройство ТТЛ элемента • Элементарная ячейка И-НЕ в микросхемах с ТТЛ логикой Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 13

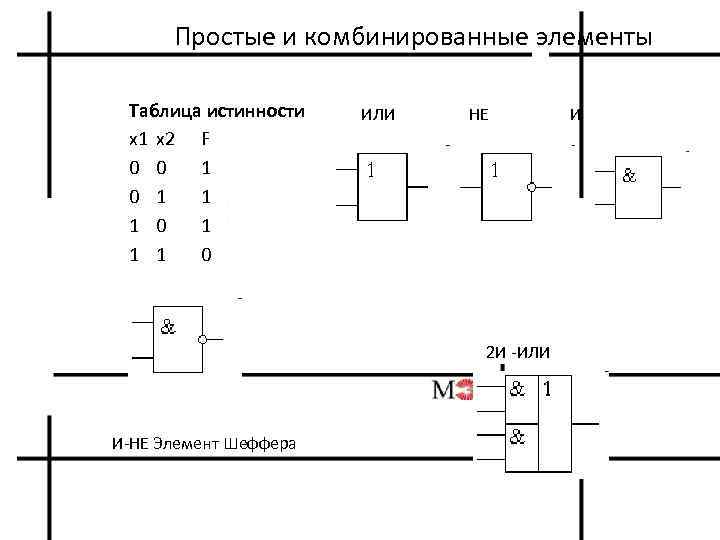

Простые и комбинированные элементы Таблица истинности x 1 x 2 F 0 0 1 1 1 0 ИЛИ НЕ И 2 И -ИЛИ И-НЕ Элемент Шеффера

Простые и комбинированные элементы Таблица истинности x 1 x 2 F 0 0 1 1 1 0 ИЛИ НЕ И 2 И -ИЛИ И-НЕ Элемент Шеффера

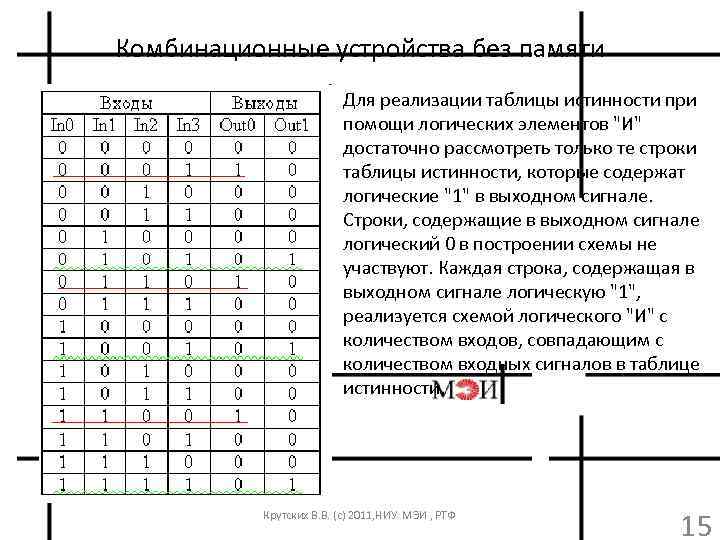

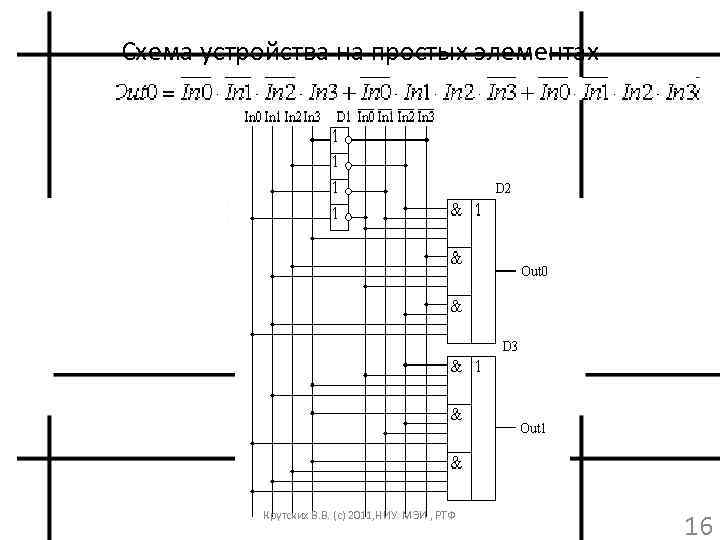

Комбинационные устройства без памяти • Для реализации таблицы истинности при помощи логических элементов "И" достаточно рассмотреть только те строки таблицы истинности, которые содержат логические "1" в выходном сигнале. Строки, содержащие в выходном сигнале логический 0 в построении схемы не участвуют. Каждая строка, содержащая в выходном сигнале логическую "1", реализуется схемой логического "И" с количеством входов, совпадающим с количеством входных сигналов в таблице истинности. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 15

Комбинационные устройства без памяти • Для реализации таблицы истинности при помощи логических элементов "И" достаточно рассмотреть только те строки таблицы истинности, которые содержат логические "1" в выходном сигнале. Строки, содержащие в выходном сигнале логический 0 в построении схемы не участвуют. Каждая строка, содержащая в выходном сигнале логическую "1", реализуется схемой логического "И" с количеством входов, совпадающим с количеством входных сигналов в таблице истинности. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 15

Схема устройства на простых элементах Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 16

Схема устройства на простых элементах Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 16

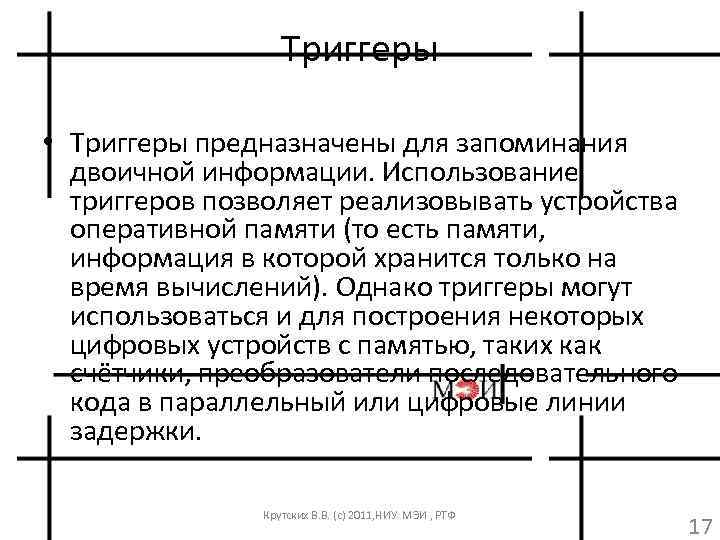

Триггеры • Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений). Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 17

Триггеры • Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений). Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 17

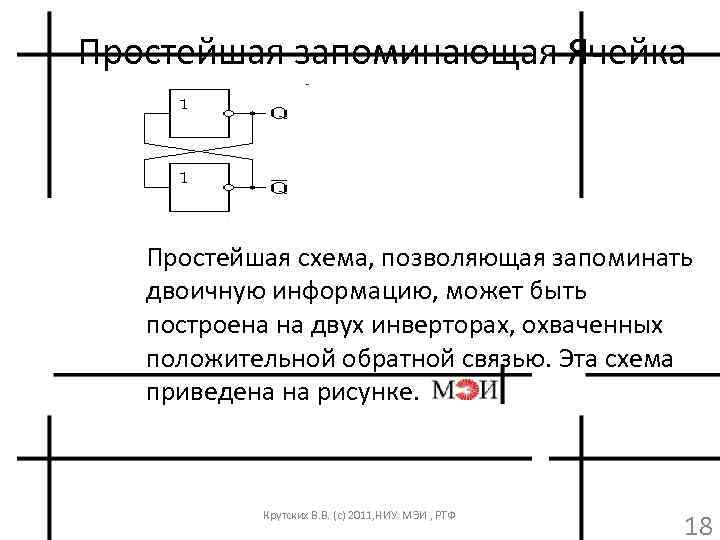

Простейшая запоминающая Ячейка Простейшая схема, позволяющая запоминать двоичную информацию, может быть построена на двух инверторах, охваченных положительной обратной связью. Эта схема приведена на рисунке. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 18

Простейшая запоминающая Ячейка Простейшая схема, позволяющая запоминать двоичную информацию, может быть построена на двух инверторах, охваченных положительной обратной связью. Эта схема приведена на рисунке. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 18

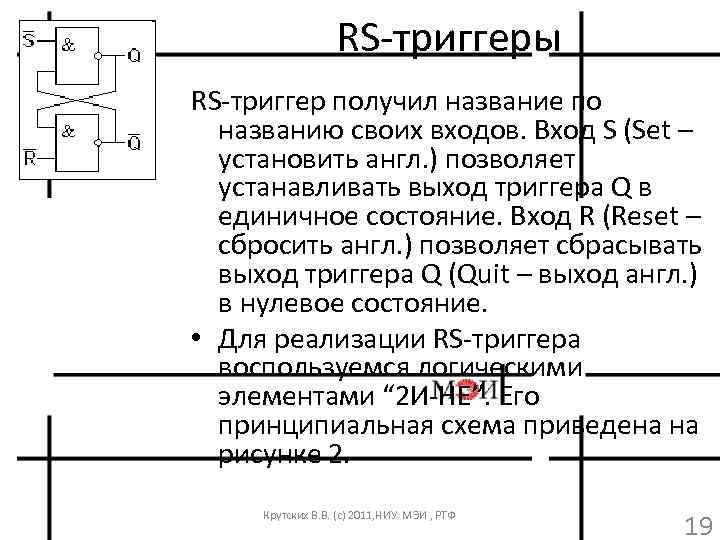

RS-триггеры RS-триггер получил название по названию своих входов. Вход S (Set – установить англ. ) позволяет устанавливать выход триггера Q в единичное состояние. Вход R (Reset – сбросить англ. ) позволяет сбрасывать выход триггера Q (Quit – выход англ. ) в нулевое состояние. • Для реализации RS-триггера воспользуемся логическими элементами “ 2 И-НЕ”. Его принципиальная схема приведена на рисунке 2. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 19

RS-триггеры RS-триггер получил название по названию своих входов. Вход S (Set – установить англ. ) позволяет устанавливать выход триггера Q в единичное состояние. Вход R (Reset – сбросить англ. ) позволяет сбрасывать выход триггера Q (Quit – выход англ. ) в нулевое состояние. • Для реализации RS-триггера воспользуемся логическими элементами “ 2 И-НЕ”. Его принципиальная схема приведена на рисунке 2. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 19

Таблица истинности RS-триггера Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 20

Таблица истинности RS-триггера Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 20

Синхронные RS-триггеры • Схема RS-триггера позволяет запоминать состояние логической схемы, но так как в начальный момент времени может возникать переходный процесс (в цифровых схемах этот процесс называется опасные гонки), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены. • Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала). Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Для того чтобы отличать от них рассмотренные ранее варианты (RSтриггер и триггер Шмитта) эти триггеры получили название асинхронных. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 21

Синхронные RS-триггеры • Схема RS-триггера позволяет запоминать состояние логической схемы, но так как в начальный момент времени может возникать переходный процесс (в цифровых схемах этот процесс называется опасные гонки), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены. • Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала). Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Для того чтобы отличать от них рассмотренные ранее варианты (RSтриггер и триггер Шмитта) эти триггеры получили название асинхронных. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 21

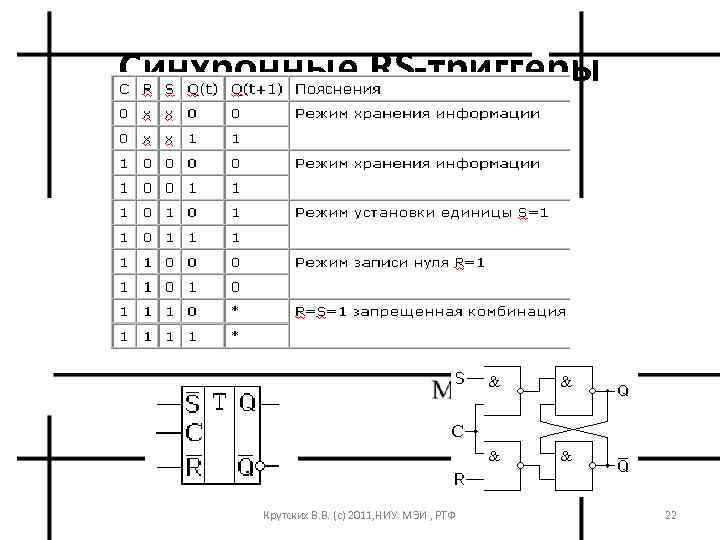

Синхронные RS-триггеры Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 22

Синхронные RS-триггеры Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 22

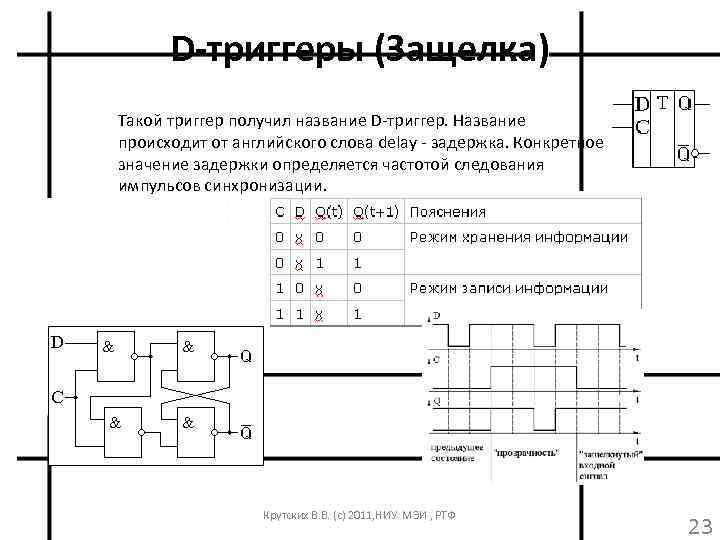

D-триггеры (Защелка) Такой триггер получил название D-триггер. Название происходит от английского слова delay - задержка. Конкретное значение задержки определяется частотой следования импульсов синхронизации. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 23

D-триггеры (Защелка) Такой триггер получил название D-триггер. Название происходит от английского слова delay - задержка. Конкретное значение задержки определяется частотой следования импульсов синхронизации. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 23

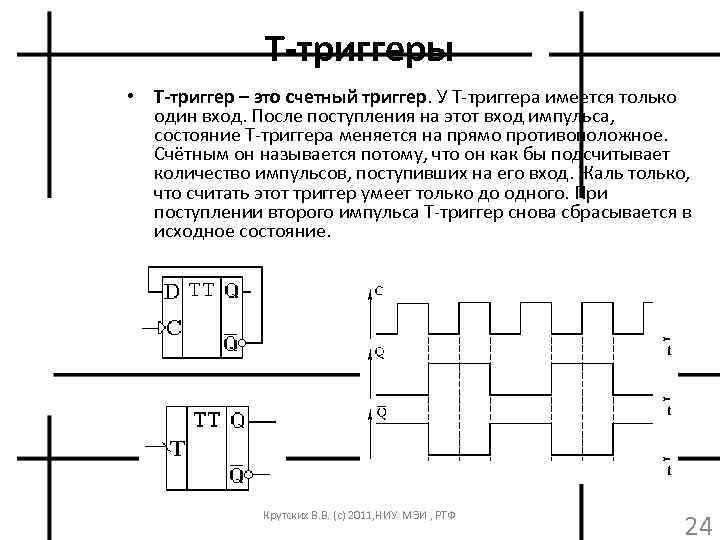

T-триггеры • Т-триггер – это счетный триггер. У Т-триггера имеется только один вход. После поступления на этот вход импульса, состояние Т-триггера меняется на прямо противоположное. Счётным он называется потому, что он как бы подсчитывает количество импульсов, поступивших на его вход. Жаль только, что считать этот триггер умеет только до одного. При поступлении второго импульса T-триггер снова сбрасывается в исходное состояние. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 24

T-триггеры • Т-триггер – это счетный триггер. У Т-триггера имеется только один вход. После поступления на этот вход импульса, состояние Т-триггера меняется на прямо противоположное. Счётным он называется потому, что он как бы подсчитывает количество импульсов, поступивших на его вход. Жаль только, что считать этот триггер умеет только до одного. При поступлении второго импульса T-триггер снова сбрасывается в исходное состояние. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 24

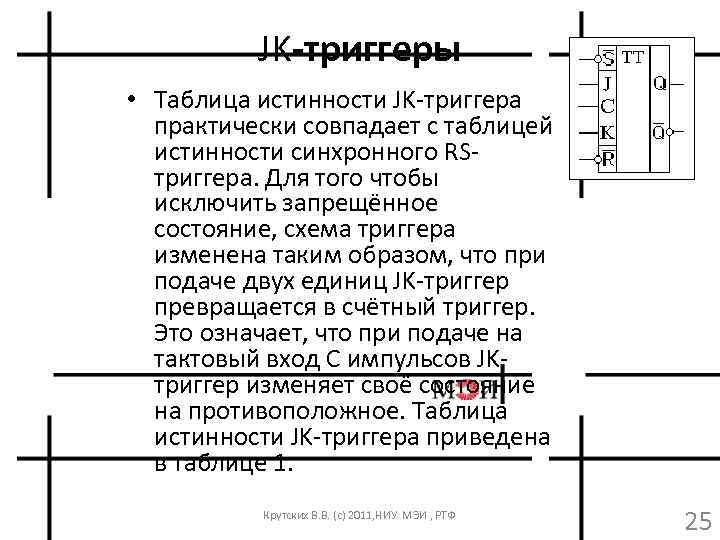

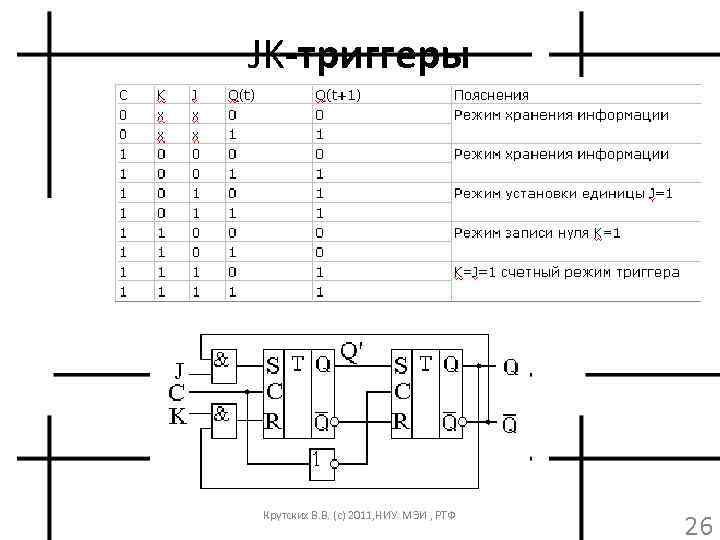

JK-триггеры • Таблица истинности JK-триггера практически совпадает с таблицей истинности синхронного RSтриггера. Для того чтобы исключить запрещённое состояние, схема триггера изменена таким образом, что при подаче двух единиц JK-триггер превращается в счётный триггер. Это означает, что при подаче на тактовый вход C импульсов JKтриггер изменяет своё состояние на противоположное. Таблица истинности JK-триггера приведена в таблице 1. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 25

JK-триггеры • Таблица истинности JK-триггера практически совпадает с таблицей истинности синхронного RSтриггера. Для того чтобы исключить запрещённое состояние, схема триггера изменена таким образом, что при подаче двух единиц JK-триггер превращается в счётный триггер. Это означает, что при подаче на тактовый вход C импульсов JKтриггер изменяет своё состояние на противоположное. Таблица истинности JK-триггера приведена в таблице 1. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 25

JK-триггеры Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 26

JK-триггеры Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 26

Регистры • Регистром называется последовательное или параллельное соединение триггеров. Регистры обычно строятся на основе D триггеров. При этом для построения регистров могут использоваться как динамические D триггеры, так и статические триггеры. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 27

Регистры • Регистром называется последовательное или параллельное соединение триггеров. Регистры обычно строятся на основе D триггеров. При этом для построения регистров могут использоваться как динамические D триггеры, так и статические триггеры. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 27

Параллельные регистры Параллельный регистр служит для запоминания многоразрядного двоичного (или недвоичного) слова. Количество триггеров, входящее в состав параллельного регистра определяет его разрядность. Схема четырёхразрядного параллельного регистра приведена на рисунке 1, а его условно-графическое обозначение - на рисунке 2. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 28

Параллельные регистры Параллельный регистр служит для запоминания многоразрядного двоичного (или недвоичного) слова. Количество триггеров, входящее в состав параллельного регистра определяет его разрядность. Схема четырёхразрядного параллельного регистра приведена на рисунке 1, а его условно-графическое обозначение - на рисунке 2. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 28

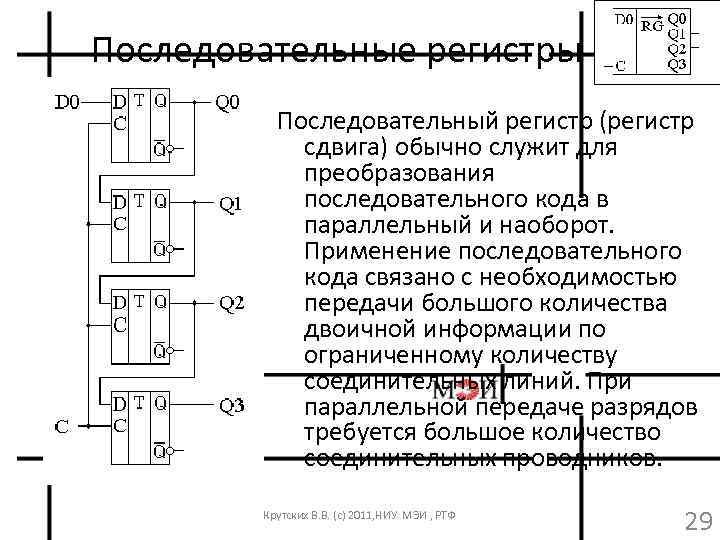

Последовательные регистры Последовательный регистр (регистр сдвига) обычно служит для преобразования последовательного кода в параллельный и наоборот. Применение последовательного кода связано с необходимостью передачи большого количества двоичной информации по ограниченному количеству соединительных линий. При параллельной передаче разрядов требуется большое количество соединительных проводников. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 29

Последовательные регистры Последовательный регистр (регистр сдвига) обычно служит для преобразования последовательного кода в параллельный и наоборот. Применение последовательного кода связано с необходимостью передачи большого количества двоичной информации по ограниченному количеству соединительных линий. При параллельной передаче разрядов требуется большое количество соединительных проводников. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 29

Счётчики • Счётчики используются для построения таймеров или для выборки инструкций из ПЗУ в микропроцессорах. Они могут использоваться как делители частоты в управляемых генераторах частоты (синтезаторах). При использовании в цепи ФАП счётчики могут быть использованы для умножения частоты как в синтезаторах, так и в микропроцессорах. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 30

Счётчики • Счётчики используются для построения таймеров или для выборки инструкций из ПЗУ в микропроцессорах. Они могут использоваться как делители частоты в управляемых генераторах частоты (синтезаторах). При использовании в цепи ФАП счётчики могут быть использованы для умножения частоты как в синтезаторах, так и в микропроцессорах. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 30

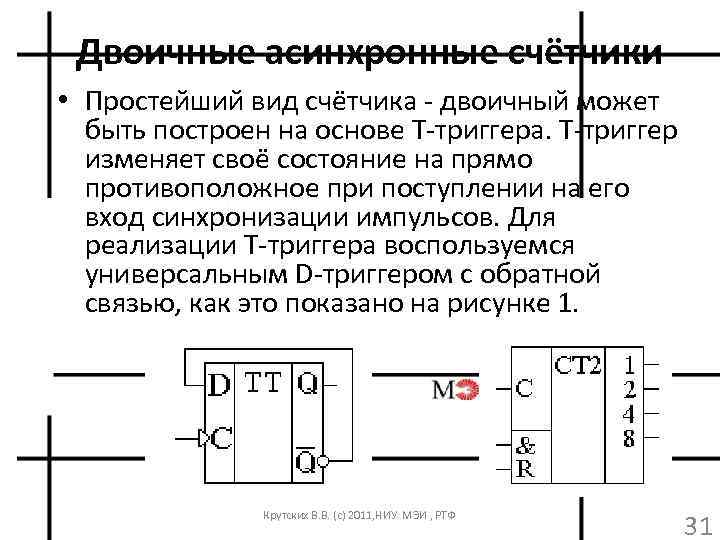

Двоичные асинхронные счётчики • Простейший вид счётчика - двоичный может быть построен на основе T-триггера. T-триггер изменяет своё состояние на прямо противоположное при поступлении на его вход синхронизации импульсов. Для реализации T-триггера воспользуемся универсальным D-триггером с обратной связью, как это показано на рисунке 1. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 31

Двоичные асинхронные счётчики • Простейший вид счётчика - двоичный может быть построен на основе T-триггера. T-триггер изменяет своё состояние на прямо противоположное при поступлении на его вход синхронизации импульсов. Для реализации T-триггера воспользуемся универсальным D-триггером с обратной связью, как это показано на рисунке 1. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 31

Двоичные асинхронные счётчики В этом случае можно использовать выходной сигнал первого счетного триггера как входной сигнал для следующего триггера, то есть соединить триггеры последовательно. Так можно построить любой счётчик, считающий до максимального числа, кратного степени два. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 32

Двоичные асинхронные счётчики В этом случае можно использовать выходной сигнал первого счетного триггера как входной сигнал для следующего триггера, то есть соединить триггеры последовательно. Так можно построить любой счётчик, считающий до максимального числа, кратного степени два. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 32

Синхронные счётчики • В рассмотренных схемах делителей частоты быстродействие всей схемы определяется временем распространения сигнала от входа до выхода самого старшего разряда. При этом получается, что чем больше требуемый коэффициент деления, тем больше двоичных разрядов счётчика требуется для реализации этого делителя. Тем большее время требуется для распространения сигнала от входа синхронизации счётчика, до его выхода, и тем меньше будет предельная частота, которую можно подавать на вход этого делителя. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 33

Синхронные счётчики • В рассмотренных схемах делителей частоты быстродействие всей схемы определяется временем распространения сигнала от входа до выхода самого старшего разряда. При этом получается, что чем больше требуемый коэффициент деления, тем больше двоичных разрядов счётчика требуется для реализации этого делителя. Тем большее время требуется для распространения сигнала от входа синхронизации счётчика, до его выхода, и тем меньше будет предельная частота, которую можно подавать на вход этого делителя. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 33

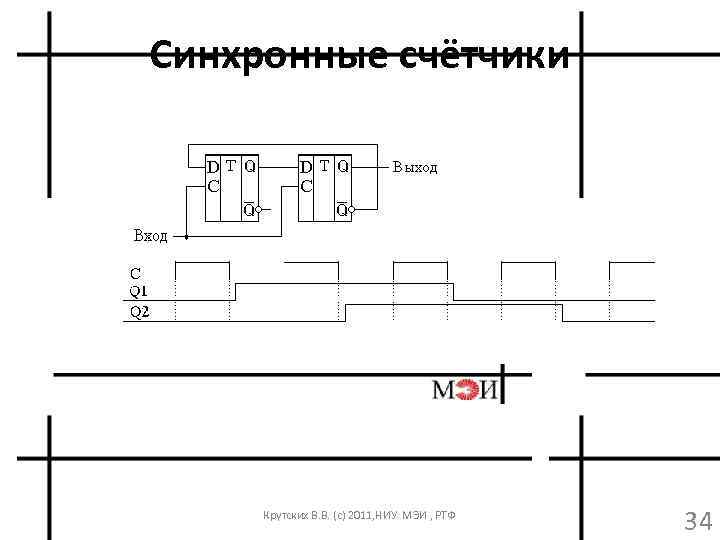

Синхронные счётчики Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 34

Синхронные счётчики Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 34

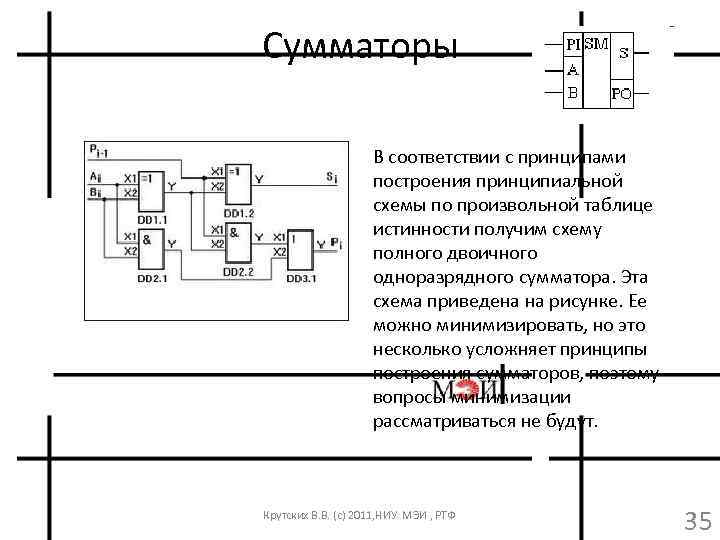

Сумматоры В соответствии с принципами построения принципиальной схемы по произвольной таблице истинности получим схему полного двоичного одноразрядного сумматора. Эта схема приведена на рисунке. Ее можно минимизировать, но это несколько усложняет принципы построения сумматоров, поэтому вопросы минимизации рассматриваться не будут. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 35

Сумматоры В соответствии с принципами построения принципиальной схемы по произвольной таблице истинности получим схему полного двоичного одноразрядного сумматора. Эта схема приведена на рисунке. Ее можно минимизировать, но это несколько усложняет принципы построения сумматоров, поэтому вопросы минимизации рассматриваться не будут. Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 35

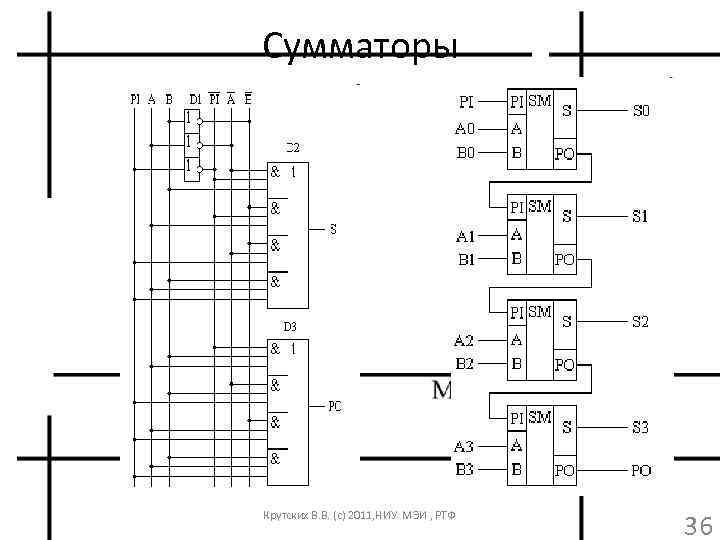

Сумматоры Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 36

Сумматоры Крутских В. В. (с) 2011, НИУ МЭИ , РТФ 36