L_121_PLIS.ppt

- Количество слайдов: 30

ЛЕКЦІЯ № 12 з навчальної дисципліни „ОСНОВИ КОМП'ЮТЕРНОГО ПРОЕКТУВАННЯ ТА МОДЕЛЮВАННЯ СИСТЕМ ЗАХИСТУ ІНФОРМАЦІЇ” Модуль 3. АВТОМАТИЗАЦІЯ ПРОЕКТУВАННЯ ПРИСТРОЇВ НА ПЛІС Заняття № 1. Види структурної організації ПЛІС 1

ЛЕКЦІЯ № 12 з навчальної дисципліни „ОСНОВИ КОМП'ЮТЕРНОГО ПРОЕКТУВАННЯ ТА МОДЕЛЮВАННЯ СИСТЕМ ЗАХИСТУ ІНФОРМАЦІЇ” Модуль 3. АВТОМАТИЗАЦІЯ ПРОЕКТУВАННЯ ПРИСТРОЇВ НА ПЛІС Заняття № 1. Види структурної організації ПЛІС 1

n n Навчальна мета: ознайомити студентів із класифікацією мікросхем програмованої логіки та з’ясувати основні принципи їх структурної організації Література: 1. Грушвицкий Р. И. , Мурсаев А. Х. , Угрюмов Е. П. Проектирование систем на микросхемах программируемой логики. – СПб. : Петербург, 2002, стр. 23 -91. 2

n n Навчальна мета: ознайомити студентів із класифікацією мікросхем програмованої логіки та з’ясувати основні принципи їх структурної організації Література: 1. Грушвицкий Р. И. , Мурсаев А. Х. , Угрюмов Е. П. Проектирование систем на микросхемах программируемой логики. – СПб. : Петербург, 2002, стр. 23 -91. 2

n n n Навчальні питання: 1 Класифікація ПЛІС. 2. Структура ПЛІС CPLD. 3. Структура ПЛІС FPGA. 4. Структура ПЛІС FLEX. 3

n n n Навчальні питання: 1 Класифікація ПЛІС. 2. Структура ПЛІС CPLD. 3. Структура ПЛІС FPGA. 4. Структура ПЛІС FLEX. 3

Питання на самостійну роботу n Відпрацювання матеріалу лекції 4

Питання на самостійну роботу n Відпрацювання матеріалу лекції 4

Питання 1. Класифікація програмованих логічних інтегральних мікросхем 1. 1. Класифікація ПЛІС за архітектурою У класифікації за даною ознакою ПЛІС поділяються на чотири класи. ПЛІС SPLD CPLD Класичні FPGA Комбінованої архітектури FPGA 5

Питання 1. Класифікація програмованих логічних інтегральних мікросхем 1. 1. Класифікація ПЛІС за архітектурою У класифікації за даною ознакою ПЛІС поділяються на чотири класи. ПЛІС SPLD CPLD Класичні FPGA Комбінованої архітектури FPGA 5

n n n Перший із класів – SPLD (Simple Programmable Logic Devices), тобто прості програмовані логічні пристрої. По архітектурі ці ПЛІС поділяються на підкласи програмованих логічних матриць ПЛМ (PLA, Programmable Logic Arrays) і програмованої матричної логіки ПМЛ (PAL, Programmable Arrays Logic, або GAL, Generic Array Logic). Обидва зазначені підкласи мікросхем реалізують диз’юнктивні нормальні форми (ДНФ) перемикальних функцій, а їхніми основними блоками є дві матриці: матриця елементів “І” і матриця елементів “АБО”, що включені послідовно. Така структурна модель ПЛМ і ПМЛ. 6

n n n Перший із класів – SPLD (Simple Programmable Logic Devices), тобто прості програмовані логічні пристрої. По архітектурі ці ПЛІС поділяються на підкласи програмованих логічних матриць ПЛМ (PLA, Programmable Logic Arrays) і програмованої матричної логіки ПМЛ (PAL, Programmable Arrays Logic, або GAL, Generic Array Logic). Обидва зазначені підкласи мікросхем реалізують диз’юнктивні нормальні форми (ДНФ) перемикальних функцій, а їхніми основними блоками є дві матриці: матриця елементів “І” і матриця елементів “АБО”, що включені послідовно. Така структурна модель ПЛМ і ПМЛ. 6

n n На входи першої матриці надходять т вхідних змінних у вигляді як прямих, так і інверсних значень, так що матриця має 2 т вхідних ліній. На її виходах формуються кон’юктивні терми, ранг яких не вище т. Надалі для стислості кон’юктивні терми називаються просто термами. Число термів не має прямого зв’язку з величиною т і визначається конструктивними параметрами матриці – числом кон’юкторів, що визначається через q. Перша матриця ідентична для обох підкласів SPLD, тобто для ПЛМ і ПМЛ. Вироблені терми надходять на вхід матриці “АБО”. Ці матриці для ПЛМ і ПМЛ різні. У ПЛМ матриця “АБО” програмується, а в “ПМЛ” вона фіксована. 7

n n На входи першої матриці надходять т вхідних змінних у вигляді як прямих, так і інверсних значень, так що матриця має 2 т вхідних ліній. На її виходах формуються кон’юктивні терми, ранг яких не вище т. Надалі для стислості кон’юктивні терми називаються просто термами. Число термів не має прямого зв’язку з величиною т і визначається конструктивними параметрами матриці – числом кон’юкторів, що визначається через q. Перша матриця ідентична для обох підкласів SPLD, тобто для ПЛМ і ПМЛ. Вироблені терми надходять на вхід матриці “АБО”. Ці матриці для ПЛМ і ПМЛ різні. У ПЛМ матриця “АБО” програмується, а в “ПМЛ” вона фіксована. 7

n n n Програмована матриця “АБО” мікросхем ПЛМ складена з диз’юнкторів, що мають по q входів. На входи кожного диз’юнктора при програмуванні можна подати будь-яку комбінацію наявних термів, причому терми можна використовувати багаторазово (тобто той же самий терм може бути використаний для подачі на входи декількох диз’юнкторів). Кількість диз’юнкторів у матриці “АБО” визначає число виходів ПЛМ, що позначається через п. З викладеного видно, що ПЛМ дозволяє реалізувати систему з n перемикальних функцій, що залежать не більш ніж від т змінних і утримуючих не більш ніж q термів. Тому функціональні можливості ПЛМ характеризуються трьома цифрами: m, q, п. 8

n n n Програмована матриця “АБО” мікросхем ПЛМ складена з диз’юнкторів, що мають по q входів. На входи кожного диз’юнктора при програмуванні можна подати будь-яку комбінацію наявних термів, причому терми можна використовувати багаторазово (тобто той же самий терм може бути використаний для подачі на входи декількох диз’юнкторів). Кількість диз’юнкторів у матриці “АБО” визначає число виходів ПЛМ, що позначається через п. З викладеного видно, що ПЛМ дозволяє реалізувати систему з n перемикальних функцій, що залежать не більш ніж від т змінних і утримуючих не більш ніж q термів. Тому функціональні можливості ПЛМ характеризуються трьома цифрами: m, q, п. 8

n У ПМЛ вироблені матрицею “І” терми надходять на фіксовану (непрограмовану) матрицю елементів “АБО”. Це означає заздалегідь заданий розподіл наявних термів між окремими диз’юнкторами. Кожному диз’юнктору надаються свої власні терми, і якщо для різних диз’юнкторів виявляться потрібними однакові терми, потрібно виробляти їх у матриці “І” кілька разів. Проте при цьому програмованість матриці “АБО” виключається, що для багатьох завдань у підсумку істотно спрощує схему ПМЛ у порівнянні зі схемою ПЛМ. 9

n У ПМЛ вироблені матрицею “І” терми надходять на фіксовану (непрограмовану) матрицю елементів “АБО”. Це означає заздалегідь заданий розподіл наявних термів між окремими диз’юнкторами. Кожному диз’юнктору надаються свої власні терми, і якщо для різних диз’юнкторів виявляться потрібними однакові терми, потрібно виробляти їх у матриці “І” кілька разів. Проте при цьому програмованість матриці “АБО” виключається, що для багатьох завдань у підсумку істотно спрощує схему ПМЛ у порівнянні зі схемою ПЛМ. 9

n n ПЛМ мають більшу функціональну гнучкість, всі відтворені ними функції можуть бути комбінаціями будь-якого числа термів, формованих матрицею “І”. Тому ПМЛ поширені більше, ніж ПЛМ, і до їхнього складу відноситься більшість SPLD. 10

n n ПЛМ мають більшу функціональну гнучкість, всі відтворені ними функції можуть бути комбінаціями будь-якого числа термів, формованих матрицею “І”. Тому ПМЛ поширені більше, ніж ПЛМ, і до їхнього складу відноситься більшість SPLD. 10

n n n CPLD (Complex Programmable Logic Devices) – складні програмовані логічні схеми, які включають кілька блоків, подібних ПМЛ, і поєднуються засобами програмованої комутаційної матриці. В CPLD можуть входити сотні блоків і десятки тисяч еквівалентних вентилів. Архітектури CPLD розробляються фірмами Altera, Atmel, Lattice Semiconductor, Cypress Semiconductor, Xilinx і ін. Впливаючи на програмовані з’єднання комутаційної матриці й ПМЛ, що входять до складу CPLD, можна реалізувати будь-яку необхідну схему. 11

n n n CPLD (Complex Programmable Logic Devices) – складні програмовані логічні схеми, які включають кілька блоків, подібних ПМЛ, і поєднуються засобами програмованої комутаційної матриці. В CPLD можуть входити сотні блоків і десятки тисяч еквівалентних вентилів. Архітектури CPLD розробляються фірмами Altera, Atmel, Lattice Semiconductor, Cypress Semiconductor, Xilinx і ін. Впливаючи на програмовані з’єднання комутаційної матриці й ПМЛ, що входять до складу CPLD, можна реалізувати будь-яку необхідну схему. 11

n n FPGA (Field Programmable Gate Arrays) – мікросхеми програмованих користувачами вентильних матриць. У своїй основі складаються з великого числа конфігуруємих логічних блоків (ЛБ), що розташовані по рядкам і стовпцям у вигляді матриці, і трасувальних ресурсів, що забезпечують їх з’єднання. 12

n n FPGA (Field Programmable Gate Arrays) – мікросхеми програмованих користувачами вентильних матриць. У своїй основі складаються з великого числа конфігуруємих логічних блоків (ЛБ), що розташовані по рядкам і стовпцям у вигляді матриці, і трасувальних ресурсів, що забезпечують їх з’єднання. 12

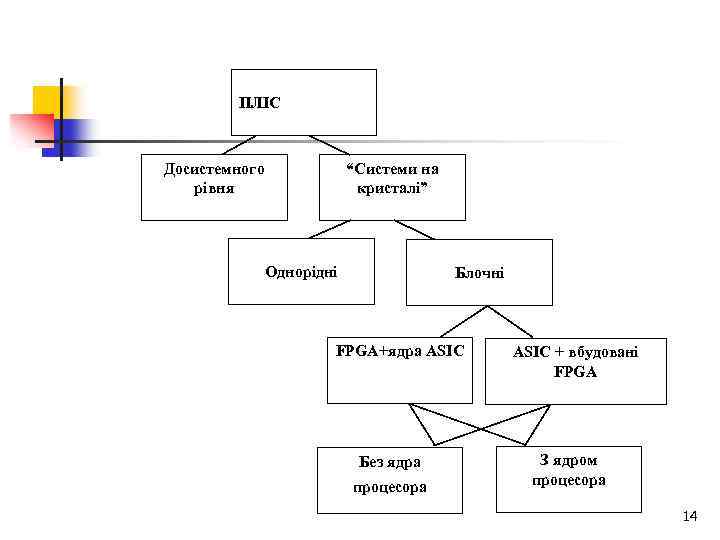

n n n 1. 2. Класифікація ПЛІС за рівнем інтеграції Класифікація за рівнем інтеграції відбиває, головним чином, ситуацію останніх років – бурхливий ріст рівня інтеграції ПЛІС і виділення з них класу “системи на кристалі”. У силу наявності тісного зв’язку між рівнем інтеграції й архітектурою, класифікація не є строгою. 13

n n n 1. 2. Класифікація ПЛІС за рівнем інтеграції Класифікація за рівнем інтеграції відбиває, головним чином, ситуацію останніх років – бурхливий ріст рівня інтеграції ПЛІС і виділення з них класу “системи на кристалі”. У силу наявності тісного зв’язку між рівнем інтеграції й архітектурою, класифікація не є строгою. 13

ПЛІС Досистемного рівня “Системи на кристалі” Однорідні Блочні FPGA+ядра ASIC Без ядра процесора ASIC + вбудовані FPGA З ядром процесора 14

ПЛІС Досистемного рівня “Системи на кристалі” Однорідні Блочні FPGA+ядра ASIC Без ядра процесора ASIC + вбудовані FPGA З ядром процесора 14

n n ПЛІС із широким діапазоном зміни рівня інтеграції (від простих до тих, що утримують сотні тисяч вентилів) віднесені до “досистемних” у тому розумінні, що для них не розглядалися питання створення цілих систем на одному кристалі. ПЛІС мегавентильного (найбільшого рівня інтеграції, що містить сотні тисяч або навіть мільйони еквівалентних вентилів) рівня інтеграції віднесені до “систем на кристалі”, що позначаються далі як SOPC (Systems On Programmable Chip). 15

n n ПЛІС із широким діапазоном зміни рівня інтеграції (від простих до тих, що утримують сотні тисяч вентилів) віднесені до “досистемних” у тому розумінні, що для них не розглядалися питання створення цілих систем на одному кристалі. ПЛІС мегавентильного (найбільшого рівня інтеграції, що містить сотні тисяч або навіть мільйони еквівалентних вентилів) рівня інтеграції віднесені до “систем на кристалі”, що позначаються далі як SOPC (Systems On Programmable Chip). 15

n n В однорідних SOPC різні блоки системи реалізуються тими самими апаратними засобами, завдяки програмованості цих засобів. Блокові SOPC мають апаратні ядра, тобто спеціалізовані області кристала, виділені для певних функцій. 16

n n В однорідних SOPC різні блоки системи реалізуються тими самими апаратними засобами, завдяки програмованості цих засобів. Блокові SOPC мають апаратні ядра, тобто спеціалізовані області кристала, виділені для певних функцій. 16

1. 3. Класифікація ПЛІС за кратністю програмування Класифікація за ознакою кратності програмування, обумовленої типом пам’яті конфігурації ПЛІС Однократно програмовані З плаваючими затворами без стирання заряду З перемичками З плавкими Репрограмовані в спеціальних режимах Оперативно репрограмовані З плаваючими затворами та ультрафіолетови м стиранням З репрогрумаванням перезагрузкою З плаваючими затворами та електричним стиранням З динамічним репрограмуванням Що пробиваються 17

1. 3. Класифікація ПЛІС за кратністю програмування Класифікація за ознакою кратності програмування, обумовленої типом пам’яті конфігурації ПЛІС Однократно програмовані З плаваючими затворами без стирання заряду З перемичками З плавкими Репрограмовані в спеціальних режимах Оперативно репрограмовані З плаваючими затворами та ультрафіолетови м стиранням З репрогрумаванням перезагрузкою З плаваючими затворами та електричним стиранням З динамічним репрограмуванням Що пробиваються 17

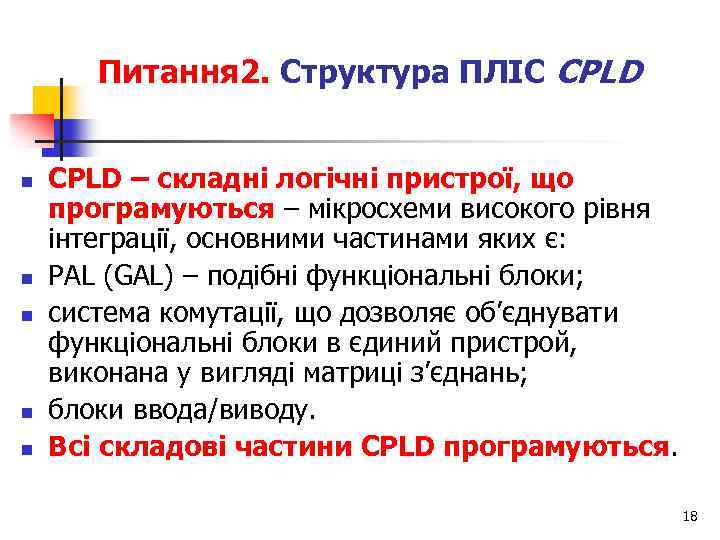

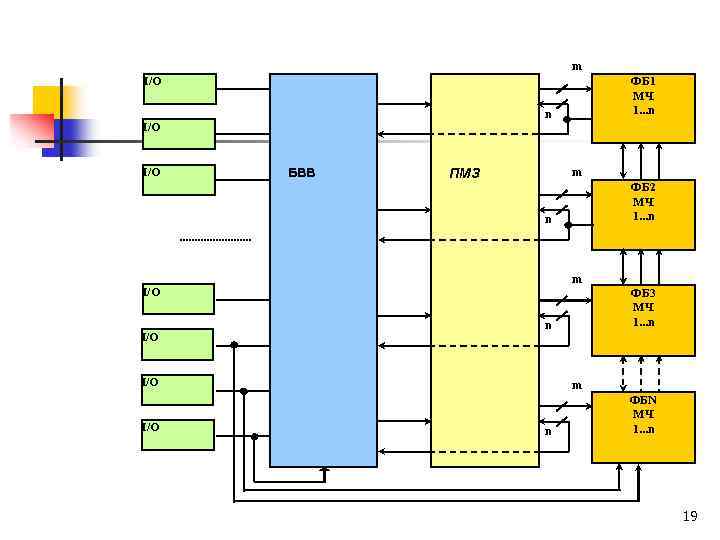

Питання 2. Структура ПЛІС CPLD n n n CPLD – складні логічні пристрої, що програмуються – мікросхеми високого рівня інтеграції, основними частинами яких є: PAL (GAL) – подібні функціональні блоки; система комутації, що дозволяє об’єднувати функціональні блоки в єдиний пристрой, виконана у вигляді матриці з’єднань; блоки ввода/виводу. Всі складові частини CPLD програмуються. 18

Питання 2. Структура ПЛІС CPLD n n n CPLD – складні логічні пристрої, що програмуються – мікросхеми високого рівня інтеграції, основними частинами яких є: PAL (GAL) – подібні функціональні блоки; система комутації, що дозволяє об’єднувати функціональні блоки в єдиний пристрой, виконана у вигляді матриці з’єднань; блоки ввода/виводу. Всі складові частини CPLD програмуються. 18

m І/О n І/О ФБ 1 МЧ 1. . . n БВВ m ПМЗ ФБ 2 МЧ 1. . . n n m І/О n І/О ФБ 3 МЧ 1. . . n m n ФБN МЧ 1. . . n 19

m І/О n І/О ФБ 1 МЧ 1. . . n БВВ m ПМЗ ФБ 2 МЧ 1. . . n n m І/О n І/О ФБ 3 МЧ 1. . . n m n ФБN МЧ 1. . . n 19

n n n В структурній схемі прийняти такі позначення. Через ФБ позначені функціональні блоки, кількість яких N залежить від рівня інтеграції мікросхеми і може змінюватися у достатньо широких межах. В кожному ФБ є n макрочарунок МЧ. Функціональні блоки отримують вхідні сигнали від програмованої матриці з’єднань ПМЗ. Кількість таких сигналів m. Вихідні сигнали ФБ поступають як в ПМЗ, так і в блоки вводу/виводу БВВ. ПМЗ забезпечує повну комутацію функціональних блоків, тобто можливість подавати сигнали з будь -якого їх виходу на будь-який вхід. 20

n n n В структурній схемі прийняти такі позначення. Через ФБ позначені функціональні блоки, кількість яких N залежить від рівня інтеграції мікросхеми і може змінюватися у достатньо широких межах. В кожному ФБ є n макрочарунок МЧ. Функціональні блоки отримують вхідні сигнали від програмованої матриці з’єднань ПМЗ. Кількість таких сигналів m. Вихідні сигнали ФБ поступають як в ПМЗ, так і в блоки вводу/виводу БВВ. ПМЗ забезпечує повну комутацію функціональних блоків, тобто можливість подавати сигнали з будь -якого їх виходу на будь-який вхід. 20

n n n Блоки вводу/виводу зв’язані із зовнішніми дво направленими виводами I/O, що, у залежності від запрограмованості, можуть бути використані як входи або як виходи. Три нижніх виводи або спеціалізуються для подачі на матрицю функціональних блоків сигналів глобального тактування, сигналів глобальної установки/обнулення; сигналів глобального керування третім станом вихідних буферів; Ці ж виводи можуть бути використані для 21 операцій вводу/виводу.

n n n Блоки вводу/виводу зв’язані із зовнішніми дво направленими виводами I/O, що, у залежності від запрограмованості, можуть бути використані як входи або як виходи. Три нижніх виводи або спеціалізуються для подачі на матрицю функціональних блоків сигналів глобального тактування, сигналів глобальної установки/обнулення; сигналів глобального керування третім станом вихідних буферів; Ці ж виводи можуть бути використані для 21 операцій вводу/виводу.

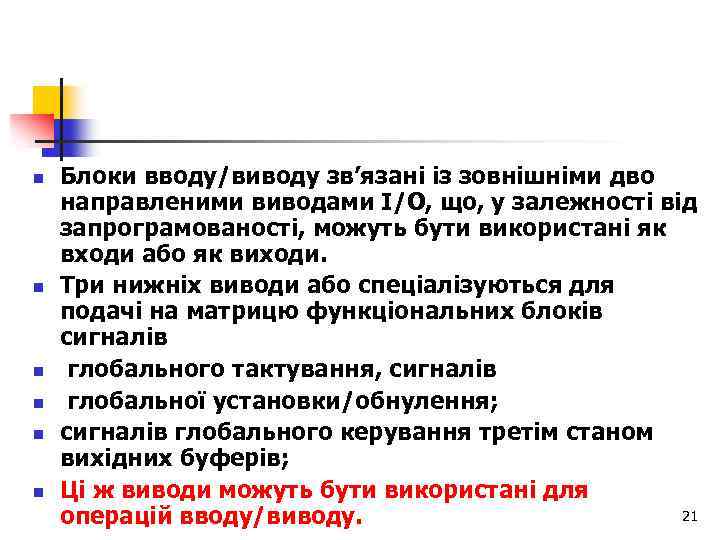

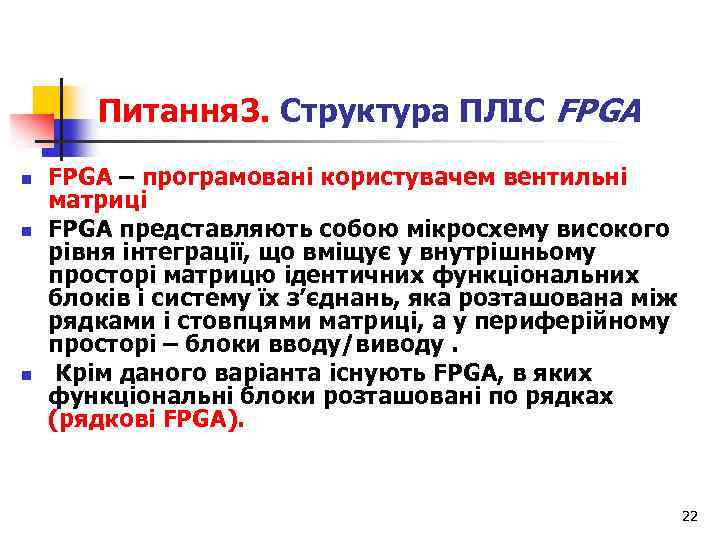

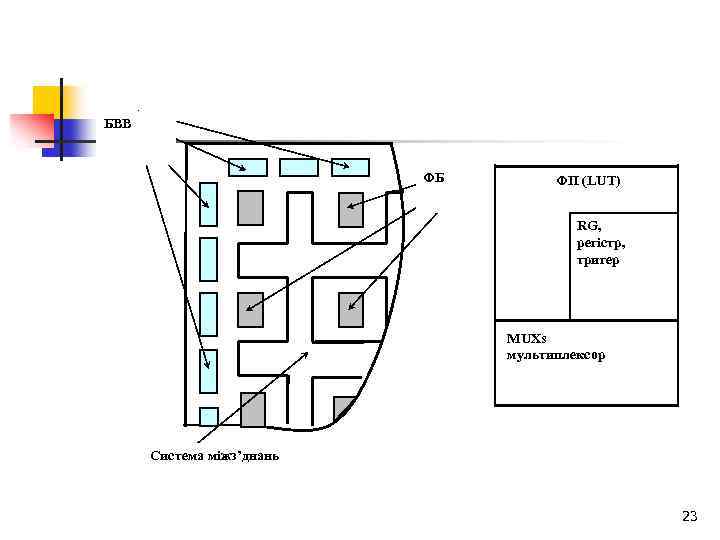

Питання 3. Структура ПЛІС FPGA n n n FPGA – програмовані користувачем вентильні матриці FPGA представляють собою мікросхему високого рівня інтеграції, що вміщує у внутрішньому просторі матрицю ідентичних функціональних блоків і систему їх з’єднань, яка розташована між рядками і стовпцями матриці, а у периферійному просторі – блоки вводу/виводу. Крім даного варіанта існують FPGA, в яких функціональні блоки розташовані по рядках (рядкові FPGA). 22

Питання 3. Структура ПЛІС FPGA n n n FPGA – програмовані користувачем вентильні матриці FPGA представляють собою мікросхему високого рівня інтеграції, що вміщує у внутрішньому просторі матрицю ідентичних функціональних блоків і систему їх з’єднань, яка розташована між рядками і стовпцями матриці, а у периферійному просторі – блоки вводу/виводу. Крім даного варіанта існують FPGA, в яких функціональні блоки розташовані по рядках (рядкові FPGA). 22

БВВ ФБ ФП (LUT) RG, регістр, тригер MUXs мультиплексор Система міжз’днань 23

БВВ ФБ ФП (LUT) RG, регістр, тригер MUXs мультиплексор Система міжз’днань 23

n n При конфігуруванні FPGA функціональні блоки налаштовуються на виконання потрібних операцій перетворення даних, а система з’єднань – на потрібні зв’язки між функціональними блоками. В результаті у внутрішньому просторі FPGA реалізується схема потрібної конфігурації. Розташовані по краям кристала блоки ввода/виводу забезпечують інтерфейс FPGA із зовнішнім середовищем. 24

n n При конфігуруванні FPGA функціональні блоки налаштовуються на виконання потрібних операцій перетворення даних, а система з’єднань – на потрібні зв’язки між функціональними блоками. В результаті у внутрішньому просторі FPGA реалізується схема потрібної конфігурації. Розташовані по краям кристала блоки ввода/виводу забезпечують інтерфейс FPGA із зовнішнім середовищем. 24

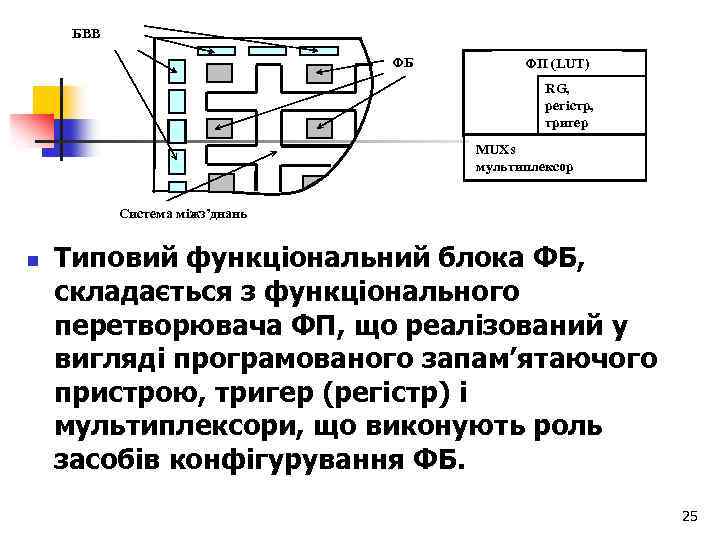

БВВ ФБ ФП (LUT) RG, регістр, тригер MUXs мультиплексор Система міжз’днань n Типовий функціональний блока ФБ, складається з функціонального перетворювача ФП, що реалізований у вигляді програмованого запам’ятаючого пристрою, тригер (регістр) і мультиплексори, що виконують роль засобів конфігурування ФБ. 25

БВВ ФБ ФП (LUT) RG, регістр, тригер MUXs мультиплексор Система міжз’днань n Типовий функціональний блока ФБ, складається з функціонального перетворювача ФП, що реалізований у вигляді програмованого запам’ятаючого пристрою, тригер (регістр) і мультиплексори, що виконують роль засобів конфігурування ФБ. 25

Питання 4. Структура ПЛІС FLEX n n ПЛІС с комбінованою архітектурою (FLEX) По мірі росту рівня інтеграції ПЛІС їх архітектури ускладнювалися, з’явилися архітектури, які в той чи іншій мірі об’єднують досягнення CPLD i FPGA. До кількості знову з’явившихся мікросхем за даною архітектурою в першу чергу можна віднести сімейство FLEX (Flexible Logic Element matri. X) фірми Altera. 26

Питання 4. Структура ПЛІС FLEX n n ПЛІС с комбінованою архітектурою (FLEX) По мірі росту рівня інтеграції ПЛІС їх архітектури ускладнювалися, з’явилися архітектури, які в той чи іншій мірі об’єднують досягнення CPLD i FPGA. До кількості знову з’явившихся мікросхем за даною архітектурою в першу чергу можна віднести сімейство FLEX (Flexible Logic Element matri. X) фірми Altera. 26

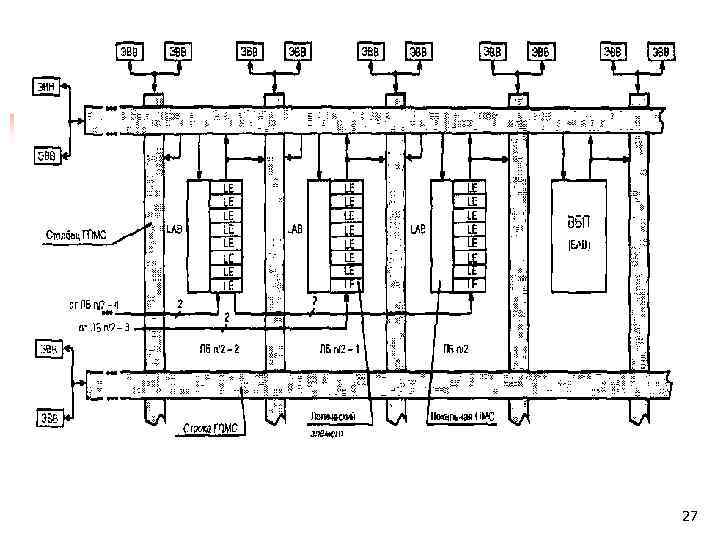

27

27

n n n Мікросхеми сімейства FLEX мають функціональні блоки LABs з логічними елементами ЛЕ, що включають функціональні перетворювачі ФП табличного типа. Функціональні блоки розташовані у вигляді матриці, між їх рядками і стовпцями розташовані горизонтальні і вертикальні трасировочні канали. Оскільки в схемах з великою кількістю функціональних блоків використання єдиної комутаційної матриці обмежена, то система комутації FLEX має два рівня з’єднань – глобальний і локальний. Локальна програмована матриця з’єднань (локальна ПМЗ або ЛПМЗ) забезпечує з’єднання логічних елементів ЛЕ, з яких складаються функціональні блоки LABs. У склад LAB входять 8 логічних елементів. 28

n n n Мікросхеми сімейства FLEX мають функціональні блоки LABs з логічними елементами ЛЕ, що включають функціональні перетворювачі ФП табличного типа. Функціональні блоки розташовані у вигляді матриці, між їх рядками і стовпцями розташовані горизонтальні і вертикальні трасировочні канали. Оскільки в схемах з великою кількістю функціональних блоків використання єдиної комутаційної матриці обмежена, то система комутації FLEX має два рівня з’єднань – глобальний і локальний. Локальна програмована матриця з’єднань (локальна ПМЗ або ЛПМЗ) забезпечує з’єднання логічних елементів ЛЕ, з яких складаються функціональні блоки LABs. У склад LAB входять 8 логічних елементів. 28

n n З’єднання між блоками LAB забезпечує глобальна програмована матриця з’єднань ГПМЗ, до кінців рядків і стовпців якої підключаються блоки ввода/виводу. У складі багатьох мікросхем ПЛІС є вбудовані блоки пам’яті ВБП. 29

n n З’єднання між блоками LAB забезпечує глобальна програмована матриця з’єднань ГПМЗ, до кінців рядків і стовпців якої підключаються блоки ввода/виводу. У складі багатьох мікросхем ПЛІС є вбудовані блоки пам’яті ВБП. 29

Дякую за увагу! 30

Дякую за увагу! 30