Лекция_10_рус.ppt

- Количество слайдов: 37

Лекция 10

Лекция 10

Принципы построения поцессоров 1. Все команды должны выполнятся с помощью аппаратного обеспечения. 2. Увеличение количество команд выполняемых компьютером. 3. Простата декодирования команд. 4. Память должна работать только с командами загрузки и хранения данных. 5. Увеличение количество регистров.

Принципы построения поцессоров 1. Все команды должны выполнятся с помощью аппаратного обеспечения. 2. Увеличение количество команд выполняемых компьютером. 3. Простата декодирования команд. 4. Память должна работать только с командами загрузки и хранения данных. 5. Увеличение количество регистров.

Параллелизм • Параллелизм на уровне команд – увеличение количество команд выполняемых за одну секунду • Параллелизм на уровне процессоров – одновременное использование нескольких процессоров

Параллелизм • Параллелизм на уровне команд – увеличение количество команд выполняемых за одну секунду • Параллелизм на уровне процессоров – одновременное использование нескольких процессоров

Параллелизм на уровне команд • Конвейер • Суперскалярная архитектура

Параллелизм на уровне команд • Конвейер • Суперскалярная архитектура

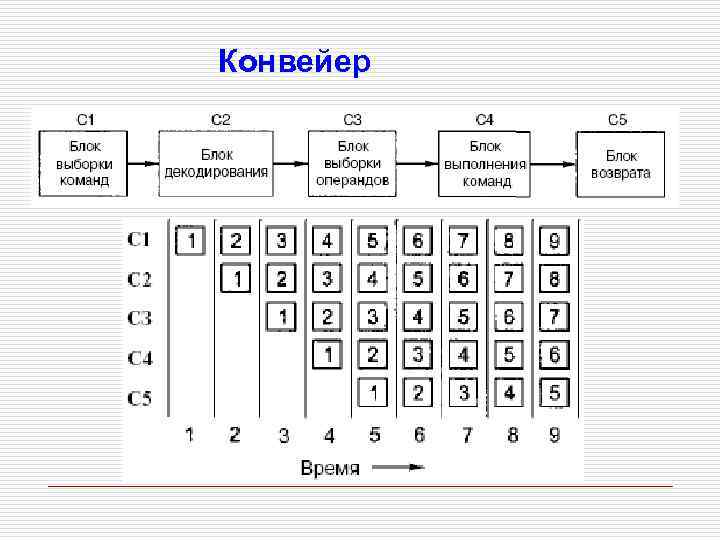

Конвейер

Конвейер

Конвейер • Время полного оборота цикла – 2 нс • Время прохождения команд через конвейр – 10 нс • 100 млн. операции в секунду • 500 млн. операции в секунду

Конвейер • Время полного оборота цикла – 2 нс • Время прохождения команд через конвейр – 10 нс • 100 млн. операции в секунду • 500 млн. операции в секунду

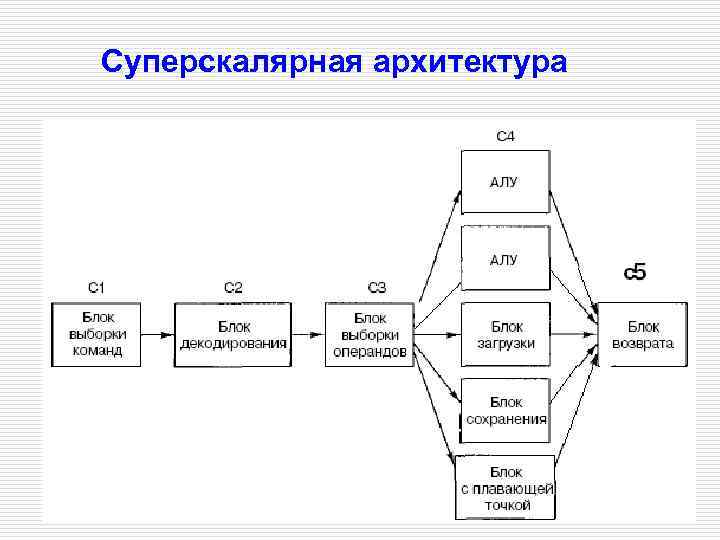

Суперскалярная архитектура

Суперскалярная архитектура

Суперскалярная архитектура

Суперскалярная архитектура

Параллелизм на уровне процессоров Филин Фенг Хокни Шнайдер

Параллелизм на уровне процессоров Филин Фенг Хокни Шнайдер

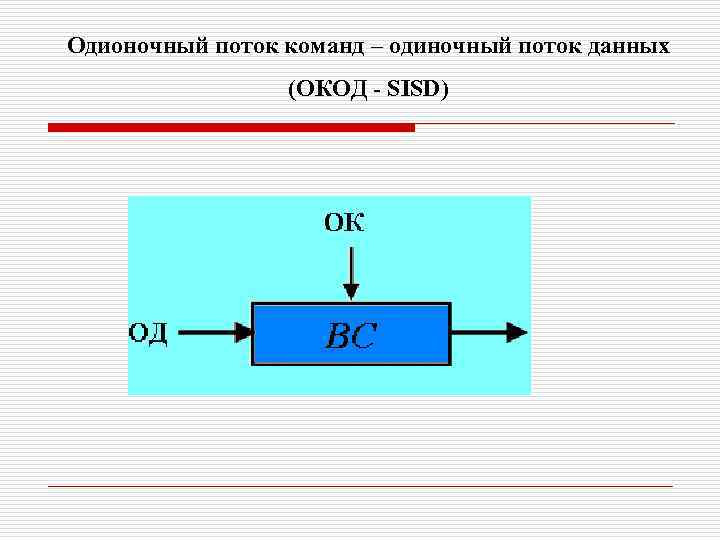

Одионочный поток команд – одиночный поток данных (ОКОД - SISD)

Одионочный поток команд – одиночный поток данных (ОКОД - SISD)

SISD Архитектура SISD – применяется в однопроцессорных и одномашинных вычислительных системах. К такому типу можно отнести обычные последовательные ЭВМ. Параллельизм в таких системах осуществляется за счет парраллельной работы отдельных блоков АЛУ, УВВ и процессора (PDP-11).

SISD Архитектура SISD – применяется в однопроцессорных и одномашинных вычислительных системах. К такому типу можно отнести обычные последовательные ЭВМ. Параллельизм в таких системах осуществляется за счет парраллельной работы отдельных блоков АЛУ, УВВ и процессора (PDP-11).

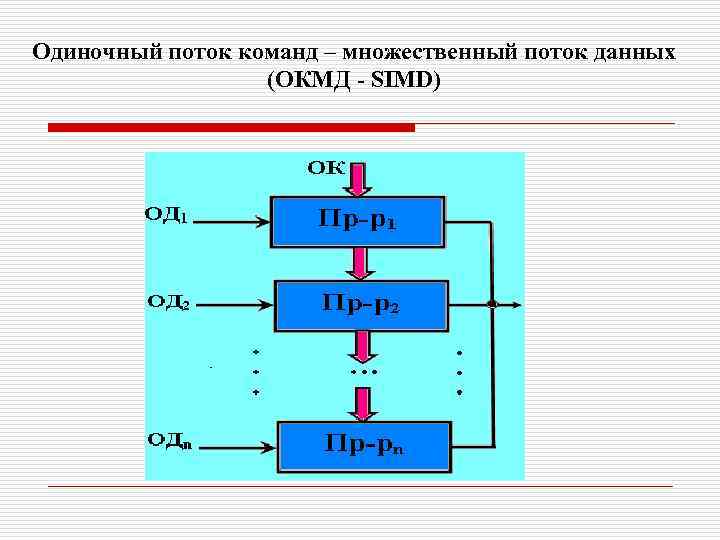

Одиночный поток команд – множественный поток данных (ОКМД - SIMD)

Одиночный поток команд – множественный поток данных (ОКМД - SIMD)

SIMD Архитектура SIMD – данные обрабатываются в векторном или матричном виде. Система состоит из нескольких однотипных процессоров, они управляется одной командой, одноко каждый процессор обрабатывает свои данные. Архитектура SIMD используется при обработке массивов, в линейных и нелинейных системах, при решении алгебраических задач, дифференциальных уровнении т. д. (ILLIAC IV, CARY 1).

SIMD Архитектура SIMD – данные обрабатываются в векторном или матричном виде. Система состоит из нескольких однотипных процессоров, они управляется одной командой, одноко каждый процессор обрабатывает свои данные. Архитектура SIMD используется при обработке массивов, в линейных и нелинейных системах, при решении алгебраических задач, дифференциальных уровнении т. д. (ILLIAC IV, CARY 1).

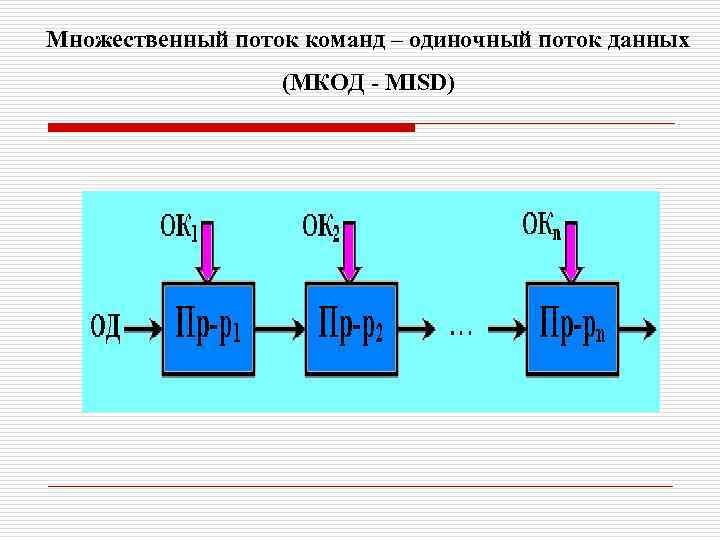

Множественный поток команд – одиночный поток данных (МКОД - MISD)

Множественный поток команд – одиночный поток данных (МКОД - MISD)

MISD Архитектура MISD - конвейр процессоров. Результаты оброботки данных на одном процессоре последовательно передается в следующий процессор.

MISD Архитектура MISD - конвейр процессоров. Результаты оброботки данных на одном процессоре последовательно передается в следующий процессор.

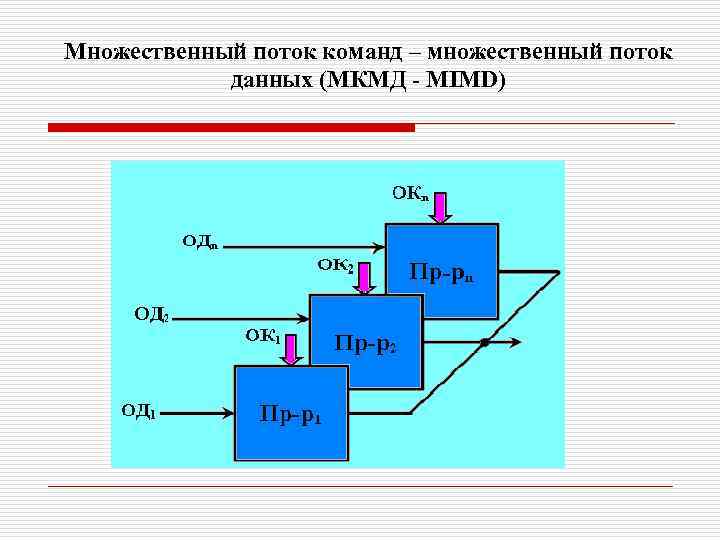

Множественный поток команд – множественный поток данных (МКМД - MIMD)

Множественный поток команд – множественный поток данных (МКМД - MIMD)

МIМD Архитектура МIМD – каждый процессор системы работает со своей программой и со своим потоком команд. Архитектура МIМD используется во многих вычислительных системах для увеличения пропускной способности.

МIМD Архитектура МIМD – каждый процессор системы работает со своей программой и со своим потоком команд. Архитектура МIМD используется во многих вычислительных системах для увеличения пропускной способности.

Многопроцессорные системы MIMD системы Мультипроцессоры NUMA системы Мультикомпьютеры MPP системы Кластеры

Многопроцессорные системы MIMD системы Мультипроцессоры NUMA системы Мультикомпьютеры MPP системы Кластеры

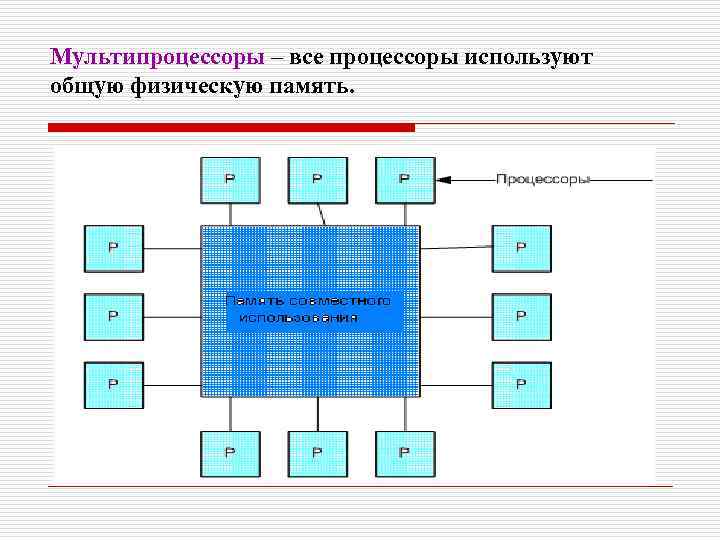

Мультипроцессоры – все процессоры используют общую физическую память.

Мультипроцессоры – все процессоры используют общую физическую память.

Мультипроцессор Достойнства: Любой из подключенных процессоров имеет доступ к информации записанной в памяти; Любой из подключенных процессоров имеет доступ к любому элементу памяти. Недостаток: Организация совместного доступа.

Мультипроцессор Достойнства: Любой из подключенных процессоров имеет доступ к информации записанной в памяти; Любой из подключенных процессоров имеет доступ к любому элементу памяти. Недостаток: Организация совместного доступа.

Мультикомпьютеры не используют общую память. Обмен данными между процессорами осуществляется через коммуникационную сеть.

Мультикомпьютеры не используют общую память. Обмен данными между процессорами осуществляется через коммуникационную сеть.

Мультикомпьютер Достойнство: Простота аппаратного устройства. Недостаток: Сложность централизованного управления и распределение данных между разными памятью. Заключение: Мультипроцессоры - сложность организации, простота программирования. Мультикомпьютеры – простота организации, сложность программированиия.

Мультикомпьютер Достойнство: Простота аппаратного устройства. Недостаток: Сложность централизованного управления и распределение данных между разными памятью. Заключение: Мультипроцессоры - сложность организации, простота программирования. Мультикомпьютеры – простота организации, сложность программированиия.

Мультипроцессоры UMA-системы UMA — архитектура с однородным доступом к памяти. Каждый процессор имеет одно и то же время доступа к любому модулю памяти. т. е. каждое слово памяти можно считать с той же скоростью, что и любое другое слово памяти. Если это технически невозможно, самые быстрые обращения замедляются, чтобы соответствовать самым медленным, поэтому программисты не увидят никакой разницы. Это и значит «однородный» . Такая однородность делает производительность предсказуемой, а этот фактор очень важен для написания эффективной программы.

Мультипроцессоры UMA-системы UMA — архитектура с однородным доступом к памяти. Каждый процессор имеет одно и то же время доступа к любому модулю памяти. т. е. каждое слово памяти можно считать с той же скоростью, что и любое другое слово памяти. Если это технически невозможно, самые быстрые обращения замедляются, чтобы соответствовать самым медленным, поэтому программисты не увидят никакой разницы. Это и значит «однородный» . Такая однородность делает производительность предсказуемой, а этот фактор очень важен для написания эффективной программы.

Мультипроцессоры UMA-системы Векторные параллельные системы (PVP) Симметричные мультипроцессоры (SMP)

Мультипроцессоры UMA-системы Векторные параллельные системы (PVP) Симметричные мультипроцессоры (SMP)

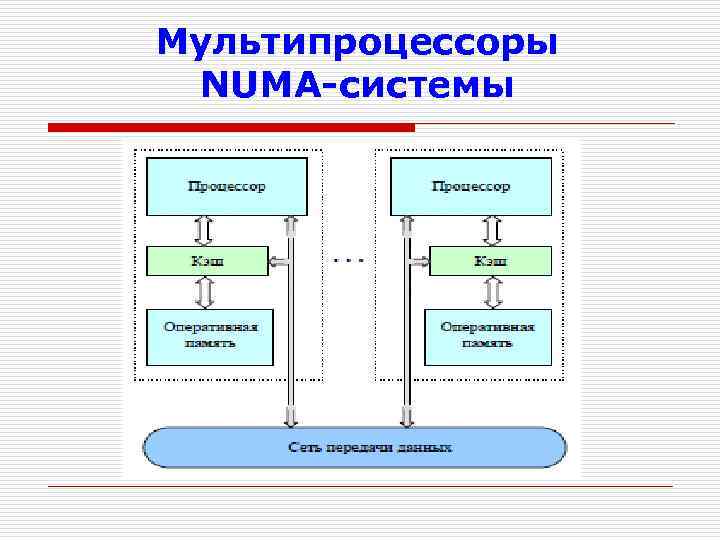

Мультипроцессоры NUMA-системы NUMA — архитектура с неоднородным доступом к памяти. Система состоит из однородных базовых модулей (плат), состоящих из небольшого числа процессоров и блока памяти. Модули объединены с помощью высокоскоростного коммутатора. Поддерживается единое адресное пространство, аппаратно поддерживается доступ к удаленной памяти, т. е. к памяти других модулей. При этом доступ к локальной памяти в несколько раз быстрее, чем к удаленной.

Мультипроцессоры NUMA-системы NUMA — архитектура с неоднородным доступом к памяти. Система состоит из однородных базовых модулей (плат), состоящих из небольшого числа процессоров и блока памяти. Модули объединены с помощью высокоскоростного коммутатора. Поддерживается единое адресное пространство, аппаратно поддерживается доступ к удаленной памяти, т. е. к памяти других модулей. При этом доступ к локальной памяти в несколько раз быстрее, чем к удаленной.

Мультипроцессоры NUMA-системы

Мультипроцессоры NUMA-системы

NUMA-системы COMA-системы (cache-only memory architecture) – системы, в которых для представления данных используется только локальная кэш память имеющихся процессоров; CC-NUMA-системы (cache-coherent NUMA) – системы, в которых обеспечивается однозначность (когерентность) локальных кэш памяти разных процессоров ; NCC-NUMA-системы (non-cache coherent NUMA) - системы, в которых обеспечивается общий доступ к локальной памяти разных процессоров без поддержки на аппаратном уровне когерентности кэша.

NUMA-системы COMA-системы (cache-only memory architecture) – системы, в которых для представления данных используется только локальная кэш память имеющихся процессоров; CC-NUMA-системы (cache-coherent NUMA) – системы, в которых обеспечивается однозначность (когерентность) локальных кэш памяти разных процессоров ; NCC-NUMA-системы (non-cache coherent NUMA) - системы, в которых обеспечивается общий доступ к локальной памяти разных процессоров без поддержки на аппаратном уровне когерентности кэша.

Мультикомпьютеры MPP-системы МРР — процессоры с массовым параллелизмом — дорогостоящие суперкомпьютеры, которые состоят из большого количества процессоров, связанных высокоскоростной коммуникационной сетью.

Мультикомпьютеры MPP-системы МРР — процессоры с массовым параллелизмом — дорогостоящие суперкомпьютеры, которые состоят из большого количества процессоров, связанных высокоскоростной коммуникационной сетью.

Мультикомпьютеры MPP-системы

Мультикомпьютеры MPP-системы

Мультикомпьютеры Кластерные системы (вычислительные кластеры)представляют собой более дешевый вариант MPP-систем. Вычислительный кластер состоит из совокупности персональных компьютеров или рабочих станций, объединенных локальной сетью в качестве коммуникационной среды. В отличии от локальных сетей у кластерные систем отличаются высокой надежностью, эффективностью и гораздо дешевле.

Мультикомпьютеры Кластерные системы (вычислительные кластеры)представляют собой более дешевый вариант MPP-систем. Вычислительный кластер состоит из совокупности персональных компьютеров или рабочих станций, объединенных локальной сетью в качестве коммуникационной среды. В отличии от локальных сетей у кластерные систем отличаются высокой надежностью, эффективностью и гораздо дешевле.

Топология сети передачи данных Центральный процессор Модули памяти Интерфейс Каналы связи Коммутаторы

Топология сети передачи данных Центральный процессор Модули памяти Интерфейс Каналы связи Коммутаторы

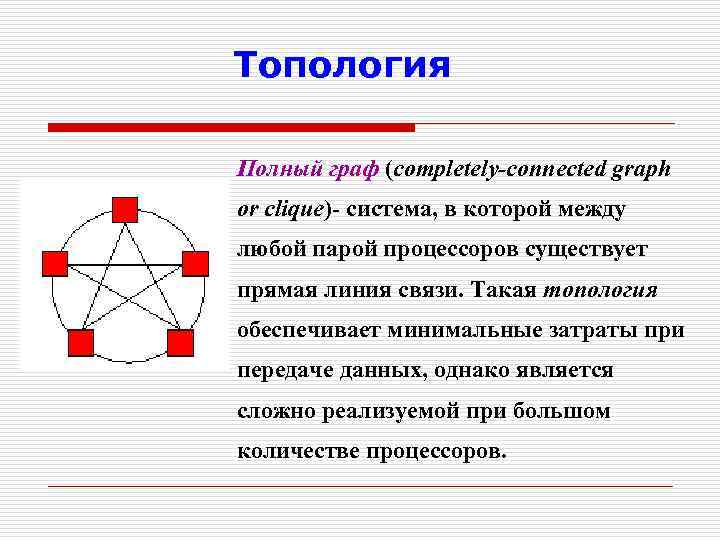

Топология Полный граф (completely-connected graph or clique)- система, в которой между любой парой процессоров существует прямая линия связи. Такая топология обеспечивает минимальные затраты при передаче данных, однако является сложно реализуемой при большом количестве процессоров.

Топология Полный граф (completely-connected graph or clique)- система, в которой между любой парой процессоров существует прямая линия связи. Такая топология обеспечивает минимальные затраты при передаче данных, однако является сложно реализуемой при большом количестве процессоров.

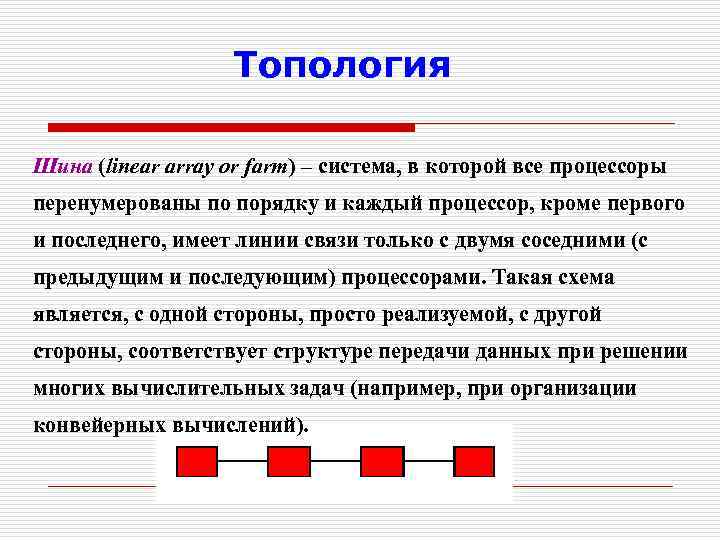

Топология Шина (linear array or farm) – система, в которой все процессоры перенумерованы по порядку и каждый процессор, кроме первого и последнего, имеет линии связи только с двумя соседними (с предыдущим и последующим) процессорами. Такая схема является, с одной стороны, просто реализуемой, c другой стороны, соответствует структуре передачи данных при решении многих вычислительных задач (например, при организации конвейерных вычислений).

Топология Шина (linear array or farm) – система, в которой все процессоры перенумерованы по порядку и каждый процессор, кроме первого и последнего, имеет линии связи только с двумя соседними (с предыдущим и последующим) процессорами. Такая схема является, с одной стороны, просто реализуемой, c другой стороны, соответствует структуре передачи данных при решении многих вычислительных задач (например, при организации конвейерных вычислений).

Топология Кольцо (ring) – топология получается из линейки процессоров соединением первого и последнего процессоров линейки.

Топология Кольцо (ring) – топология получается из линейки процессоров соединением первого и последнего процессоров линейки.

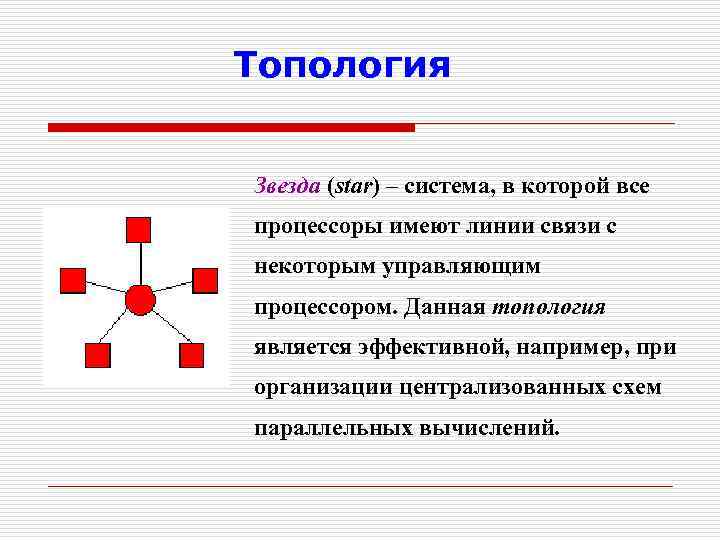

Топология Звезда (star) – система, в которой все процессоры имеют линии связи с некоторым управляющим процессором. Данная топология является эффективной, например, при организации централизованных схем параллельных вычислений.

Топология Звезда (star) – система, в которой все процессоры имеют линии связи с некоторым управляющим процессором. Данная топология является эффективной, например, при организации централизованных схем параллельных вычислений.

Топология Сетка (mesh) – система, в которой граф линий связи образует прямоугольную сетку (обычно двух- или трехмерную). Подобная топология может быть достаточно просто реализована и, кроме того, эффективно использована при параллельном выполнении многих численных алгоритмов.

Топология Сетка (mesh) – система, в которой граф линий связи образует прямоугольную сетку (обычно двух- или трехмерную). Подобная топология может быть достаточно просто реализована и, кроме того, эффективно использована при параллельном выполнении многих численных алгоритмов.

Топология Гиперкуб (hypercube) – данная топология представляет собой частный случай структуры решетки, когда по каждой размерности сетки имеется только два процессора (т. е. гиперкуб содержит 2 n процессоров при размерности n). Такой вариант организации сети передачи данных достаточно широко распространен на практике.

Топология Гиперкуб (hypercube) – данная топология представляет собой частный случай структуры решетки, когда по каждой размерности сетки имеется только два процессора (т. е. гиперкуб содержит 2 n процессоров при размерности n). Такой вариант организации сети передачи данных достаточно широко распространен на практике.