39edfed1034541921d2a9da383db537a.ppt

- Количество слайдов: 35

Lecture 2 Microprocessor Architecture Image from: http: //micro. magnet. fsu. edu/chipshots/intel/images/intel 8080 dielarge. jpg

Lecture 2 Microprocessor Architecture Image from: http: //micro. magnet. fsu. edu/chipshots/intel/images/intel 8080 dielarge. jpg

Agenda n Microprocessor components n The memory n Internal organization of MPU n Introducing MARIE n Source n Homework

Agenda n Microprocessor components n The memory n Internal organization of MPU n Introducing MARIE n Source n Homework

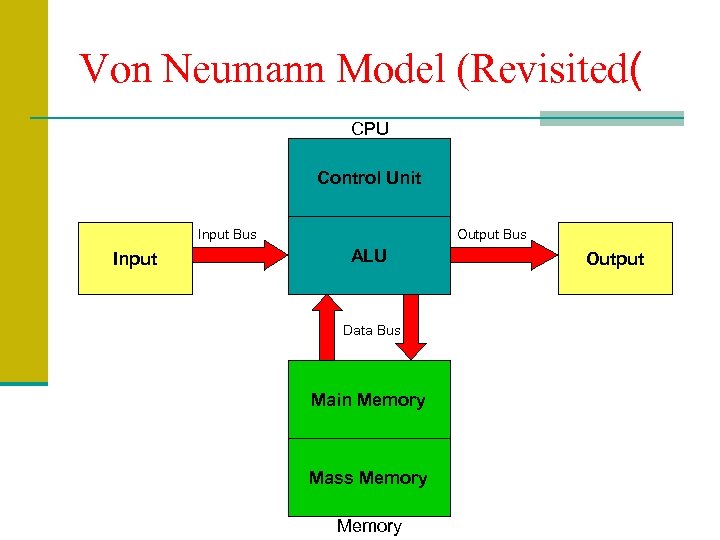

Von Neumann Model (Revisited( CPU Control Unit Input Bus Input Output Bus ALU Data Bus Main Memory Mass Memory Output

Von Neumann Model (Revisited( CPU Control Unit Input Bus Input Output Bus ALU Data Bus Main Memory Mass Memory Output

CPU Components n Arithmetic Logic Unit (ALU) n Performs A & L ops on the data passing through it. n Addition, subtraction n Logical AND, OR, shift ops n Control Unit (CU) n Sequences the ops of the entire system n Fetch, decode, execute the successive instructions of a program stored in the memory. n Generate signals to synchronize operations n There are 3 buses used to interconnect a system n Address buses, data buses, and control buses

CPU Components n Arithmetic Logic Unit (ALU) n Performs A & L ops on the data passing through it. n Addition, subtraction n Logical AND, OR, shift ops n Control Unit (CU) n Sequences the ops of the entire system n Fetch, decode, execute the successive instructions of a program stored in the memory. n Generate signals to synchronize operations n There are 3 buses used to interconnect a system n Address buses, data buses, and control buses

Memory Module n Store information (programs, data) n A program specifies the sequence of steps exec by the computer. n Each successive instruction is fetched into a special register of the CU. n Then, it is decoded and executed. n The data are processed by the ALU. n Max size of main memory (RAM, ROM) is limited by cost and by the addressing capability of the CPU. n Therefore, mass memory (disks, tapes, etc) is required.

Memory Module n Store information (programs, data) n A program specifies the sequence of steps exec by the computer. n Each successive instruction is fetched into a special register of the CU. n Then, it is decoded and executed. n The data are processed by the ALU. n Max size of main memory (RAM, ROM) is limited by cost and by the addressing capability of the CPU. n Therefore, mass memory (disks, tapes, etc) is required.

Input/Output Modules n They are used to communicate with the outside world. n Input supplies information to the ALU, or the memory. n n Keyboard, mouse, sensors, etc. Output displays the data coming out of the ALU or executes commands. n Printer, control mechanism (motor, relay), etc.

Input/Output Modules n They are used to communicate with the outside world. n Input supplies information to the ALU, or the memory. n n Keyboard, mouse, sensors, etc. Output displays the data coming out of the ALU or executes commands. n Printer, control mechanism (motor, relay), etc.

The Buses n Data bus Transmits data between units n Bidirectional n Bus width typically equals to microprocessor’s bit-width (i. e. 8 -bit MPU has 8 -bit wide data bus) n Address bus n Used to select the origin or destination of signal transmitted on another bus or line. n If there are 16 lines of address bus 64 K addressable n Control bus n Synchronizes the activities of the system. n Carries status and control info both to and from the MPU n An effective bus design is crucial to the speed of the system. n

The Buses n Data bus Transmits data between units n Bidirectional n Bus width typically equals to microprocessor’s bit-width (i. e. 8 -bit MPU has 8 -bit wide data bus) n Address bus n Used to select the origin or destination of signal transmitted on another bus or line. n If there are 16 lines of address bus 64 K addressable n Control bus n Synchronizes the activities of the system. n Carries status and control info both to and from the MPU n An effective bus design is crucial to the speed of the system. n

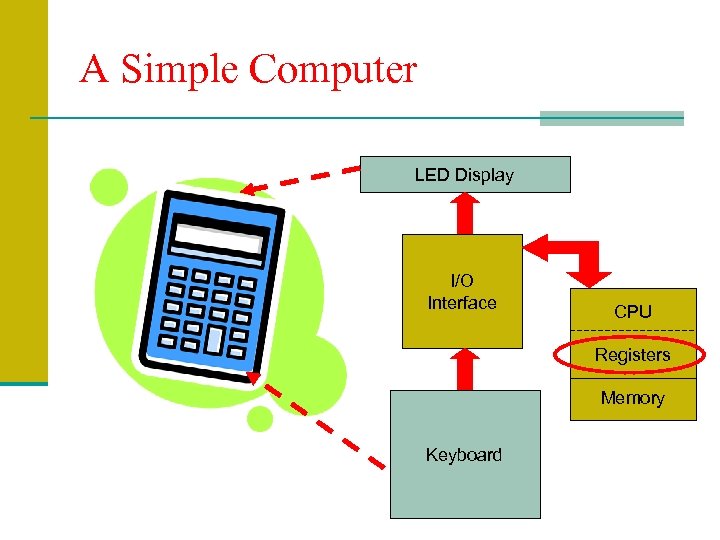

A Simple Computer LED Display I/O Interface CPU Registers Memory Keyboard

A Simple Computer LED Display I/O Interface CPU Registers Memory Keyboard

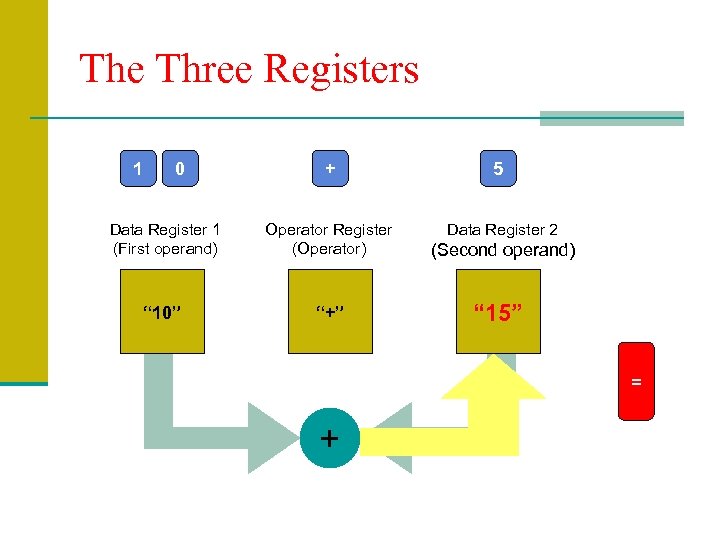

The Three Registers 1 0 + 5 Data Register 1 (First operand) Operator Register (Operator) Data Register 2 (Second operand) “ 10” “+” “ 5” “ 15” = +

The Three Registers 1 0 + 5 Data Register 1 (First operand) Operator Register (Operator) Data Register 2 (Second operand) “ 10” “+” “ 5” “ 15” = +

The Memory n Memory Hierarchy n Internal registers (fastest, lowest capacity) n Part of the ALU Main memory n Mass memory (slowest, largest capacity) n n Memory Access n Logically organized in “words”.

The Memory n Memory Hierarchy n Internal registers (fastest, lowest capacity) n Part of the ALU Main memory n Mass memory (slowest, largest capacity) n n Memory Access n Logically organized in “words”.

Bits. . Bytes. . Words!… n A bit represents either 0 or 1. n 1 byte = 8 bits n A logical word of: n 8 -bit MPU = 1 byte n 16 -bit MPU = 2 bytes n 32 -bit MPU = 4 bytes n I want to know what information you could get from the word “bit”, so I decided to assign you a homework…

Bits. . Bytes. . Words!… n A bit represents either 0 or 1. n 1 byte = 8 bits n A logical word of: n 8 -bit MPU = 1 byte n 16 -bit MPU = 2 bytes n 32 -bit MPU = 4 bytes n I want to know what information you could get from the word “bit”, so I decided to assign you a homework…

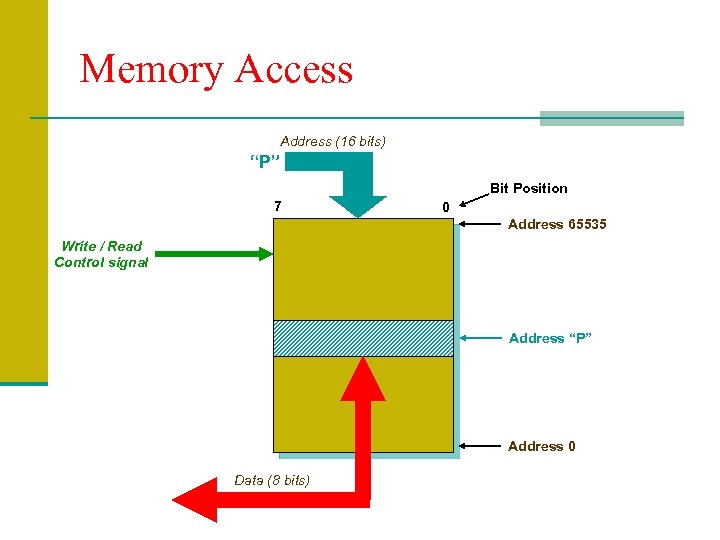

Memory Access Address (16 bits) “P” Bit Position 7 0 Address 65535 Write / Read Control signal Address “P” Address 0 Data (8 bits)

Memory Access Address (16 bits) “P” Bit Position 7 0 Address 65535 Write / Read Control signal Address “P” Address 0 Data (8 bits)

http: //www. intel. com Take a closer look… (Intel 8080(

http: //www. intel. com Take a closer look… (Intel 8080(

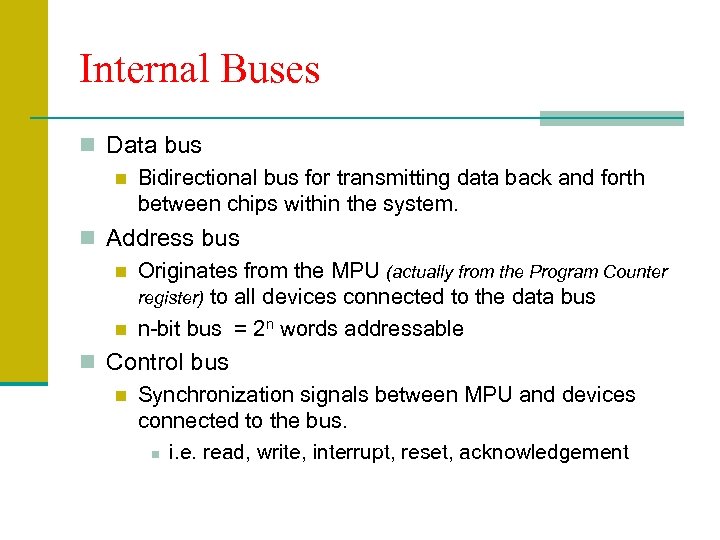

Internal Buses n Data bus n Bidirectional bus for transmitting data back and forth between chips within the system. n Address bus n Originates from the MPU (actually from the Program Counter register) to all devices connected to the data bus n n-bit bus = 2 n words addressable n Control bus n Synchronization signals between MPU and devices connected to the bus. n i. e. read, write, interrupt, reset, acknowledgement

Internal Buses n Data bus n Bidirectional bus for transmitting data back and forth between chips within the system. n Address bus n Originates from the MPU (actually from the Program Counter register) to all devices connected to the data bus n n-bit bus = 2 n words addressable n Control bus n Synchronization signals between MPU and devices connected to the bus. n i. e. read, write, interrupt, reset, acknowledgement

Architecture Category n The data bus is the bus that defines the architecture of a system. n Count the number of data buses used to communicate between the registers and the ALU

Architecture Category n The data bus is the bus that defines the architecture of a system. n Count the number of data buses used to communicate between the registers and the ALU

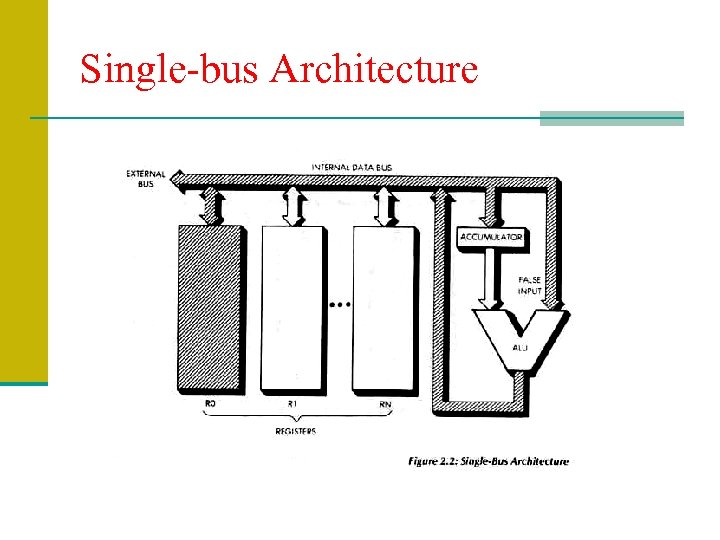

Single-bus Architecture

Single-bus Architecture

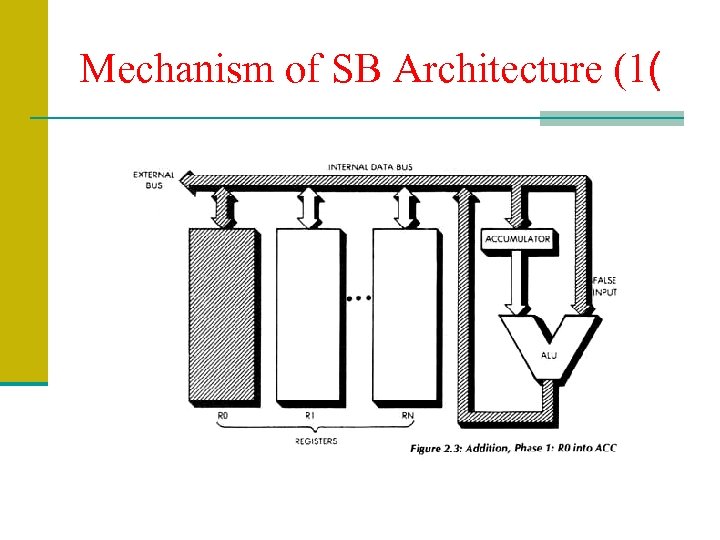

Mechanism of SB Architecture (1(

Mechanism of SB Architecture (1(

Mechanism of SB Architecture (2(

Mechanism of SB Architecture (2(

Mechanism of SB Architecture (3(

Mechanism of SB Architecture (3(

The Critical Race Problem

The Critical Race Problem

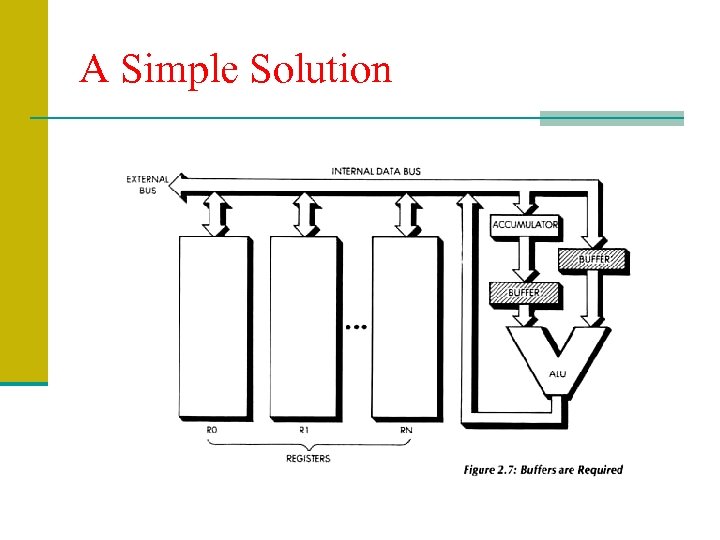

A Simple Solution

A Simple Solution

Double-Bus Architecture

Double-Bus Architecture

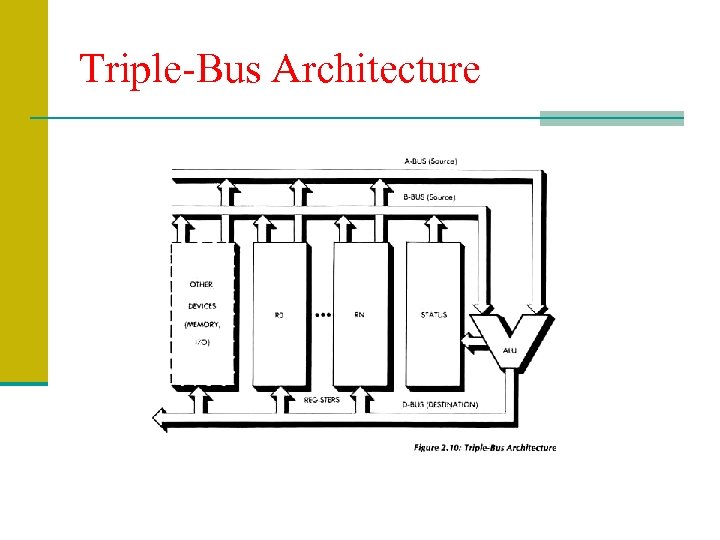

Triple-Bus Architecture

Triple-Bus Architecture

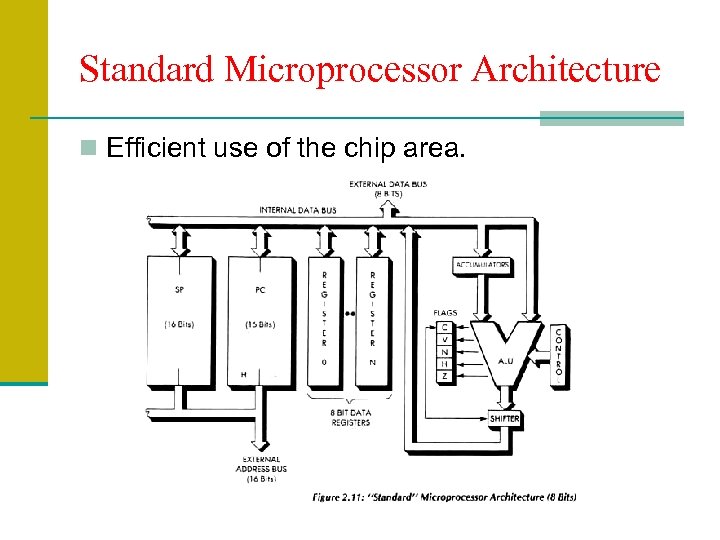

Standard Microprocessor Architecture n Efficient use of the chip area.

Standard Microprocessor Architecture n Efficient use of the chip area.

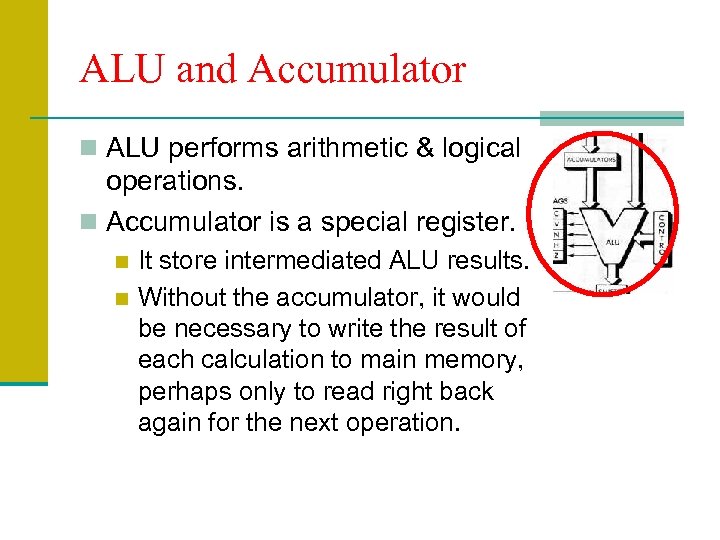

ALU and Accumulator n ALU performs arithmetic & logical operations. n Accumulator is a special register. It store intermediated ALU results. n Without the accumulator, it would be necessary to write the result of each calculation to main memory, perhaps only to read right back again for the next operation. n

ALU and Accumulator n ALU performs arithmetic & logical operations. n Accumulator is a special register. It store intermediated ALU results. n Without the accumulator, it would be necessary to write the result of each calculation to main memory, perhaps only to read right back again for the next operation. n

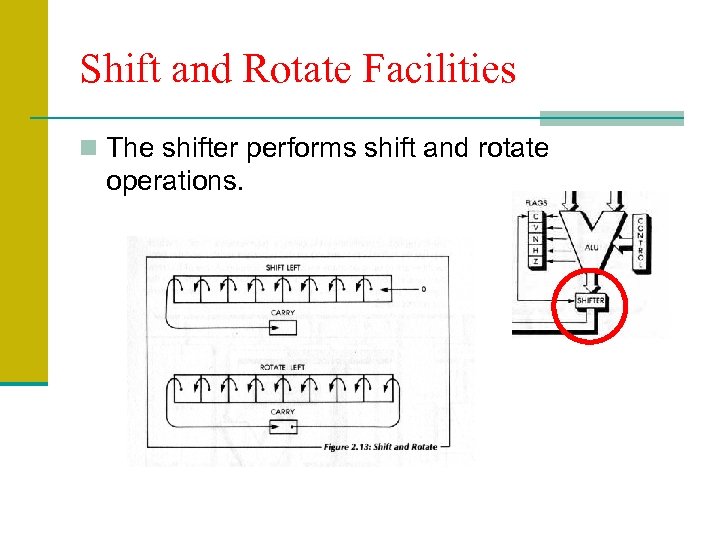

Shift and Rotate Facilities n The shifter performs shift and rotate operations.

Shift and Rotate Facilities n The shifter performs shift and rotate operations.

Flags Register n Stores exceptional conditions occurring within the ALU n n n C (Carry) V (Overflow) N (Negative) H (Half-carry) Z (Zero) n The contents of the flags register may then be n tested by specialized instruction, or n read on the internal data bus n Note: Status bits may be named differently from one MPU to another. There also might be more status bits (read the spec).

Flags Register n Stores exceptional conditions occurring within the ALU n n n C (Carry) V (Overflow) N (Negative) H (Half-carry) Z (Zero) n The contents of the flags register may then be n tested by specialized instruction, or n read on the internal data bus n Note: Status bits may be named differently from one MPU to another. There also might be more status bits (read the spec).

General-Purpose Registers n Fast memories provided that the ALU can manipulate data at high speed. n There are limited number of GPRs because of restrictions placed on the number of bits that it is reasonable to provide within an instruction. n Specific role of these registers is not defined in advance. They may be used to contain any data generated by the program. n Register-pairs facilitate to operate two of these registers simultaneously.

General-Purpose Registers n Fast memories provided that the ALU can manipulate data at high speed. n There are limited number of GPRs because of restrictions placed on the number of bits that it is reasonable to provide within an instruction. n Specific role of these registers is not defined in advance. They may be used to contain any data generated by the program. n Register-pairs facilitate to operate two of these registers simultaneously.

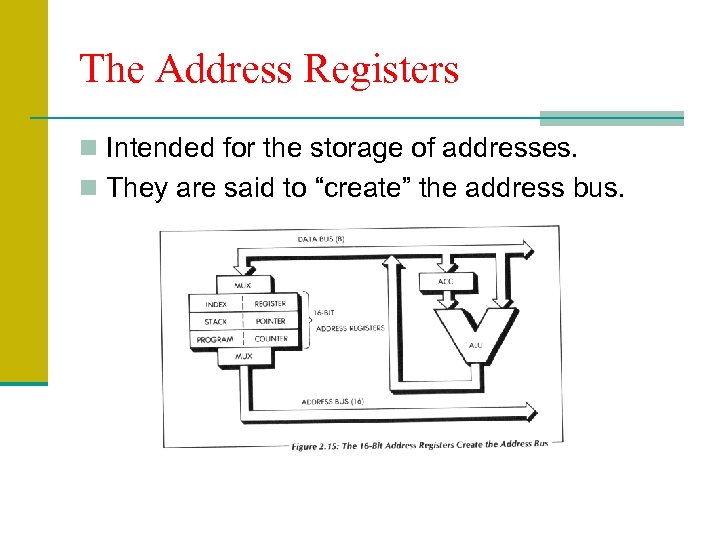

The Address Registers n Intended for the storage of addresses. n They are said to “create” the address bus.

The Address Registers n Intended for the storage of addresses. n They are said to “create” the address bus.

Program Counter (PC( n All microprocessors contains at least the program counter. n Contains the address of the next instruction to be executed.

Program Counter (PC( n All microprocessors contains at least the program counter. n Contains the address of the next instruction to be executed.

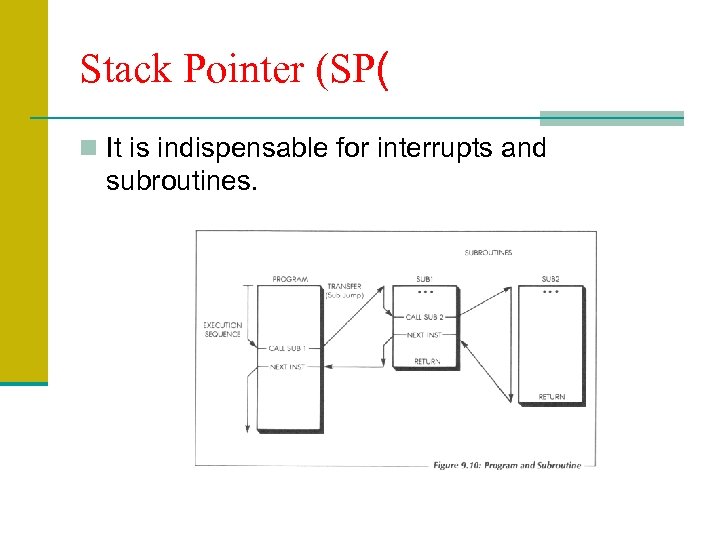

Stack Pointer (SP( n It is indispensable for interrupts and subroutines.

Stack Pointer (SP( n It is indispensable for interrupts and subroutines.

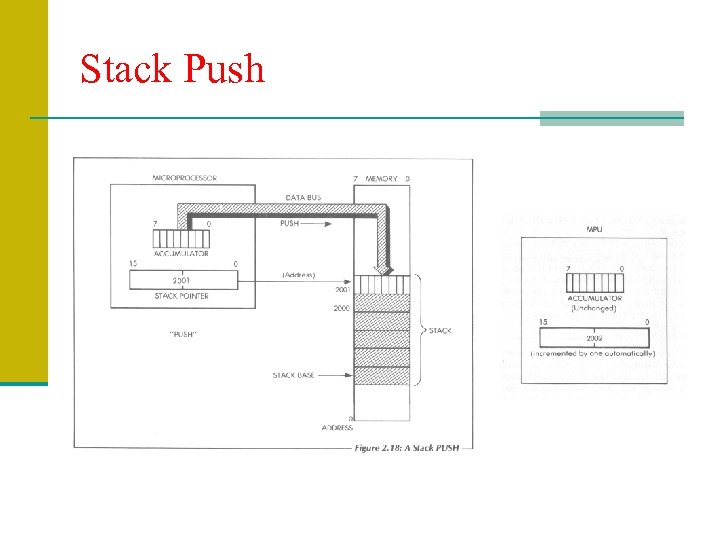

Stack Push

Stack Push

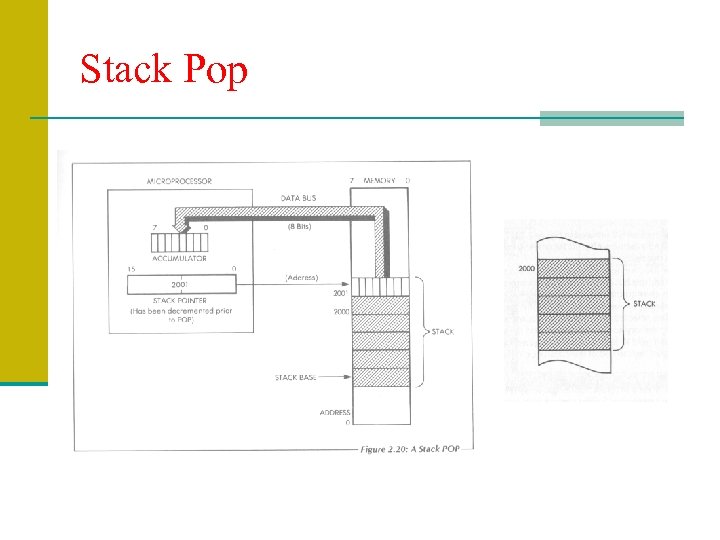

Stack Pop

Stack Pop

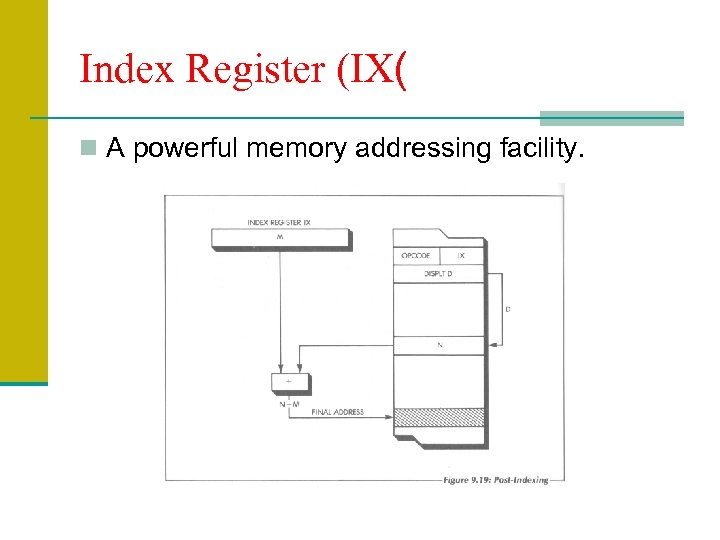

Index Register (IX( n A powerful memory addressing facility.

Index Register (IX( n A powerful memory addressing facility.

Disclaimer n Some diagrams in this slide are scanned and some are redrawn for teaching purpose only. They are in the book: R. Zaks, From Chips to Systems: an Introduction to Microprocessors, Sybex, 1981.

Disclaimer n Some diagrams in this slide are scanned and some are redrawn for teaching purpose only. They are in the book: R. Zaks, From Chips to Systems: an Introduction to Microprocessors, Sybex, 1981.