3c489470922f9b942cd4e2bbc94cf23e.ppt

- Количество слайдов: 26

Layout-based Logic Decomposition for Timing Optimization Yun-Yin Lien* Youn-Long Lin Department of Computer Science, National Tsing Hua University, Hsin-Chu, Taiwan 300, ROC *Global Unichip Corporation

Outline z. Introduction z. Motivation z. Previous Work z. Proposed Methods z. Experimental Results z. Conclusions and Future Works Uni. Chip

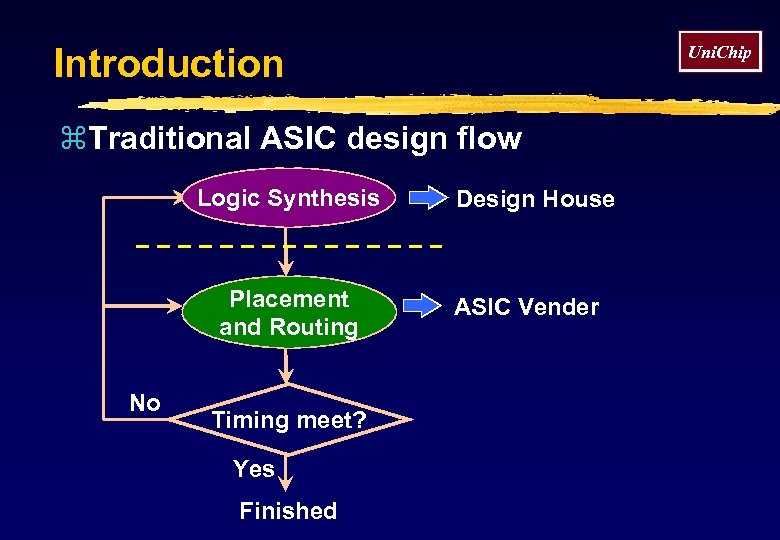

Introduction Uni. Chip z. Traditional ASIC design flow Logic Synthesis Placement and Routing No Timing meet? Yes Finished Design House ASIC Vender

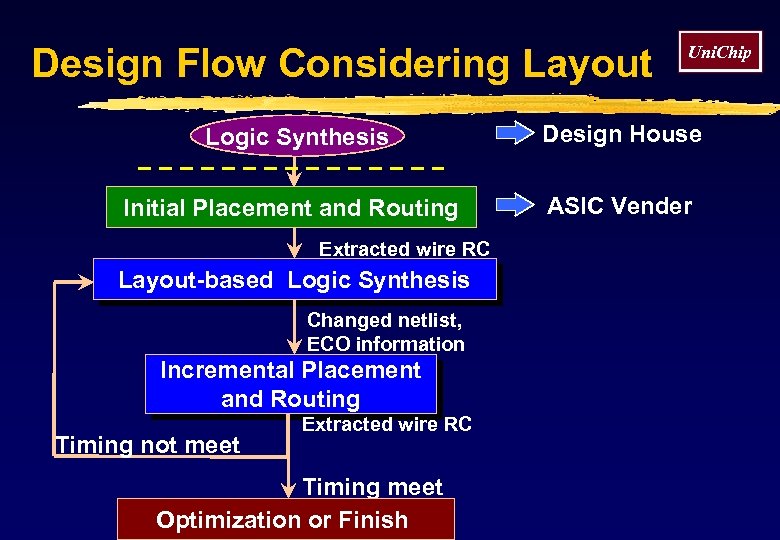

Design Flow Considering Layout Uni. Chip Logic Synthesis Design House Initial Placement and Routing ASIC Vender Extracted wire RC Layout-based Logic Synthesis Changed netlist, ECO information Incremental Placement and Routing Timing not meet Extracted wire RC Timing meet Optimization or Finish

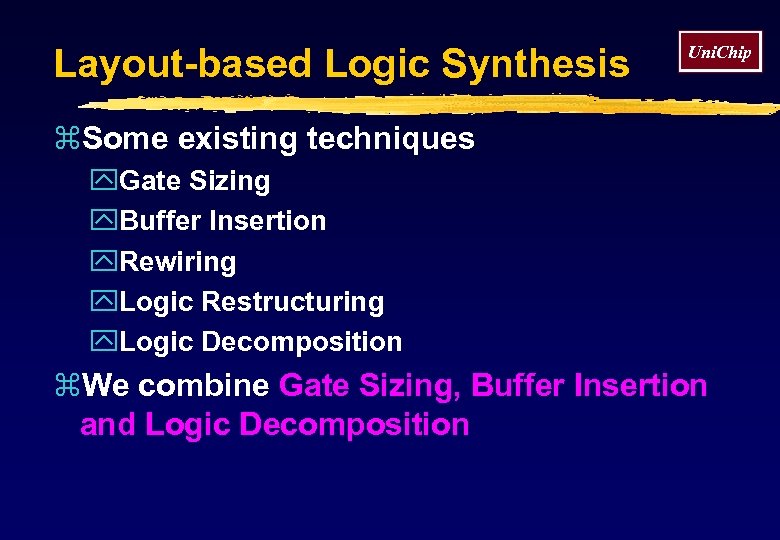

Layout-based Logic Synthesis Uni. Chip z. Some existing techniques y. Gate Sizing y. Buffer Insertion y. Rewiring y. Logic Restructuring y. Logic Decomposition z. We combine Gate Sizing, Buffer Insertion and Logic Decomposition

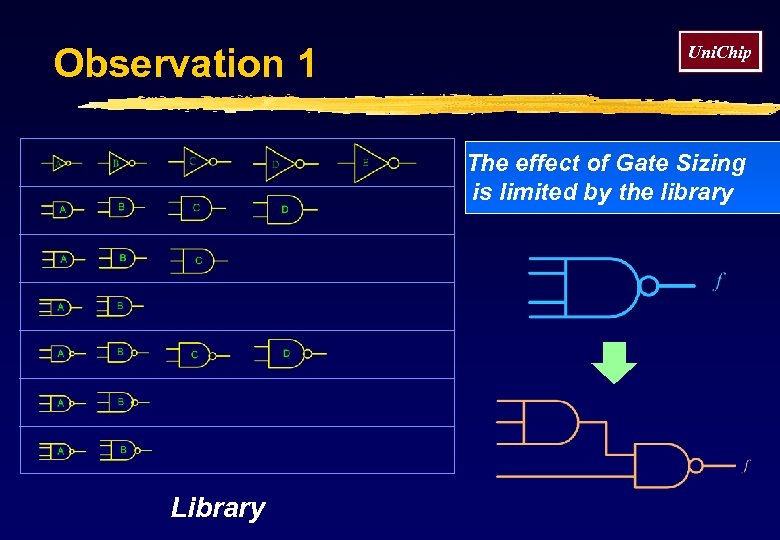

Observation 1 Uni. Chip The effect of Gate Sizing is limited by the library Library

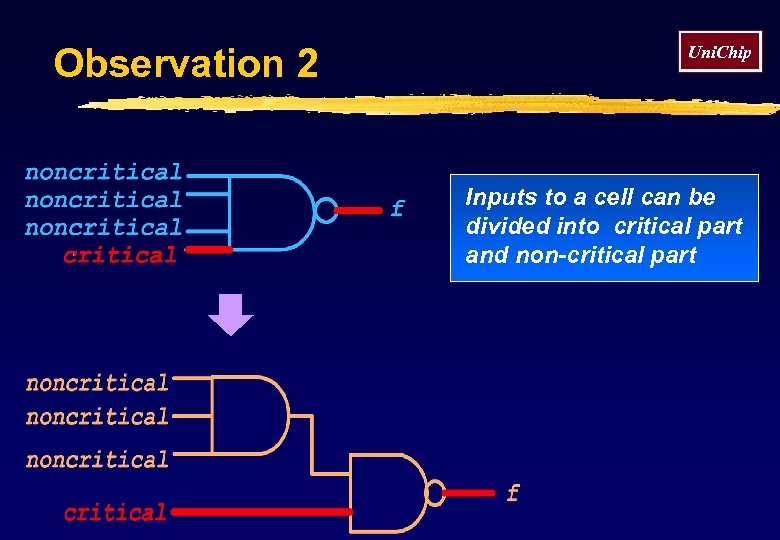

Observation 2 Uni. Chip Inputs to a cell can be divided into critical part and non-critical part

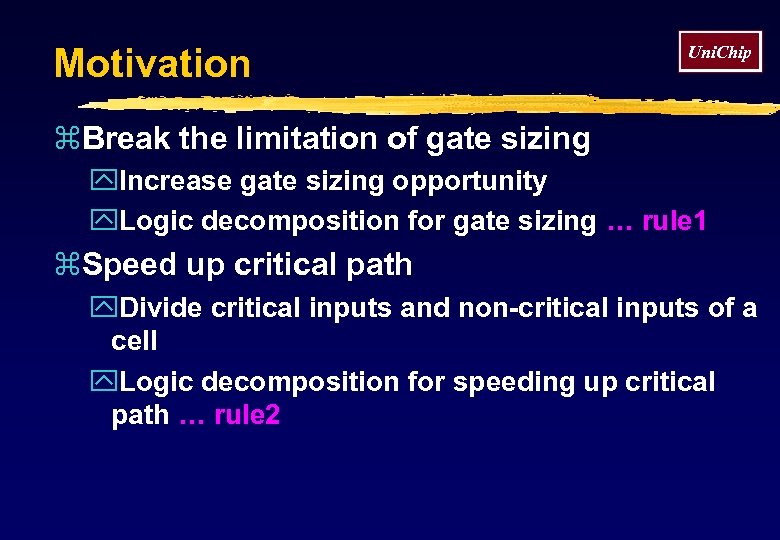

Motivation Uni. Chip z. Break the limitation of gate sizing y. Increase gate sizing opportunity y. Logic decomposition for gate sizing … rule 1 z. Speed up critical path y. Divide critical inputs and non-critical inputs of a cell y. Logic decomposition for speeding up critical path … rule 2

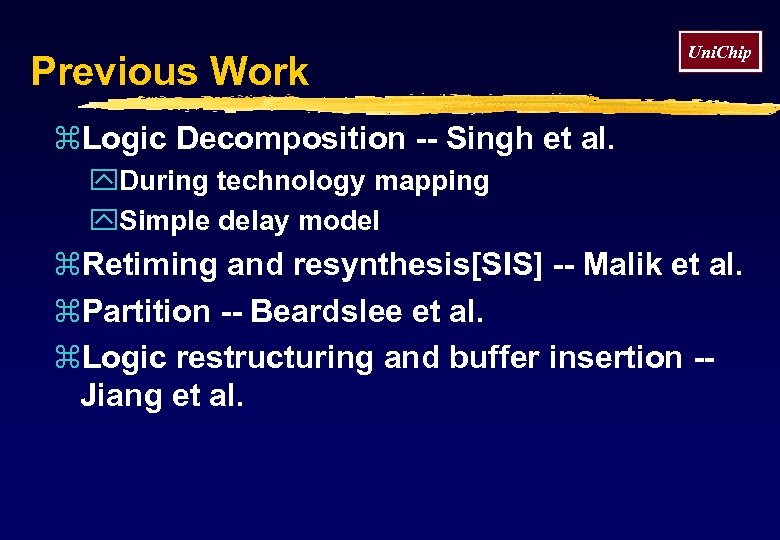

Previous Work Uni. Chip z. Logic Decomposition -- Singh et al. y. During technology mapping y. Simple delay model z. Retiming and resynthesis[SIS] -- Malik et al. z. Partition -- Beardslee et al. z. Logic restructuring and buffer insertion -Jiang et al.

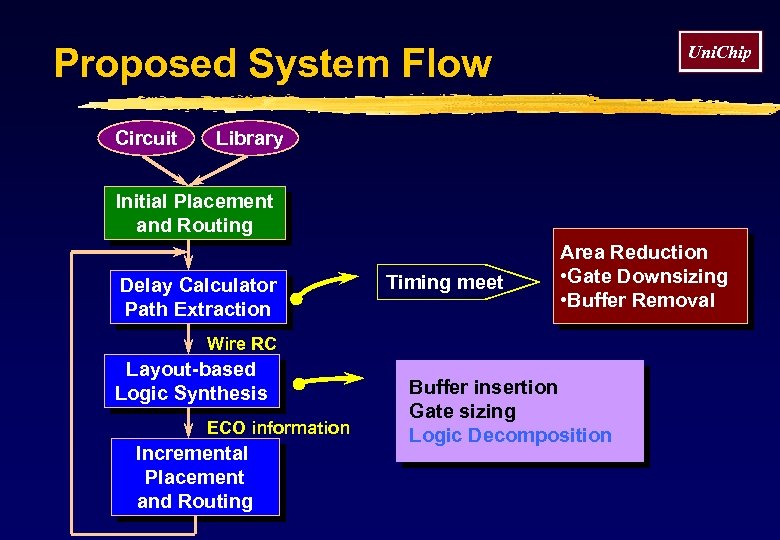

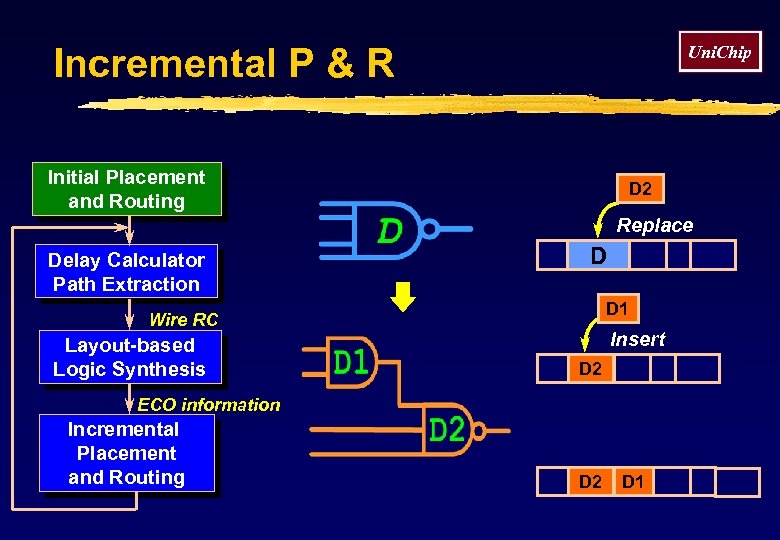

Proposed System Flow Circuit Uni. Chip Library Initial Placement and Routing Delay Calculator Path Extraction Timing meet Area Reduction • Gate Downsizing • Buffer Removal Wire RC Layout-based Logic Synthesis ECO information Incremental Placement and Routing Buffer insertion Gate sizing Logic Decomposition

Logic Decomposition z. Cell Selection z. Cell Substitute Generation z. Candidate Selection z. Cell Substitution Uni. Chip

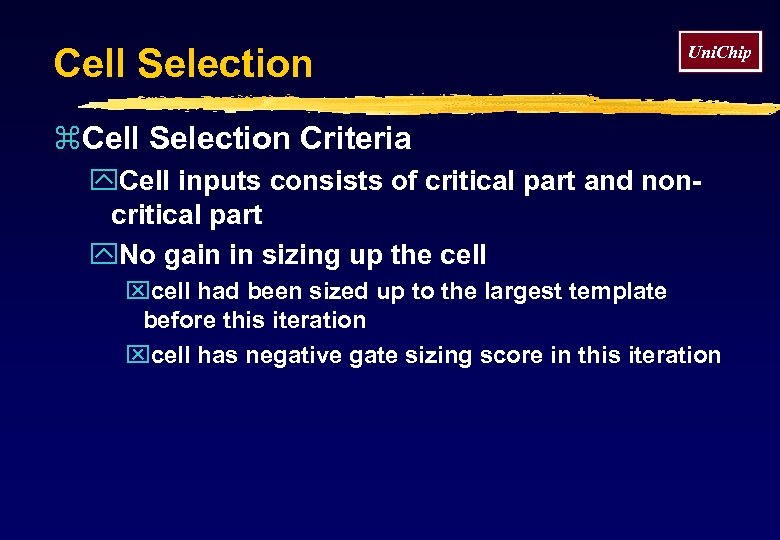

Cell Selection Uni. Chip z. Cell Selection Criteria y. Cell inputs consists of critical part and noncritical part y. No gain in sizing up the cell xcell had been sized up to the largest template before this iteration xcell has negative gate sizing score in this iteration

Cell Substitute Generation Uni. Chip ztwo-level substitutes y. For rule 1 . . .

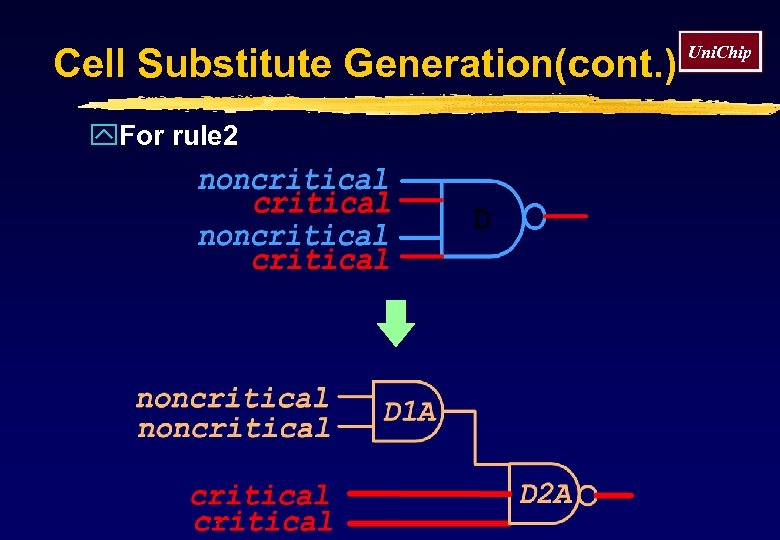

Cell Substitute Generation(cont. ) y. For rule 2 Uni. Chip

Candidate Selection Uni. Chip z. Criteria y. The longest path delaycandidate < The longest path delayoriginal y. The longest path delaycandidate is the smallest one among all substitutions

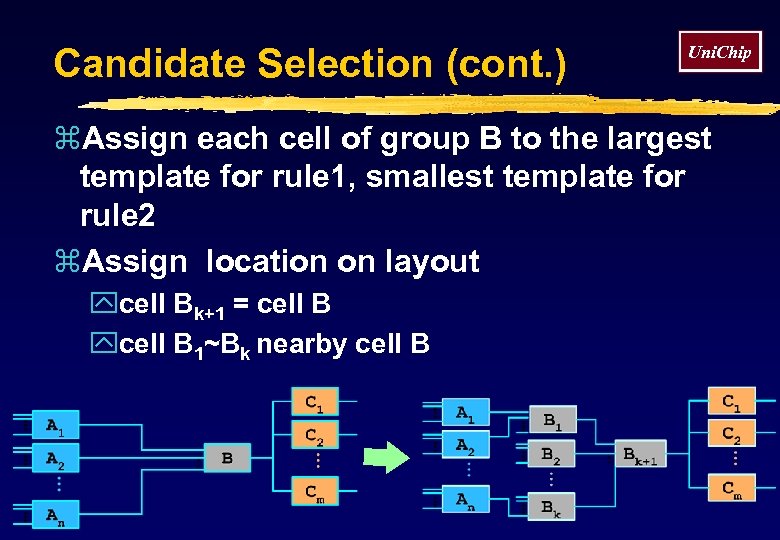

Candidate Selection (cont. ) Uni. Chip z. Assign each cell of group B to the largest template for rule 1, smallest template for rule 2 z. Assign location on layout ycell Bk+1 = cell B ycell B 1~Bk nearby cell B

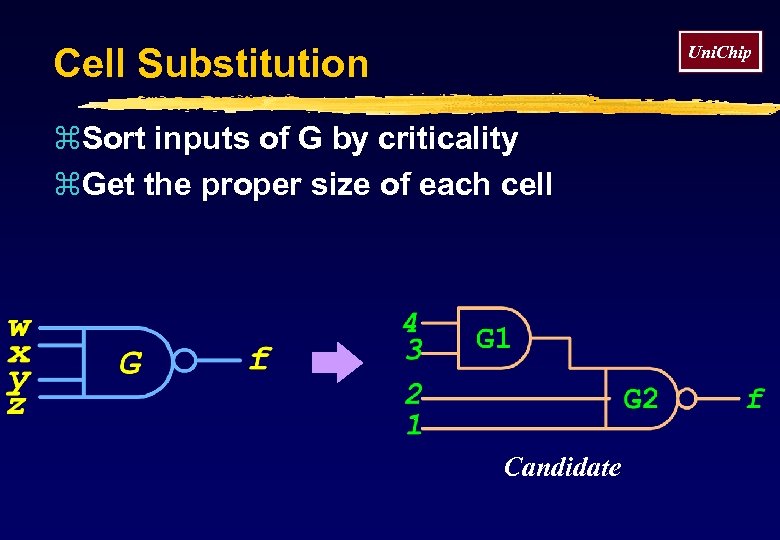

Cell Substitution Uni. Chip z. Sort inputs of G by criticality z. Get the proper size of each cell Candidate

Incremental P & R Uni. Chip Initial Placement and Routing D 2 Replace Delay Calculator Path Extraction D D 1 Wire RC Layout-based Logic Synthesis Insert D 2 ECO information Incremental Placement and Routing D 2 D 1

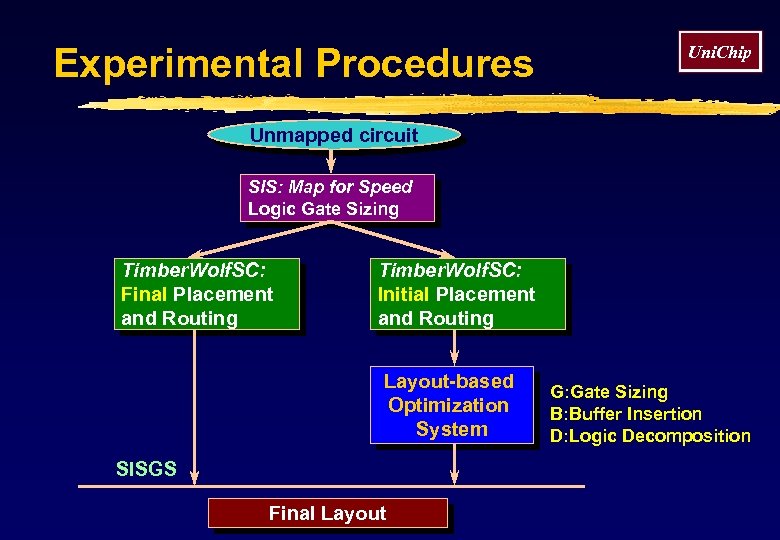

Experimental Procedures Uni. Chip Unmapped circuit SIS: Map for Speed Logic Gate Sizing Timber. Wolf. SC: Final Placement and Routing Timber. Wolf. SC: Initial Placement and Routing Layout-based Optimization System SISGS Final Layout G: Gate Sizing B: Buffer Insertion D: Logic Decomposition

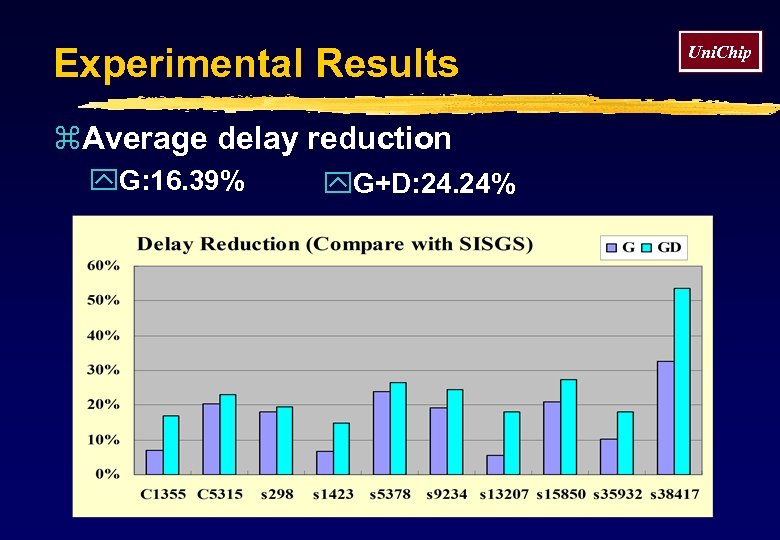

Experimental Results z. Average delay reduction y. G: 16. 39% y. G+D: 24. 24% Uni. Chip

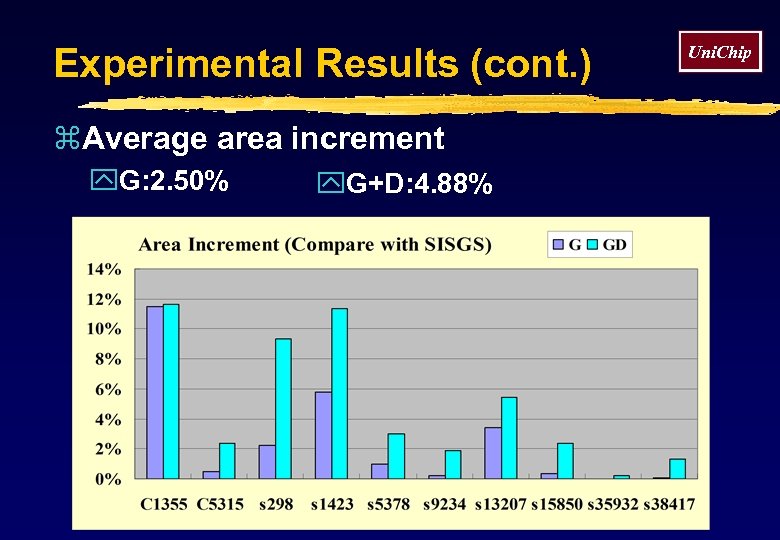

Experimental Results (cont. ) z. Average area increment y. G: 2. 50% y. G+D: 4. 88% Uni. Chip

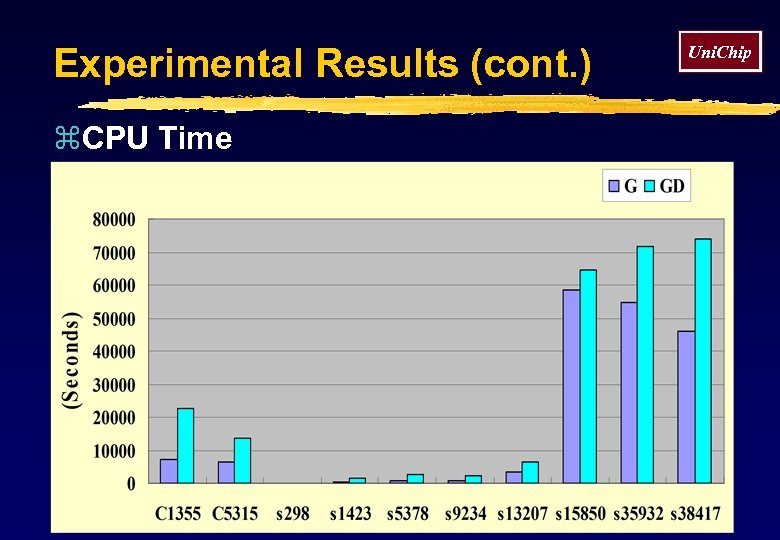

Experimental Results (cont. ) z. CPU Time Uni. Chip

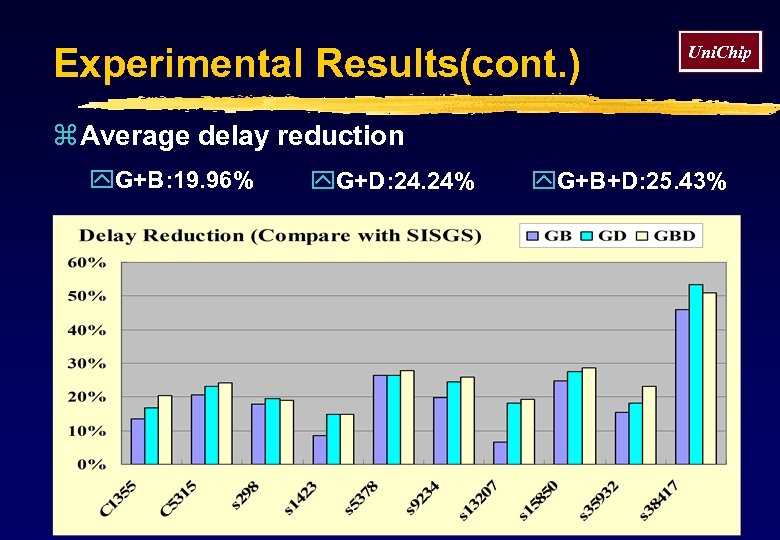

Experimental Results(cont. ) Uni. Chip z Average delay reduction y. G+B: 19. 96% y. G+D: 24. 24% y. G+B+D: 25. 43%

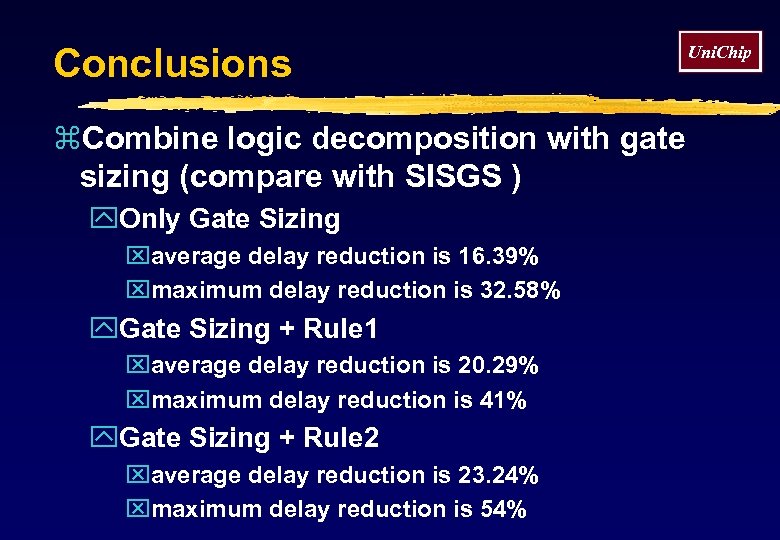

Conclusions z. Combine logic decomposition with gate sizing (compare with SISGS ) y. Only Gate Sizing xaverage delay reduction is 16. 39% xmaximum delay reduction is 32. 58% y. Gate Sizing + Rule 1 xaverage delay reduction is 20. 29% xmaximum delay reduction is 41% y. Gate Sizing + Rule 2 xaverage delay reduction is 23. 24% xmaximum delay reduction is 54% Uni. Chip

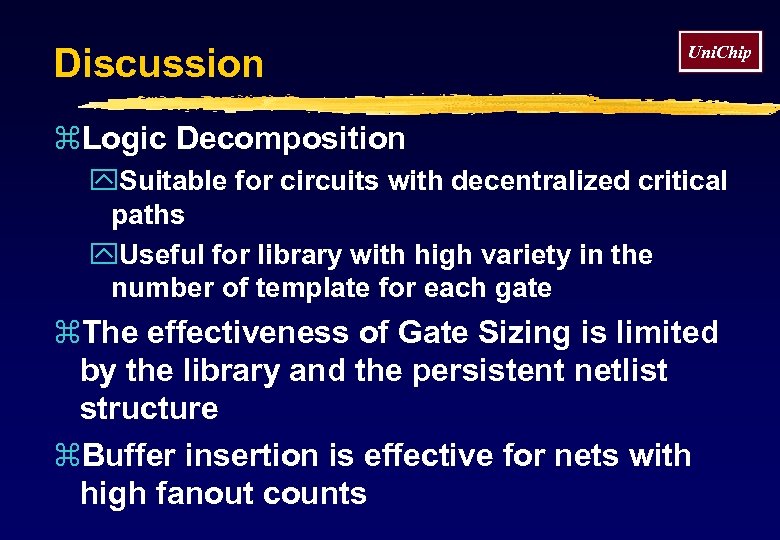

Discussion Uni. Chip z. Logic Decomposition y. Suitable for circuits with decentralized critical paths y. Useful for library with high variety in the number of template for each gate z. The effectiveness of Gate Sizing is limited by the library and the persistent netlist structure z. Buffer insertion is effective for nets with high fanout counts

Future Work z. Design a filter program which can analyze the input circuit first y. Find suitable optimized techniques y. Save program run time z. Interconnect-Centric Methodology Uni. Chip

3c489470922f9b942cd4e2bbc94cf23e.ppt