36466e1d752dbb12dcd7e74aced46976.ppt

- Количество слайдов: 9

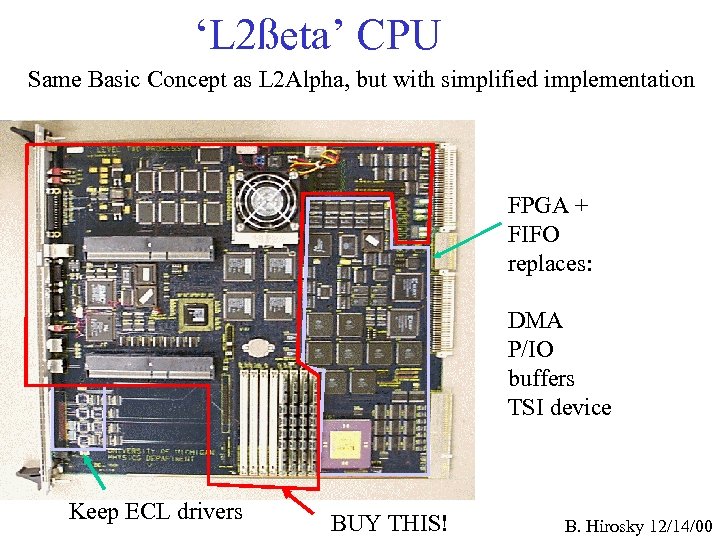

‘L 2ßeta’ CPU Same Basic Concept as L 2 Alpha, but with simplified implementation FPGA + FIFO replaces: DMA P/IO buffers TSI device Keep ECL drivers BUY THIS! B. Hirosky 12/14/00

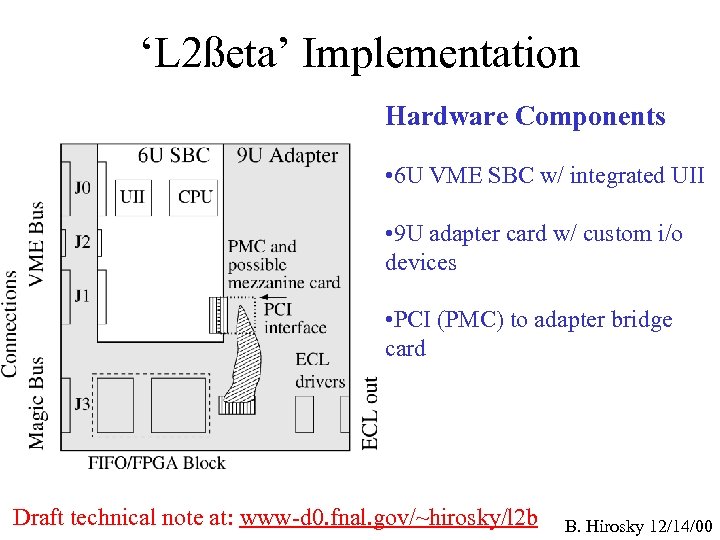

‘L 2ßeta’ Implementation Hardware Components • 6 U VME SBC w/ integrated UII • 9 U adapter card w/ custom i/o devices • PCI (PMC) to adapter bridge card Draft technical note at: www-d 0. fnal. gov/~hirosky/l 2 b B. Hirosky 12/14/00

Practical goals • Minimal engineering • Maximum use of manufactured components (hardware/firmware) • Hardware compatibility w/ present system • MBus/VME compliance • Software (source code) compatibility w/ present system • Device driver APIs • Short development time • Support/flush out L 2 if hardware set not complete • Long term solution to L 2 support • freedom from parts obsolescence for repair/spares • clear upgrade path to modern/powerful CPUs B. Hirosky 12/14/00

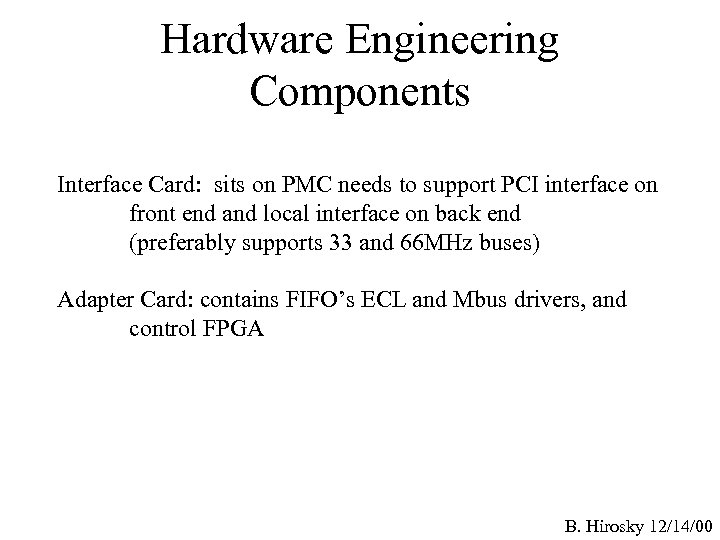

Hardware Engineering Components Interface Card: sits on PMC needs to support PCI interface on front end and local interface on back end (preferably supports 33 and 66 MHz buses) Adapter Card: contains FIFO’s ECL and Mbus drivers, and control FPGA B. Hirosky 12/14/00

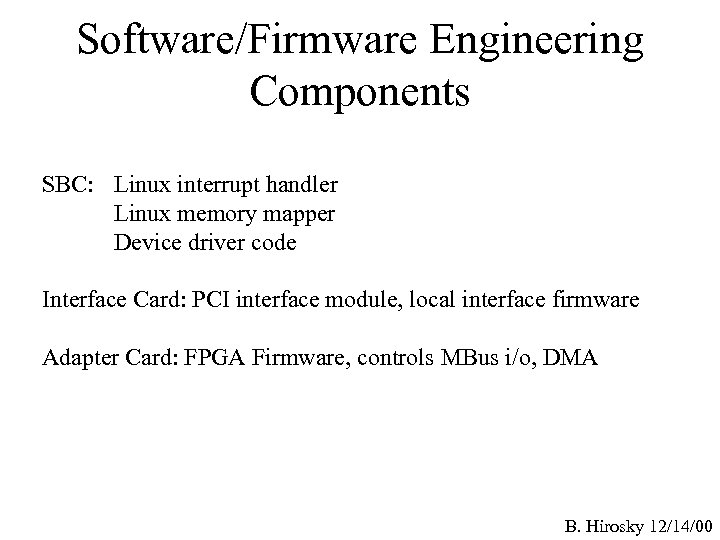

Software/Firmware Engineering Components SBC: Linux interrupt handler Linux memory mapper Device driver code Interface Card: PCI interface module, local interface firmware Adapter Card: FPGA Firmware, controls MBus i/o, DMA B. Hirosky 12/14/00

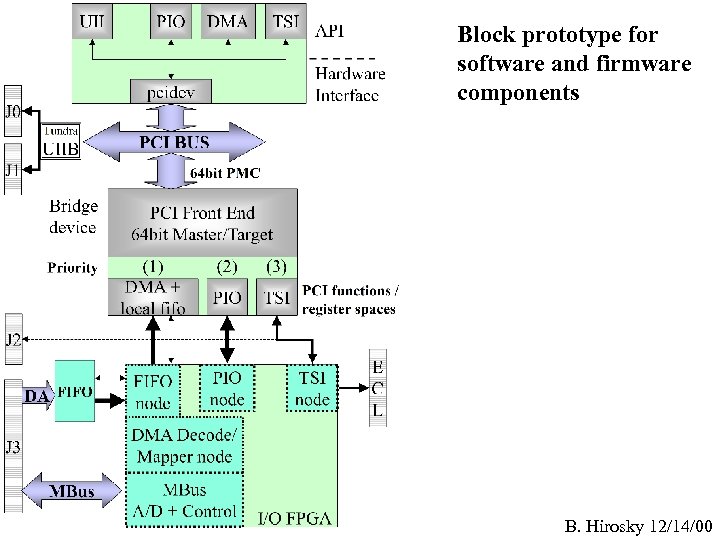

Block prototype for software and firmware components B. Hirosky 12/14/00

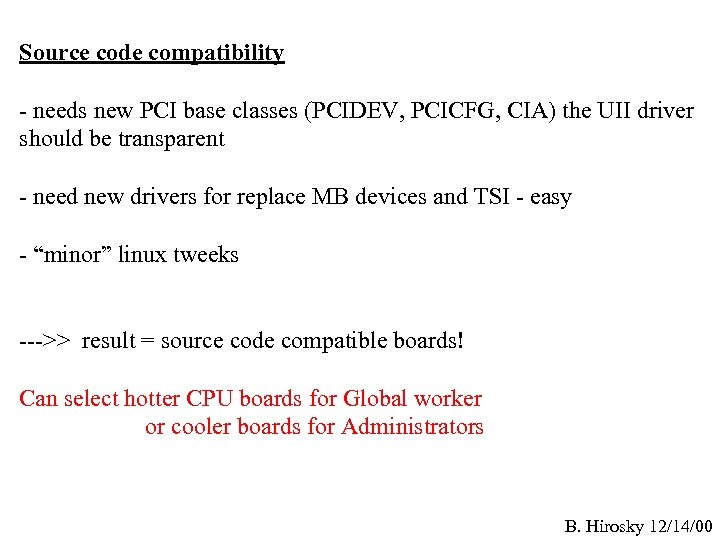

Source code compatibility - needs new PCI base classes (PCIDEV, PCICFG, CIA) the UII driver should be transparent - need new drivers for replace MB devices and TSI - easy - “minor” linux tweeks --->> result = source code compatible boards! Can select hotter CPU boards for Global worker or cooler boards for Administrators B. Hirosky 12/14/00

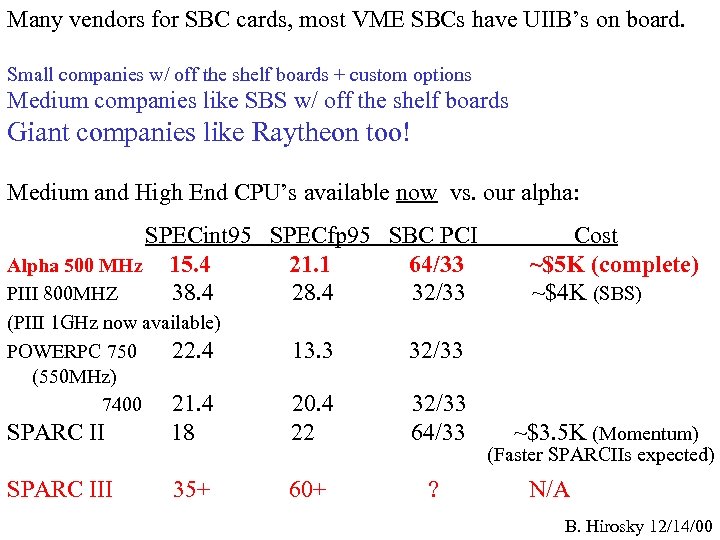

Many vendors for SBC cards, most VME SBCs have UIIB’s on board. Small companies w/ off the shelf boards + custom options Medium companies like SBS w/ off the shelf boards Giant companies like Raytheon too! Medium and High End CPU’s available now vs. our alpha: SPECint 95 SPECfp 95 SBC PCI Alpha 500 MHz 15. 4 21. 1 64/33 PIII 800 MHZ 38. 4 28. 4 32/33 (PIII 1 GHz now available) POWERPC 750 22. 4 (550 MHz) 7400 21. 4 13. 3 32/33 64/33 ? Cost ~$5 K (complete) ~$4 K (SBS) SPARC II 18 20. 4 22 SPARC III 35+ 60+ ~$3. 5 K (Momentum) (Faster SPARCIIs expected) N/A B. Hirosky 12/14/00

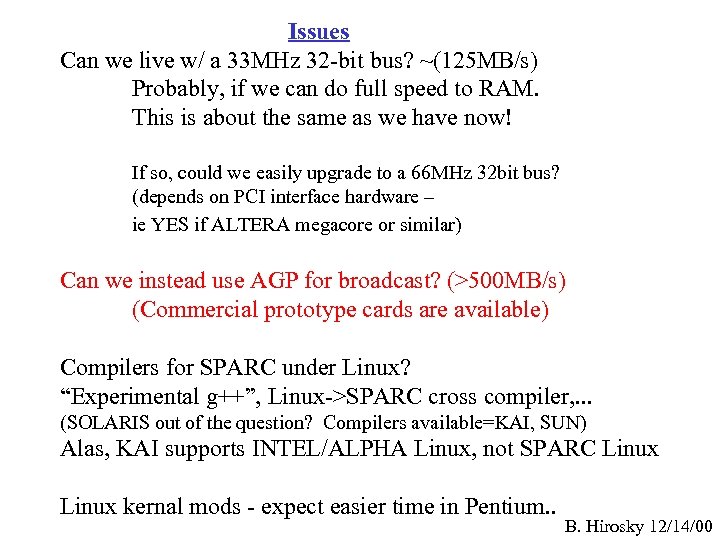

Issues Can we live w/ a 33 MHz 32 -bit bus? ~(125 MB/s) Probably, if we can do full speed to RAM. This is about the same as we have now! If so, could we easily upgrade to a 66 MHz 32 bit bus? (depends on PCI interface hardware – ie YES if ALTERA megacore or similar) Can we instead use AGP for broadcast? (>500 MB/s) (Commercial prototype cards are available) Compilers for SPARC under Linux? “Experimental g++”, Linux->SPARC cross compiler, . . . (SOLARIS out of the question? Compilers available=KAI, SUN) Alas, KAI supports INTEL/ALPHA Linux, not SPARC Linux kernal mods - expect easier time in Pentium. . B. Hirosky 12/14/00

36466e1d752dbb12dcd7e74aced46976.ppt