4aada30a60f6f2b60bf201c4971c9367.ppt

- Количество слайдов: 33

L 15 : Logic Level Design 성균관대학교 조 준 동 교수 http: //vlsicad. skku. ac. kr

Node Transition Activity

Low Activity XOR Function

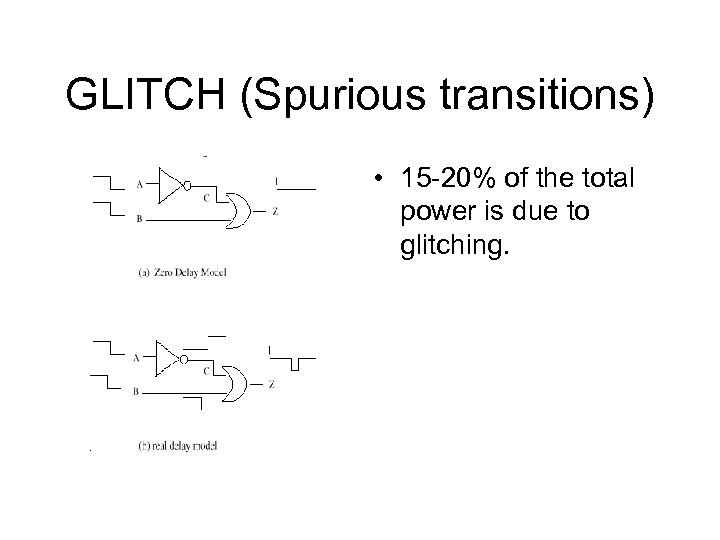

GLITCH (Spurious transitions) • 15 -20% of the total power is due to glitching.

Glitches

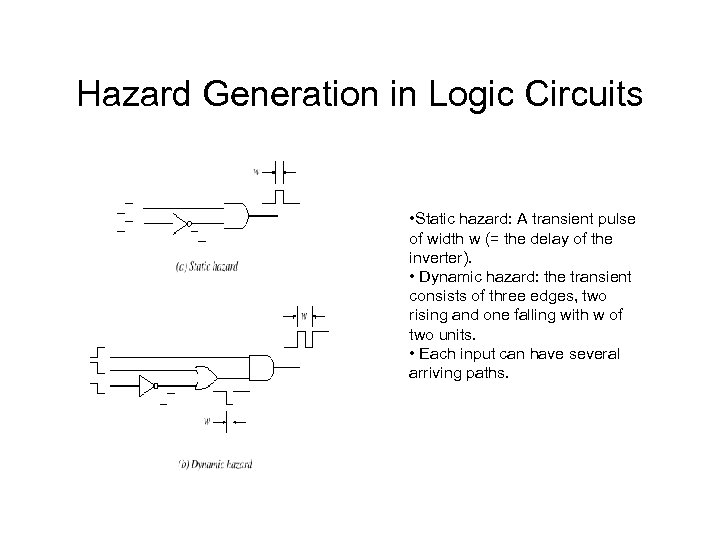

Hazard Generation in Logic Circuits • Static hazard: A transient pulse of width w (= the delay of the inverter). • Dynamic hazard: the transient consists of three edges, two rising and one falling with w of two units. • Each input can have several arriving paths.

High-Performance Power. Distribution • (S: Switching probability; C: Capacitance) • Start with all logic at the lowest power level; then, successive iterations of delay calculation, identifying the failing blocks, and powering • up are done until either all of the nets pass their delay criteria or the • maximum power level is reached. • Voltage drops in ground and supply wires use up a more serious fraction of the total noise margin

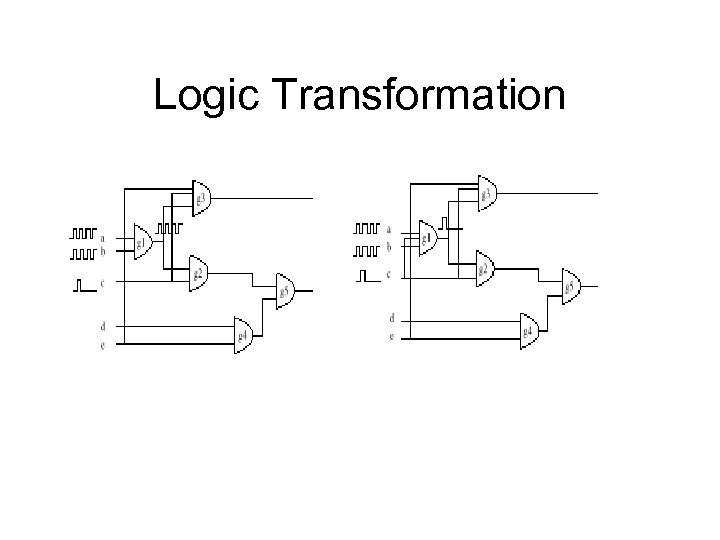

Logic Transformation • • Use a signal with low switching activity to reduce the activity on a highly active signal. Done by the addition of a redundant connection between the gate with low activity (source gate) to the gate with a high switching activity (target gate). Signals a, b, and g 1 have very high switching activity and most of time its value is zero Suppose c and g 1 are selected as the source and target of a new connection ` 1 is undetectable, hence the function of the new circuit remains the same. Signal c has a long run of zero, and zero is the controlling value of the and gate g 1 , most of the switching activities at the input of g 1 will not be seen at the output, thus switching activity of the gate g 1 is reduced. The redundant connection in a circuit may result in some irredundant connections becoming redundant. By adding ` 1 , the connections from c to g 3 become redundant.

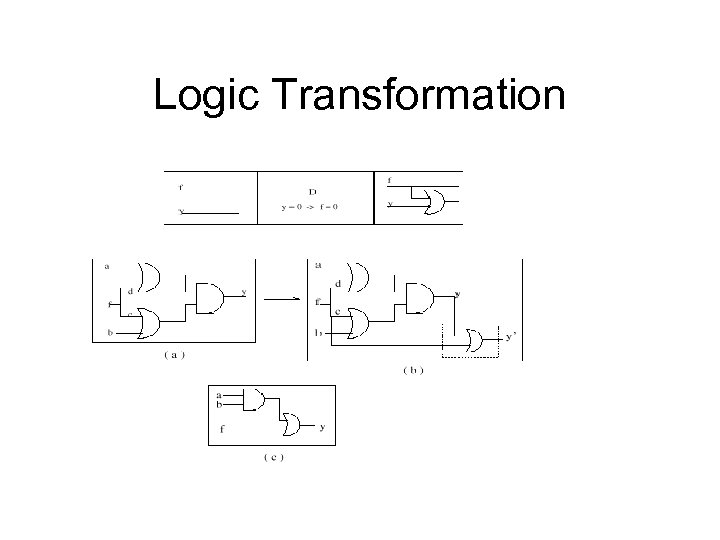

Logic Transformation

Logic Transformation

Frequency Reduction ◈ Power saving 4 Reduces capacitance on the clock network 4 Reduces internal power in the affected registers 4 Reduces need for muxes(data recirculation) ◈ Opportunity 4 Large opportunity for power reduction, dependent on; · Number of registers gated · percentage of time clock is enabled ◈ Cost 4 Testability 4 Complicates clock tree synthesis 4 Complicates clock skew balancing

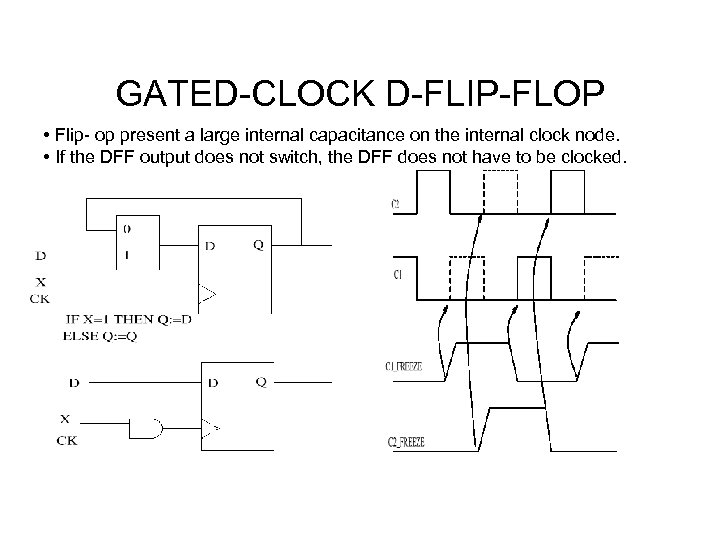

GATED-CLOCK D-FLIP-FLOP • Flip- op present a large internal capacitance on the internal clock node. • If the DFF output does not switch, the DFF does not have to be clocked.

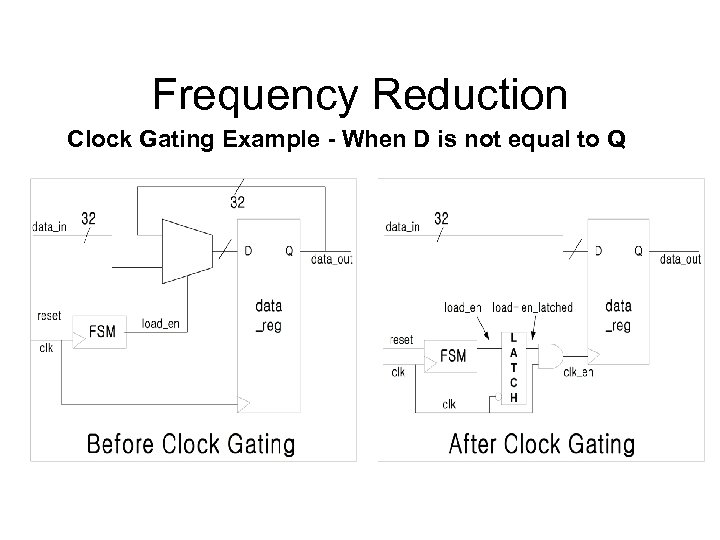

Frequency Reduction Clock Gating Example - When D is not equal to Q

Frequency Reduction ◈ Clock Gating Example - Before Code library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_unsigned. all; entity nongate is port(clk, rst : in std_logic; data_in : in std_logic_vector(31 downto 0); data_out : out std_logic_vector(31 downto 0)); end nongate; architecture behave of nongate is signal load_en : std_logic; signal data_reg : std_logic_vector(31 downto 0); signal count : integer range 0 to 15; begin FSM : process begin wait until clk'event and clk='1'; if rst='0' then count <= 0; elsif count=9 then count <= 0; else count <= count+1; end if; end process FSM; enable_logic : process(count, load_en) begin if(count=9) then load_en <= '1'; else load_en <= '0'; end if; end process enable_logic; datapath : process begin wait until clk'event and clk='1'; if load_en='1' then data_reg <= data_in; end if; end process datapath; data_out <= data_reg; end behave; configuration cfg_nongate of nongate is for behave end for; end cfg_nongate;

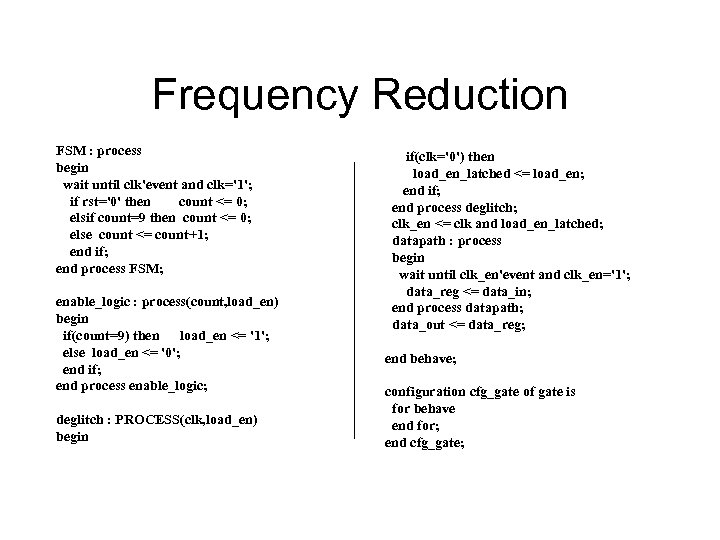

Frequency Reduction ◈ Clock Gating Example - After Code library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_unsigned. all; entity gate is port(clk, rst : in std_logic; data_in : in std_logic_vector(31 downto 0); data_out : out std_logic_vector(31 downto 0)); end gate; architecture behave of gate is signal load_en, load_en_latched, clk_en : std_logic; signal data_reg : std_logic_vector(31 downto 0); signal count : integer range 0 to 15; begin

Frequency Reduction FSM : process begin wait until clk'event and clk='1'; if rst='0' then count <= 0; elsif count=9 then count <= 0; else count <= count+1; end if; end process FSM; enable_logic : process(count, load_en) begin if(count=9) then load_en <= '1'; else load_en <= '0'; end if; end process enable_logic; deglitch : PROCESS(clk, load_en) begin if(clk='0') then load_en_latched <= load_en; end if; end process deglitch; clk_en <= clk and load_en_latched; datapath : process begin wait until clk_en'event and clk_en='1'; data_reg <= data_in; end process datapath; data_out <= data_reg; end behave; configuration cfg_gate of gate is for behave end for; end cfg_gate;

Frequency Reduction ◈ Clock Gating Example - Report

Frequency Reduction ◈ 4 -bit Synchronous & Ripple counter - code 4 -bit Synchronous Counter Library IEEE; use IEEE. std_logic_1164. all; use IEEE. std_logic_arith. all; entity BINARY is Port ( clk : In std_logic; reset : In std_logic; count : BUFFER UNSIGNED (3 downto 0)); end BINARY; architecture BEHAVIORAL of BINARY is begin process(reset, clk, count) begin if (reset = '0') then count <= "0000” elsif (clk'event and clk = '1') then if (count = UNSIGNED'("1111")) then count <= "0000"; else count <=count+UNSIGNED'("1"); end if; end process; end BEHAVIORAL; configuration CFG_BINARY_BLOCK_BEHAVIORAL of BINARY is for BEHAVIORAL end for; end CFG_BINARY_BLOCK_BEHAVIORAL;

Frequency Reduction 4 -bit Ripple Counter Library IEEE; use IEEE. std_logic_1164. all; use IEEE. std_logic_arith. all; entity RIPPLE is Port ( clk : In std_logic; reset : In std_logic; count : BUFFER UNSIGNED (3 downto 0)); end RIPPLE; architecture BEHAVIORAL of RIPPLE is signal count 0, count 1, count 2 : std_logic; begin process(count) begin count 0 <= count(0); count 1 <= count(1); count 2 <= count(2); end process; process(reset, clk) begin if (reset = '0') then count(0) <= '0'; elsif (clk'event and clk = '1') then if (count(0) = '1') then count(0) <= '0'; else count(0) <= '1'; end if; end process; process(reset, count 0) begin if (reset = '0') then count(1) <= '0'; elsif (count 0'event and count 0 = '1') then

Frequency Reduction if (count(1) = '1') then count(1) <= '0'; else count(1) <= '1'; end if; end process; process(reset, count 1) begin if (reset = '0') then count(2) <= '0'; elsif (count 1'event and count 1 = '1') then if (count(2) = '1') then count(2) <= '0'; else count(2) <= '1'; end if; end process; process(reset, count 2) begin if (reset = '0') then count(3) <= '0'; elsif (count 2'event and count 2 = '1') then if (count(3) = '1') then count(3) <= '0'; else count(3) <= '1'; end if; end process; end BEHAVIORAL; configuration CFG_RIPPLE_BLOCK_BEHAVIORAL of RIPPLE is for BEHAVIORAL end for; end CFG_RIPPLE_BLOCK_BEHAVIORAL;

Frequency Reduction ◈ 4 -bit Synchronous & Ripple counter - Report

![References [1] H. B. Bakoglu, Circuits, Interconnections and Packaging for VLSI, Addison-Wesley, 1990. [2] References [1] H. B. Bakoglu, Circuits, Interconnections and Packaging for VLSI, Addison-Wesley, 1990. [2]](https://present5.com/presentation/4aada30a60f6f2b60bf201c4971c9367/image-22.jpg)

References [1] H. B. Bakoglu, Circuits, Interconnections and Packaging for VLSI, Addison-Wesley, 1990. [2] T. K. Callaway, E. E. Swartzlander, Estimating the Power Consumption of CMOS Adders", 11 th Symp. on Comp. Arithmetic, pp. 210 -216, Windsor, Ontario, 1993. [3] A. P. Chandrakasan, S. Sheng, R. W. Brodersen, Low-Power CMOS Digital Design", IEEE Journal of Solid-State Circuits, pp. 473 -484, April 1992. [4] A. P. Chandrakasan, M. Potkonjak, J. Rabaey, R. W. Brodersen, HYPER-LP: A System for Power Minimization Using Architectural Transformations", ICCAD-92, pp. 300 -303, Nov. 1992, Santa Clara, CA. [5] A. P. Chandrakasan, M. Potkonjak, J. Rabaey, R. W. Brodersen, An Approach to Power Minimization Using Transformations", IEEE VLSI for Signal Processing Workshop, pp. , 1992, CA. [6] S. Devadas, K. Keutzer, J. White, Estimation of Power Dissipation in CMOS Combinational Circuits", IEEE Custom Integrated Circuits Conference, pp. 19. 7. 1 -19. 7. 6, 1990. [7] D. Dobberpuhl et al. A 200 -MHz 64 -bit Dual-Issue CMOS Microprocessor", IEEE Journal of Solid-State Circuits, pp. 15551567, Nov. 1992. [8] R. J. Fletcher, Integrated Circuit Having Outputs Congured for Reduced State Changes", U. S. Patent no. 4, 667, 337, May, 1987. [9] D. Gajski, N. Dutt, A. Wu, S. Lin, High-Level Synthesis, Introduction to Chip and System Design, Kluwer Academic Publishers, 1992. [10] J. S. Gardner, Designing with the IDT Sync. FIFO: the Architecture of the Future", 1992 Synchronous (Clocked) FIFO Design Guide, Integrated Device Technology AN-60, pp. 7 -10, 1992, Santa Clara, CA. [11] A. Ghosh, S. Devadas, K. Keutzer, J. White, Estimation of Average Switching Activity in Combinational and Sequential Circuits", Proceedings of the 29 th DAC, pp. 253 -259, June 1992, Anaheim, CA. [12] J. L. Hennessy, D. A. Patterson, Computer Architecture - A Quantitative Approach, Morgan Kaufmann Publishers, Palo Alto, CA, 1990. [13] S. Kodical, Simultaneous Switching Noise", 1993 IDT High-Speed CMOS Logic Design Guide, Integrated Device Technology AN-47, pp. 41 -47, 1993, Santa Clara, CA. [14] F. Najm, Transition Density, A Stochastic Measure of Activity in Digital Circuits", Proceedings of the 28 th DAC, pp. 644 -649, June 1991, Anaheim, CA.

![References [16] A. Park, R. Maeder, Codes to Reduce Switching Transients Across VLSI I/O References [16] A. Park, R. Maeder, Codes to Reduce Switching Transients Across VLSI I/O](https://present5.com/presentation/4aada30a60f6f2b60bf201c4971c9367/image-23.jpg)

References [16] A. Park, R. Maeder, Codes to Reduce Switching Transients Across VLSI I/O Pins", Computer Architecture News, pp. 17 -21, Sept. 1992. [17] Rambus - Architectural Overview, Rambus Inc. , Mountain View, CA, 1993. Contact ray@rambus. com. [18] A. Shen, A. Ghosh, S. Devadas, K. Keutzer, On Average Power Dissipation and Random Pattern Testability", ICCAD-92, pp. 402 -407, Nov. 1992, Santa Clara, CA. [19] M. R. Stan, Shift register generators for circular FIFOs", Electronic Engineering, pp. 26 -27, February 1991, Morgan Grampian House, London, England. [20] M. R. Stan, W. P. Burleson, Limited-weight codes for low power I/O", International Workshop on Low Power Design, April 1994, Napa, CA. [21] J. Tabor, Noise Reduction Using Low Weight and Constant Weight Coding Techniques, Master's Thesis, EECS Dept. , MIT, May 1990. [22] W. -C. Tan, T. H. -Y. Meng, Low-power polygon renderer for computer graphics", Int. Conf. on A. S. A. P. , pp. 200 -213, 1993. [23] N. Weste, K. Eshraghian, Principles of CMOS VLSI Design, A Systems Perspective, Addison. Wesley Publishing Company, 1988. [24] R. Wilson, Low power and paradox", Electronic Engineering Times, pp. 38, November 1, 1993. [25] J. Ziv, A. Lempel, A universal Algorithm for Sequential Data Compression", IEEE Trans. on Inf. Theory, vol. IT-23, pp. 337 -343, 1977.

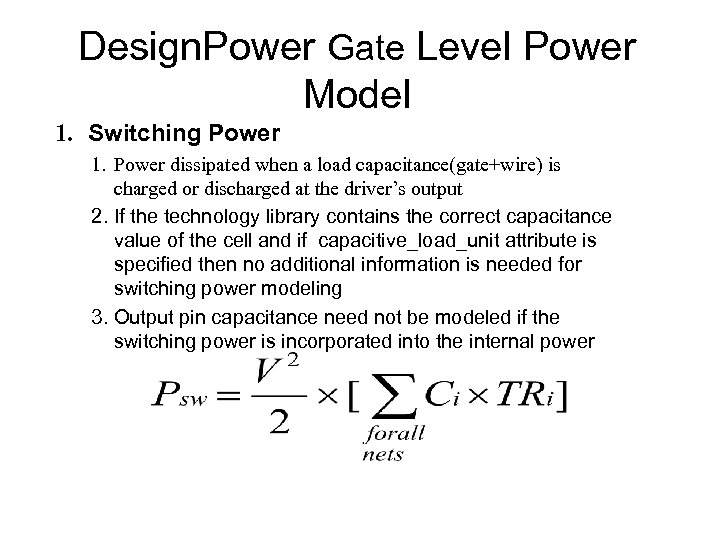

Design. Power Gate Level Power Model 1. Switching Power 1. Power dissipated when a load capacitance(gate+wire) is charged or discharged at the driver’s output 2. If the technology library contains the correct capacitance value of the cell and if capacitive_load_unit attribute is specified then no additional information is needed for switching power modeling 3. Output pin capacitance need not be modeled if the switching power is incorporated into the internal power

Design. Power Gate Level Power Model ◈ Internal Power 4 power dissipated internal to a library cell 4 Modeled using energy lookup table indexed by input transition time and output load 4 Library cells may contain one or more internal energy lookup tables

Design. Power Gate Level Power Model ◈ Leakage Power 4 Leakage power model supports a signal value for each library cell 4 State dependent leakage power is not supported

Operand Isolation • Combinational logic dissipates significant power when output is unused • Inputs to combination logic held stable when output is unused

Operation Isolation Example -Diagram Before Operand Isolation After Operand Isolation

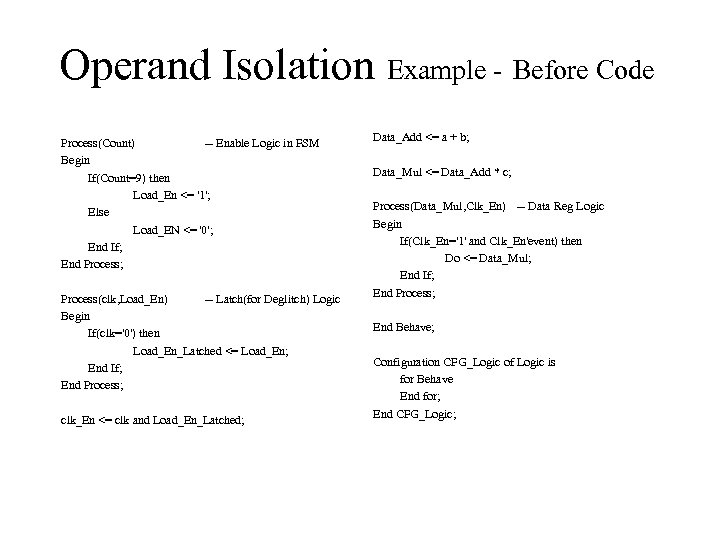

Operand Isolation Example - Before Code Library IEEE; Use IEEE. STD_LOGIC_1164. ALL; Use IEEE. STD_LOGIC_SIGNED. ALL; Signal Data_Add : std_logic_vector(7 downto 0); Signal Data_Mul : std_logic_vector(15 downto 0); Begin Entity Logic is Port( a, b, c : in std_logic_vector(7 downto 0); do : out std_logic_vector(15 downto 0); rst : in std_logic; clk : in std_logic ); End Logic; Process(clk, rst) Architecture Behave of Logic is Signal Count : integer; Signal Load_En : std_logic; Signal Load_En_Latched : std_logic; Signal Clk_En : std_logic; -- Counter Logic in FSM Begin If(clk='1' and clk'event) then If(rst='0') then Count <= 0; Elsif(Count=9) then Count <= 0; Else Count <= Count + 1; End If; End Process;

Operand Isolation Example - Before Code Process(Count) -- Enable Logic in FSM Begin If(Count=9) then Load_En <= '1'; Else Load_EN <= '0'; End If; End Process; Process(clk, Load_En) -- Latch(for Deglitch) Logic Begin If(clk='0') then Load_En_Latched <= Load_En; End If; End Process; clk_En <= clk and Load_En_Latched; Data_Add <= a + b; Data_Mul <= Data_Add * c; Process(Data_Mul, Clk_En) -- Data Reg Logic Begin If(Clk_En='1' and Clk_En'event) then Do <= Data_Mul; End If; End Process; End Behave; Configuration CFG_Logic of Logic is for Behave End for; End CFG_Logic;

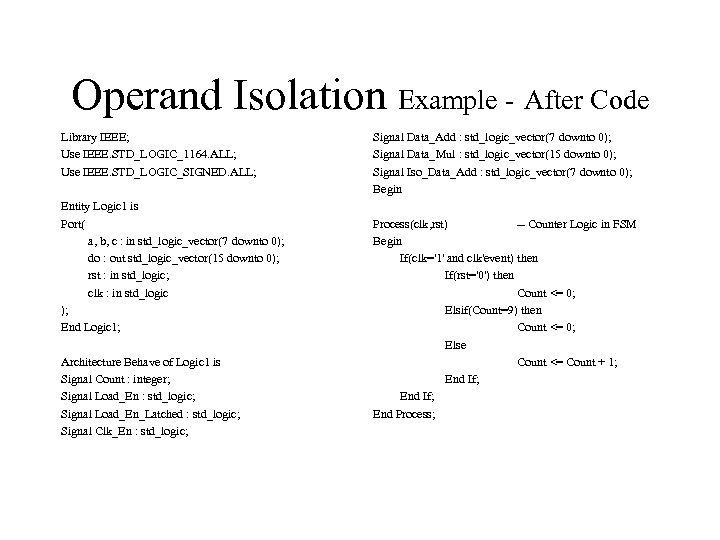

Operand Isolation Example - After Code Library IEEE; Use IEEE. STD_LOGIC_1164. ALL; Use IEEE. STD_LOGIC_SIGNED. ALL; Entity Logic 1 is Port( a, b, c : in std_logic_vector(7 downto 0); do : out std_logic_vector(15 downto 0); rst : in std_logic; clk : in std_logic ); End Logic 1; Architecture Behave of Logic 1 is Signal Count : integer; Signal Load_En : std_logic; Signal Load_En_Latched : std_logic; Signal Clk_En : std_logic; Signal Data_Add : std_logic_vector(7 downto 0); Signal Data_Mul : std_logic_vector(15 downto 0); Signal Iso_Data_Add : std_logic_vector(7 downto 0); Begin Process(clk, rst) -- Counter Logic in FSM Begin If(clk='1' and clk'event) then If(rst='0') then Count <= 0; Elsif(Count=9) then Count <= 0; Else Count <= Count + 1; End If; End Process;

Operand Isolation Example - After Code Process(Count) -- Enable Logic in FSM Begin If(Count=9) then Load_En <= '1'; Else Load_EN <= '0'; End If; End Process; Process(clk, Load_En) -- Latch(for Deglitch) Logic Begin If(clk='0') then Load_En_Latched <= Load_En; End If; End Process; clk_En <= clk and Load_En_Latched; Data_Add <= a + b; Process(Load_En_Latched, Data_Add) -- Latch Begin -- for Operand Isolation If(Load_En_Latched='1' and Load_En_Latched'event) then Iso_Data_Add <= Data_Add; End If; End Process; Data_Mul <= Iso_Data_Add * c; Process(Data_Mul, Clk_En) -- Data Reg Logic Begin If(Clk_En='1' and Clk_En'event) then Do <= Data_Mul; End If; End Process; End Behave;

Operand Isolation Example - Report Before Code After Code

4aada30a60f6f2b60bf201c4971c9367.ppt