SCH-T-2.ppt

- Количество слайдов: 41

Компьютерная Схемотехника 2012 ЭЛЕКТРОННЫЙ КЛЮЧ НА БИПОЛЯРНОМ ТРАНЗИСТОРЕ АЛГЕБРА ЛОГИКИ ПРИ АНАЛИЗЕ И СИНТЕЗЕ ЛОГИЧЕСКИХ СХЕМ БАЗОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТТЛ ХНУРЭ, факультет КИУ, каф ЭВМ, Тел. 70 -21 -354. Доц. Торба А. А.

Компьютерная Схемотехника 2012 ОСНОВНЫЕ ТЕМЫ ЛЕКЦИИ • ЭЛЕКТРОННЫЙ КЛЮЧ НА БИПОЛЯРНОМ ТРАНЗИСТОРЕ • АЛГЕБРА ЛОГИКИ ПРИ АНАЛИЗЕ И СИНТЕЗЕ ЛОГИЧЕСКИХ СХЕМ • ФУНКЦИОНАЛЬНО ПОЛНАЯ СИСТЕМА ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ • БАЗОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ - ТТЛ • ОСОБЕННОСТИ СХЕМОТЕХНИКИ ЭЛЕМЕНТОВ ТТЛ • ПОВЫШЕНИЕ БЫСТРОДЕЙСТВИЯ ЭЛЕМЕНТОВ ТТЛ

ЭЛЕКТРОННЫЙ КЛЮЧ НА БИПОЛЯРНОМ ТРАНЗИСТОРЕ Основным элементом вычислительных машин является ЭЛЕКТРОННЫЙ КЛЮЧ, имеющий два устойчивых состояния: «включен» - «выключен» ; или «высокий уровень» - «низкий уровень» . Условимся называть «низкий уровень» - ЛОГИЧЕСКИМ НУЛЕМ, а «высокий уровень» - ЛОГИЧЕСКОЙ ЕДИНИЦЕЙ. ЭЛЕКТРОННЫЙ КЛЮЧ может быть реализован на активных элементах: биполярных или полевых транзисторах, на туннельных диодах, на тиристорах и др. В интегральной схемотехнике наиболее широко используется электронный ключ на БИПОЛЯРНОМ ТРАНЗИСТОРЕ

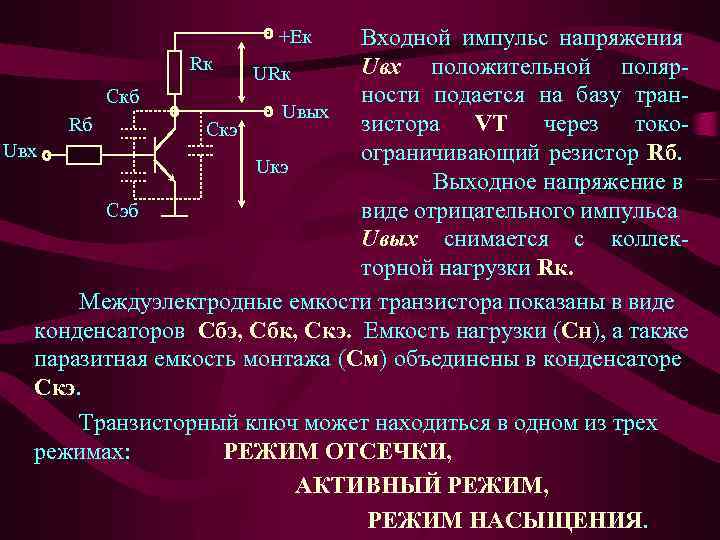

Входной импульс напряжения Rк Uвх положительной поляр. URк ности подается на базу тран. Скб Uвых Rб зистора VT через токо. Скэ Uвх ограничивающий резистор Rб. Uкэ Выходное напряжение в Сэб виде отрицательного импульса Uвых снимается с коллекторной нагрузки Rк. Междуэлектродные емкости транзистора показаны в виде конденсаторов Сбэ, Сбк, Скэ. Емкость нагрузки (Сн), а также паразитная емкость монтажа (См) объединены в конденсаторе Скэ. Транзисторный ключ может находиться в одном из трех режимах: РЕЖИМ ОТСЕЧКИ, АКТИВНЫЙ РЕЖИМ, РЕЖИМ НАСЫЩЕНИЯ. +Ек

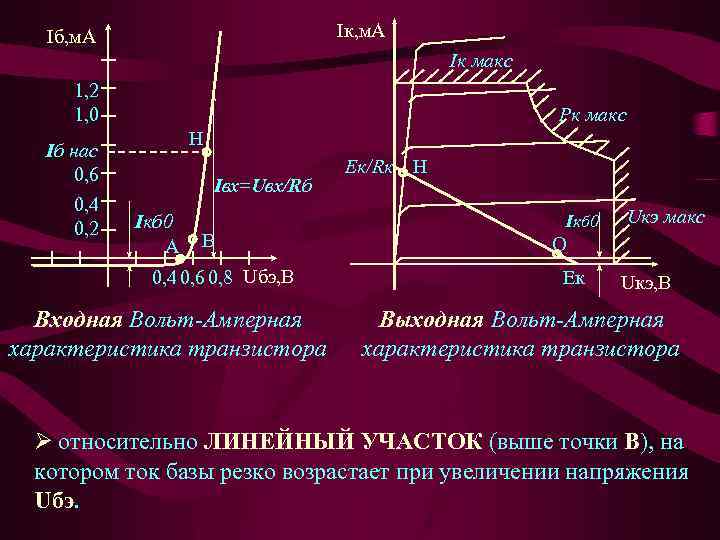

В РЕЖИМЕ ОТСЕЧКИ оба перехода транзистора (базаэмиттер и база-коллектор) находятся в закрытом (не токопроводящем) состоянии. В АКТИВНОМ РЕЖИМЕ переход база-эмиттер открыт, а переход база-коллектор - закрыт. В РЕЖИМЕ НАСЫЩЕНИЯ - оба перехода открыты. Очень редко в некоторых схемах используется ИНВЕРСНЫЙ РЕЖИМ, при котором переход база-эмиттер закрыт, а переход база-коллектор открыт. На входной Вольт-Амперной характеристике (ВАХ) кремниевого биполярного транзистора выделим три области : • Ø левее точки А - ОБЛАСТЬ ОТСЕЧКИ; через переход базаэмиттер протекает очень маленький (доли микро. Ампер) тепловой ток неосновных носителей Iкб 0; • Ø нелинейный участок между точками А и В – КВАДРА ТИЧНЫЙ УЧАСТОК (в некоторых книгах он называется - ЭКСПОНЕНЦИАЛЬНЫЙ УЧАСТОК);

Iк, м. А Iб, м. А Iк макс 1, 2 1, 0 Iб нас 0, 6 0, 4 0, 2 Рк макс Н Iвх=Uвх/Rб Iкб 0 А В 0, 4 0, 6 0, 8 Uбэ, В Входная Вольт-Амперная характеристика транзистора Ек/Rк Н Iкб 0 Uкэ макс О Ек Uкэ, В Выходная Вольт-Амперная характеристика транзистора Ø относительно ЛИНЕЙНЫЙ УЧАСТОК (выше точки В), на котором ток базы резко возрастает при увеличении напряжения Uбэ.

На выходной Вольт-Амперной характеристике (ВАХ) выделим РАБОЧУЮ ОБЛАСТЬ, ограниченную: Ø сверху - максимальным током коллектора (Iкмакс); Ø справа - максимально допустимым напряжением коллектор-эмиттер (Uкэмакс); Ø а также ограниченную гиперболой максимально допустимой мощности рассеивания (Рк макс). В пределах РАБОЧЕЙ ОБЛАСТИ строим НАГРУЗОЧНУЮ ПРЯМУЮ, проходящую через две точки: · на горизонтальной оси через точку Uкэ = Ек; · на вертикальной оси через точку Iк = Ек / Rк. На этой прямой выделим точку режима отсечки «О» и точку режима насыщения «Н» . Между точками «О» и «Н» находится участок АКТИВНОГО РЕЖИМА работы транзистора.

Методы повышения быстродействия электронного ключа 1. Повышение быстродействия ключевых схем достигается уменьшением времени перезаряда конденсаторов Сбэ, Сбк, Скэ и Сн за счет увеличения токов в схеме, т. е. за счет уменьшения номиналов резисторов Rк и Rб. Такое увеличение быстродействия ключевых схем сопровождается пропорциональным УВЕЛИЧЕНИЕМ ПОТРЕБЛЯЕМОЙ МОЩНОСТИ. 2. В современных цифровых схемах значительно уменьшены номиналы конденсаторов Сбэ, Сбк, Скэ и Сн за счет уменьшения размеров интегральных транзисторов, что также позволяет повысить быстродействие интегральных схем. 3. Для повышения быстродействия ключевых схем желательно не доводить транзистор ДО НАСЫЩЕНИЯ, при этом время рассасывания будет равно нулю.

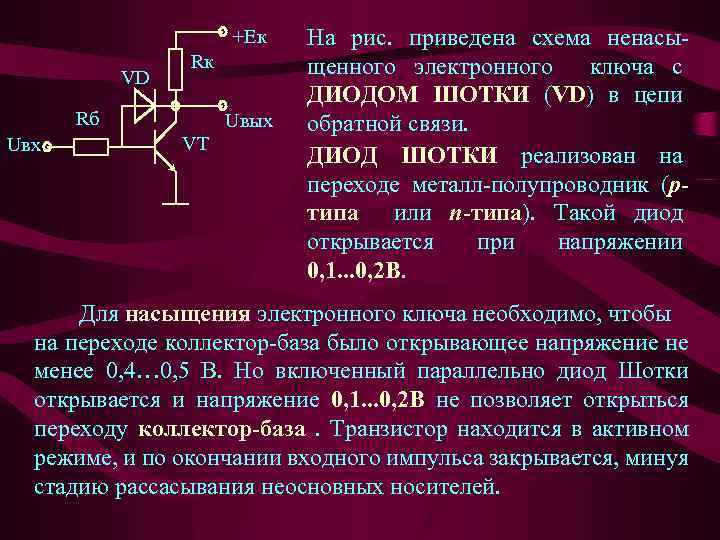

+Ек VD Rк Rб Uвх Uвых VT На рис. приведена схема ненасыщенного электронного ключа с ДИОДОМ ШОТКИ (VD) в цепи обратной связи. ДИОД ШОТКИ реализован на переходе металл-полупроводник (pтипа или n-типа). Такой диод открывается при напряжении 0, 1. . . 0, 2 В. Для насыщения электронного ключа необходимо, чтобы на переходе коллектор-база было открывающее напряжение не менее 0, 4… 0, 5 В. Но включенный параллельно диод Шотки открывается и напряжение 0, 1. . . 0, 2 В не позволяет открыться переходу коллектор-база . Транзистор находится в активном режиме, и по окончании входного импульса закрывается, минуя стадию рассасывания неосновных носителей.

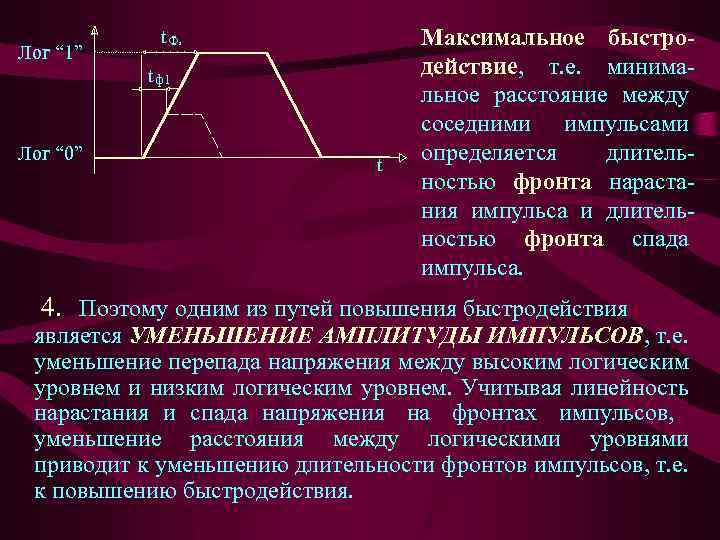

Лог “ 1” t. Ф 2 t ф1 Лог “ 0” t Максимальное быстродействие, т. е. минимальное расстояние между соседними импульсами определяется длительностью фронта нарастания импульса и длительностью фронта спада импульса. 4. Поэтому одним из путей повышения быстродействия является УМЕНЬШЕНИЕ АМПЛИТУДЫ ИМПУЛЬСОВ, т. е. уменьшение перепада напряжения между высоким логическим уровнем и низким логическим уровнем. Учитывая линейность нарастания и спада напряжения на фронтах импульсов, уменьшение расстояния между логическими уровнями приводит к уменьшению длительности фронтов импульсов, т. е. к повышению быстродействия.

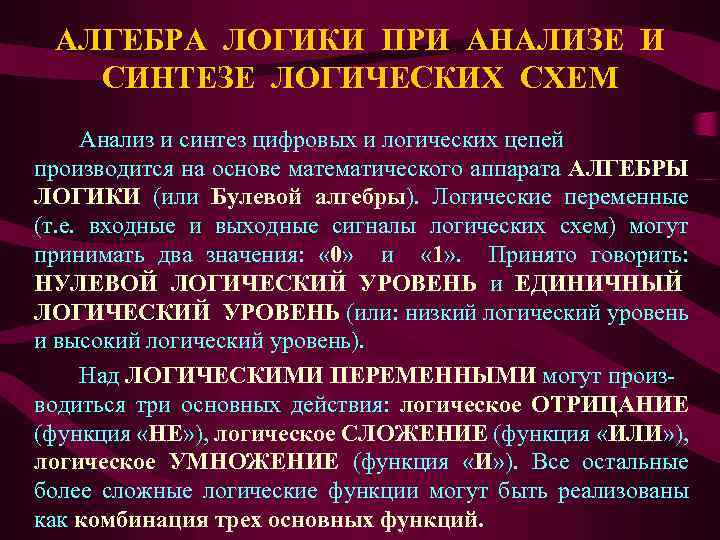

АЛГЕБРА ЛОГИКИ ПРИ АНАЛИЗЕ И СИНТЕЗЕ ЛОГИЧЕСКИХ СХЕМ Анализ и синтез цифровых и логических цепей производится на основе математического аппарата АЛГЕБРЫ ЛОГИКИ (или Булевой алгебры). Логические переменные (т. е. входные и выходные сигналы логических схем) могут принимать два значения: « 0» и « 1» . Принято говорить: НУЛЕВОЙ ЛОГИЧЕСКИЙ УРОВЕНЬ и ЕДИНИЧНЫЙ ЛОГИЧЕСКИЙ УРОВЕНЬ (или: низкий логический уровень и высокий логический уровень). Над ЛОГИЧЕСКИМИ ПЕРЕМЕННЫМИ могут производиться три основных действия: логическое ОТРИЦАНИЕ (функция «НЕ» ), логическое СЛОЖЕНИЕ (функция «ИЛИ» ), логическое УМНОЖЕНИЕ (функция «И» ). Все остальные более сложные логические функции могут быть реализованы как комбинация трех основных функций.

ОСНОВНЫЕ ЗАКОНЫ АЛГЕБРЫ ЛОГИКИ Законы алгебры логики Переместительный закон Сочетательный закон Распределительный закон Закон поглощения Закон склеивания Закон отрицания (Правило де Моргана) В базисе "ИЛИ" В базисе "И" a + b = b + a a & b = b & a (a & b) & c = (a+b)+c = a+(b+c) a & (b & c) a+(b&c)= a&(b+c) = a&b+a&c (a+b)&(a+c) a + a & b = a a & (a + b) = a a & b + a & ~b = a (a + b) & (a + ~b) = a a + b = a & b a&b=a+b

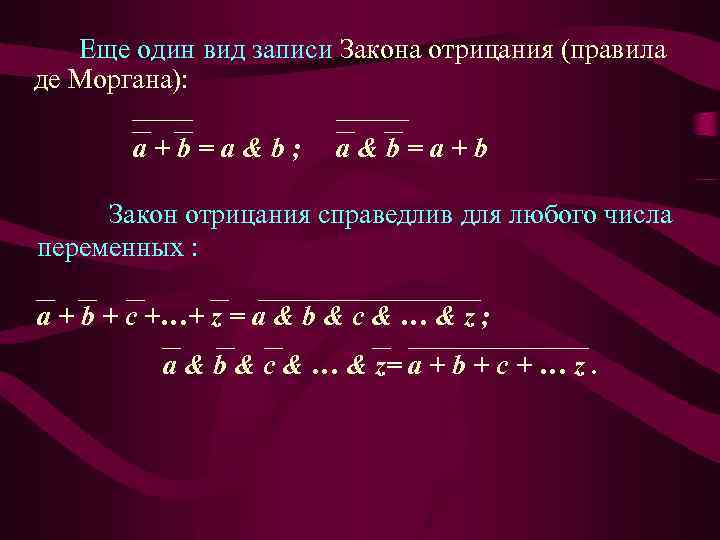

Еще один вид записи Закона отрицания (правила де Моргана): a+b=a&b; a&b=a+b Закон отрицания справедлив для любого числа переменных : a + b + c +…+ z = a & b & c & … & z ; a & b & c & … & z= a + b + c + … z.

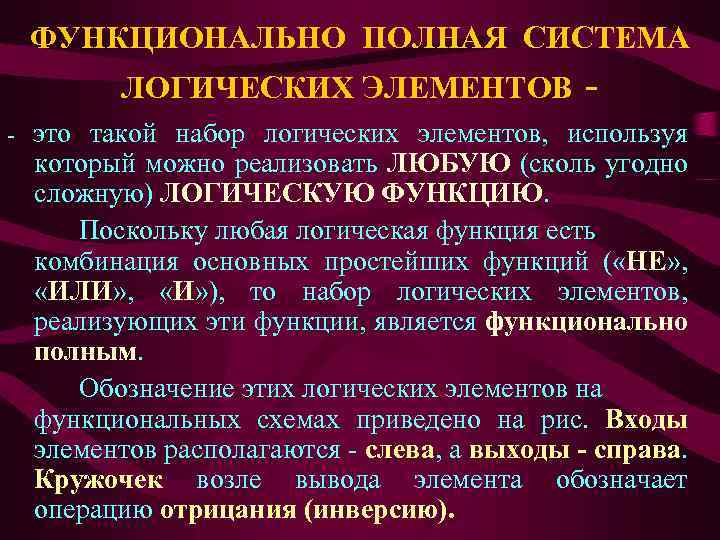

ФУНКЦИОНАЛЬНО ПОЛНАЯ СИСТЕМА ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ - это такой набор логических элементов, используя который можно реализовать ЛЮБУЮ (сколь угодно сложную) ЛОГИЧЕСКУЮ ФУНКЦИЮ. Поскольку любая логическая функция есть комбинация основных простейших функций ( «НЕ» , «ИЛИ» , «И» ), то набор логических элементов, реализующих эти функции, является функционально полным. Обозначение этих логических элементов на функциональных схемах приведено на рис. Входы элементов располагаются - слева, а выходы - справа. Кружочек возле вывода элемента обозначает операцию отрицания (инверсию).

& ИНВЕРТОР 1 Логическое «И» КОНЪЮНКЦИЯ Логическое «ИЛИ» ДИЗЪЮНКЦИЯ Например, логическую функцию: a a & 1 b & b F можно реализовать с помощью двух ячеек «НЕ» (они нужны для того, чтобы получить инверсии входных переменных), двух логических схем «И» (схем конъюнкции) и схемы «ИЛИ»

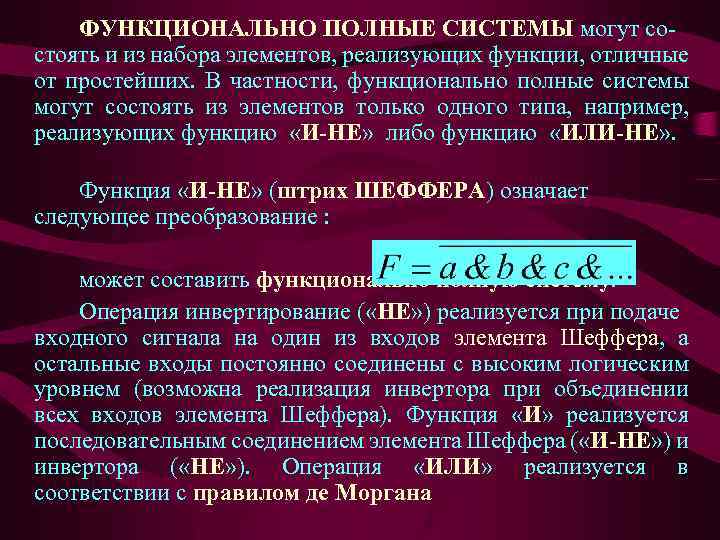

ФУНКЦИОНАЛЬНО ПОЛНЫЕ СИСТЕМЫ могут состоять и из набора элементов, реализующих функции, отличные от простейших. В частности, функционально полные системы могут состоять из элементов только одного типа, например, реализующих функцию «И-НЕ» либо функцию «ИЛИ-НЕ» . Функция «И-НЕ» (штрих ШЕФФЕРА) означает следующее преобразование : может составить функционально полную систему. Операция инвертирование ( «НЕ» ) реализуется при подаче входного сигнала на один из входов элемента Шеффера, а остальные входы постоянно соединены с высоким логическим уровнем (возможна реализация инвертора при объединении всех входов элемента Шеффера). Функция «И» реализуется последовательным соединением элемента Шеффера ( «И-НЕ» ) и инвертора ( «НЕ» ). Операция «ИЛИ» реализуется в соответствии с правилом де Моргана

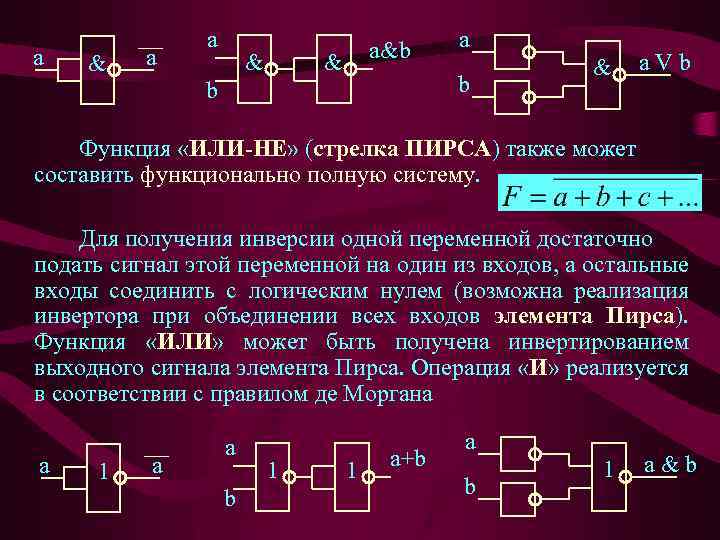

a & a&b & a b b & a V b Функция «ИЛИ-НЕ» (стрелка ПИРСА) также может составить функционально полную систему. Для получения инверсии одной переменной достаточно подать сигнал этой переменной на один из входов, а остальные входы соединить с логическим нулем (возможна реализация инвертора при объединении всех входов элемента Пирса). Функция «ИЛИ» может быть получена инвертированием выходного сигнала элемента Пирса. Операция «И» реализуется в соответствии с правилом де Моргана a 1 a a b 1 1 a+b a b 1 a & b

БАЗОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ - ТТЛ R 1 R 2 VT 1 X 2 X 3 X 4 R 4 +Ек VT 3 VT 2 VD VT 4 R 3 Y Наибольшее распространение получили логические элементы на основе ТТЛ (Транзисторно. Транзисторная Логика) структур Многоэмиттерный транзистор (МЭТ) VT 1 совместно с резистором R 1 образует логическую схему «И» . На трех транзисторах (VT 2. . . VT 4) реализован инвертор (по схеме Дарлингтона). Коллекторной нагрузкой инвертора является резистор R 2. Для уменьшения времени перезаряда паразитных конденсаторов нагрузки (Сн) через резистор R 2 при закрывании составного транзистора VT 2 и VT 4 введен дополнительный эмиттерный повторитель VT 3.

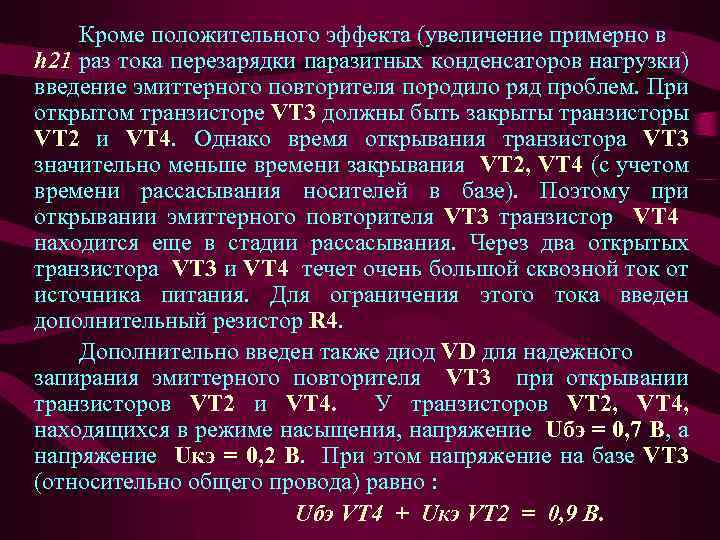

Кроме положительного эффекта (увеличение примерно в h 21 раз тока перезарядки паразитных конденсаторов нагрузки) введение эмиттерного повторителя породило ряд проблем. При открытом транзисторе VT 3 должны быть закрыты транзисторы VT 2 и VT 4. Однако время открывания транзистора VT 3 значительно меньше времени закрывания VT 2, VT 4 (с учетом времени рассасывания носителей в базе). Поэтому при открывании эмиттерного повторителя VT 3 транзистор VT 4 находится еще в стадии рассасывания. Через два открытых транзистора VT 3 и VT 4 течет очень большой сквозной ток от источника питания. Для ограничения этого тока введен дополнительный резистор R 4. Дополнительно введен также диод VD для надежного запирания эмиттерного повторителя VT 3 при открывании транзисторов VT 2 и VT 4. У транзисторов VT 2, VT 4, находящихся в режиме насыщения, напряжение Uбэ = 0, 7 В, а напряжение Uкэ = 0, 2 В. При этом напряжение на базе VT 3 (относительно общего провода) равно : Uбэ VT 4 + Uкэ VT 2 = 0, 9 В.

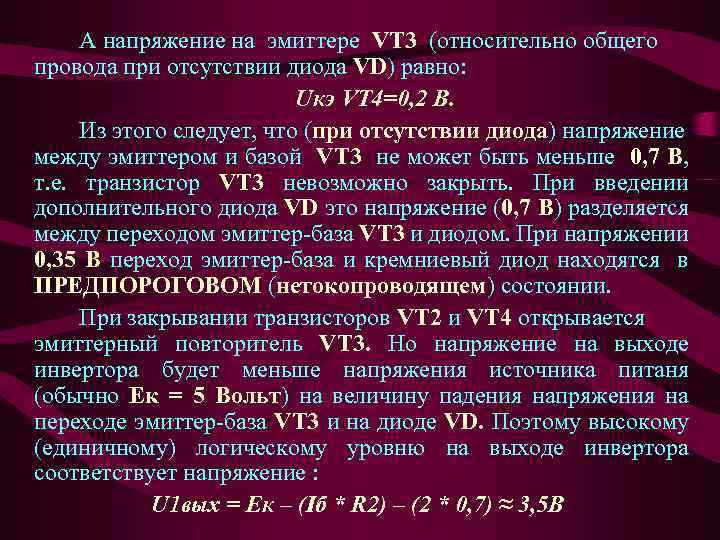

А напряжение на эмиттере VT 3 (относительно общего провода при отсутствии диода VD) равно: Uкэ VT 4=0, 2 В. Из этого следует, что (при отсутствии диода) напряжение между эмиттером и базой VT 3 не может быть меньше 0, 7 В, т. е. транзистор VT 3 невозможно закрыть. При введении дополнительного диода VD это напряжение (0, 7 В) разделяется между переходом эмиттер-база VT 3 и диодом. При напряжении 0, 35 В переход эмиттер-база и кремниевый диод находятся в ПРЕДПОРОГОВОМ (нетокопроводящем) состоянии. При закрывании транзисторов VT 2 и VT 4 открывается эмиттерный повторитель VT 3. Но напряжение на выходе инвертора будет меньше напряжения источника питаня (обычно Ек = 5 Вольт) на величину падения напряжения на переходе эмиттер-база VT 3 и на диоде VD. Поэтому высокому (единичному) логическому уровню на выходе инвертора соответствует напряжение : U 1 вых = Ек – (Iб * R 2) – (2 * 0, 7) ≈ 3, 5 В

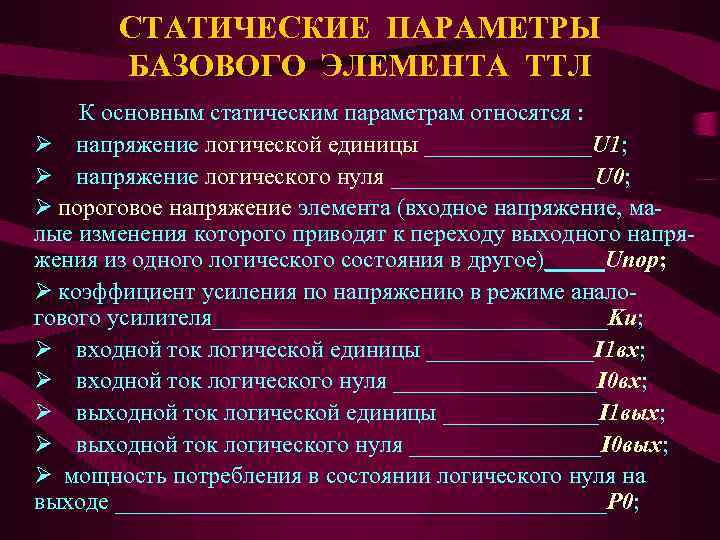

СТАТИЧЕСКИЕ ПАРАМЕТРЫ БАЗОВОГО ЭЛЕМЕНТА ТТЛ К основным статическим параметрам относятся : Ø напряжение логической единицы _______U 1; Ø напряжение логического нуля _________U 0; Ø пороговое напряжение элемента (входное напряжение, малые изменения которого приводят к переходу выходного напряжения из одного логического состояния в другое)_____Uпор; Ø коэффициент усиления по напряжению в режиме аналогового усилителя_________________Ku; Ø входной ток логической единицы _______I 1 вх; Ø входной ток логического нуля _________I 0 вх; Ø выходной ток логической единицы _______I 1 вых; Ø выходной ток логического нуля ________I 0 вых; Ø мощность потребления в состоянии логического нуля на выходе _____________________Р 0;

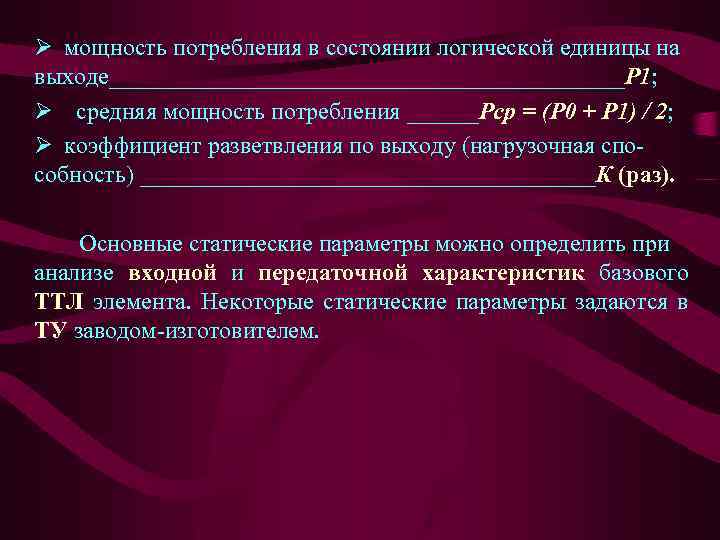

Ø мощность потребления в состоянии логической единицы на выходе______________________Р 1; Ø средняя мощность потребления ______Рср = (Р 0 + Р 1) / 2; Ø коэффициент разветвления по выходу (нагрузочная способность) ___________________К (раз). Основные статические параметры можно определить при анализе входной и передаточной характеристик базового ТТЛ элемента. Некоторые статические параметры задаются в ТУ заводом-изготовителем.

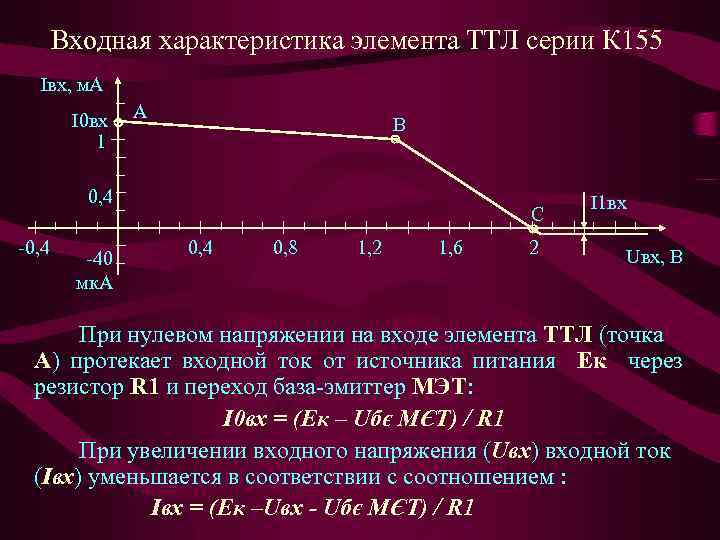

Входная характеристика элемента ТТЛ серии К 155 Iвх, м. А I 0 вх 1 А В 0, 4 -40 мк. А С 0, 4 0, 8 1, 2 1, 6 2 I 1 вх Uвх, В При нулевом напряжении на входе элемента ТТЛ (точка А) протекает входной ток от источника питания Ек через резистор R 1 и переход база-эмиттер МЭТ: I 0 вх = (Ек – Uбє МЄТ) / R 1 При увеличении входного напряжения (Uвх) входной ток (Iвх) уменьшается в соответствии с соотношением : Iвх = (Ек –Uвх - Uбє МЄТ) / R 1

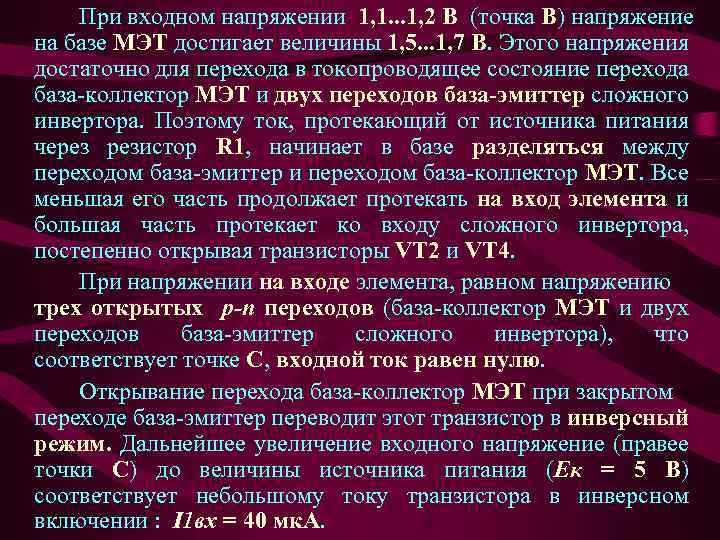

При входном напряжении 1, 1. . . 1, 2 В (точка В) напряжение на базе МЭТ достигает величины 1, 5. . . 1, 7 В. Этого напряжения достаточно для перехода в токопроводящее состояние перехода база-коллектор МЭТ и двух переходов база-эмиттер сложного инвертора. Поэтому ток, протекающий от источника питания через резистор R 1, начинает в базе разделяться между переходом база-эмиттер и переходом база-коллектор МЭТ. Все меньшая его часть продолжает протекать на вход элемента и большая часть протекает ко входу сложного инвертора, постепенно открывая транзисторы VT 2 и VT 4. При напряжении на входе элемента, равном напряжению трех открытых p-n переходов (база-коллектор МЭТ и двух переходов база-эмиттер сложного инвертора), что соответствует точке С, входной ток равен нулю. Открывание перехода база-коллектор МЭТ при закрытом переходе база-эмиттер переводит этот транзистор в инверсный режим. Дальнейшее увеличение входного напряжение (правее точки С) до величины источника питания (Ек = 5 В) соответствует небольшому току транзистора в инверсном включении : I 1 вх = 40 мк. А.

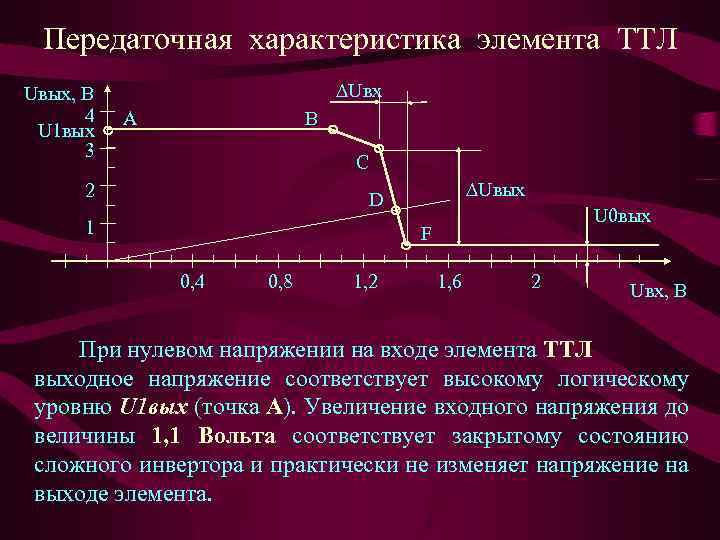

Передаточная характеристика элемента ТТЛ Uвых, В 4 U 1 вых 3 ∆Uвх А В С 2 ∆Uвых D 1 U 0 вых F 0, 4 0, 8 1, 2 1, 6 2 Uвх, В При нулевом напряжении на входе элемента ТТЛ выходное напряжение соответствует высокому логическому уровню U 1 вых (точка А). Увеличение входного напряжения до величины 1, 1 Вольта соответствует закрытому состоянию сложного инвертора и практически не изменяет напряжение на выходе элемента.

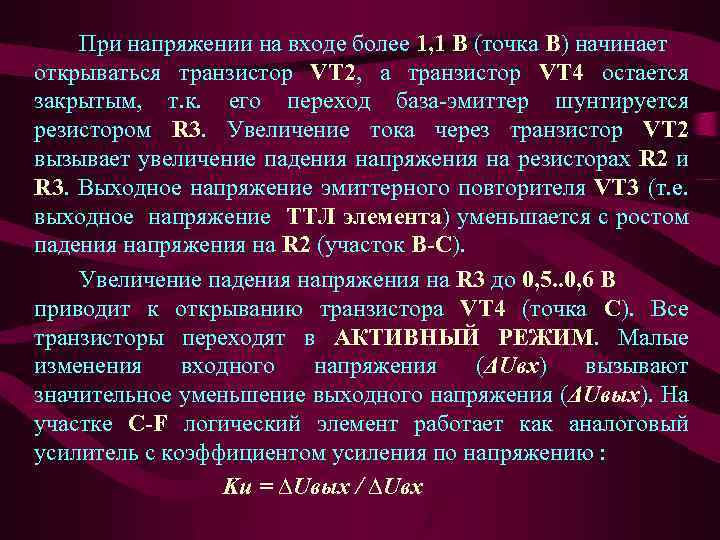

При напряжении на входе более 1, 1 В (точка В) начинает открываться транзистор VT 2, а транзистор VT 4 остается закрытым, т. к. его переход база-эмиттер шунтируется резистором R 3. Увеличение тока через транзистор VT 2 вызывает увеличение падения напряжения на резисторах R 2 и R 3. Выходное напряжение эмиттерного повторителя VT 3 (т. е. выходное напряжение ТТЛ элемента) уменьшается с ростом падения напряжения на R 2 (участок В-С). Увеличение падения напряжения на R 3 до 0, 5. . 0, 6 В приводит к открыванию транзистора VT 4 (точка С). Все транзисторы переходят в АКТИВНЫЙ РЕЖИМ. Малые изменения входного напряжения (ΔUвх) вызывают значительное уменьшение выходного напряжения (ΔUвых). На участке C-F логический элемент работает как аналоговый усилитель с коэффициентом усиления по напряжению : Ku = ∆Uвых / ∆Uвх

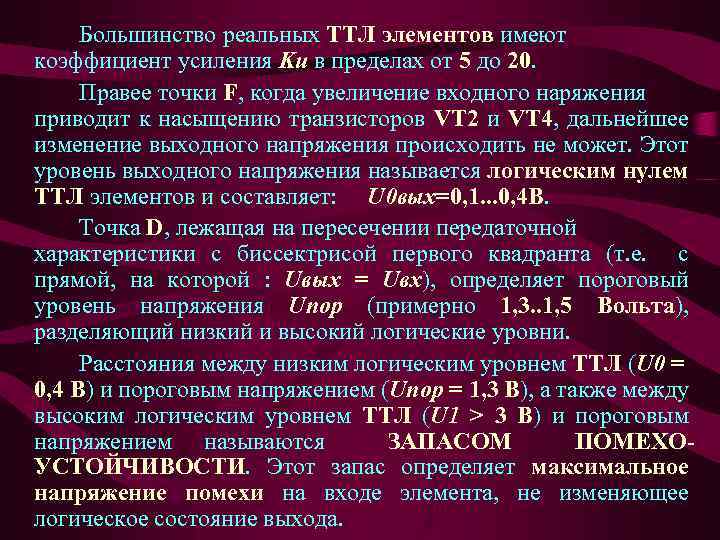

Большинство реальных ТТЛ элементов имеют коэффициент усиления Ku в пределах от 5 до 20. Правее точки F, когда увеличение входного наряжения приводит к насыщению транзисторов VT 2 и VT 4, дальнейшее изменение выходного напряжения происходить не может. Этот уровень выходного напряжения называется логическим нулем ТТЛ элементов и составляет: U 0 вых=0, 1. . . 0, 4 В. Точка D, лежащая на пересечении передаточной характеристики с биссектрисой первого квадранта (т. е. с прямой, на которой : Uвых = Uвх), определяет пороговый уровень напряжения Uпор (примерно 1, 3. . 1, 5 Вольта), разделяющий низкий и высокий логические уровни. Расстояния между низким логическим уровнем ТТЛ (U 0 = 0, 4 В) и пороговым напряжением (Uпор = 1, 3 В), а также между высоким логическим уровнем ТТЛ (U 1 > 3 В) и пороговым напряжением называются ЗАПАСОМ ПОМЕХОУСТОЙЧИВОСТИ. Этот запас определяет максимальное напряжение помехи на входе элемента, не изменяющее логическое состояние выхода.

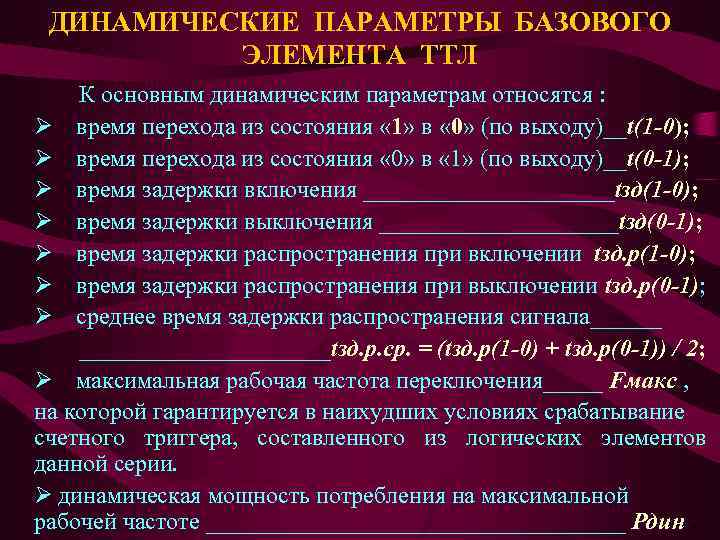

ДИНАМИЧЕСКИЕ ПАРАМЕТРЫ БАЗОВОГО ЭЛЕМЕНТА ТТЛ К основным динамическим параметрам относятся : Ø время перехода из состояния « 1» в « 0» (по выходу)__t(1 -0); Ø время перехода из состояния « 0» в « 1» (по выходу)__t(0 -1); Ø время задержки включения ___________tзд(1 -0); Ø время задержки выключения __________tзд(0 -1); Ø время задержки распространения при включении tзд. р(1 -0); Ø время задержки распространения при выключении tзд. р(0 -1); Ø среднее время задержки распространения сигнала___________tзд. р. ср. = (tзд. р(1 -0) + tзд. р(0 -1)) / 2; Ø максимальная рабочая частота переключения_____ Fмакс , на которой гарантируется в наихудших условиях срабатывание счетного триггера, составленного из логических элементов данной серии. Ø динамическая мощность потребления на максимальной рабочей частоте __________________ Рдин.

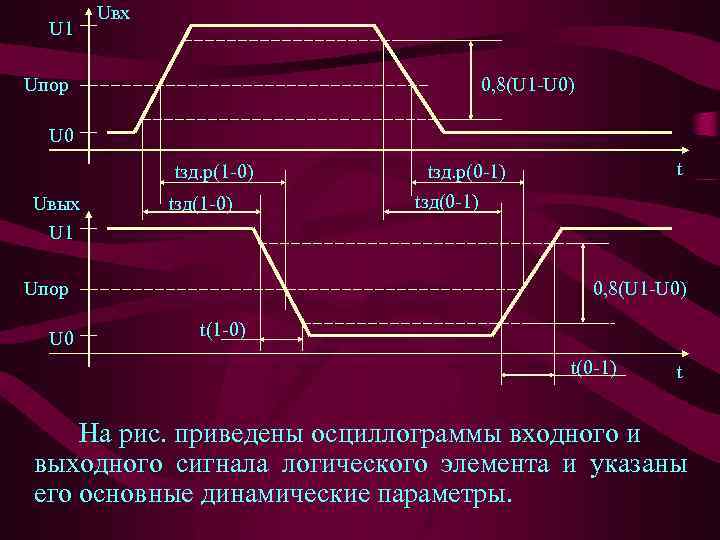

U 1 Uвх Uпор 0, 8(U 1 -U 0) U 0 tзд. р(1 -0) Uвых U 1 tзд(1 -0) Uпор U 0 t tзд. р(0 -1) tзд(0 -1) 0, 8(U 1 -U 0) t(1 -0) t(0 -1) t На рис. приведены осциллограммы входного и выходного сигнала логического элемента и указаны его основные динамические параметры.

ОСОБЕННОСТИ СХЕМОТЕХНИКИ ЭЛЕМЕНТОВ ТТЛ R 1 R 2 VT 1 X 2 X 3 X 4 +Ек R 4 VT 3 VT 5 VT 2 Y VT 4 R 3 R 5 ТТЛ элемент с повышенной нагрузочной способностью за счет применения составного эмиттерного повторителя VT 3, VT 5 и более мощного транзистора VT 4. Как особенность элемента ТТЛ следует отметить недопустимость соединения выходов нескольких элементов. Если допустить такое соединение, то в состоянии, когда на выходе одного элемента установится логический « 0» , а на другом - логическая « 1» , через последовательно соединенные транзистор VT 4 одной микросхемы и эмиттерный повторитель другой микросхемы протекает большой сквозной ток.

R 1 R 2 +5 В +12 В ТТЛ элемент с «открытым коллектором» , предна. VT 1 Rн значен для подклю. VDL VT 2 Y X 1 чения элементов ин. X 2 дикации (световой X 3 VT 4 диод VDL) или дру. X 4 R 3 гой нагрузки (например, РЕЛЕ). Причем внешняя нагрузка может быть подключена другим выводом к источнику питания логических схем +5 В или к более высокому напряжению (до 12 В). При использовании схем с «открытым коллектором» в качестве логических элементов необходимо подключить между выходом элемента и проводом питания +5 В дополнительный резистор. Выходы логических элементов с «открытым коллектором» можно объединять между собой для образования логической функции «монтажное ИЛИ» . R 6

R 2 R 1 VT 3 VT 2 X 1 X 2 X 3 X 4 R 5 VT 5 X 6 X 7 X 8 R 4 R 3 VD VT 4 +Ек Логический элемент Y «И-ИЛИ-НЕ» (4 -И, 2 -ИЛИ-НЕ) VT 6 Функция «ИЛИ» может быть также реализована внутри ТТЛ элемента. На рис. приведен ТТЛ элемент, выполняющий логическую функцию : ____________ Y = (x 1 x 2 x 3 x 4) / (x 5 x 6 x 7 x 8) При использовании в качестве VT 1 и VT 5 обычных (одноэмиттерных) транзисторов схема выполняет функцию «ИЛИ-НЕ» (элемент ПИРСА).

R 1 R 6 R 2 VT 1 X 2 X 3 X 4 R 4 VT 3 VT 5 VT 2 VT 6 R 5 VD +Ек ТТЛ элемент «И» без инверсии Y VT 4 R 3 Логическая функция «И» может быть реализована последовательным соединением элемента Шеффера «И-НЕ» и инвертора «НЕ» . При этом в два раза возрастает время запаздывания сигнала и увеличивается количество применяемых микросхем. В составе ТТЛ микросхем выпускаются логические схемы без инверсии. Эта схема фактически выполняет функцию «И-НЕ-НЕ» и содержит два инвертора (на транзисторах VT 5, VT 6 и обычный инвертор на транзисторах VT 2, VT 3, VT 4).

R 1 R 2 VT 1 X 2 X 3 OE R 4 +Ек VT 3 VT 2 VD 1 ТТЛ элемент с Z-состоянием выхода Y VT 4 R 3 При необходимости объединения нескольких выходов ТТЛ элементов (например, при формировании двунаправлен-ных шин микропроцессорных систем) используются схемы с Zсостоянием выхода (вариант названия: схема с тремя состояниями выхода). Два состояния – это обычные уровни U 0 и U 1, а третье состояние обеспечивает режим с «бесконечно большим» выходным сопротивлением (Z-состояние), в котором элемент полностью отключается от нагрузки.

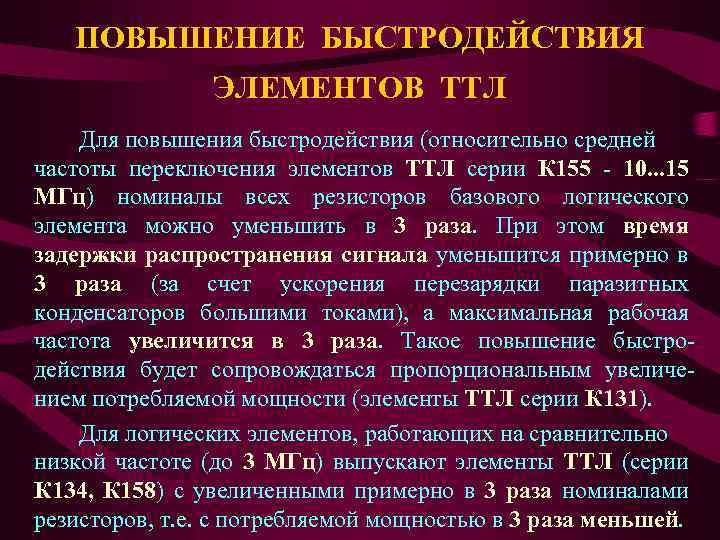

ПОВЫШЕНИЕ БЫСТРОДЕЙСТВИЯ ЭЛЕМЕНТОВ ТТЛ Для повышения быстродействия (относительно средней частоты переключения элементов ТТЛ серии К 155 - 10. . . 15 МГц) номиналы всех резисторов базового логического элемента можно уменьшить в 3 раза. При этом время задержки распространения сигнала уменьшится примерно в 3 раза (за счет ускорения перезарядки паразитных конденсаторов большими токами), а максимальная рабочая частота увеличится в 3 раза. Такое повышение быстродействия будет сопровождаться пропорциональным увеличением потребляемой мощности (элементы ТТЛ серии К 131). Для логических элементов, работающих на сравнительно низкой частоте (до 3 МГц) выпускают элементы ТТЛ (серии К 134, К 158) с увеличенными примерно в 3 раза номиналами резисторов, т. е. с потребляемой мощностью в 3 раза меньшей.

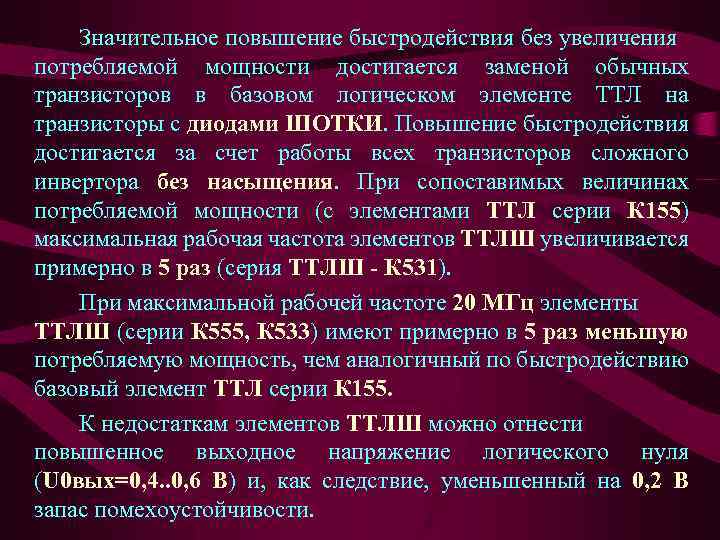

Значительное повышение быстродействия без увеличения потребляемой мощности достигается заменой обычных транзисторов в базовом логическом элементе ТТЛ на транзисторы с диодами ШОТКИ. Повышение быстродействия достигается за счет работы всех транзисторов сложного инвертора без насыщения. При сопоставимых величинах потребляемой мощности (с элементами ТТЛ серии К 155) максимальная рабочая частота элементов ТТЛШ увеличивается примерно в 5 раз (серия ТТЛШ - К 531). При максимальной рабочей частоте 20 МГц элементы ТТЛШ (серии К 555, К 533) имеют примерно в 5 раз меньшую потребляемую мощность, чем аналогичный по быстродействию базовый элемент ТТЛ серии К 155. К недостаткам элементов ТТЛШ можно отнести повышенное выходное напряжение логического нуля (U 0 вых=0, 4. . 0, 6 В) и, как следствие, уменьшенный на 0, 2 В запас помехоустойчивости.

+Ек VT 1′ R 1 X 1 R 2 VT 6 VT 3 VD′ VT 4 VD″ X 2 R 8 R 4 VT 7 R 7 VT 1″ R 3 R 5 R 6 Y VT 8 VT 5 VT 2′ VT 2″ Схема базового элемента ТТЛШ серии К 1533. Микросхемы изготавливаются по усовершенствованной эпитаксиально-планарной технологии с диодами ШОТКИ и оксидной изоляцией элементов.

Основные особенности схемы: Ø все транзисторы и диоды выполнены с барьером Шотки; Ø на входе вместо МЭТ применяются эмиттерные повторители на транзисторах p-n-p (VT 1', VT 1") для уменьшения входных токов логического нуля и логической единицы; Ø диоды Шотки VD', VD" введены для уменьшения времени закрывания сложного инвертора VT 4. . . VT 8; Ø транзисторы VT 2', VT 2" в диодном включении защищают входы ИС от выбросов отрицательного напряжения; Ø транзистор VT 5 и резисторы R 5, R 6 образуют схему термокомпенсации, стабилизируя параметры ИС в широком диапазоне рабочих температур.

Вопросы для экспресс-контроля • 1. На каких активных элементах может быть реализованы логические ключи? • 2. Назовите 4 режима работы биполярного транзистора и состояния переходов в каждом из этих режимов. • 3. Почему работа биполярного транзистора с насыщением приводит к уменьшению быстродействия электронных ключей? • 4. Назовите методы повышения быстродействия электронных ключей на биполярных транзисторах.

Вопросы для экспресс-контроля • 5. Назовите основные законы АЛГЕБРЫ ЛОГИКИ. • 6. Что такое функционально полная система логических элементов? Приведите примеры функционально полных систем.

ЛЕКЦИЯ ОКОНЧЕНА СПАСИБО ЗА ВНИМАНИЕ

SCH-T-2.ppt