!Компьютер и его подсистемы.ppt

- Количество слайдов: 158

Компьютер и его подсистемы Процессор Иерархическая память Подсистема ввода-вывода Подсистема связи

Компьютер и его подсистемы Процессор Иерархическая память Подсистема ввода-вывода Подсистема связи

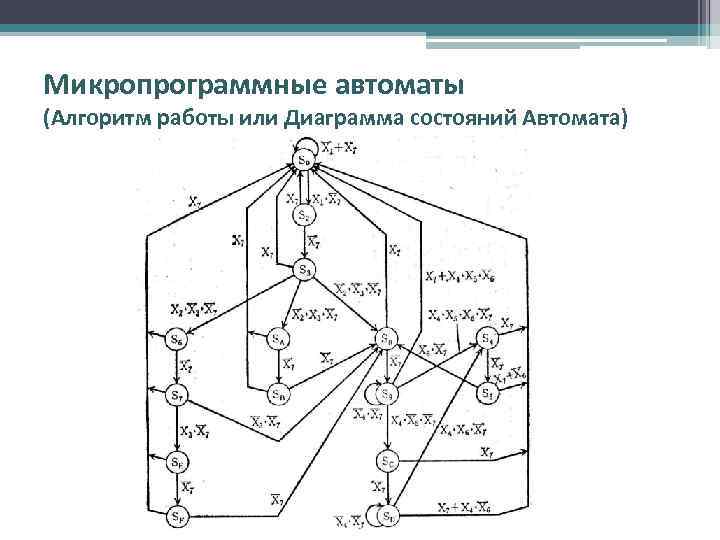

Микропрограммные автоматы (Алгоритм работы или Диаграмма состояний Автомата)

Микропрограммные автоматы (Алгоритм работы или Диаграмма состояний Автомата)

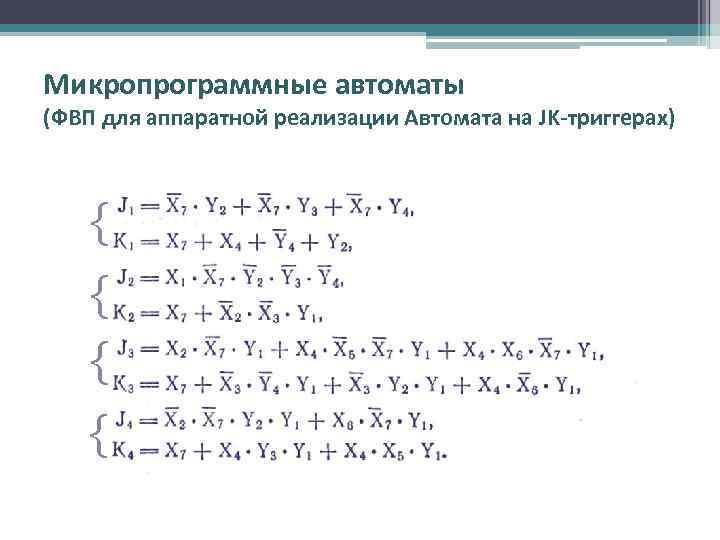

Микропрограммные автоматы (ФВП для аппаратной реализации Автомата на JK-триггерах) { {

Микропрограммные автоматы (ФВП для аппаратной реализации Автомата на JK-триггерах) { {

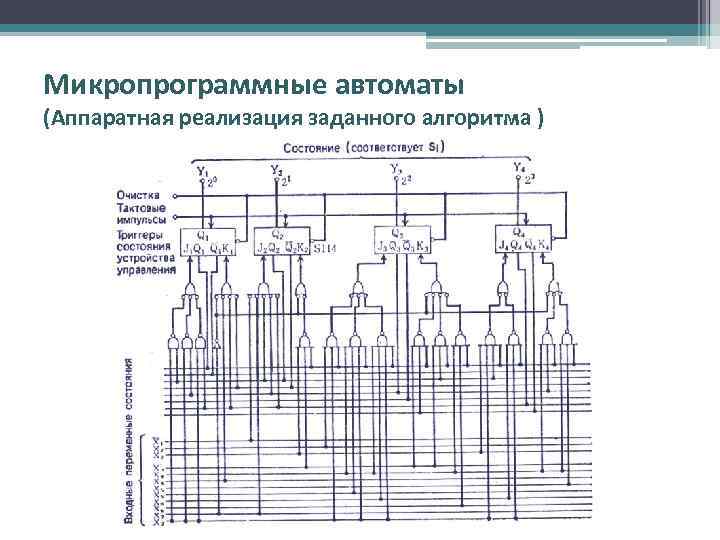

Микропрограммные автоматы (Аппаратная реализация заданного алгоритма )

Микропрограммные автоматы (Аппаратная реализация заданного алгоритма )

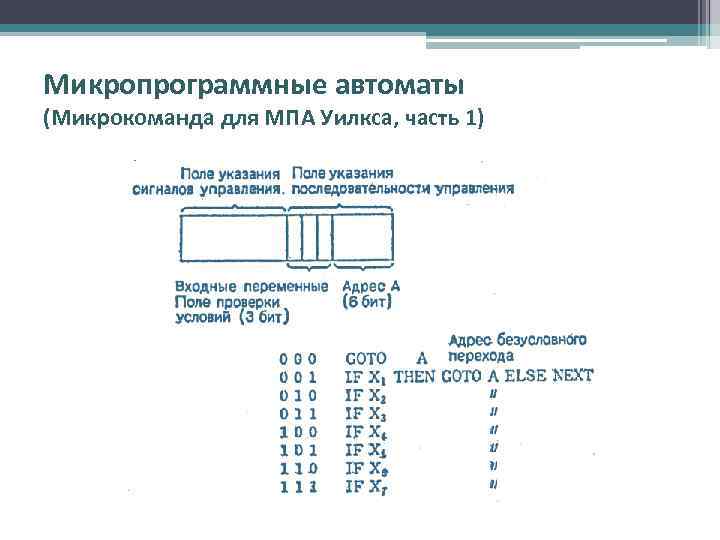

Микропрограммные автоматы (Микрокоманда для МПА Уилкса, часть 1)

Микропрограммные автоматы (Микрокоманда для МПА Уилкса, часть 1)

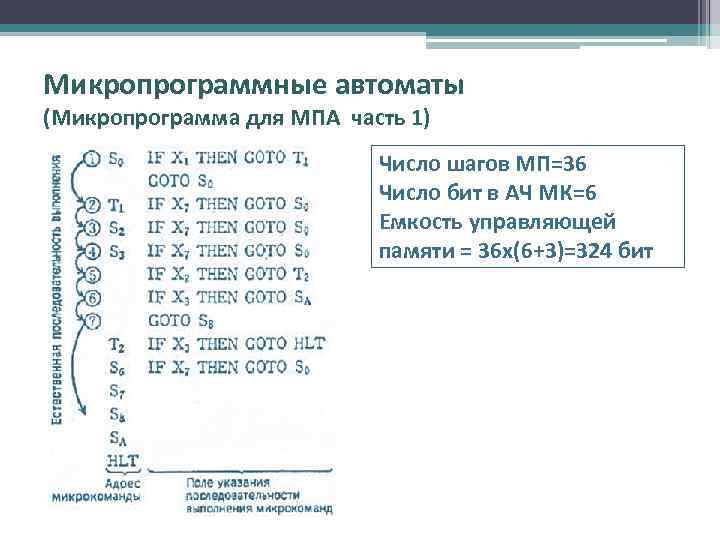

Микропрограммные автоматы (Микропрограмма для МПА часть 1) Число шагов МП=36 Число бит в АЧ МК=6 Емкость управляющей памяти = 36 х(6+3)=324 бит

Микропрограммные автоматы (Микропрограмма для МПА часть 1) Число шагов МП=36 Число бит в АЧ МК=6 Емкость управляющей памяти = 36 х(6+3)=324 бит

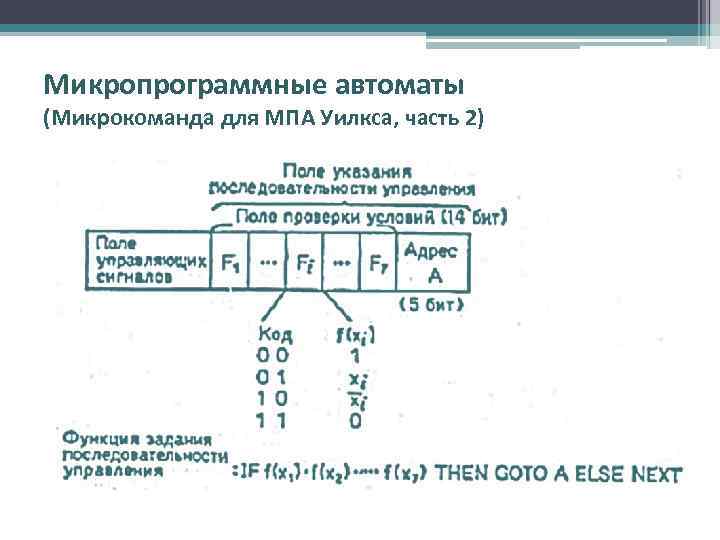

Микропрограммные автоматы (Микрокоманда для МПА Уилкса, часть 2)

Микропрограммные автоматы (Микрокоманда для МПА Уилкса, часть 2)

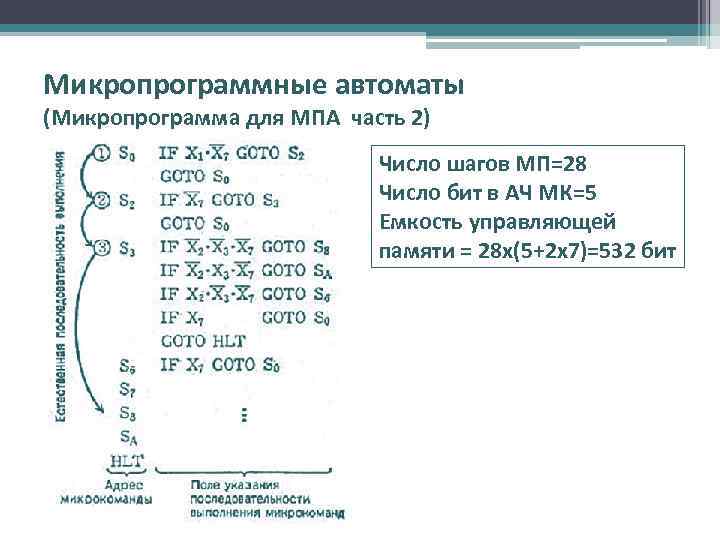

Микропрограммные автоматы (Микропрограмма для МПА часть 2) Число шагов МП=28 Число бит в АЧ МК=5 Емкость управляющей памяти = 28 х(5+2 х7)=532 бит

Микропрограммные автоматы (Микропрограмма для МПА часть 2) Число шагов МП=28 Число бит в АЧ МК=5 Емкость управляющей памяти = 28 х(5+2 х7)=532 бит

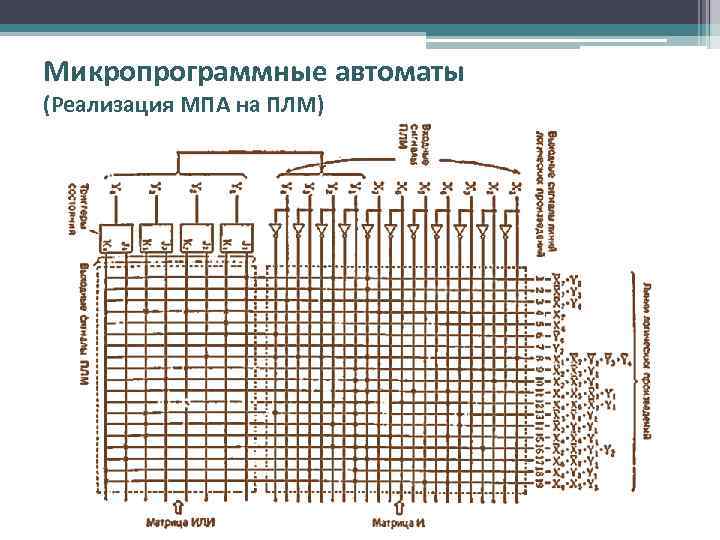

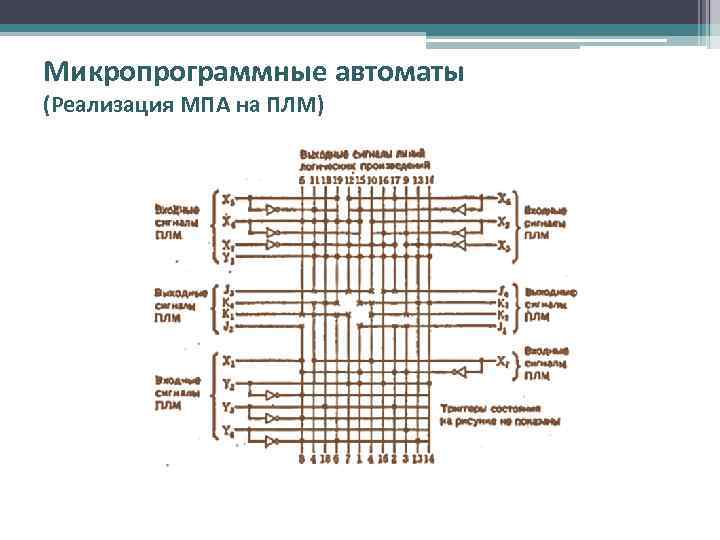

Микропрограммные автоматы (Реализация МПА на ПЛМ)

Микропрограммные автоматы (Реализация МПА на ПЛМ)

Микропрограммные автоматы (Реализация МПА на ПЛМ)

Микропрограммные автоматы (Реализация МПА на ПЛМ)

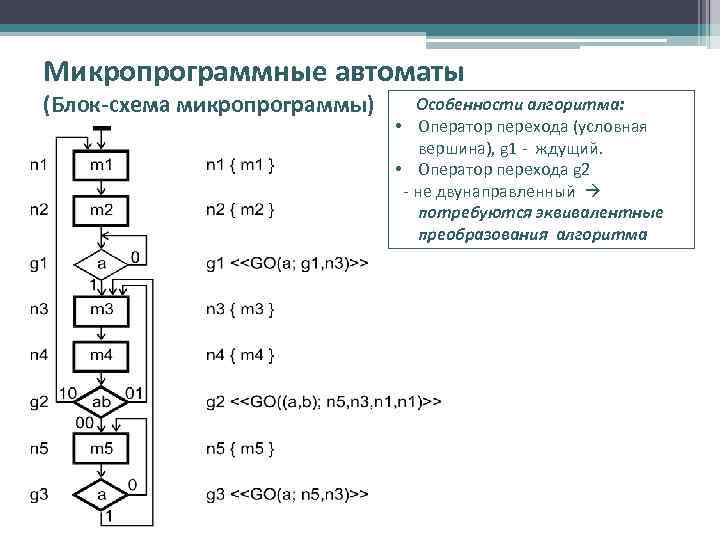

Микропрограммные автоматы (Блок-схема микропрограммы) Особенности алгоритма: • Оператор перехода (условная вершина), g 1 - ждущий. • Оператор перехода g 2 - не двунаправленный потребуются эквивалентные преобразования алгоритма

Микропрограммные автоматы (Блок-схема микропрограммы) Особенности алгоритма: • Оператор перехода (условная вершина), g 1 - ждущий. • Оператор перехода g 2 - не двунаправленный потребуются эквивалентные преобразования алгоритма

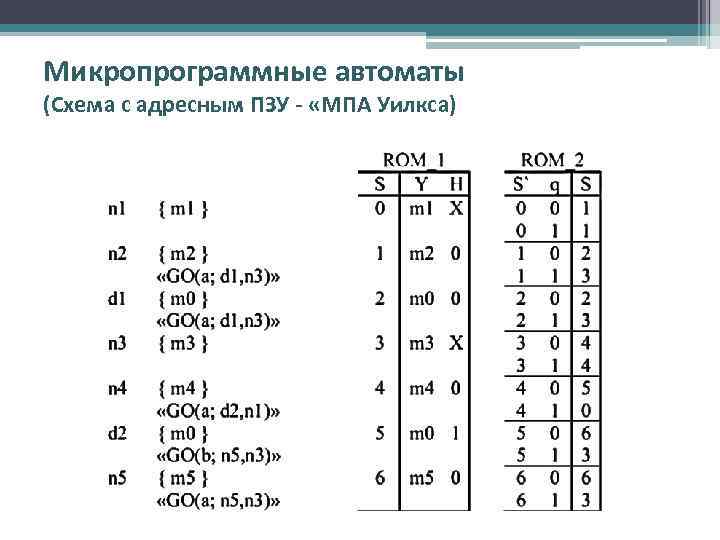

Микропрограммные автоматы (Схема с адресным ПЗУ - «МПА Уилкса» ) последовательная

Микропрограммные автоматы (Схема с адресным ПЗУ - «МПА Уилкса» ) последовательная

Микропрограммные автоматы (Схема с адресным ПЗУ - «МПА Уилкса)

Микропрограммные автоматы (Схема с адресным ПЗУ - «МПА Уилкса)

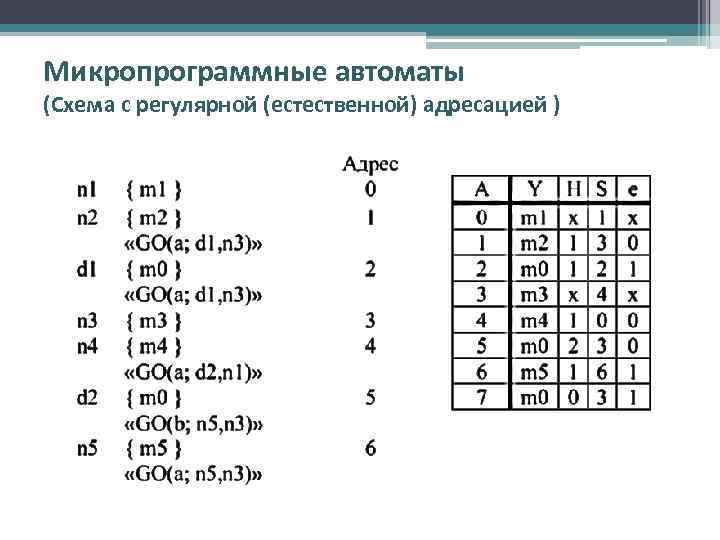

Микропрограммные автоматы (Схема с регулярной (естественной) адресацией )

Микропрограммные автоматы (Схема с регулярной (естественной) адресацией )

Микропрограммные автоматы (Схема с регулярной (естественной) адресацией )

Микропрограммные автоматы (Схема с регулярной (естественной) адресацией )

Операционные автоматы (Универсальный ОА)

Операционные автоматы (Универсальный ОА)

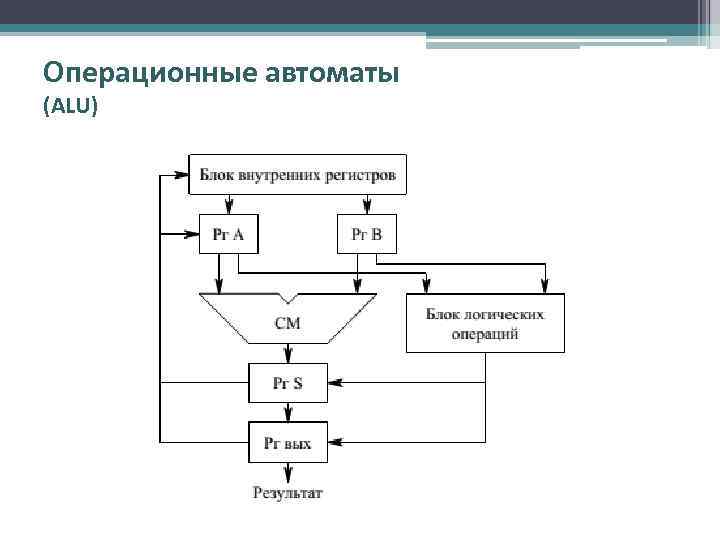

Операционные автоматы (ALU)

Операционные автоматы (ALU)

Микропрограммные автоматы (Процессор. Многофункциональное АЛУ)

Микропрограммные автоматы (Процессор. Многофункциональное АЛУ)

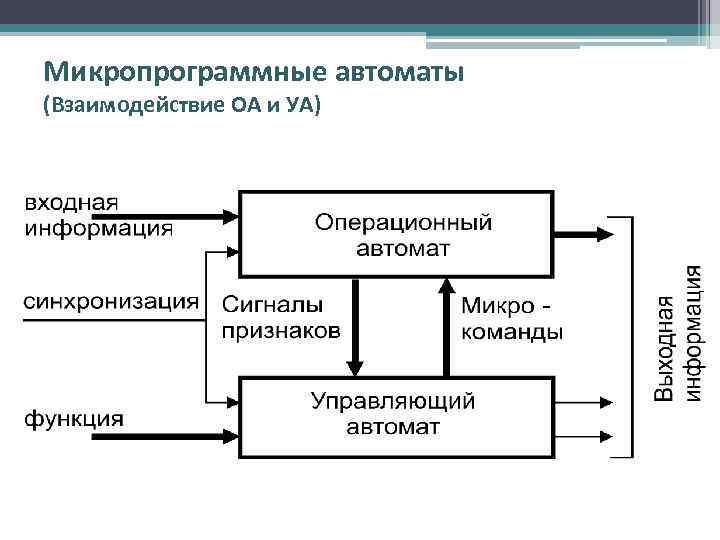

Микропрограммные автоматы (Взаимодействие ОА и УА)

Микропрограммные автоматы (Взаимодействие ОА и УА)

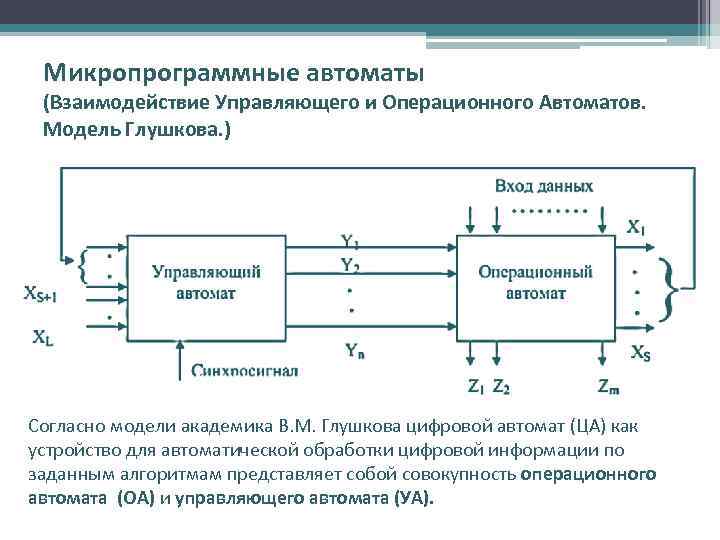

Микропрограммные автоматы (Взаимодействие Управляющего и Операционного Автоматов. Модель Глушкова. ) Согласно модели академика В. М. Глушкова цифровой автомат (ЦА) как устройство для автоматической обработки цифровой информации по заданным алгоритмам представляет собой совокупность операционного автомата (ОА) и управляющего автомата (УА).

Микропрограммные автоматы (Взаимодействие Управляющего и Операционного Автоматов. Модель Глушкова. ) Согласно модели академика В. М. Глушкова цифровой автомат (ЦА) как устройство для автоматической обработки цифровой информации по заданным алгоритмам представляет собой совокупность операционного автомата (ОА) и управляющего автомата (УА).

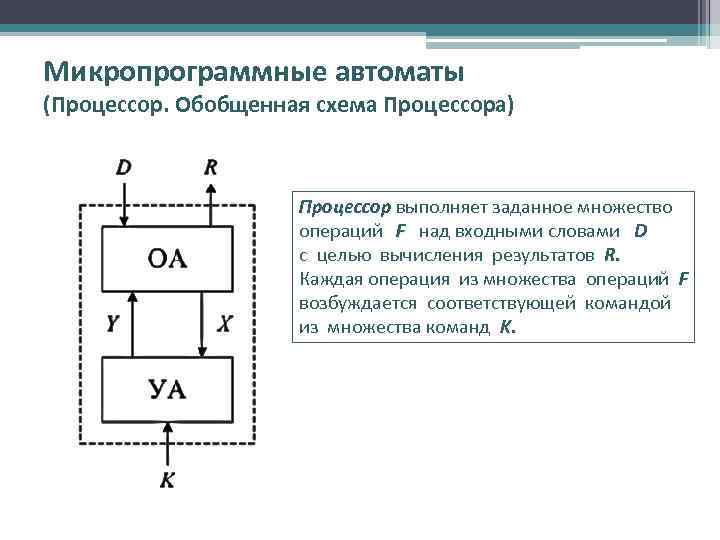

Микропрограммные автоматы (Процессор. Обобщенная схема Процессора) Процессор выполняет заданное множество операций F над входными словами D с целью вычисления результатов R. Каждая операция из множества операций F возбуждается соответствующей командой из множества команд K.

Микропрограммные автоматы (Процессор. Обобщенная схема Процессора) Процессор выполняет заданное множество операций F над входными словами D с целью вычисления результатов R. Каждая операция из множества операций F возбуждается соответствующей командой из множества команд K.

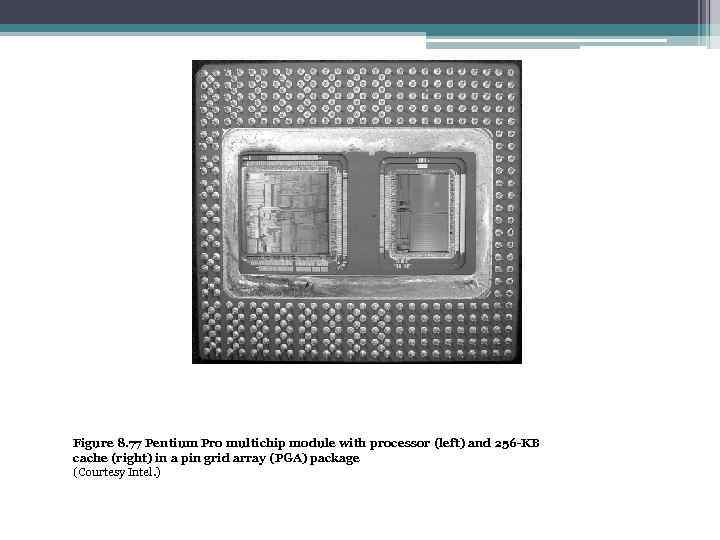

Figure 8. 77 Pentium Pro multichip module with processor (left) and 256 -KB cache (right) in a pin grid array (PGA) package (Courtesy Intel. )

Figure 8. 77 Pentium Pro multichip module with processor (left) and 256 -KB cache (right) in a pin grid array (PGA) package (Courtesy Intel. )

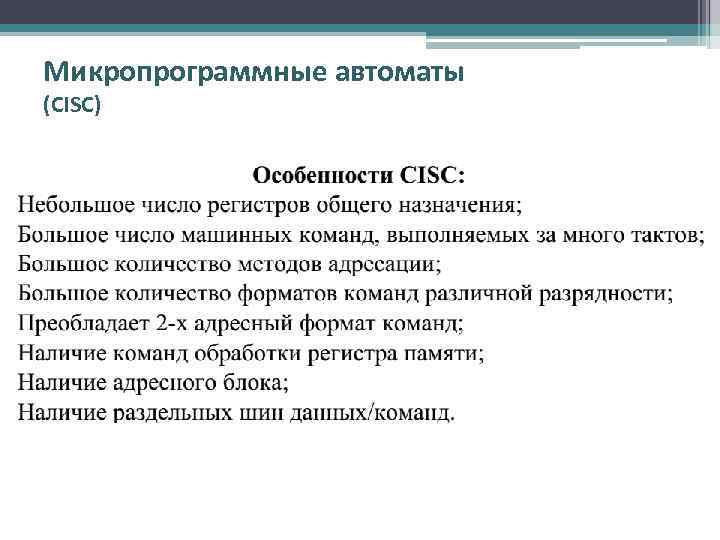

Микропрограммные автоматы (CISC)

Микропрограммные автоматы (CISC)

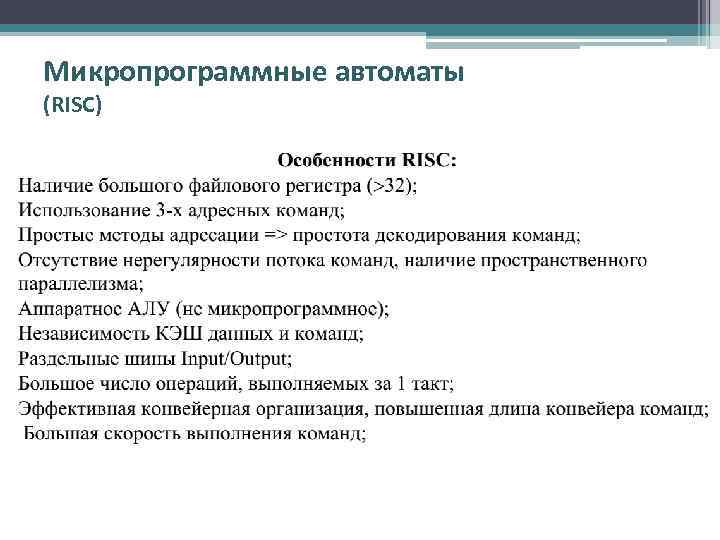

Микропрограммные автоматы (RISC)

Микропрограммные автоматы (RISC)

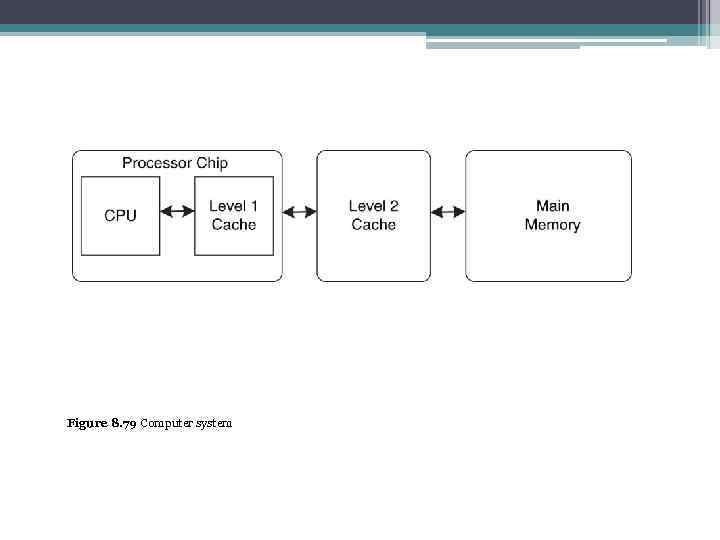

Figure 8. 79 Computer system

Figure 8. 79 Computer system

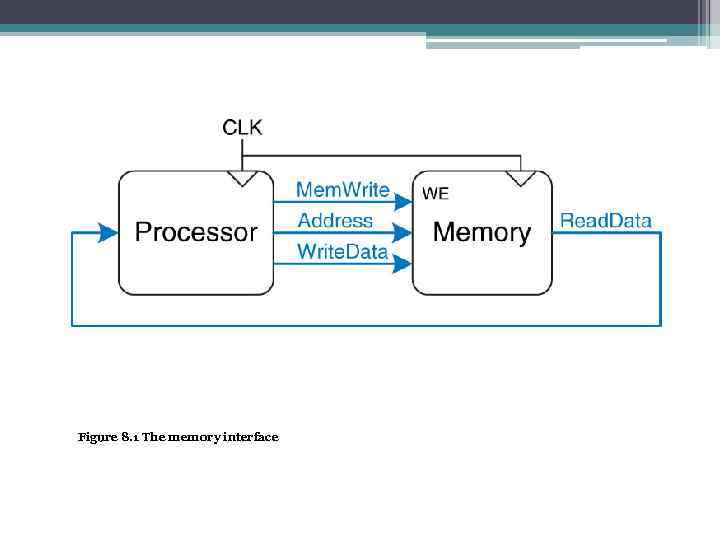

Figure 8. 1 The memory interface

Figure 8. 1 The memory interface

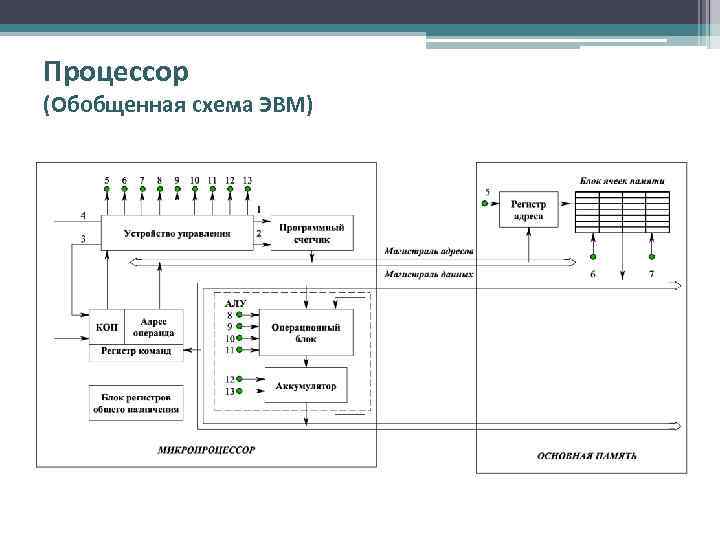

Процессор (Обобщенная схема ЭВМ)

Процессор (Обобщенная схема ЭВМ)

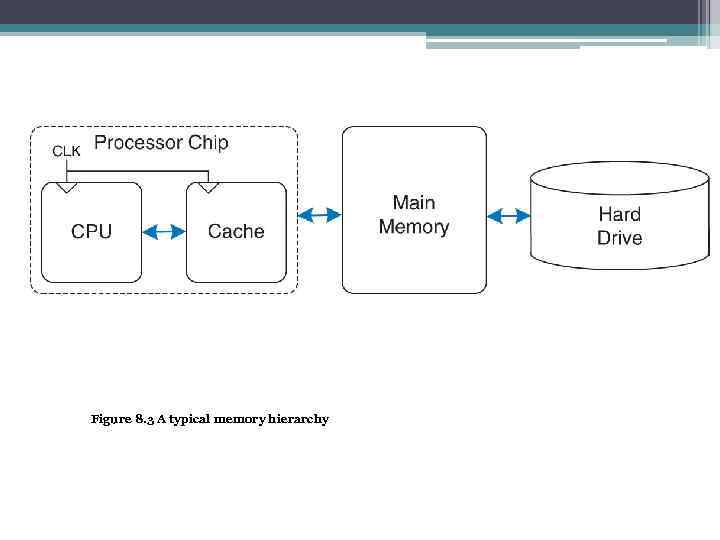

Figure 8. 3 A typical memory hierarchy

Figure 8. 3 A typical memory hierarchy

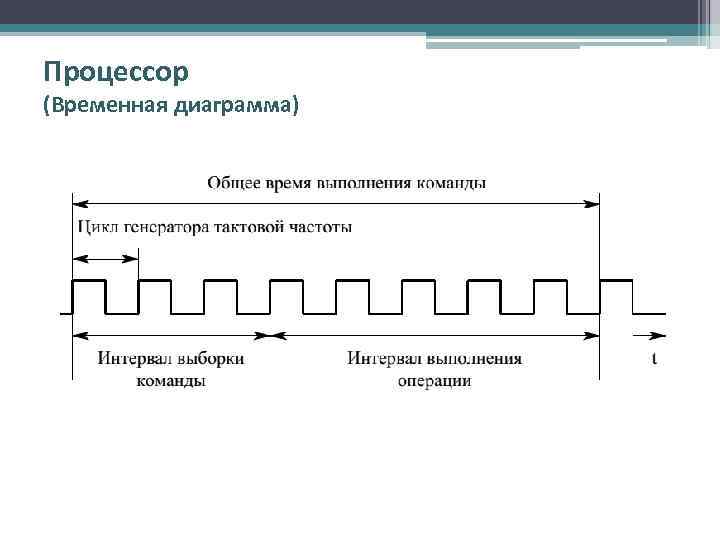

Процессор (Временная диаграмма)

Процессор (Временная диаграмма)

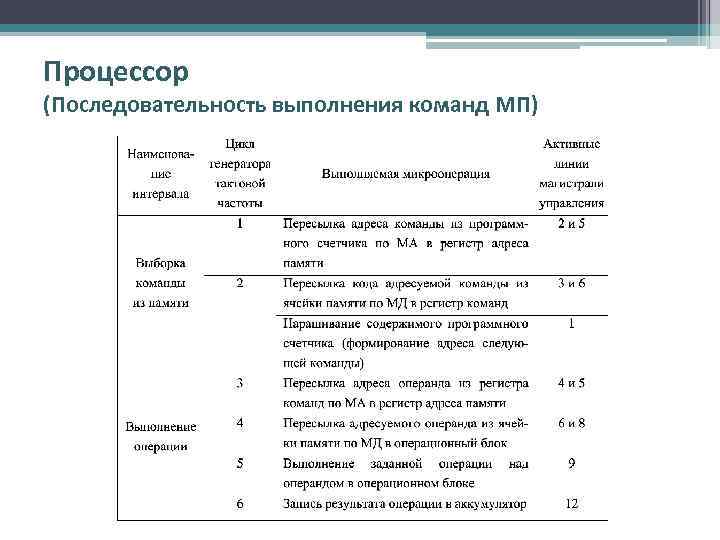

Процессор (Последовательность выполнения команд МП)

Процессор (Последовательность выполнения команд МП)

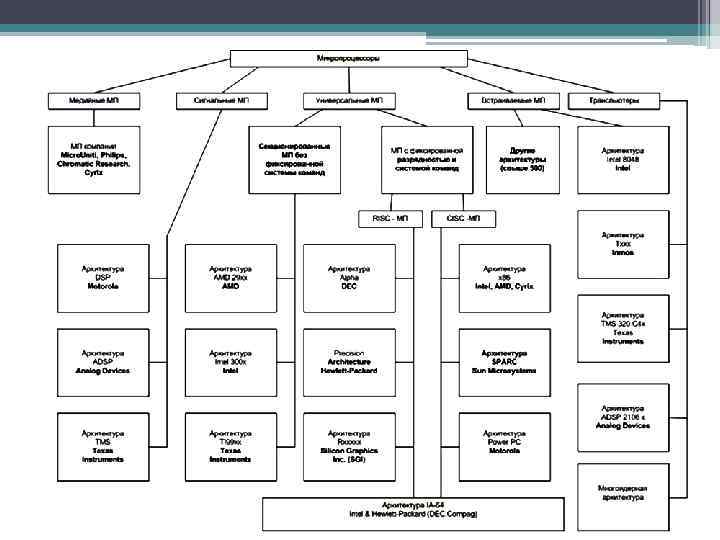

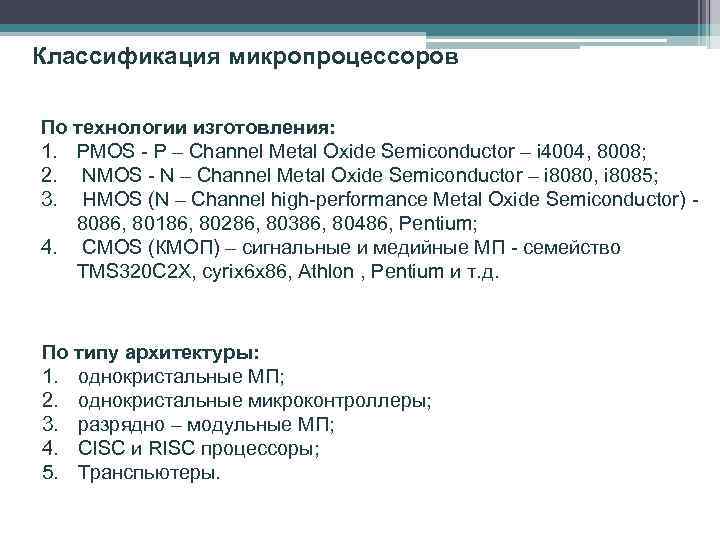

Классификация микропроцессоров По технологии изготовления: 1. PMOS - P – Channel Metal Oxide Semiconductor – i 4004, 8008; 2. NMOS - N – Channel Metal Oxide Semiconductor – i 8080, i 8085; 3. HMOS (N – Channel high-performance Metal Oxide Semiconductor) 8086, 80186, 80286, 80386, 80486, Pentium; 4. CMOS (КМОП) – сигнальные и медийные МП - семейство TMS 320 C 2 X, cyrix 6 x 86, Athlon , Pentium и т. д. По типу архитектуры: 1. однокристальные МП; 2. однокристальные микроконтроллеры; 3. разрядно – модульные МП; 4. CISC и RISC процессоры; 5. Транспьютеры.

Классификация микропроцессоров По технологии изготовления: 1. PMOS - P – Channel Metal Oxide Semiconductor – i 4004, 8008; 2. NMOS - N – Channel Metal Oxide Semiconductor – i 8080, i 8085; 3. HMOS (N – Channel high-performance Metal Oxide Semiconductor) 8086, 80186, 80286, 80386, 80486, Pentium; 4. CMOS (КМОП) – сигнальные и медийные МП - семейство TMS 320 C 2 X, cyrix 6 x 86, Athlon , Pentium и т. д. По типу архитектуры: 1. однокристальные МП; 2. однокристальные микроконтроллеры; 3. разрядно – модульные МП; 4. CISC и RISC процессоры; 5. Транспьютеры.

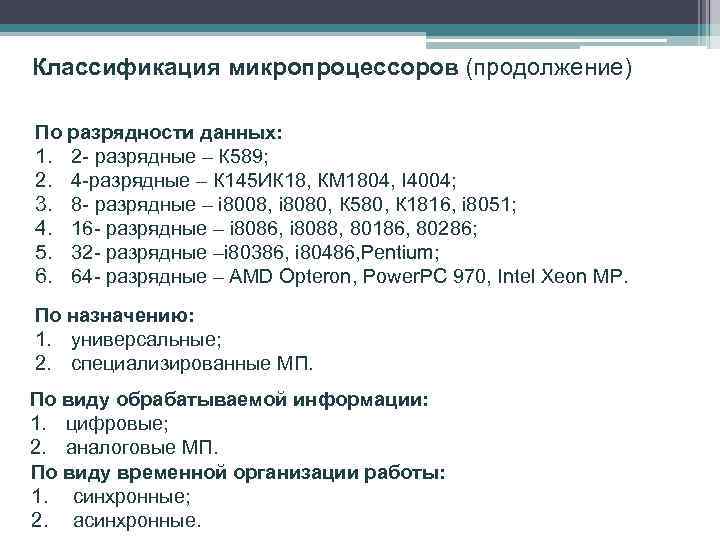

Классификация микропроцессоров (продолжение) По разрядности данных: 1. 2 - разрядные – К 589; 2. 4 -разрядные – К 145 ИК 18, КМ 1804, I 4004; 3. 8 - разрядные – i 8008, i 8080, К 580, К 1816, i 8051; 4. 16 - разрядные – i 8086, i 8088, 80186, 80286; 5. 32 - разрядные –i 80386, i 80486, Pentium; 6. 64 - разрядные – AMD Opteron, Power. PC 970, Intel Xeon MP. По назначению: 1. универсальные; 2. специализированные МП. По виду обрабатываемой информации: 1. цифровые; 2. аналоговые МП. По виду временной организации работы: 1. синхронные; 2. асинхронные.

Классификация микропроцессоров (продолжение) По разрядности данных: 1. 2 - разрядные – К 589; 2. 4 -разрядные – К 145 ИК 18, КМ 1804, I 4004; 3. 8 - разрядные – i 8008, i 8080, К 580, К 1816, i 8051; 4. 16 - разрядные – i 8086, i 8088, 80186, 80286; 5. 32 - разрядные –i 80386, i 80486, Pentium; 6. 64 - разрядные – AMD Opteron, Power. PC 970, Intel Xeon MP. По назначению: 1. универсальные; 2. специализированные МП. По виду обрабатываемой информации: 1. цифровые; 2. аналоговые МП. По виду временной организации работы: 1. синхронные; 2. асинхронные.

Figure 8. 28 Support hardware for memory-mapped I/O

Figure 8. 28 Support hardware for memory-mapped I/O

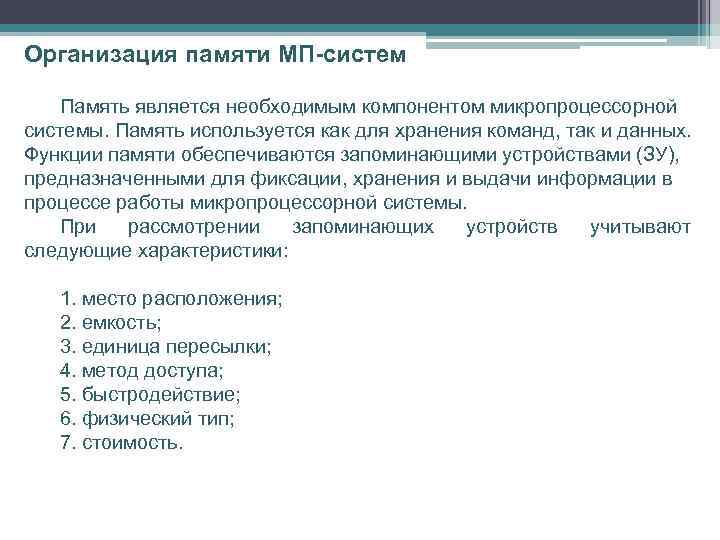

Организация памяти МП-систем Память является необходимым компонентом микропроцессорной системы. Память используется как для хранения команд, так и данных. Функции памяти обеспечиваются запоминающими устройствами (ЗУ), предназначенными для фиксации, хранения и выдачи информации в процессе работы микропроцессорной системы. При рассмотрении запоминающих устройств учитывают следующие характеристики: 1. место расположения; 2. емкость; 3. единица пересылки; 4. метод доступа; 5. быстродействие; 6. физический тип; 7. стоимость.

Организация памяти МП-систем Память является необходимым компонентом микропроцессорной системы. Память используется как для хранения команд, так и данных. Функции памяти обеспечиваются запоминающими устройствами (ЗУ), предназначенными для фиксации, хранения и выдачи информации в процессе работы микропроцессорной системы. При рассмотрении запоминающих устройств учитывают следующие характеристики: 1. место расположения; 2. емкость; 3. единица пересылки; 4. метод доступа; 5. быстродействие; 6. физический тип; 7. стоимость.

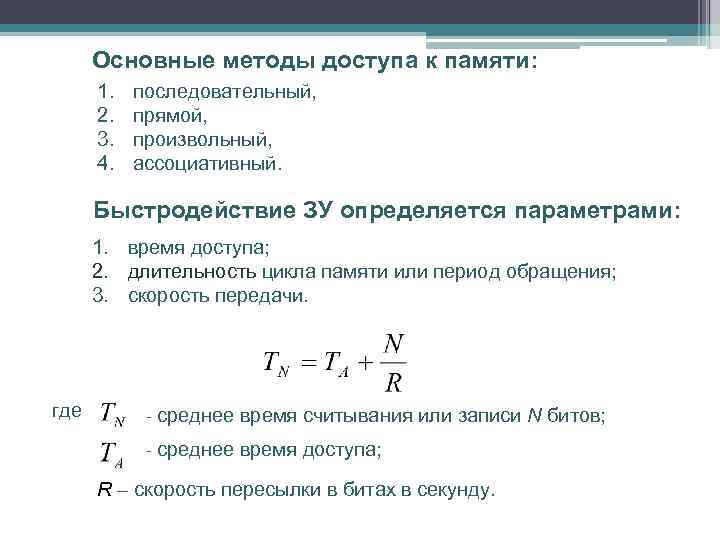

Основные методы доступа к памяти: 1. 2. 3. 4. последовательный, прямой, произвольный, ассоциативный. Быстродействие ЗУ определяется параметрами: 1. время доступа; 2. длительность цикла памяти или период обращения; 3. скорость передачи. где - среднее время считывания или записи N битов; - среднее время доступа; R – скорость пересылки в битах в секунду.

Основные методы доступа к памяти: 1. 2. 3. 4. последовательный, прямой, произвольный, ассоциативный. Быстродействие ЗУ определяется параметрами: 1. время доступа; 2. длительность цикла памяти или период обращения; 3. скорость передачи. где - среднее время считывания или записи N битов; - среднее время доступа; R – скорость пересылки в битах в секунду.

Организация памяти МП-систем

Организация памяти МП-систем

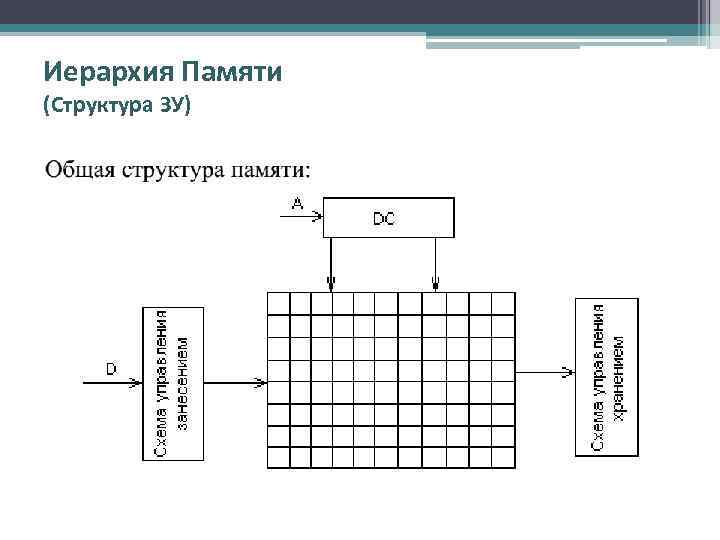

Иерархия Памяти (Структура ЗУ)

Иерархия Памяти (Структура ЗУ)

Иерархия Памяти (Классификация ЗУ) По физическому признаку По типу обращения

Иерархия Памяти (Классификация ЗУ) По физическому признаку По типу обращения

Иерархия Памяти (Классификация ЗУ) ПЗУ По типу обращения

Иерархия Памяти (Классификация ЗУ) ПЗУ По типу обращения

Иерархия Памяти (ПЗУ, Статическая, Динамическая)

Иерархия Памяти (ПЗУ, Статическая, Динамическая)

Иерархия Памяти (Структура ЗУ)

Иерархия Памяти (Структура ЗУ)

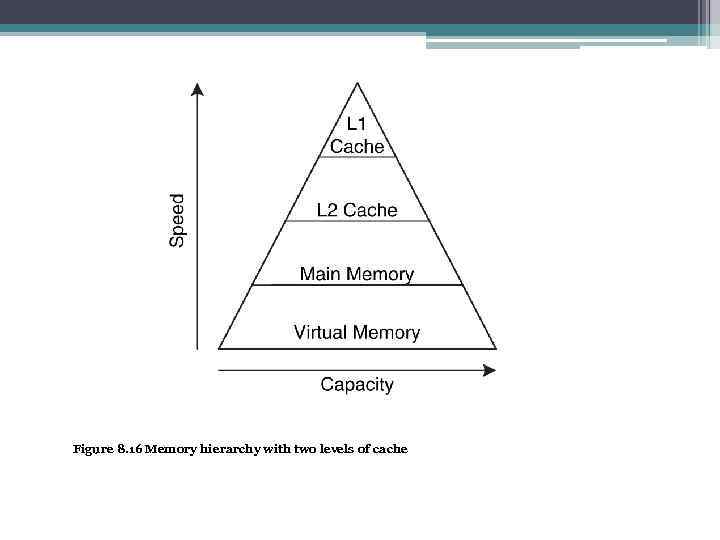

Figure 8. 16 Memory hierarchy with two levels of cache

Figure 8. 16 Memory hierarchy with two levels of cache

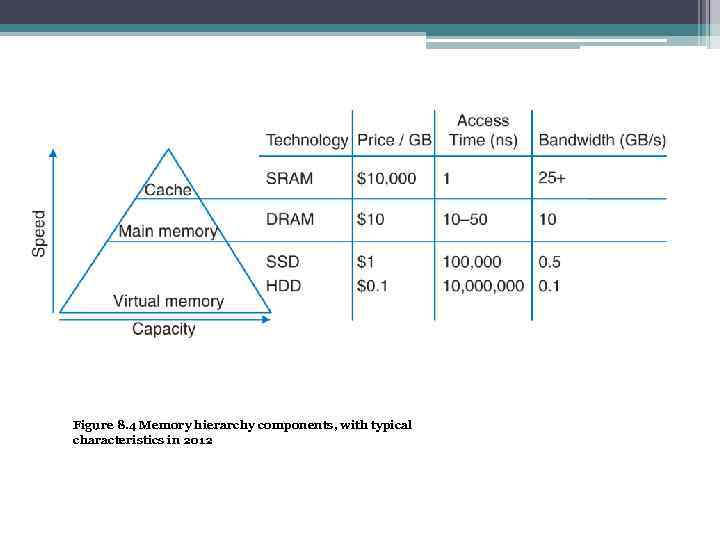

Figure 8. 4 Memory hierarchy components, with typical characteristics in 2012

Figure 8. 4 Memory hierarchy components, with typical characteristics in 2012

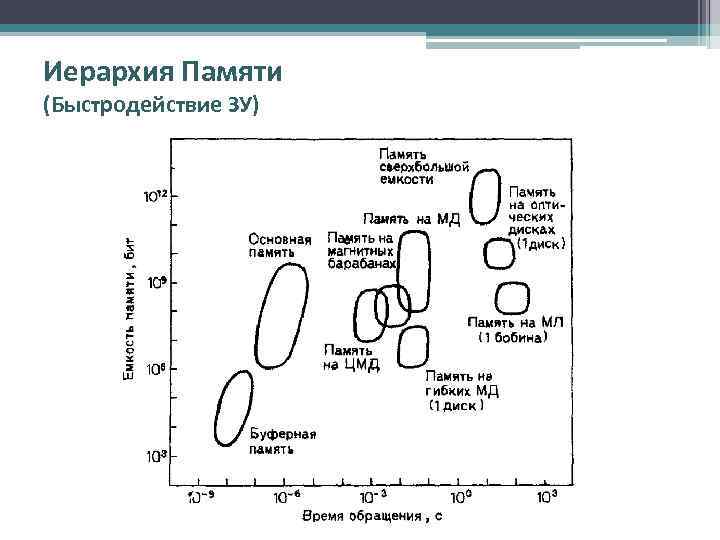

Иерархия Памяти (Быстродействие ЗУ)

Иерархия Памяти (Быстродействие ЗУ)

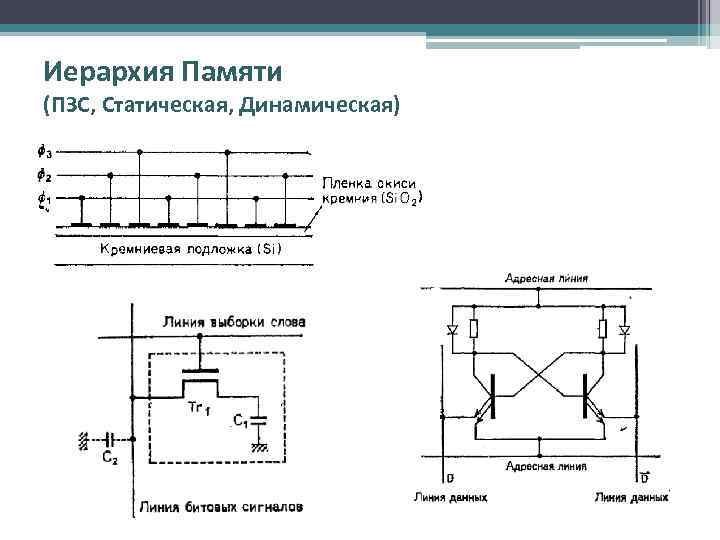

Иерархия Памяти (ПЗС, Статическая, Динамическая)

Иерархия Памяти (ПЗС, Статическая, Динамическая)

Иерархия Памяти (FLASH) Технологию предложила компания Toshiba более 30 лет назад Появилась же flash-память благодаря усилиям японских ученых. В 1984 г. компания Toshiba объявила о создании нового типа запоминающих устройств, а годом позже начала производство микросхем емкостью 256 Кbit. Правда, событие это, вероятно в силу малой востребованности в то время подобной памяти, не всколыхнуло мировую общественность. Второе рождение flash-микросхем произошло уже под брэндом Intel в 1988 г. , когда мировой гигант радиоэлектронной промышленности разработал собственный вариант flash-памяти. Однако в течение почти целого десятилетия новинка оставалась вещью, широко известной лишь в узких кругах инженеров-компьютерщиков. И только появление малогабаритных цифровых устройств, требовавших для своей работы значительных объемов памяти, стало началом роста популярности flash-устройств.

Иерархия Памяти (FLASH) Технологию предложила компания Toshiba более 30 лет назад Появилась же flash-память благодаря усилиям японских ученых. В 1984 г. компания Toshiba объявила о создании нового типа запоминающих устройств, а годом позже начала производство микросхем емкостью 256 Кbit. Правда, событие это, вероятно в силу малой востребованности в то время подобной памяти, не всколыхнуло мировую общественность. Второе рождение flash-микросхем произошло уже под брэндом Intel в 1988 г. , когда мировой гигант радиоэлектронной промышленности разработал собственный вариант flash-памяти. Однако в течение почти целого десятилетия новинка оставалась вещью, широко известной лишь в узких кругах инженеров-компьютерщиков. И только появление малогабаритных цифровых устройств, требовавших для своей работы значительных объемов памяти, стало началом роста популярности flash-устройств.

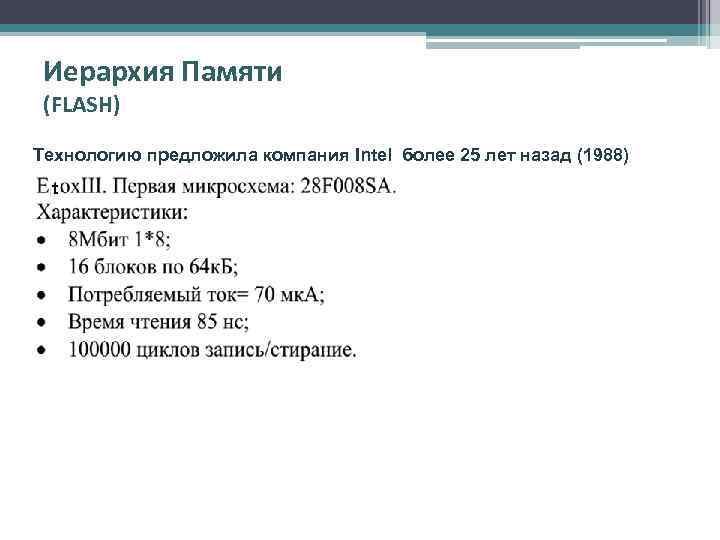

Иерархия Памяти (FLASH) Технологию предложила компания Intel более 25 лет назад (1988) t

Иерархия Памяти (FLASH) Технологию предложила компания Intel более 25 лет назад (1988) t

Иерархия Памяти (FLASH)

Иерархия Памяти (FLASH)

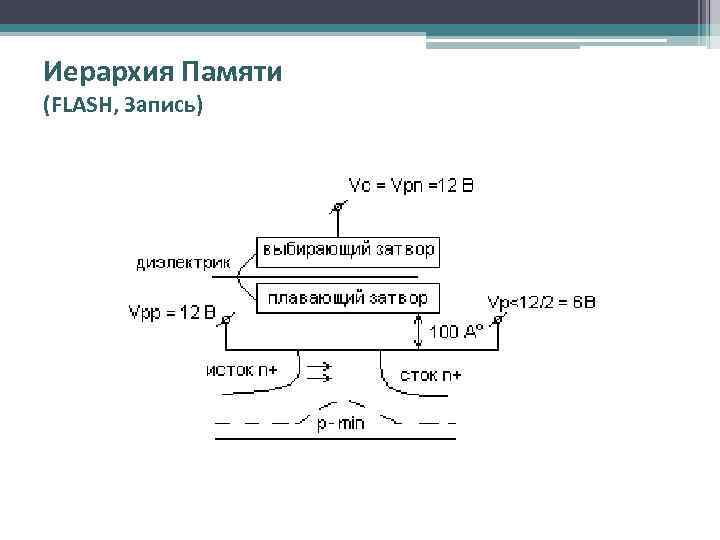

Иерархия Памяти (FLASH, Запись)

Иерархия Памяти (FLASH, Запись)

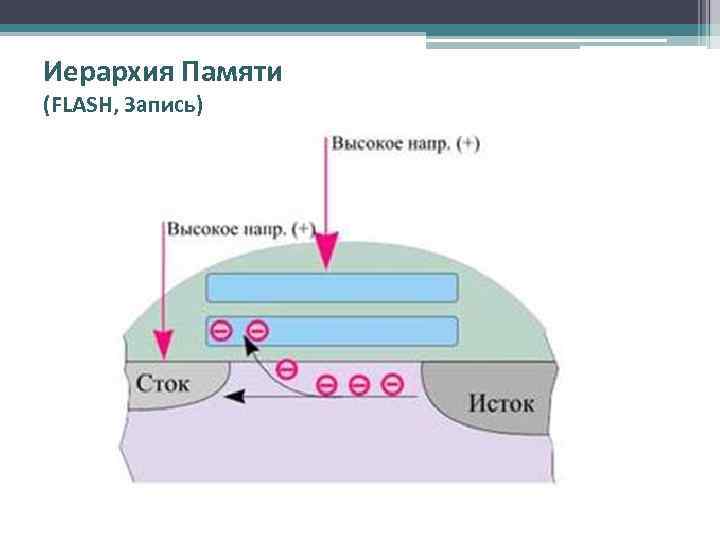

Иерархия Памяти (FLASH, Запись)

Иерархия Памяти (FLASH, Запись)

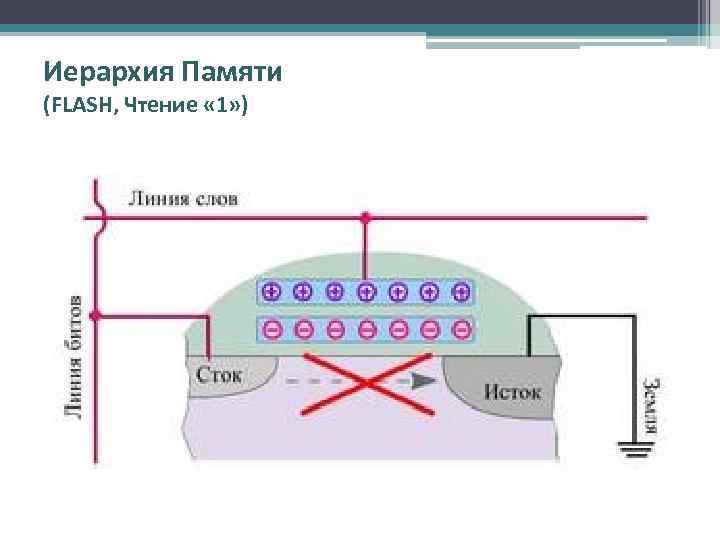

Иерархия Памяти (FLASH, Чтение « 1» )

Иерархия Памяти (FLASH, Чтение « 1» )

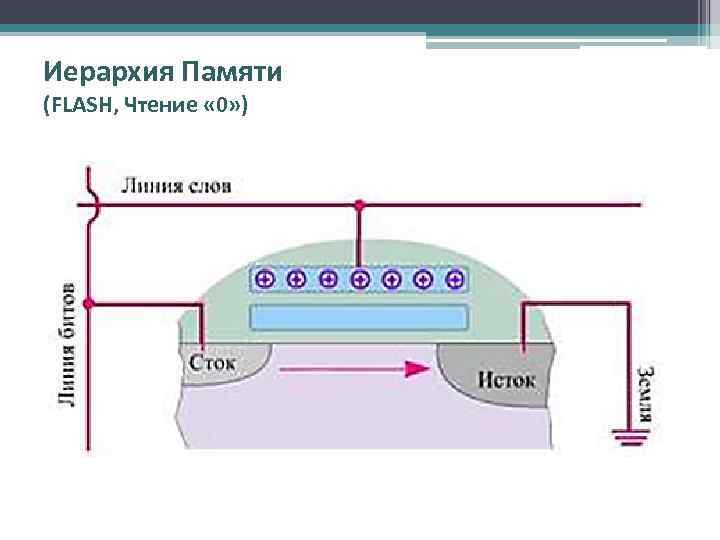

Иерархия Памяти (FLASH, Чтение « 0» )

Иерархия Памяти (FLASH, Чтение « 0» )

Иерархия Памяти (FLASH, Стирание)

Иерархия Памяти (FLASH, Стирание)

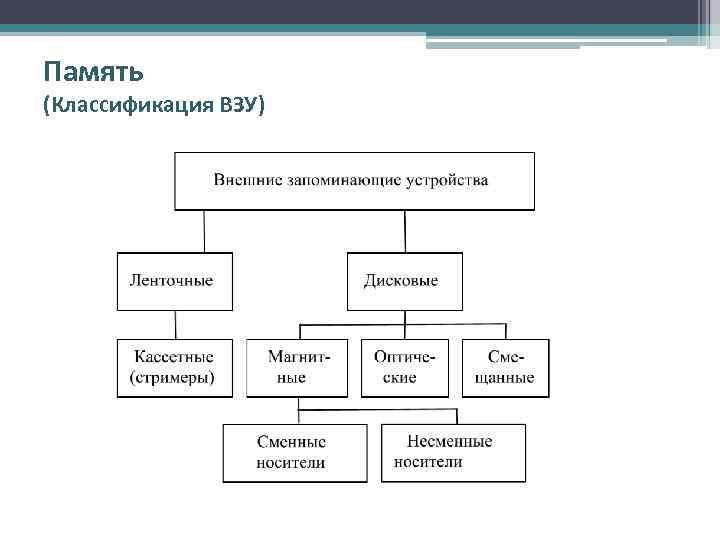

Память (Классификация ВЗУ)

Память (Классификация ВЗУ)

Иерархия Памяти (Магнитная память)

Иерархия Памяти (Магнитная память)

Иерархия Памяти (Магнитная память)

Иерархия Памяти (Магнитная память)

Иерархия Памяти (Магнитная память)

Иерархия Памяти (Магнитная память)

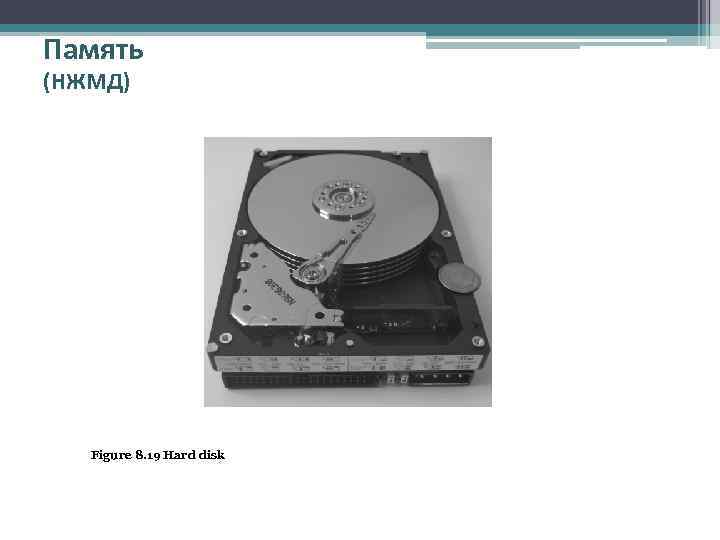

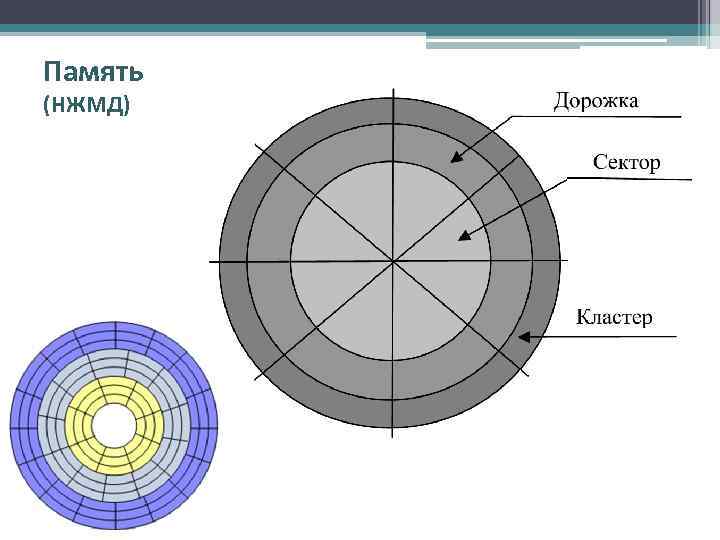

Память (НЖМД) Figure 8. 19 Hard disk

Память (НЖМД) Figure 8. 19 Hard disk

Память (НЖМД)

Память (НЖМД)

Память (НЖМД)

Память (НЖМД)

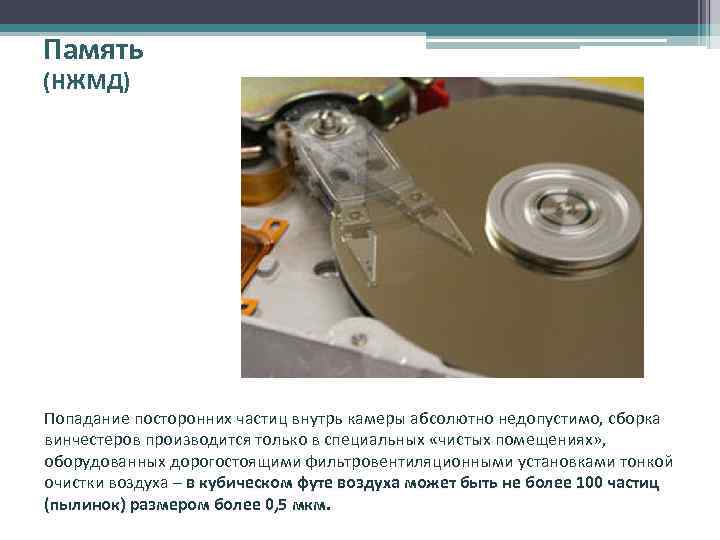

Память (НЖМД) Попадание посторонних частиц внутрь камеры абсолютно недопустимо, сборка винчестеров производится только в специальных «чистых помещениях» , оборудованных дорогостоящими фильтровентиляционными установками тонкой очистки воздуха – в кубическом футе воздуха может быть не более 100 частиц (пылинок) размером более 0, 5 мкм.

Память (НЖМД) Попадание посторонних частиц внутрь камеры абсолютно недопустимо, сборка винчестеров производится только в специальных «чистых помещениях» , оборудованных дорогостоящими фильтровентиляционными установками тонкой очистки воздуха – в кубическом футе воздуха может быть не более 100 частиц (пылинок) размером более 0, 5 мкм.

Память НЖМД Гермоблок Внутренний объем не изолирован от внешней среды – обязательно предусматривается возможность перетока воздуха снаружи в камеру и наоборот. Это необходимо для выравнивания давления внутри камеры с внешним давлением для предотвращения деформаций корпуса. Достигается это с помощью так называемого барометрического фильтра, размещаемого фильтра внутри камеры. Фильтр способен задерживать частицы, размер которых превышает величину рабочего зазора между головкой и поверхностью диска. Кроме того, в камере винчестера обязательно размещается фильтр рециркуляции, предназначенный для улавливания частиц, которые могут возникать внутри самой камеры, например за счет осыпания поверхности дисков при «взлетах» и «посадках» головок в зоне парковки, или проникать внутрь камеры через барометрический фильтр.

Память НЖМД Гермоблок Внутренний объем не изолирован от внешней среды – обязательно предусматривается возможность перетока воздуха снаружи в камеру и наоборот. Это необходимо для выравнивания давления внутри камеры с внешним давлением для предотвращения деформаций корпуса. Достигается это с помощью так называемого барометрического фильтра, размещаемого фильтра внутри камеры. Фильтр способен задерживать частицы, размер которых превышает величину рабочего зазора между головкой и поверхностью диска. Кроме того, в камере винчестера обязательно размещается фильтр рециркуляции, предназначенный для улавливания частиц, которые могут возникать внутри самой камеры, например за счет осыпания поверхности дисков при «взлетах» и «посадках» головок в зоне парковки, или проникать внутрь камеры через барометрический фильтр.

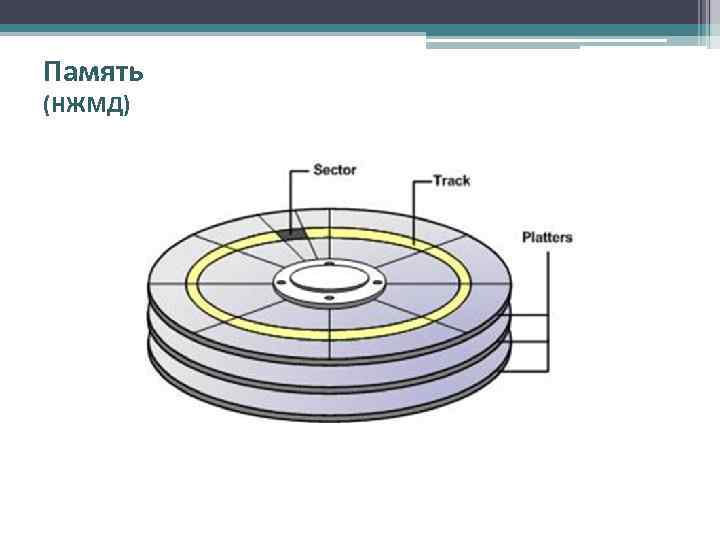

Память (НЖМД)

Память (НЖМД)

Память (НЖМД)

Память (НЖМД)

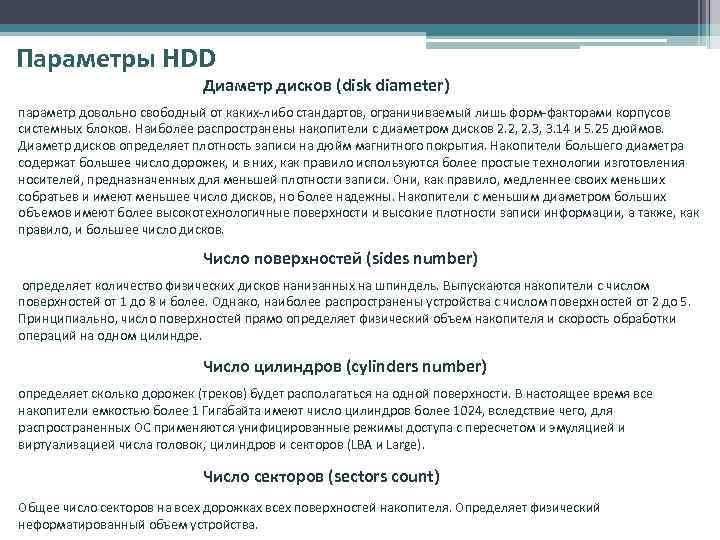

Параметры HDD Диаметр дисков (disk diameter) параметр довольно свободный от каких-либо стандартов, ограничиваемый лишь форм-факторами корпусов системных блоков. Наиболее распространены накопители с диаметром дисков 2. 2, 2. 3, 3. 14 и 5. 25 дюймов. Диаметр дисков определяет плотность записи на дюйм магнитного покрытия. Накопители большего диаметра содержат большее число дорожек, и в них, как правило используются более простые технологии изготовления носителей, предназначенных для меньшей плотности записи. Они, как правило, медленнее своих меньших собратьев и имеют меньшее число дисков, но более надежны. Накопители с меньшим диаметром больших объемов имеют более высокотехнологичные поверхности и высокие плотности записи информации, а также, как правило, и большее число дисков. Число поверхностей (sides number) определяет количество физических дисков нанизанных на шпиндель. Выпускаются накопители с числом поверхностей от 1 до 8 и более. Однако, наиболее распространены устройства с числом поверхностей от 2 до 5. Принципиально, число поверхностей прямо определяет физический объем накопителя и скорость обработки операций на одном цилиндре. Число цилиндров (cylinders number) определяет сколько дорожек (треков) будет располагаться на одной поверхности. В настоящее время все накопители емкостью более 1 Гигабайта имеют число цилиндров более 1024, вследствие чего, для распространенных ОС применяются унифицированные режимы доступа с пересчетом и эмуляцией и виртуализацией числа головок, цилиндров и секторов (LBA и Large). Число секторов (sectors count) Общее число секторов на всех дорожках всех поверхностей накопителя. Определяет физический неформатированный объем устройства.

Параметры HDD Диаметр дисков (disk diameter) параметр довольно свободный от каких-либо стандартов, ограничиваемый лишь форм-факторами корпусов системных блоков. Наиболее распространены накопители с диаметром дисков 2. 2, 2. 3, 3. 14 и 5. 25 дюймов. Диаметр дисков определяет плотность записи на дюйм магнитного покрытия. Накопители большего диаметра содержат большее число дорожек, и в них, как правило используются более простые технологии изготовления носителей, предназначенных для меньшей плотности записи. Они, как правило, медленнее своих меньших собратьев и имеют меньшее число дисков, но более надежны. Накопители с меньшим диаметром больших объемов имеют более высокотехнологичные поверхности и высокие плотности записи информации, а также, как правило, и большее число дисков. Число поверхностей (sides number) определяет количество физических дисков нанизанных на шпиндель. Выпускаются накопители с числом поверхностей от 1 до 8 и более. Однако, наиболее распространены устройства с числом поверхностей от 2 до 5. Принципиально, число поверхностей прямо определяет физический объем накопителя и скорость обработки операций на одном цилиндре. Число цилиндров (cylinders number) определяет сколько дорожек (треков) будет располагаться на одной поверхности. В настоящее время все накопители емкостью более 1 Гигабайта имеют число цилиндров более 1024, вследствие чего, для распространенных ОС применяются унифицированные режимы доступа с пересчетом и эмуляцией и виртуализацией числа головок, цилиндров и секторов (LBA и Large). Число секторов (sectors count) Общее число секторов на всех дорожках всех поверхностей накопителя. Определяет физический неформатированный объем устройства.

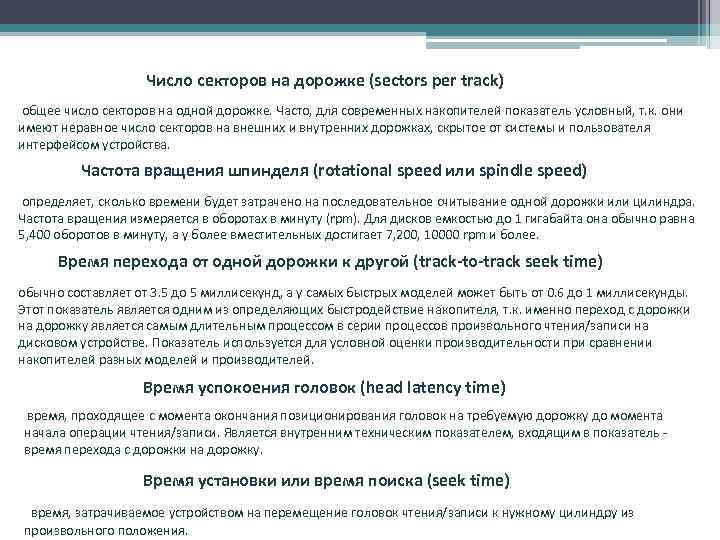

Число секторов на дорожке (sectors per track) общее число секторов на одной дорожке. Часто, для современных накопителей показатель условный, т. к. они имеют неравное число секторов на внешних и внутренних дорожках, скрытое от системы и пользователя интерфейсом устройства. Частота вращения шпинделя (rotational speed или spindle speed) определяет, сколько времени будет затрачено на последовательное считывание одной дорожки или цилиндра. Частота вращения измеряется в оборотах в минуту (rpm). Для дисков емкостью до 1 гигабайта она обычно равна 5, 400 оборотов в минуту, а у более вместительных достигает 7, 200, 10000 rpm и более. Время перехода от одной дорожки к другой (track-to-track seek time) обычно составляет от 3. 5 до 5 миллисекунд, а у самых быстрых моделей может быть от 0. 6 до 1 миллисекунды. Этот показатель является одним из определяющих быстродействие накопителя, т. к. именно переход с дорожки на дорожку является самым длительным процессом в серии процессов произвольного чтения/записи на дисковом устройстве. Показатель используется для условной оценки производительности при сравнении накопителей разных моделей и производителей. Время успокоения головок (head latency time) время, проходящее с момента окончания позиционирования головок на требуемую дорожку до момента начала операции чтения/записи. Является внутренним техническим показателем, входящим в показатель время перехода с дорожки на дорожку. Время установки или время поиска (seek time) время, затрачиваемое устройством на перемещение головок чтения/записи к нужному цилиндру из произвольного положения.

Число секторов на дорожке (sectors per track) общее число секторов на одной дорожке. Часто, для современных накопителей показатель условный, т. к. они имеют неравное число секторов на внешних и внутренних дорожках, скрытое от системы и пользователя интерфейсом устройства. Частота вращения шпинделя (rotational speed или spindle speed) определяет, сколько времени будет затрачено на последовательное считывание одной дорожки или цилиндра. Частота вращения измеряется в оборотах в минуту (rpm). Для дисков емкостью до 1 гигабайта она обычно равна 5, 400 оборотов в минуту, а у более вместительных достигает 7, 200, 10000 rpm и более. Время перехода от одной дорожки к другой (track-to-track seek time) обычно составляет от 3. 5 до 5 миллисекунд, а у самых быстрых моделей может быть от 0. 6 до 1 миллисекунды. Этот показатель является одним из определяющих быстродействие накопителя, т. к. именно переход с дорожки на дорожку является самым длительным процессом в серии процессов произвольного чтения/записи на дисковом устройстве. Показатель используется для условной оценки производительности при сравнении накопителей разных моделей и производителей. Время успокоения головок (head latency time) время, проходящее с момента окончания позиционирования головок на требуемую дорожку до момента начала операции чтения/записи. Является внутренним техническим показателем, входящим в показатель время перехода с дорожки на дорожку. Время установки или время поиска (seek time) время, затрачиваемое устройством на перемещение головок чтения/записи к нужному цилиндру из произвольного положения.

Среднее время установки или поиска (average seek time) усредненный результат большого числа операций позиционирования на разные цилиндры, часто называют средним временем позиционирования. Среднее время поиска имеет тенденцию уменьшаться с увеличением емкости накопителя, т. к повышается плотность записи и увеличивается число поверхностей. Среднее время поиска является одним из важнейших показателей оценки производительности накопителей, используемых при их сравнении. Время ожидания (latency) время, необходимое для прохода нужного сектора к головке, усредненный показатель – среднее время ожидания (average latency), получаемое как среднее от многочисленных тестовых проходов. После успокоения головок на требуемом цилиндре контроллер ищет нужный сектор. При этом, последовательно считываются адресные идентификаторы каждого проходящего под головкой сектора на дорожке. В идеальном, с точки зрения производительности случае, под головкой сразу окажется нужный сектор, в плохом - окажется, что этот сектор только что "прошел" под головкой, и, до окончания процесса успокоения необходимо будет ждать полный оборот диска для завершения операции чтения/записи. Время доступа (access time) суммарное время, затрачиваемое на установку головок и ожидание сектора. Причем, наиболее долгим является промежуток времени установки головок. . Среднее время доступа к данным (average access time) время, проходящее с момента получения запроса на операцию чтения/записи от контроллера до физического осуществления операции - результат сложения среднего время поиска и среднего времени ожидания. Среднее время доступа зависит от того, как организовано хранение данных и насколько быстро позиционируются головки чтения записи на требуемую дорожку. Среднее время доступа – усредненный показатель от многочисленных тестовых проходов, и обычно, оно составляет от 10 до 18 миллисекунд

Среднее время установки или поиска (average seek time) усредненный результат большого числа операций позиционирования на разные цилиндры, часто называют средним временем позиционирования. Среднее время поиска имеет тенденцию уменьшаться с увеличением емкости накопителя, т. к повышается плотность записи и увеличивается число поверхностей. Среднее время поиска является одним из важнейших показателей оценки производительности накопителей, используемых при их сравнении. Время ожидания (latency) время, необходимое для прохода нужного сектора к головке, усредненный показатель – среднее время ожидания (average latency), получаемое как среднее от многочисленных тестовых проходов. После успокоения головок на требуемом цилиндре контроллер ищет нужный сектор. При этом, последовательно считываются адресные идентификаторы каждого проходящего под головкой сектора на дорожке. В идеальном, с точки зрения производительности случае, под головкой сразу окажется нужный сектор, в плохом - окажется, что этот сектор только что "прошел" под головкой, и, до окончания процесса успокоения необходимо будет ждать полный оборот диска для завершения операции чтения/записи. Время доступа (access time) суммарное время, затрачиваемое на установку головок и ожидание сектора. Причем, наиболее долгим является промежуток времени установки головок. . Среднее время доступа к данным (average access time) время, проходящее с момента получения запроса на операцию чтения/записи от контроллера до физического осуществления операции - результат сложения среднего время поиска и среднего времени ожидания. Среднее время доступа зависит от того, как организовано хранение данных и насколько быстро позиционируются головки чтения записи на требуемую дорожку. Среднее время доступа – усредненный показатель от многочисленных тестовых проходов, и обычно, оно составляет от 10 до 18 миллисекунд

определяет скорость, с которой данные считываются или записываются на диск после того, как головки займут необходимое положение. Измеряется в мегабайтах в секунду (MBps) или мегабитах в секунду (Mbps) и является характеристикой контроллера и интерфейса. Различают две разновидности скорости передачи - внешняя и внутренняя. Скорость передачи данных, также является одним из основных показателей производительности накопителя и используется для ее оценки и сравнения накопителей различных моделей и производителей. Размер кеш-буфера контроллера (internal cash size) Встроенный в накопитель буфер выполняет функцию упреждающего кэширования и призван сгладить громадную разницу в быстродействии между дисковой и оперативной памятью компьютера. Выпускаются накопители с 128, 256 и 512 килобайтным буфером. Чем больше объем буфера, тем потенциально выше производительность при произвольном "длинном" чтении/записи. Средняя потребляемая мощность (capacity). При сборке мощных настольных компьютеров учитывается мощность, потребляемая всеми его устройствами. Современные накопители на ЖД потребляют от 5 до 15 Ватт, что является достаточно приемлемым, хотя, при всех остальных равных условиях, накопители с меньшей потребляемой мощностью выглядат более привлекательно Уровень шума (noise level) разумеется, является эргономическим показателем. Однако, он также, является и некоторым показателем сбалансированности механической конструкции, т. к. шум в виде треска - есть не что иное как звук ударов позиционера шагового или линейного механизма, а, даже микро- удары и вибрация так не желательны для накопителей и приводят к более быстрому их износу. Среднее время наработки на отказ (MTBF) определяет сколько времени способен проработать накопитель без сбоев Сопротивляемость ударам (G-shock rating) определяет степень сопротивляемости накопителя ударам и резким изменениям давления, измеряется в единицах допустимой перегрузки g во включенном и выключенном состоянии. Является важным показателем для настольных и мобильных систем.

определяет скорость, с которой данные считываются или записываются на диск после того, как головки займут необходимое положение. Измеряется в мегабайтах в секунду (MBps) или мегабитах в секунду (Mbps) и является характеристикой контроллера и интерфейса. Различают две разновидности скорости передачи - внешняя и внутренняя. Скорость передачи данных, также является одним из основных показателей производительности накопителя и используется для ее оценки и сравнения накопителей различных моделей и производителей. Размер кеш-буфера контроллера (internal cash size) Встроенный в накопитель буфер выполняет функцию упреждающего кэширования и призван сгладить громадную разницу в быстродействии между дисковой и оперативной памятью компьютера. Выпускаются накопители с 128, 256 и 512 килобайтным буфером. Чем больше объем буфера, тем потенциально выше производительность при произвольном "длинном" чтении/записи. Средняя потребляемая мощность (capacity). При сборке мощных настольных компьютеров учитывается мощность, потребляемая всеми его устройствами. Современные накопители на ЖД потребляют от 5 до 15 Ватт, что является достаточно приемлемым, хотя, при всех остальных равных условиях, накопители с меньшей потребляемой мощностью выглядат более привлекательно Уровень шума (noise level) разумеется, является эргономическим показателем. Однако, он также, является и некоторым показателем сбалансированности механической конструкции, т. к. шум в виде треска - есть не что иное как звук ударов позиционера шагового или линейного механизма, а, даже микро- удары и вибрация так не желательны для накопителей и приводят к более быстрому их износу. Среднее время наработки на отказ (MTBF) определяет сколько времени способен проработать накопитель без сбоев Сопротивляемость ударам (G-shock rating) определяет степень сопротивляемости накопителя ударам и резким изменениям давления, измеряется в единицах допустимой перегрузки g во включенном и выключенном состоянии. Является важным показателем для настольных и мобильных систем.

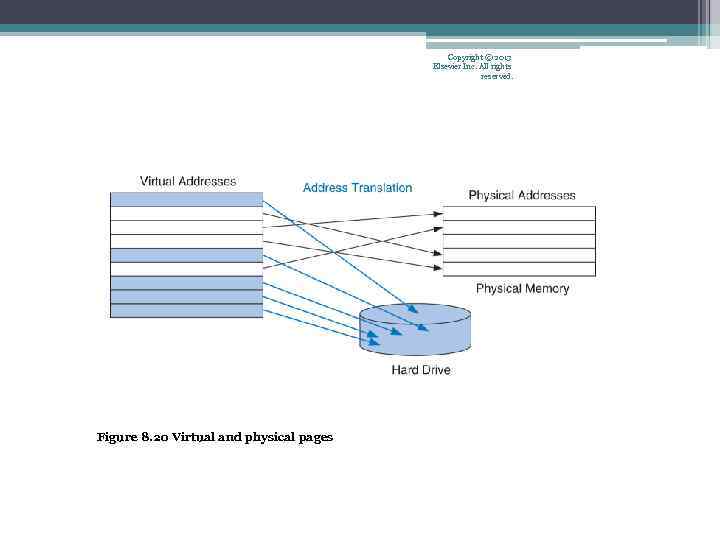

Copyright © 2013 Elsevier Inc. All rights reserved. Figure 8. 20 Virtual and physical pages

Copyright © 2013 Elsevier Inc. All rights reserved. Figure 8. 20 Virtual and physical pages

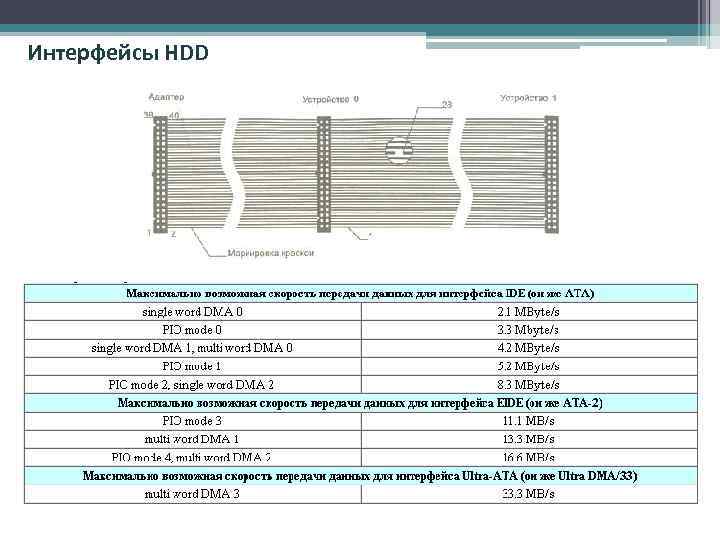

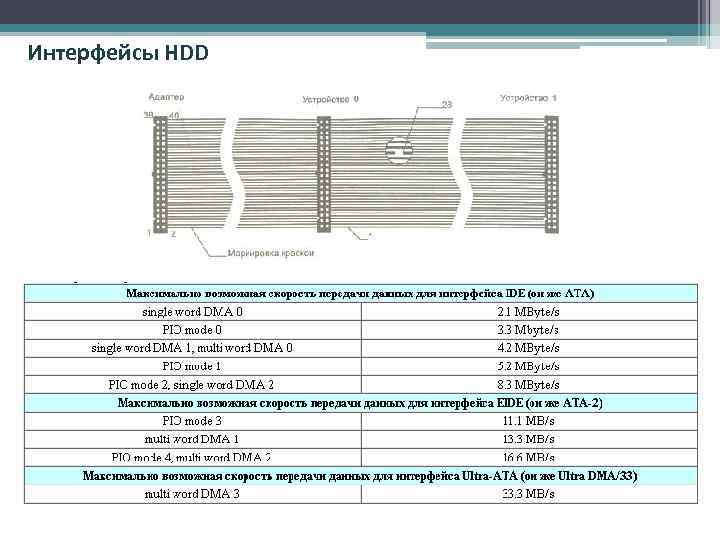

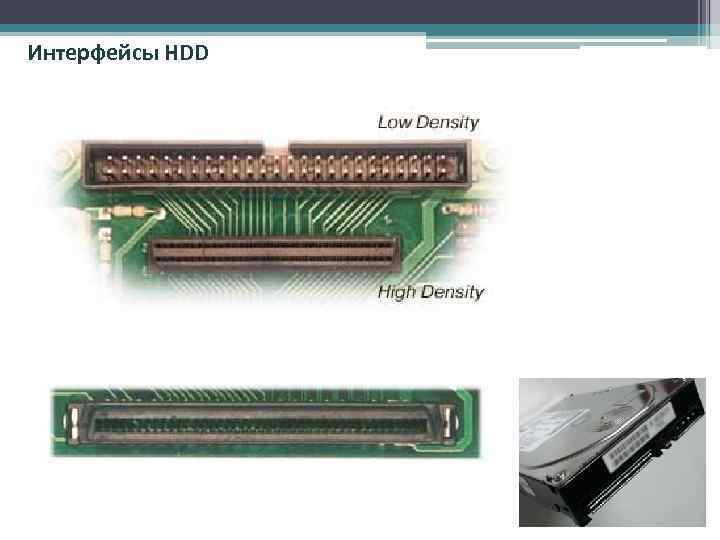

Интерфейсы HDD Интерфейсом накопителей называется набор АС, обеспечивающий обмен информацией между контроллером устройства (кеш-буфером) и компьютером. В настоящее время в настольных ПК IBM-PC, чаще других, используются три разновидности интерфейсов: • Integrated Drive Electronics - IDE, Enhanced Integrated Drive Electronics - EIDE • SCSI (Small Computers System Interface) • SATA (Serial ATA) Интерфейс IDE Для подключения устройств IDE существует несколько разновидностей интерфейса: • ATA (AT Attachment), он же AT-BUS - 16 -битный интерфейс подключения к шине компьютера AT. В настоящее время это наиболее распространенный 40 -проводной сигнальный и 4 -проводной питающий интерфейс для подключения дисковых накопителей к компьютерам класса AT. Для миниатюрных (2, 5" и меньших) накопителей используют 44 -проводной кабель, по которому передается и питание. • PC Card ATA - 16 -битный интерфейс с 68 -контактным разъемом PC Card (PCMCIA) для подключения к блокнотным ПК. • XT IDE (8 -бит), он же XT-BUS - 40 -проводной интерфейс, похожий на ATA, но несовместимый с ним. • MCA IDE (16 -бит) - 72 -проводный интерфейс, предназначенный специально для шины и накопителей PS/2. Как и компьютеры PS/2, по крайней мере в нашей стране устройства с этим интерфейсом встречаются редко. • ATA-2 - расширенная спецификация ATA, включает 2 канала, 4 устройства, PIO Mode 3, multiword DMA mode 1, Block mode, объем диска до 8 Гбайт, поддержка LBA и CHS. • Fast ATA-2 разрешает использовать Multiword DMA Mode 2 (13, 3 Mбайт/с), PIO Mode 4. • ATA-3 - расширение ATA-2. Включает средства парольной защиты, улучшенного управления питанием, самотестирования с предупреждением приближения отказа - SMART (Self Monitoring Analysis and Report Technology). • ATA/ATAPI-4 - расширение ATA-3, включающее режим Ultra DMA со скоростью обмена до 33 Мбайт/с и пакетный интерфейс ATAPI. • E-IDE (Enhanced IDE) - расширенный интерфейс, введенный фирмой Western Digital. Реализуется в адаптерах для шин PCI и VLB, позволяющий подключать до 4 устройств (к двум каналам), включая CD-ROM и стриммеры (ATAPI). Поддерживает PIO Mode 3, multiword DMA mode 1, объем диска до 8 Гбайт, LBA и CHS. С аппаратной точки зрения практически полностью соответствует спецификации ATA-2.

Интерфейсы HDD Интерфейсом накопителей называется набор АС, обеспечивающий обмен информацией между контроллером устройства (кеш-буфером) и компьютером. В настоящее время в настольных ПК IBM-PC, чаще других, используются три разновидности интерфейсов: • Integrated Drive Electronics - IDE, Enhanced Integrated Drive Electronics - EIDE • SCSI (Small Computers System Interface) • SATA (Serial ATA) Интерфейс IDE Для подключения устройств IDE существует несколько разновидностей интерфейса: • ATA (AT Attachment), он же AT-BUS - 16 -битный интерфейс подключения к шине компьютера AT. В настоящее время это наиболее распространенный 40 -проводной сигнальный и 4 -проводной питающий интерфейс для подключения дисковых накопителей к компьютерам класса AT. Для миниатюрных (2, 5" и меньших) накопителей используют 44 -проводной кабель, по которому передается и питание. • PC Card ATA - 16 -битный интерфейс с 68 -контактным разъемом PC Card (PCMCIA) для подключения к блокнотным ПК. • XT IDE (8 -бит), он же XT-BUS - 40 -проводной интерфейс, похожий на ATA, но несовместимый с ним. • MCA IDE (16 -бит) - 72 -проводный интерфейс, предназначенный специально для шины и накопителей PS/2. Как и компьютеры PS/2, по крайней мере в нашей стране устройства с этим интерфейсом встречаются редко. • ATA-2 - расширенная спецификация ATA, включает 2 канала, 4 устройства, PIO Mode 3, multiword DMA mode 1, Block mode, объем диска до 8 Гбайт, поддержка LBA и CHS. • Fast ATA-2 разрешает использовать Multiword DMA Mode 2 (13, 3 Mбайт/с), PIO Mode 4. • ATA-3 - расширение ATA-2. Включает средства парольной защиты, улучшенного управления питанием, самотестирования с предупреждением приближения отказа - SMART (Self Monitoring Analysis and Report Technology). • ATA/ATAPI-4 - расширение ATA-3, включающее режим Ultra DMA со скоростью обмена до 33 Мбайт/с и пакетный интерфейс ATAPI. • E-IDE (Enhanced IDE) - расширенный интерфейс, введенный фирмой Western Digital. Реализуется в адаптерах для шин PCI и VLB, позволяющий подключать до 4 устройств (к двум каналам), включая CD-ROM и стриммеры (ATAPI). Поддерживает PIO Mode 3, multiword DMA mode 1, объем диска до 8 Гбайт, LBA и CHS. С аппаратной точки зрения практически полностью соответствует спецификации ATA-2.

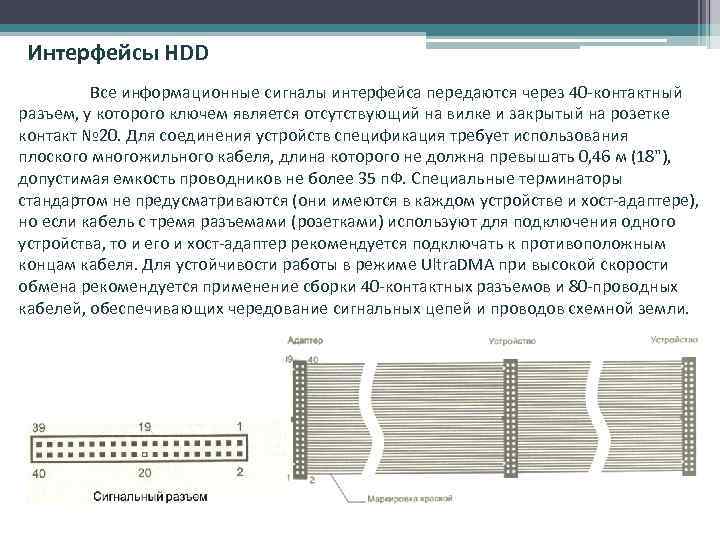

Интерфейсы HDD Все информационные сигналы интерфейса передаются через 40 -контактный разъем, у которого ключем является отсутствующий на вилке и закрытый на розетке контакт № 20. Для соединения устройств спецификация требует использования плоского многожильного кабеля, длина которого не должна превышать 0, 46 м (18"), допустимая емкость проводников не более 35 п. Ф. Специальные терминаторы стандартом не предусматриваются (они имеются в каждом устройстве и хост-адаптере), но если кабель с тремя разъемами (розетками) используют для подключения одного устройства, то и его и хост-адаптер рекомендуется подключать к противоположным концам кабеля. Для устойчивости работы в режиме Ultra. DMA при высокой скорости обмена рекомендуется применение сборки 40 -контактных разъемов и 80 -проводных кабелей, обеспечивающих чередование сигнальных цепей и проводов схемной земли.

Интерфейсы HDD Все информационные сигналы интерфейса передаются через 40 -контактный разъем, у которого ключем является отсутствующий на вилке и закрытый на розетке контакт № 20. Для соединения устройств спецификация требует использования плоского многожильного кабеля, длина которого не должна превышать 0, 46 м (18"), допустимая емкость проводников не более 35 п. Ф. Специальные терминаторы стандартом не предусматриваются (они имеются в каждом устройстве и хост-адаптере), но если кабель с тремя разъемами (розетками) используют для подключения одного устройства, то и его и хост-адаптер рекомендуется подключать к противоположным концам кабеля. Для устойчивости работы в режиме Ultra. DMA при высокой скорости обмена рекомендуется применение сборки 40 -контактных разъемов и 80 -проводных кабелей, обеспечивающих чередование сигнальных цепей и проводов схемной земли.

Интерфейсы HDD

Интерфейсы HDD

Интерфейсы HDD

Интерфейсы HDD

Интерфейсы HDD

Интерфейсы HDD

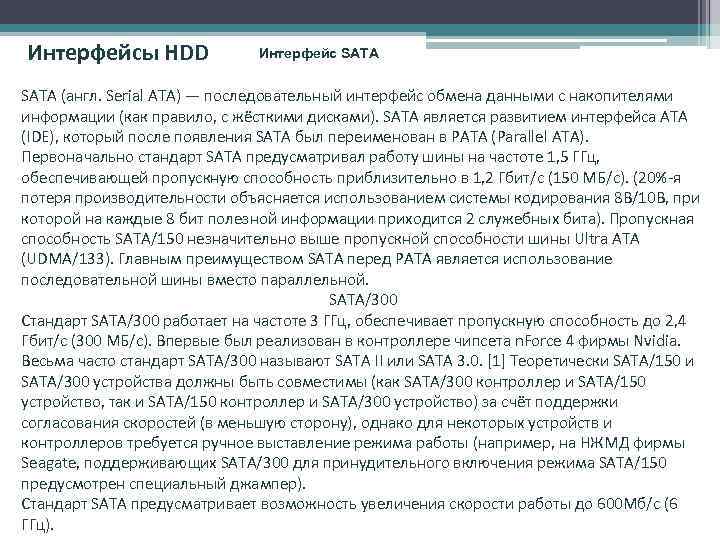

Интерфейсы HDD Интерфейс SATA (англ. Serial ATA) — последовательный интерфейс обмена данными с накопителями информации (как правило, с жёсткими дисками). SATA является развитием интерфейса ATA (IDE), который после появления SATA был переименован в PATA (Parallel ATA). Первоначально стандарт SATA предусматривал работу шины на частоте 1, 5 ГГц, обеспечивающей пропускную способность приблизительно в 1, 2 Гбит/с (150 МБ/с). (20%-я потеря производительности объясняется использованием системы кодирования 8 B/10 B, при которой на каждые 8 бит полезной информации приходится 2 служебных бита). Пропускная способность SATA/150 незначительно выше пропускной способности шины Ultra ATA (UDMA/133). Главным преимуществом SATA перед PATA является использование последовательной шины вместо параллельной. SATA/300 Стандарт SATA/300 работает на частоте 3 ГГц, обеспечивает пропускную способность до 2, 4 Гбит/с (300 МБ/с). Впервые был реализован в контроллере чипсета n. Force 4 фирмы Nvidia. Весьма часто стандарт SATA/300 называют SATA II или SATA 3. 0. [1] Теоретически SATA/150 и SATA/300 устройства должны быть совместимы (как SATA/300 контроллер и SATA/150 устройство, так и SATA/150 контроллер и SATA/300 устройство) за счёт поддержки согласования скоростей (в меньшую сторону), однако для некоторых устройств и контроллеров требуется ручное выставление режима работы (например, на НЖМД фирмы Seagate, поддерживающих SATA/300 для принудительного включения режима SATA/150 предусмотрен специальный джампер). Стандарт SATA предусматривает возможность увеличения скорости работы до 600 Мб/с (6 ГГц).

Интерфейсы HDD Интерфейс SATA (англ. Serial ATA) — последовательный интерфейс обмена данными с накопителями информации (как правило, с жёсткими дисками). SATA является развитием интерфейса ATA (IDE), который после появления SATA был переименован в PATA (Parallel ATA). Первоначально стандарт SATA предусматривал работу шины на частоте 1, 5 ГГц, обеспечивающей пропускную способность приблизительно в 1, 2 Гбит/с (150 МБ/с). (20%-я потеря производительности объясняется использованием системы кодирования 8 B/10 B, при которой на каждые 8 бит полезной информации приходится 2 служебных бита). Пропускная способность SATA/150 незначительно выше пропускной способности шины Ultra ATA (UDMA/133). Главным преимуществом SATA перед PATA является использование последовательной шины вместо параллельной. SATA/300 Стандарт SATA/300 работает на частоте 3 ГГц, обеспечивает пропускную способность до 2, 4 Гбит/с (300 МБ/с). Впервые был реализован в контроллере чипсета n. Force 4 фирмы Nvidia. Весьма часто стандарт SATA/300 называют SATA II или SATA 3. 0. [1] Теоретически SATA/150 и SATA/300 устройства должны быть совместимы (как SATA/300 контроллер и SATA/150 устройство, так и SATA/150 контроллер и SATA/300 устройство) за счёт поддержки согласования скоростей (в меньшую сторону), однако для некоторых устройств и контроллеров требуется ручное выставление режима работы (например, на НЖМД фирмы Seagate, поддерживающих SATA/300 для принудительного включения режима SATA/150 предусмотрен специальный джампер). Стандарт SATA предусматривает возможность увеличения скорости работы до 600 Мб/с (6 ГГц).

Figure 8. 72 SATA cable

Figure 8. 72 SATA cable

Интерфейсы HDD SATA использует 7 -контактный разъём вместо 40 -контактного разъёма у PATA. SATA-кабель имеет меньшую площадь, за счёт чего уменьшается сопротивление воздуху, обдувающему комплектующие компьютера; улучшается охлаждение системы. SATA-кабель за счёт своей формы более устойчив к многократному подключению. Питающий шнур SATA так же разработан с учётом многократных подключений. Разъём питания SATA подаёт 3 напряжения питания: +12 В, +5 В и +3, 3 В; однако современные устройства могут работать без напряжения +3, 3 В, что даёт возможность использовать пассивный переходник с стандартного разъёма питания IDE на SATA. Ряд SATA устройств поставляется с двумя разъёмами питания: SATA и Molex. Стандарт SATA отказался от традиционного для PATA подключения по два устройства на шлейф; каждому устройству полагается отдельный кабель, что снижает задержки при одновременной работе двух устройств на одном кабеле, уменьшает возможные проблемы при сборке (проблема конфликта Slave/Master устройств для SATA отсутствует), устраняет возможность ошибок при использовании нетерминированных PATA-шлейфов. Стандарт SATA предусматривает горячую замену устройств и функцию очереди команд (NCQ). SATA устройства используют два разъёма — один, семи контактный, для подключения шины данных и второй, 15 -ти контактный, для подключения питания. Стандарт SATA предусматривает возможность использовать вместо 15 -ти контактного разъёма питания стандартный 4 -х контактный разъём Molex. Использование одновременно обоих типов силовых разъёмов может привести к повреждению устройства.

Интерфейсы HDD SATA использует 7 -контактный разъём вместо 40 -контактного разъёма у PATA. SATA-кабель имеет меньшую площадь, за счёт чего уменьшается сопротивление воздуху, обдувающему комплектующие компьютера; улучшается охлаждение системы. SATA-кабель за счёт своей формы более устойчив к многократному подключению. Питающий шнур SATA так же разработан с учётом многократных подключений. Разъём питания SATA подаёт 3 напряжения питания: +12 В, +5 В и +3, 3 В; однако современные устройства могут работать без напряжения +3, 3 В, что даёт возможность использовать пассивный переходник с стандартного разъёма питания IDE на SATA. Ряд SATA устройств поставляется с двумя разъёмами питания: SATA и Molex. Стандарт SATA отказался от традиционного для PATA подключения по два устройства на шлейф; каждому устройству полагается отдельный кабель, что снижает задержки при одновременной работе двух устройств на одном кабеле, уменьшает возможные проблемы при сборке (проблема конфликта Slave/Master устройств для SATA отсутствует), устраняет возможность ошибок при использовании нетерминированных PATA-шлейфов. Стандарт SATA предусматривает горячую замену устройств и функцию очереди команд (NCQ). SATA устройства используют два разъёма — один, семи контактный, для подключения шины данных и второй, 15 -ти контактный, для подключения питания. Стандарт SATA предусматривает возможность использовать вместо 15 -ти контактного разъёма питания стандартный 4 -х контактный разъём Molex. Использование одновременно обоих типов силовых разъёмов может привести к повреждению устройства.

Память (НЖМД) Figure 8. 19 Hard disk

Память (НЖМД) Figure 8. 19 Hard disk

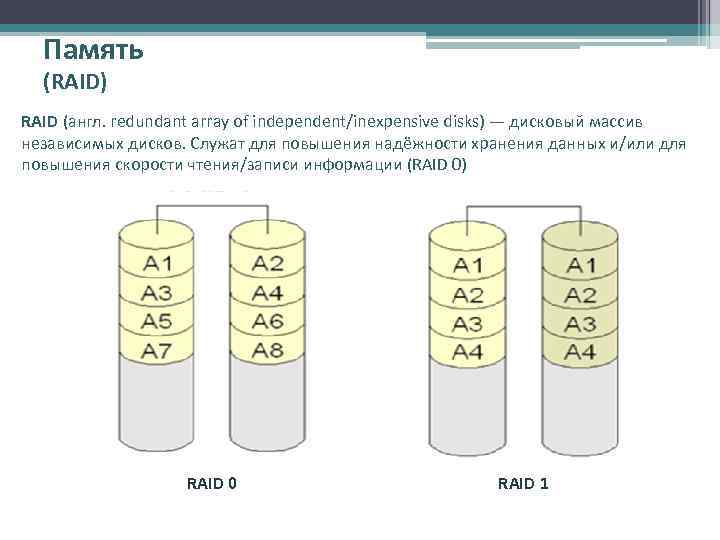

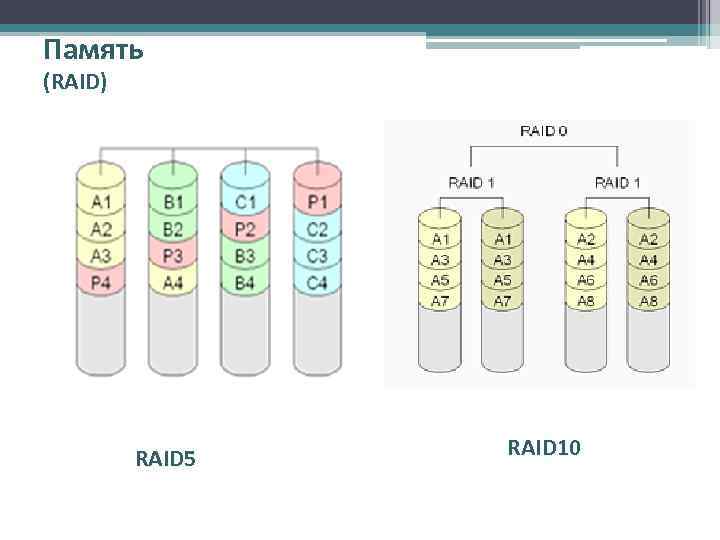

Память (RAID) RAID (англ. redundant array of independent/inexpensive disks) — дисковый массив независимых дисков. Служат для повышения надёжности хранения данных и/или для повышения скорости чтения/записи информации (RAID 0) RAID 0 RAID 1

Память (RAID) RAID (англ. redundant array of independent/inexpensive disks) — дисковый массив независимых дисков. Служат для повышения надёжности хранения данных и/или для повышения скорости чтения/записи информации (RAID 0) RAID 0 RAID 1

Память (RAID) RAID 0 ( «Striping» ) — дисковый массив с отсутствием избыточности. Информация записывается сквозь все диски последовательно, разбиваясь на блоки данных (Ai). За счёт этого существенно повышается производительность, но страдает надёжность всего массива. (При выходе из строя любого из входящих в RAID 0 винчестеров полностью и безвозвратно пропадает вся информация). В соответствии с теорией вероятности, надёжность массива RAID 0 равна произведению надёжностей составляющих его дисков, каждая из которых меньше единицы, т. о. совокупная надёжность заведомо ниже надёжности любого из дисков. RAID 0 может быть реализован как программно так и аппаратно RAID 1 (Mirroring — «зеркало» ). отказоустойчивый массив из пары дисков. При записи данные с первого диска дублируются на втором (так называемое зеркалирование). Это эффективное и сравнительно простое в реализации решение обладает существенным недостатком — объем дискового пространства массива равен емкости наименьшего диска (например, если объединить в RAID 1 диски на 30 и 40 Гбайт, то доступно будет только 30 Гбайт). Имеет защиту от выхода из строя половины имеющихся аппаратных средств (в частном случае — одного из двух жёстких дисков), обеспечивает приемлемую скорость записи и выигрыш по скорости чтения за счёт распараллеливания запросов. Зеркало на многих дисках — RAID 1+0. При использовании такого уровня 1+0 зеркальные пары дисков выстраиваются в «цепочку» , поэтому объём полученного тома может превосходить ёмкость одного жёсткого диска.

Память (RAID) RAID 0 ( «Striping» ) — дисковый массив с отсутствием избыточности. Информация записывается сквозь все диски последовательно, разбиваясь на блоки данных (Ai). За счёт этого существенно повышается производительность, но страдает надёжность всего массива. (При выходе из строя любого из входящих в RAID 0 винчестеров полностью и безвозвратно пропадает вся информация). В соответствии с теорией вероятности, надёжность массива RAID 0 равна произведению надёжностей составляющих его дисков, каждая из которых меньше единицы, т. о. совокупная надёжность заведомо ниже надёжности любого из дисков. RAID 0 может быть реализован как программно так и аппаратно RAID 1 (Mirroring — «зеркало» ). отказоустойчивый массив из пары дисков. При записи данные с первого диска дублируются на втором (так называемое зеркалирование). Это эффективное и сравнительно простое в реализации решение обладает существенным недостатком — объем дискового пространства массива равен емкости наименьшего диска (например, если объединить в RAID 1 диски на 30 и 40 Гбайт, то доступно будет только 30 Гбайт). Имеет защиту от выхода из строя половины имеющихся аппаратных средств (в частном случае — одного из двух жёстких дисков), обеспечивает приемлемую скорость записи и выигрыш по скорости чтения за счёт распараллеливания запросов. Зеркало на многих дисках — RAID 1+0. При использовании такого уровня 1+0 зеркальные пары дисков выстраиваются в «цепочку» , поэтому объём полученного тома может превосходить ёмкость одного жёсткого диска.

Память (RAID) RAID 5 RAID 10

Память (RAID) RAID 5 RAID 10

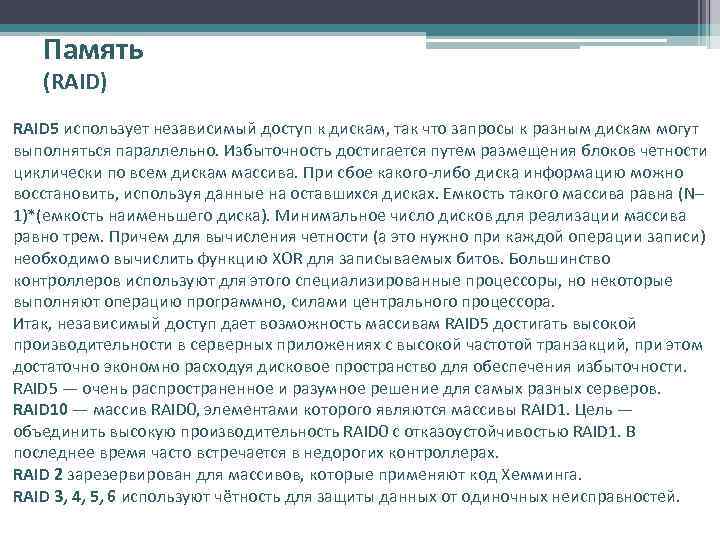

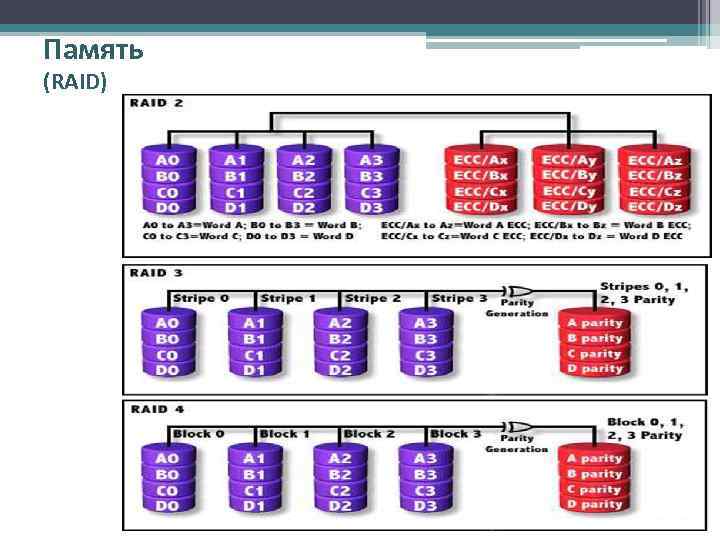

Память (RAID) RAID 5 использует независимый доступ к дискам, так что запросы к разным дискам могут выполняться параллельно. Избыточность достигается путем размещения блоков четности циклически по всем дискам массива. При сбое какого-либо диска информацию можно восстановить, используя данные на оставшихся дисках. Емкость такого массива равна (N– 1)*(емкость наименьшего диска). Минимальное число дисков для реализации массива равно трем. Причем для вычисления четности (а это нужно при каждой операции записи) необходимо вычислить функцию XOR для записываемых битов. Большинство контроллеров используют для этого специализированные процессоры, но некоторые выполняют операцию программно, силами центрального процессора. Итак, независимый доступ дает возможность массивам RAID 5 достигать высокой производительности в серверных приложениях с высокой частотой транзакций, при этом достаточно экономно расходуя дисковое пространство для обеспечения избыточности. RAID 5 — очень распространенное и разумное решение для самых разных серверов. RAID 10 — массив RAID 0, элементами которого являются массивы RAID 1. Цель — объединить высокую производительность RAID 0 с отказоустойчивостью RAID 1. В последнее время часто встречается в недорогих контроллерах. RAID 2 зарезервирован для массивов, которые применяют код Хемминга. RAID 3, 4, 5, 6 используют чётность для защиты данных от одиночных неисправностей.

Память (RAID) RAID 5 использует независимый доступ к дискам, так что запросы к разным дискам могут выполняться параллельно. Избыточность достигается путем размещения блоков четности циклически по всем дискам массива. При сбое какого-либо диска информацию можно восстановить, используя данные на оставшихся дисках. Емкость такого массива равна (N– 1)*(емкость наименьшего диска). Минимальное число дисков для реализации массива равно трем. Причем для вычисления четности (а это нужно при каждой операции записи) необходимо вычислить функцию XOR для записываемых битов. Большинство контроллеров используют для этого специализированные процессоры, но некоторые выполняют операцию программно, силами центрального процессора. Итак, независимый доступ дает возможность массивам RAID 5 достигать высокой производительности в серверных приложениях с высокой частотой транзакций, при этом достаточно экономно расходуя дисковое пространство для обеспечения избыточности. RAID 5 — очень распространенное и разумное решение для самых разных серверов. RAID 10 — массив RAID 0, элементами которого являются массивы RAID 1. Цель — объединить высокую производительность RAID 0 с отказоустойчивостью RAID 1. В последнее время часто встречается в недорогих контроллерах. RAID 2 зарезервирован для массивов, которые применяют код Хемминга. RAID 3, 4, 5, 6 используют чётность для защиты данных от одиночных неисправностей.

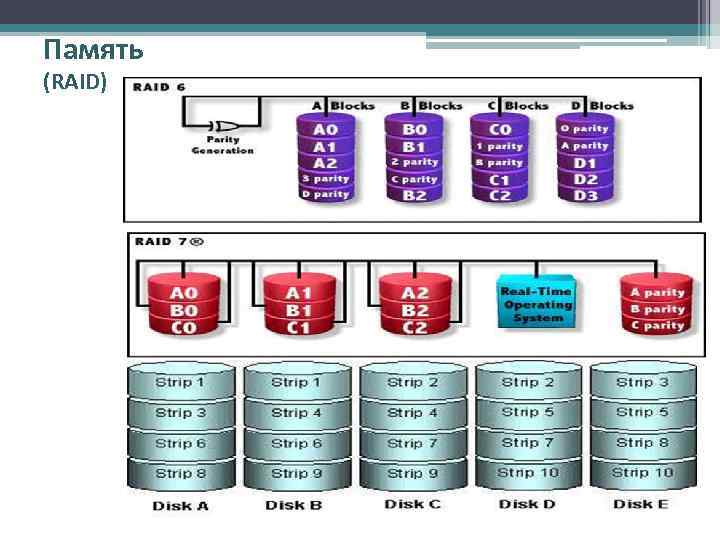

Память (RAID)

Память (RAID)

Память (RAID)

Память (RAID)

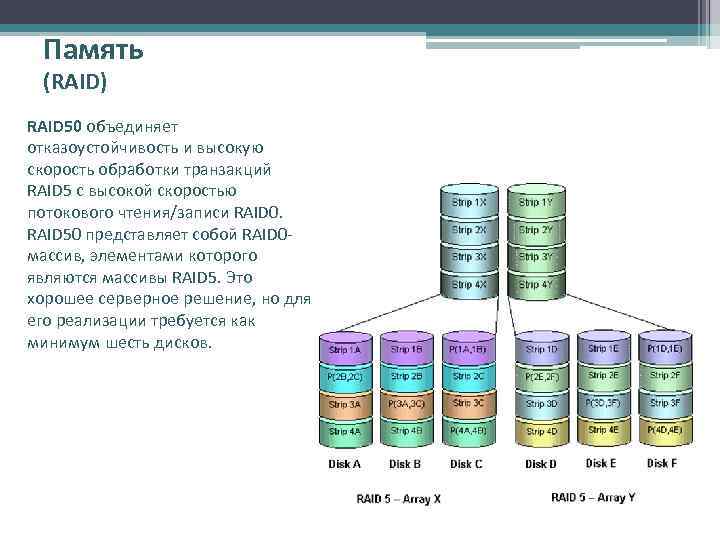

Память (RAID) RAID 50 объединяет отказоустойчивость и высокую скорость обработки транзакций RAID 5 с высокой скоростью потокового чтения/записи RAID 0. RAID 50 представляет собой RAID 0 массив, элементами которого являются массивы RAID 5. Это хорошее серверное решение, но для его реализации требуется как минимум шесть дисков.

Память (RAID) RAID 50 объединяет отказоустойчивость и высокую скорость обработки транзакций RAID 5 с высокой скоростью потокового чтения/записи RAID 0. RAID 50 представляет собой RAID 0 массив, элементами которого являются массивы RAID 5. Это хорошее серверное решение, но для его реализации требуется как минимум шесть дисков.

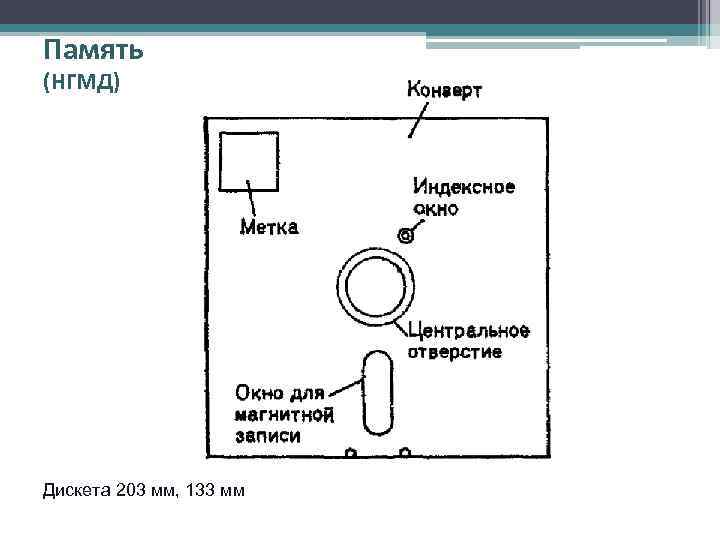

Память (НГМД) Дискета 203 мм, 133 мм

Память (НГМД) Дискета 203 мм, 133 мм

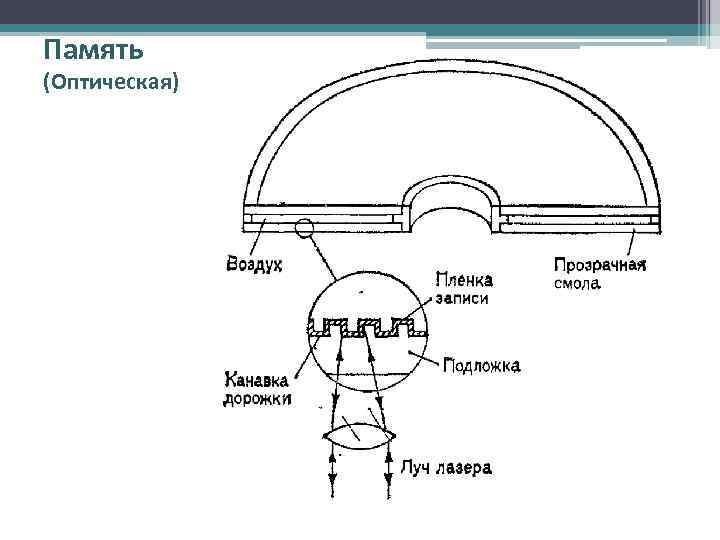

Память (Оптическая)

Память (Оптическая)

Память (Оптическая)

Память (Оптическая)

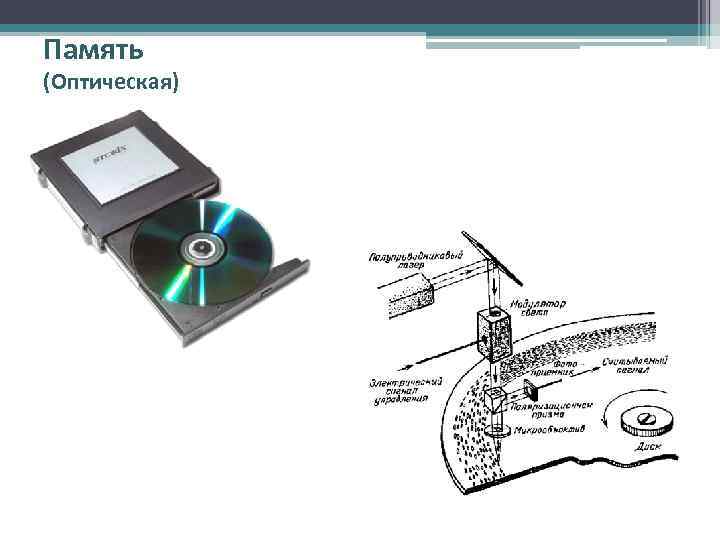

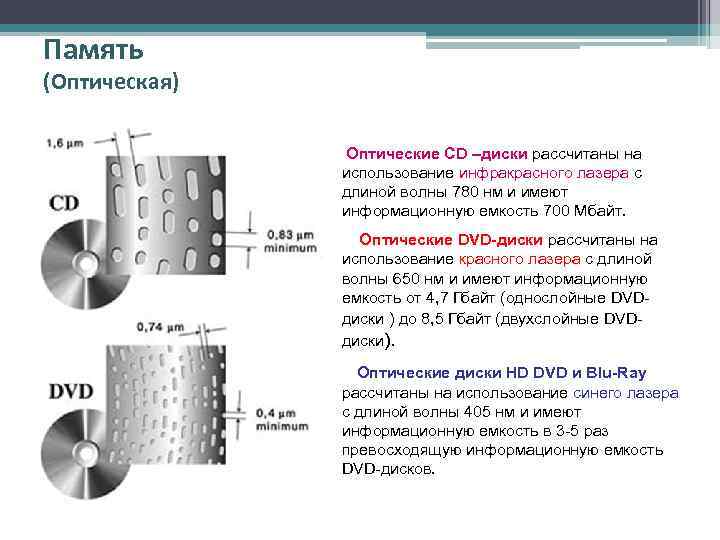

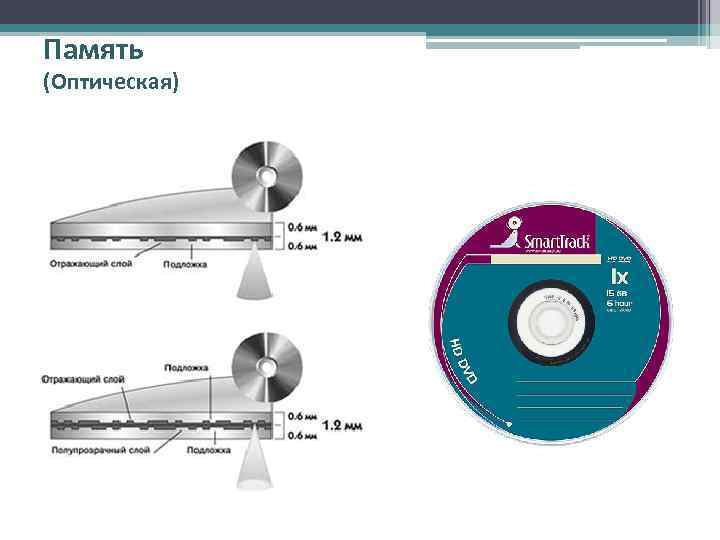

Память (Оптическая) Оптические CD –диски рассчитаны на использование инфракрасного лазера с длиной волны 780 нм и имеют информационную емкость 700 Мбайт. Оптические DVD-диски рассчитаны на использование красного лазера с длиной волны 650 нм и имеют информационную емкость от 4, 7 Гбайт (однослойные DVDдиски ) до 8, 5 Гбайт (двухслойные DVDдиски). Оптические диски HD DVD и Blu-Ray рассчитаны на использование синего лазера с длиной волны 405 нм и имеют информационную емкость в 3 -5 раз превосходящую информационную емкость DVD-дисков.

Память (Оптическая) Оптические CD –диски рассчитаны на использование инфракрасного лазера с длиной волны 780 нм и имеют информационную емкость 700 Мбайт. Оптические DVD-диски рассчитаны на использование красного лазера с длиной волны 650 нм и имеют информационную емкость от 4, 7 Гбайт (однослойные DVDдиски ) до 8, 5 Гбайт (двухслойные DVDдиски). Оптические диски HD DVD и Blu-Ray рассчитаны на использование синего лазера с длиной волны 405 нм и имеют информационную емкость в 3 -5 раз превосходящую информационную емкость DVD-дисков.

Память (Оптическая)

Память (Оптическая)

Память (Оптическая)

Память (Оптическая)

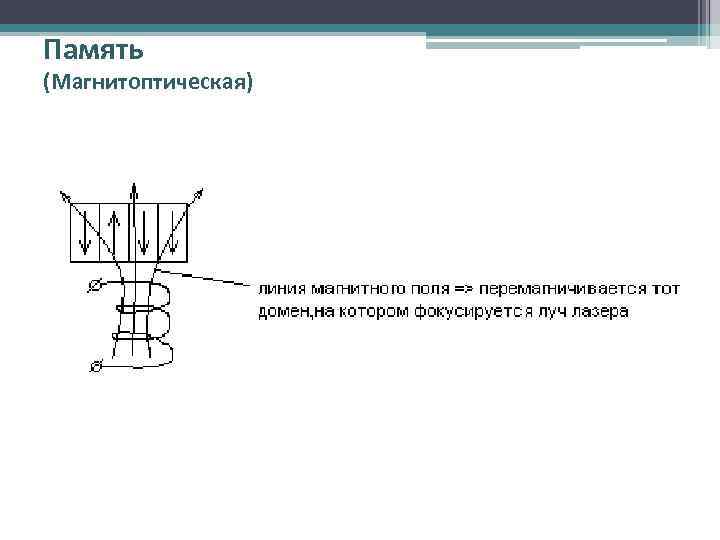

Память (Магнитоптическая)

Память (Магнитоптическая)

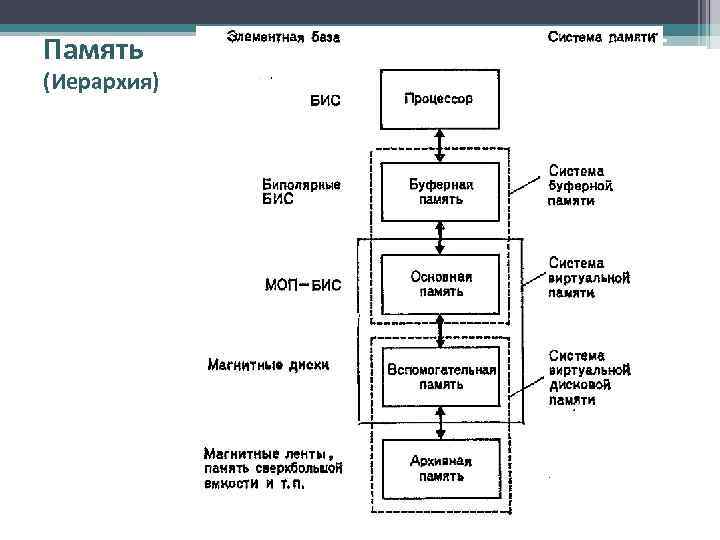

Память (Иерархия)

Память (Иерархия)

Иерархическая архитектура памяти

Иерархическая архитектура памяти

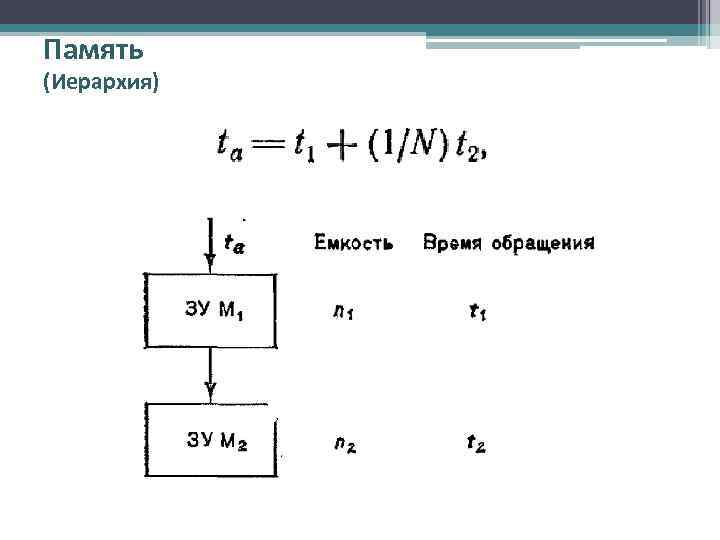

Память (Иерархия)

Память (Иерархия)

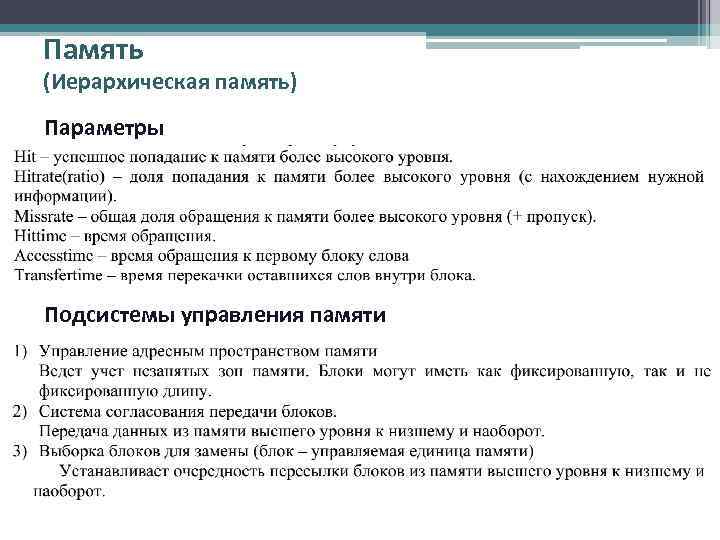

Память (Иерархическая память) Параметры Подсистемы управления памяти

Память (Иерархическая память) Параметры Подсистемы управления памяти

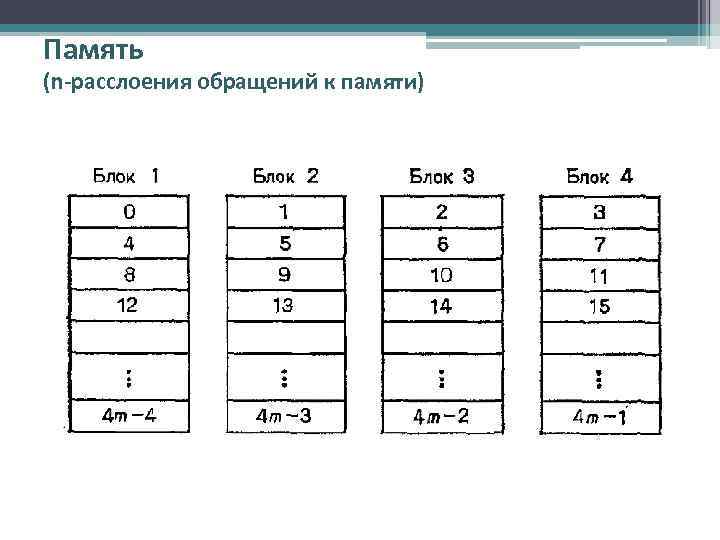

Память (n-расслоения обращений к памяти)

Память (n-расслоения обращений к памяти)

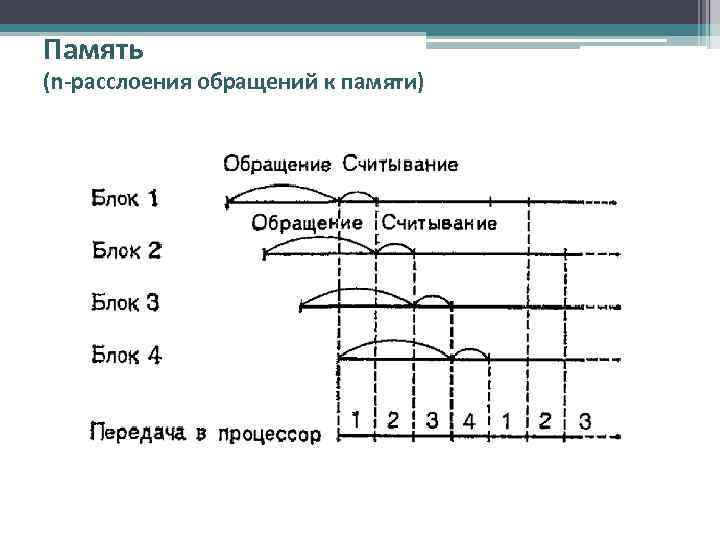

Память (n-расслоения обращений к памяти)

Память (n-расслоения обращений к памяти)

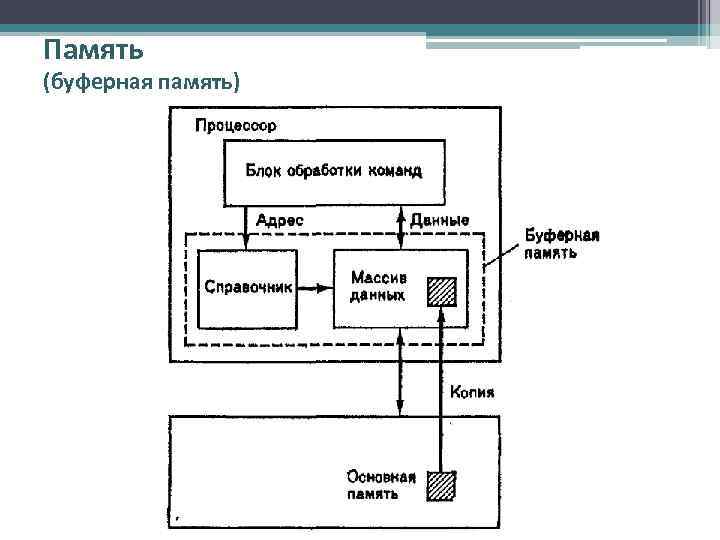

Память (буферная память)

Память (буферная память)

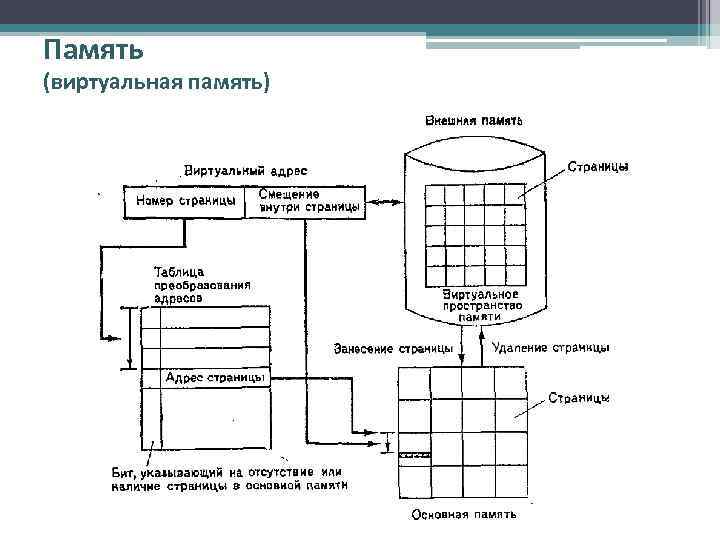

Память (виртуальная память)

Память (виртуальная память)

Память (стратегии замены страниц)

Память (стратегии замены страниц)

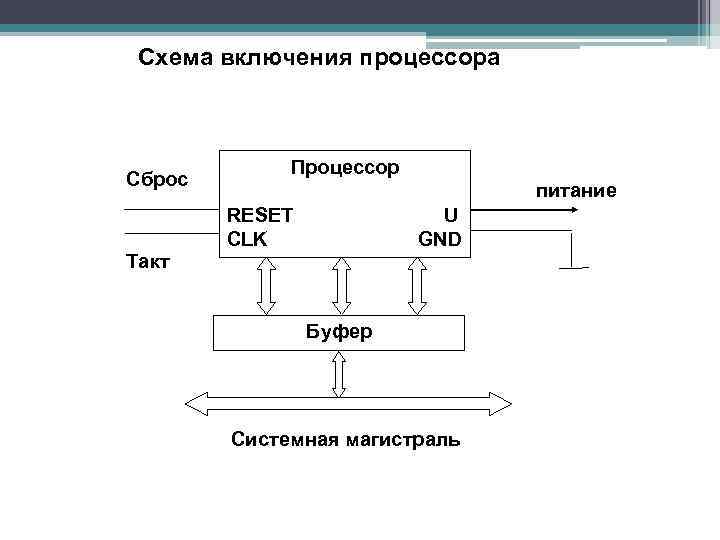

Схема включения процессора Сброс Процессор питание RESET СLK U GND Такт Буфер Системная магистраль

Схема включения процессора Сброс Процессор питание RESET СLK U GND Такт Буфер Системная магистраль

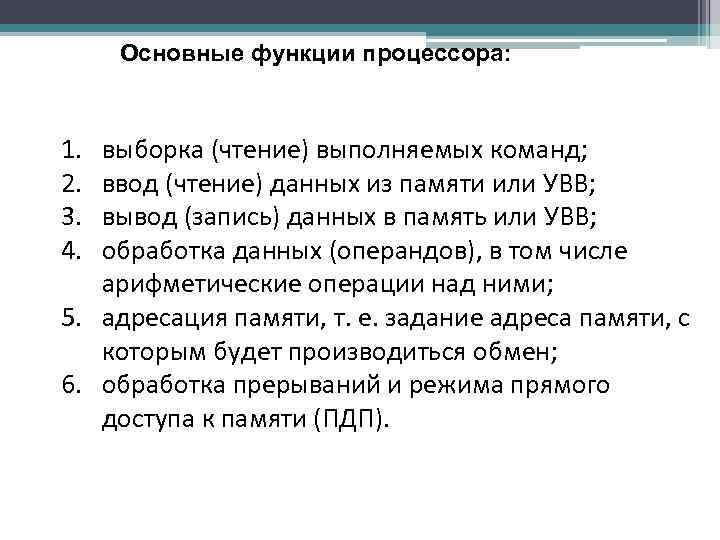

Основные функции процессора: 1. 2. 3. 4. выборка (чтение) выполняемых команд; ввод (чтение) данных из памяти или УВВ; вывод (запись) данных в память или УВВ; обработка данных (операндов), в том числе арифметические операции над ними; 5. адресация памяти, т. е. задание адреса памяти, с которым будет производиться обмен; 6. обработка прерываний и режима прямого доступа к памяти (ПДП).

Основные функции процессора: 1. 2. 3. 4. выборка (чтение) выполняемых команд; ввод (чтение) данных из памяти или УВВ; вывод (запись) данных в память или УВВ; обработка данных (операндов), в том числе арифметические операции над ними; 5. адресация памяти, т. е. задание адреса памяти, с которым будет производиться обмен; 6. обработка прерываний и режима прямого доступа к памяти (ПДП).

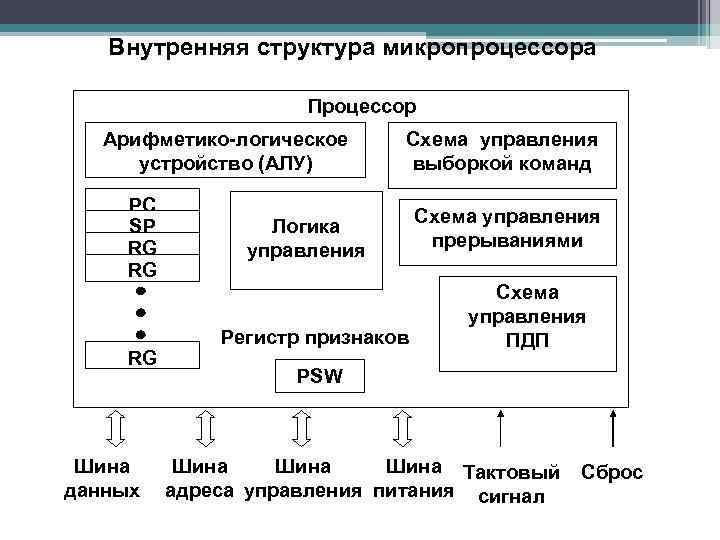

Внутренняя структура микропроцессора Процессор Арифметико-логическое устройство (АЛУ) PC SP RG RG RG Шина данных Схема управления выборкой команд Логика управления Регистр признаков Схема управления прерываниями Схема управления ПДП PSW Шина Тактовый адреса управления питания сигнал Сброс

Внутренняя структура микропроцессора Процессор Арифметико-логическое устройство (АЛУ) PC SP RG RG RG Шина данных Схема управления выборкой команд Логика управления Регистр признаков Схема управления прерываниями Схема управления ПДП PSW Шина Тактовый адреса управления питания сигнал Сброс

Память (увеличение разрядности)

Память (увеличение разрядности)

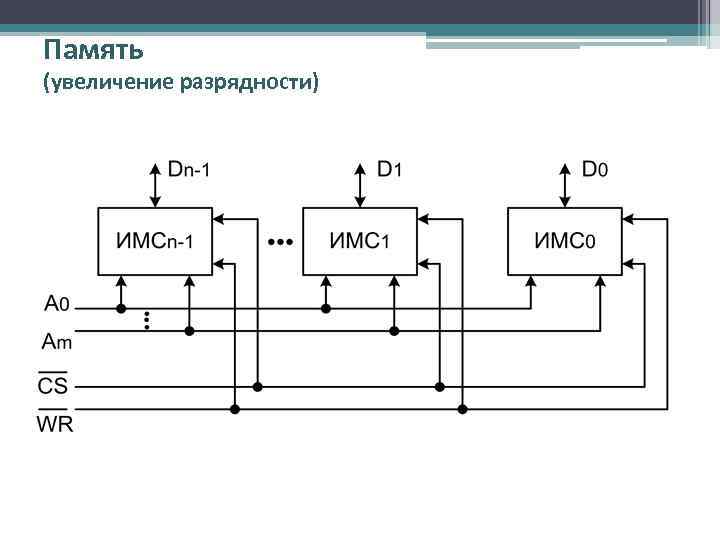

Память (увеличение разрядности)

Память (увеличение разрядности)

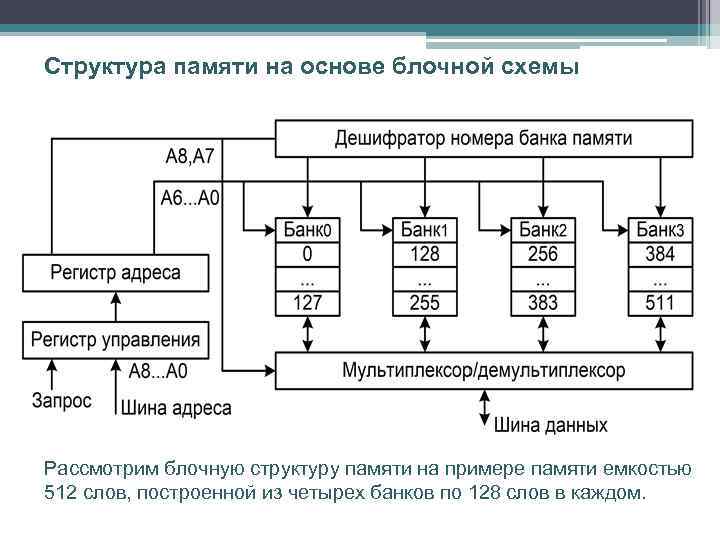

Структура памяти на основе блочной схемы Рассмотрим блочную структуру памяти на примере памяти емкостью 512 слов, построенной из четырех банков по 128 слов в каждом.

Структура памяти на основе блочной схемы Рассмотрим блочную структуру памяти на примере памяти емкостью 512 слов, построенной из четырех банков по 128 слов в каждом.

Блочная память с чередованием адресов по циклической схеме

Блочная память с чередованием адресов по циклической схеме

Блочно-циклическая схема расслоения памяти

Блочно-циклическая схема расслоения памяти

Структура микросхемы памяти

Структура микросхемы памяти

Виды статических ОЗУ

Виды статических ОЗУ

Асинхронные статические ОЗУ: время доступа составляло 15 -20 нс (в лучшем случае — 12 нс) Синхронные статические ОЗУ: SSRAM обеспечивает работу в пакетном режиме с формулой 3 -1 -1 -1, но лишь до определенных значений тактовой частоты шины. При более высоких частотах формула изменяется на 3 -2 -2 -2. РВ SRAM. Начиная с Pentium II, взамен SSRAM оснащаются статической оперативной памятью с пакетным конвейерным доступом (РВ SRAM — Pipelined Burst SRAM). Время доступа к РВ SRAM составляет от 4, 5 до 8 нс, при этом формула 3 -1 -1 -1. Компания IDT (Integrated Device Technology) предложила новую технологию, получившую название ZBT SRAM (Zero Bus Turnaround) — нулевое время переключения шины.

Асинхронные статические ОЗУ: время доступа составляло 15 -20 нс (в лучшем случае — 12 нс) Синхронные статические ОЗУ: SSRAM обеспечивает работу в пакетном режиме с формулой 3 -1 -1 -1, но лишь до определенных значений тактовой частоты шины. При более высоких частотах формула изменяется на 3 -2 -2 -2. РВ SRAM. Начиная с Pentium II, взамен SSRAM оснащаются статической оперативной памятью с пакетным конвейерным доступом (РВ SRAM — Pipelined Burst SRAM). Время доступа к РВ SRAM составляет от 4, 5 до 8 нс, при этом формула 3 -1 -1 -1. Компания IDT (Integrated Device Technology) предложила новую технологию, получившую название ZBT SRAM (Zero Bus Turnaround) — нулевое время переключения шины.

Структура двухпортового ОЗУ

Структура двухпортового ОЗУ

Энергонезависимые оперативные запоминающие устройства 1. NVRAM — Non-Volatile RAM, разработана компанией Simtec; 2. BBSRAM - Battery-Back SRAM; 3. FRAM - Ferroelectric RAM — ферроэлектрическая память, разработана компанией Ramtron. Количество циклов перезаписи для FRAM обычно составляет 10 млрд. ; 4. Магнитная нанопамять; 5. Память на основе фазовых состояний PCM; 6. Магниторезистивная память МRAM.

Энергонезависимые оперативные запоминающие устройства 1. NVRAM — Non-Volatile RAM, разработана компанией Simtec; 2. BBSRAM - Battery-Back SRAM; 3. FRAM - Ferroelectric RAM — ферроэлектрическая память, разработана компанией Ramtron. Количество циклов перезаписи для FRAM обычно составляет 10 млрд. ; 4. Магнитная нанопамять; 5. Память на основе фазовых состояний PCM; 6. Магниторезистивная память МRAM.

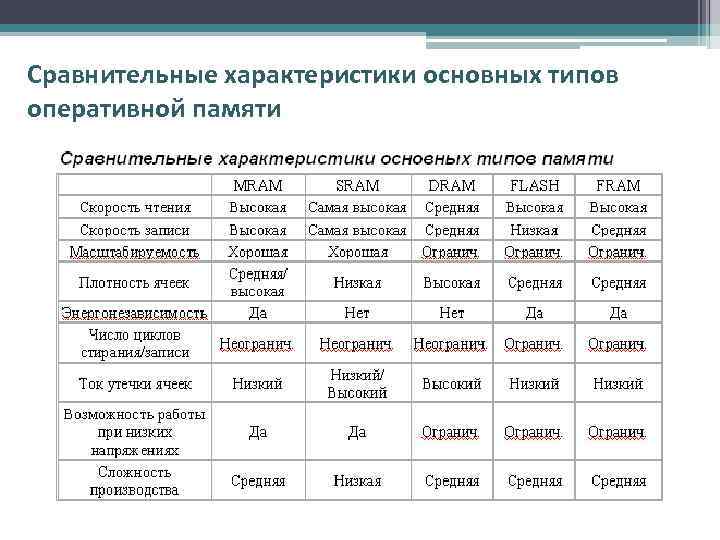

Сравнительные характеристики основных типов оперативной памяти

Сравнительные характеристики основных типов оперативной памяти

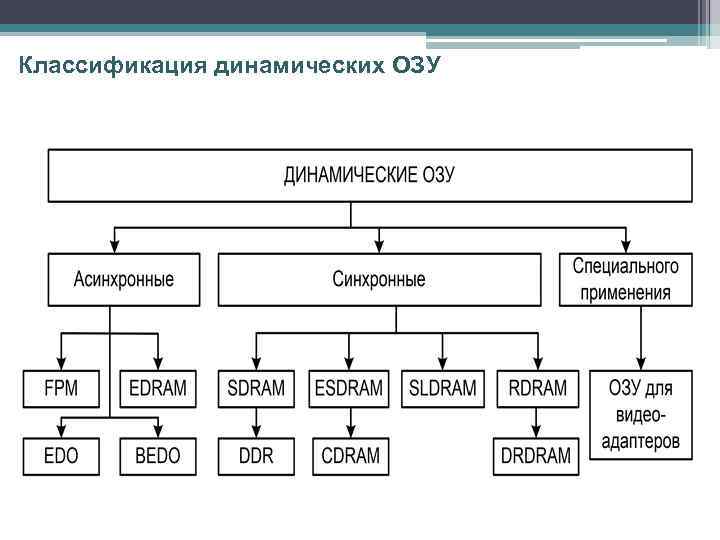

Классификация динамических ОЗУ

Классификация динамических ОЗУ

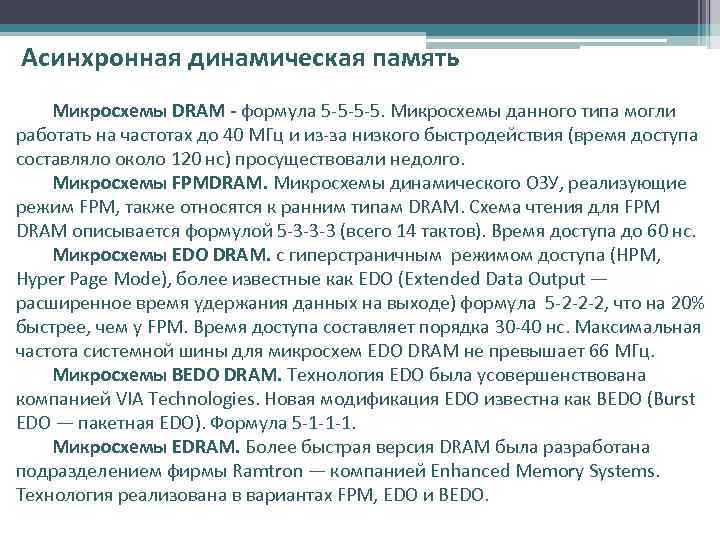

Асинхронная динамическая память Микросхемы DRAM - формула 5 -5 -5 -5. Микросхемы данного типа могли работать на частотах до 40 МГц и из-за низкого быстродействия (время доступа составляло около 120 нс) просуществовали недолго. Микросхемы FPMDRAM. Микросхемы динамического ОЗУ, реализующие режим FPM, также относятся к ранним типам DRAM. Схема чтения для FPM DRAM описывается формулой 5 -3 -3 -3 (всего 14 тактов). Время доступа до 60 нс. Микросхемы EDO DRAM. с гиперстраничным режимом доступа (НРМ, Hyper Page Mode), более известные как EDO (Extended Data Output — расширенное время удержания данных на выходе) формула 5 -2 -2 -2, что на 20% быстрее, чем у FPM. Время доступа составляет порядка 30 -40 нс. Максимальная частота системной шины для микросхем EDO DRAM не превышает 66 МГц. Микросхемы BEDО DRAM. Технология EDO была усовершенствована компанией VIA Technologies. Новая модификация EDO известна как BEDO (Burst EDO — пакетная EDO). Формула 5 -1 -1 -1. Микросхемы EDRAM. Более быстрая версия DRAM была разработана подразделением фирмы Ramtron — компанией Enhanced Memory Systems. Технология реализована в вариантах FPM, EDO и BEDO.

Асинхронная динамическая память Микросхемы DRAM - формула 5 -5 -5 -5. Микросхемы данного типа могли работать на частотах до 40 МГц и из-за низкого быстродействия (время доступа составляло около 120 нс) просуществовали недолго. Микросхемы FPMDRAM. Микросхемы динамического ОЗУ, реализующие режим FPM, также относятся к ранним типам DRAM. Схема чтения для FPM DRAM описывается формулой 5 -3 -3 -3 (всего 14 тактов). Время доступа до 60 нс. Микросхемы EDO DRAM. с гиперстраничным режимом доступа (НРМ, Hyper Page Mode), более известные как EDO (Extended Data Output — расширенное время удержания данных на выходе) формула 5 -2 -2 -2, что на 20% быстрее, чем у FPM. Время доступа составляет порядка 30 -40 нс. Максимальная частота системной шины для микросхем EDO DRAM не превышает 66 МГц. Микросхемы BEDО DRAM. Технология EDO была усовершенствована компанией VIA Technologies. Новая модификация EDO известна как BEDO (Burst EDO — пакетная EDO). Формула 5 -1 -1 -1. Микросхемы EDRAM. Более быстрая версия DRAM была разработана подразделением фирмы Ramtron — компанией Enhanced Memory Systems. Технология реализована в вариантах FPM, EDO и BEDO.

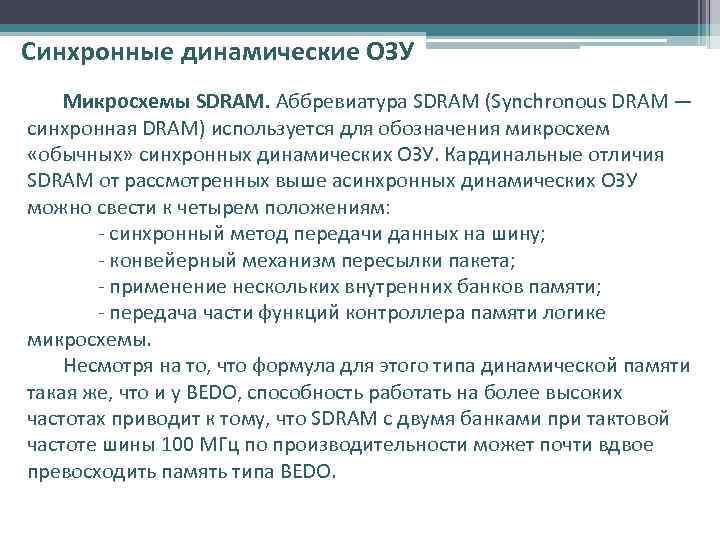

Синхронные динамические ОЗУ Микросхемы SDRAM. Аббревиатура SDRAM (Synchronous DRAM — синхронная DRAM) используется для обозначения микросхем «обычных» синхронных динамических ОЗУ. Кардинальные отличия SDRAM от рассмотренных выше асинхронных динамических ОЗУ можно свести к четырем положениям: - синхронный метод передачи данных на шину; - конвейерный механизм пересылки пакета; - применение нескольких внутренних банков памяти; - передача части функций контроллера памяти логике микросхемы. Несмотря на то, что формула для этого типа динамической памяти такая же, что и у BEDO, способность работать на более высоких частотах приводит к тому, что SDRAM с двумя банками при тактовой частоте шины 100 МГц по производительности может почти вдвое превосходить память типа BEDO.

Синхронные динамические ОЗУ Микросхемы SDRAM. Аббревиатура SDRAM (Synchronous DRAM — синхронная DRAM) используется для обозначения микросхем «обычных» синхронных динамических ОЗУ. Кардинальные отличия SDRAM от рассмотренных выше асинхронных динамических ОЗУ можно свести к четырем положениям: - синхронный метод передачи данных на шину; - конвейерный механизм пересылки пакета; - применение нескольких внутренних банков памяти; - передача части функций контроллера памяти логике микросхемы. Несмотря на то, что формула для этого типа динамической памяти такая же, что и у BEDO, способность работать на более высоких частотах приводит к тому, что SDRAM с двумя банками при тактовой частоте шины 100 МГц по производительности может почти вдвое превосходить память типа BEDO.

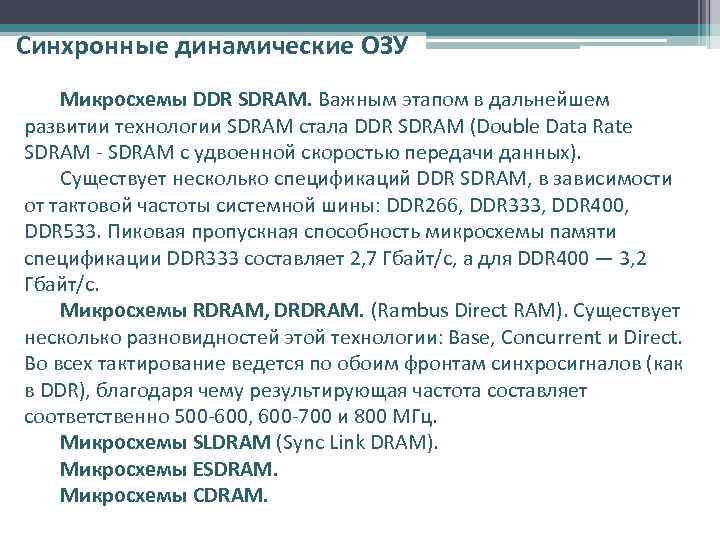

Синхронные динамические ОЗУ Микросхемы DDR SDRAM. Важным этапом в дальнейшем развитии технологии SDRAM стала DDR SDRAM (Double Data Rate SDRAM - SDRAM с удвоенной скоростью передачи данных). Существует несколько спецификаций DDR SDRAM, в зависимости от тактовой частоты системной шины: DDR 266, DDR 333, DDR 400, DDR 533. Пиковая пропускная способность микросхемы памяти спецификации DDR 333 составляет 2, 7 Гбайт/с, а для DDR 400 — 3, 2 Гбайт/с. Микросхемы RDRAM, DRDRAM. (Rambus Direct RAM). Существует несколько разновидностей этой технологии: Base, Concurrent и Direct. Во всех тактирование ведется по обоим фронтам синхросигналов (как в DDR), благодаря чему результирующая частота составляет соответственно 500 -600, 600 -700 и 800 МГц. Микросхемы SLDRAM (Sync Link DRAM). Микросхемы ESDRAM. Микросхемы CDRAM.

Синхронные динамические ОЗУ Микросхемы DDR SDRAM. Важным этапом в дальнейшем развитии технологии SDRAM стала DDR SDRAM (Double Data Rate SDRAM - SDRAM с удвоенной скоростью передачи данных). Существует несколько спецификаций DDR SDRAM, в зависимости от тактовой частоты системной шины: DDR 266, DDR 333, DDR 400, DDR 533. Пиковая пропускная способность микросхемы памяти спецификации DDR 333 составляет 2, 7 Гбайт/с, а для DDR 400 — 3, 2 Гбайт/с. Микросхемы RDRAM, DRDRAM. (Rambus Direct RAM). Существует несколько разновидностей этой технологии: Base, Concurrent и Direct. Во всех тактирование ведется по обоим фронтам синхросигналов (как в DDR), благодаря чему результирующая частота составляет соответственно 500 -600, 600 -700 и 800 МГц. Микросхемы SLDRAM (Sync Link DRAM). Микросхемы ESDRAM. Микросхемы CDRAM.

Copyright © 2013 Elsevier Inc. All rights reserved. Figure 8. 71 DDR 3 memory module

Copyright © 2013 Elsevier Inc. All rights reserved. Figure 8. 71 DDR 3 memory module

Структура ассоциативной памяти

Структура ассоциативной памяти

Классификация ассоциативных ЗУ по виду поиска

Классификация ассоциативных ЗУ по виду поиска

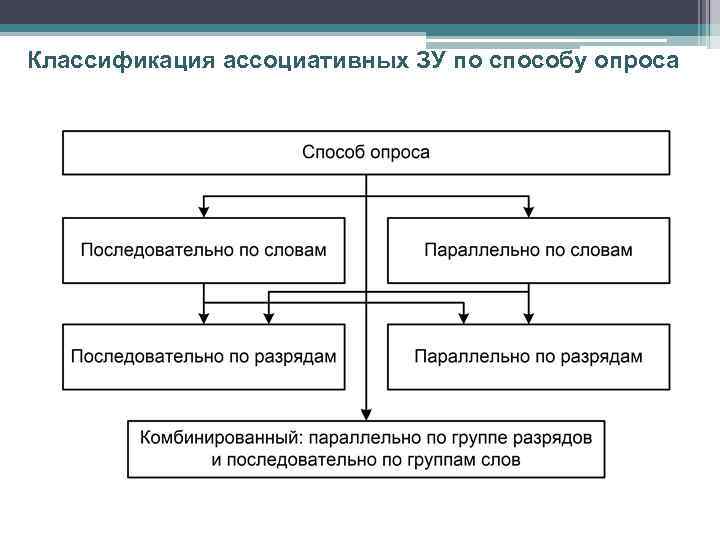

Классификация ассоциативных ЗУ по способу опроса

Классификация ассоциативных ЗУ по способу опроса

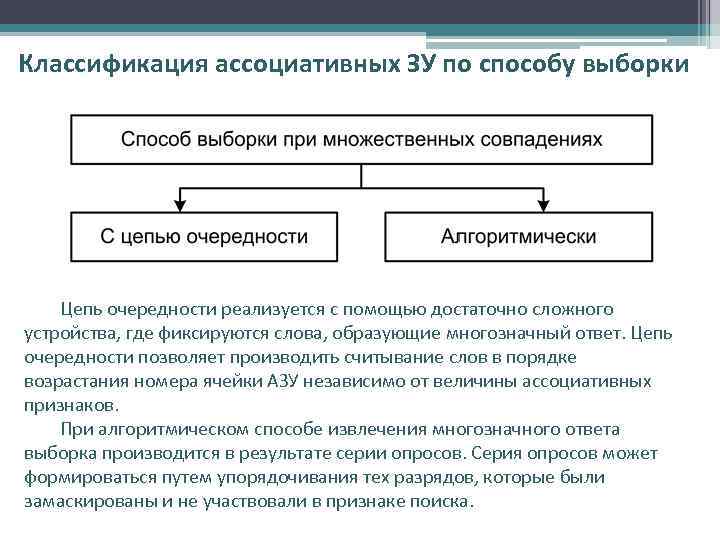

Классификация ассоциативных ЗУ по способу выборки Цепь очередности реализуется с помощью достаточно сложного устройства, где фиксируются слова, образующие многозначный ответ. Цепь очередности позволяет производить считывание слов в порядке возрастания номера ячейки АЗУ независимо от величины ассоциативных признаков. При алгоритмическом способе извлечения многозначного ответа выборка производится в результате серии опросов. Серия опросов может формироваться путем упорядочивания тех разрядов, которые были замаскированы и не участвовали в признаке поиска.

Классификация ассоциативных ЗУ по способу выборки Цепь очередности реализуется с помощью достаточно сложного устройства, где фиксируются слова, образующие многозначный ответ. Цепь очередности позволяет производить считывание слов в порядке возрастания номера ячейки АЗУ независимо от величины ассоциативных признаков. При алгоритмическом способе извлечения многозначного ответа выборка производится в результате серии опросов. Серия опросов может формироваться путем упорядочивания тех разрядов, которые были замаскированы и не участвовали в признаке поиска.

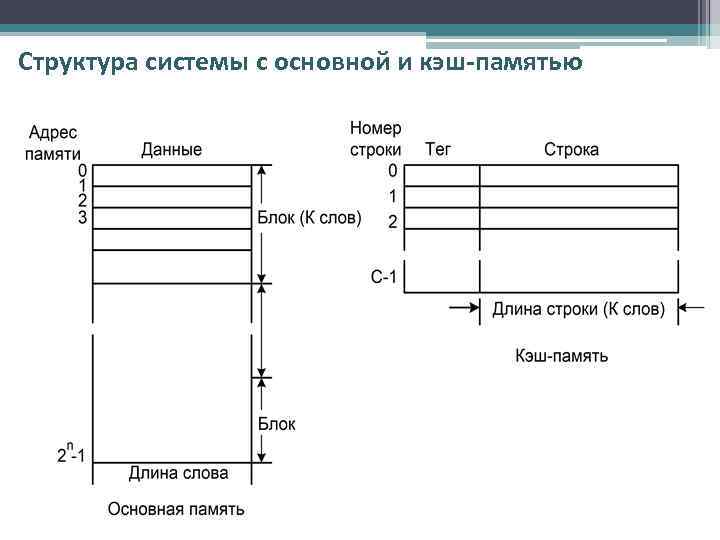

Структура системы с основной и кэш-памятью

Структура системы с основной и кэш-памятью

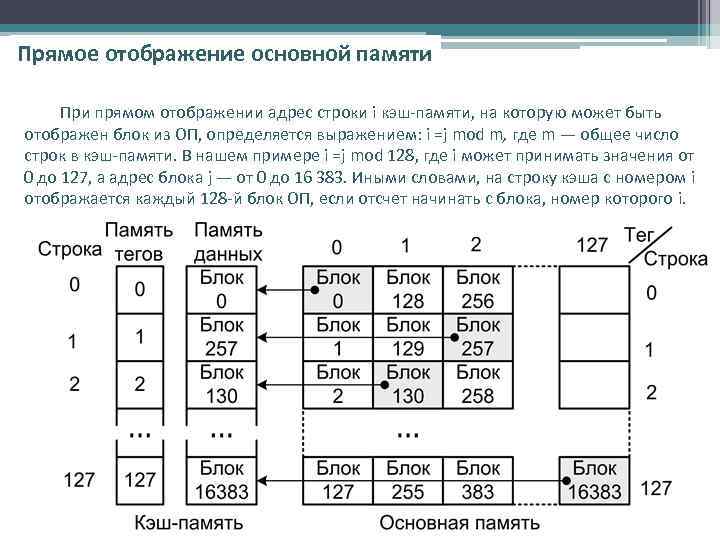

Прямое отображение основной памяти При прямом отображении адрес строки i кэш-памяти, на которую может быть отображен блок из ОП, определяется выражением: i =j mod m, где m — общее число строк в кэш-памяти. В нашем примере i =j mod 128, где i может принимать значения от 0 до 127, а адрес блока j — от 0 до 16 383. Иными словами, на строку кэша с номером i отображается каждый 128 -й блок ОП, если отсчет начинать с блока, номер которого i.

Прямое отображение основной памяти При прямом отображении адрес строки i кэш-памяти, на которую может быть отображен блок из ОП, определяется выражением: i =j mod m, где m — общее число строк в кэш-памяти. В нашем примере i =j mod 128, где i может принимать значения от 0 до 127, а адрес блока j — от 0 до 16 383. Иными словами, на строку кэша с номером i отображается каждый 128 -й блок ОП, если отсчет начинать с блока, номер которого i.

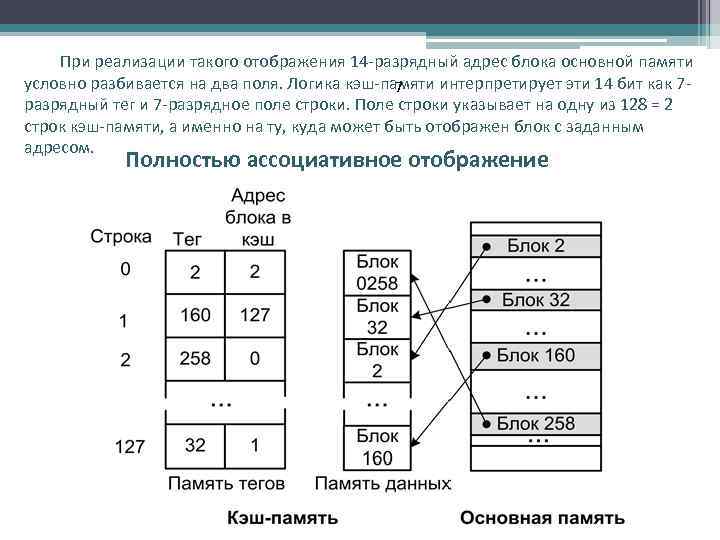

При реализации такого отображения 14 -разрядный адрес блока основной памяти условно разбивается на два поля. Логика кэш-памяти интерпретирует эти 14 бит как 77 разрядный тег и 7 -разрядное поле строки. Поле строки указывает на одну из 128 = 2 строк кэш-памяти, а именно на ту, куда может быть отображен блок с заданным адресом. Полностью ассоциативное отображение

При реализации такого отображения 14 -разрядный адрес блока основной памяти условно разбивается на два поля. Логика кэш-памяти интерпретирует эти 14 бит как 77 разрядный тег и 7 -разрядное поле строки. Поле строки указывает на одну из 128 = 2 строк кэш-памяти, а именно на ту, куда может быть отображен блок с заданным адресом. Полностью ассоциативное отображение

Уровни КЭШ-памяти Система с тремя уровнями КЭШ-памяти

Уровни КЭШ-памяти Система с тремя уровнями КЭШ-памяти

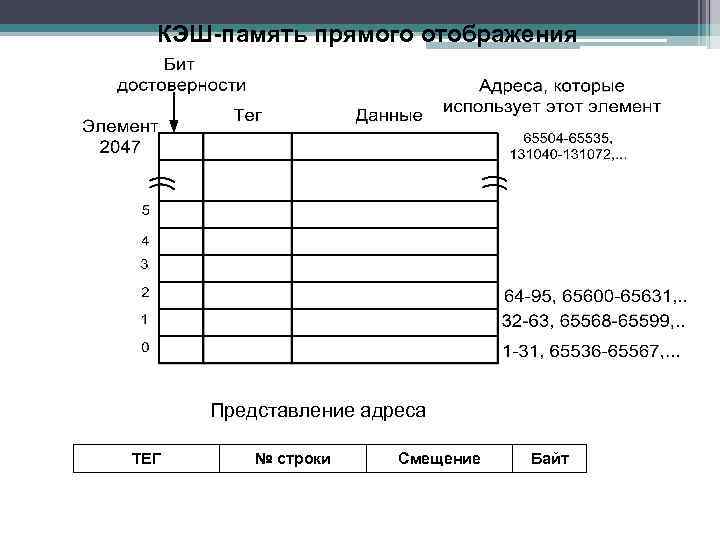

КЭШ-память прямого отображения Представление адреса ТЕГ № строки Смещение Байт

КЭШ-память прямого отображения Представление адреса ТЕГ № строки Смещение Байт

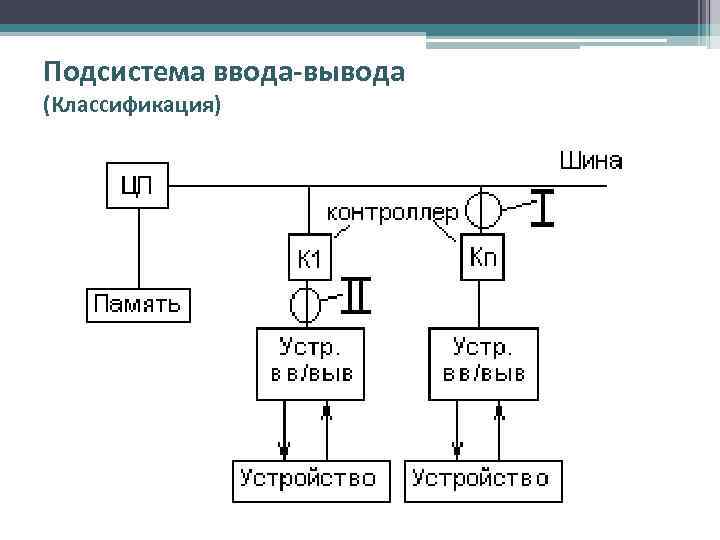

Подсистема ввода-вывода (Классификация)

Подсистема ввода-вывода (Классификация)

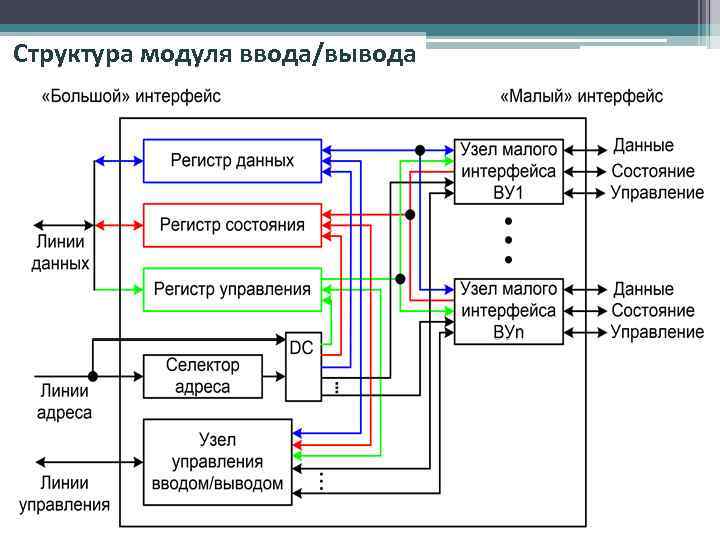

Подсистема ввода/вывода Модули ВВ Технически система ввода/вывода в рамках микропроцессорной системы реализуется комплексом модулей ввода/вывода (МВВ). Модуль ввода/вывода выполняет сопряжение ВУ с ядром микропроцессорной системы и различные коммуникационные операции между ними. Две основные функции МВВ: - обеспечение интерфейса с ЦП и памятью ( «большой» интерфейс); - обеспечение интерфейса с одним или несколькими периферийными устройствами ( «малый» интерфейс).

Подсистема ввода/вывода Модули ВВ Технически система ввода/вывода в рамках микропроцессорной системы реализуется комплексом модулей ввода/вывода (МВВ). Модуль ввода/вывода выполняет сопряжение ВУ с ядром микропроцессорной системы и различные коммуникационные операции между ними. Две основные функции МВВ: - обеспечение интерфейса с ЦП и памятью ( «большой» интерфейс); - обеспечение интерфейса с одним или несколькими периферийными устройствами ( «малый» интерфейс).

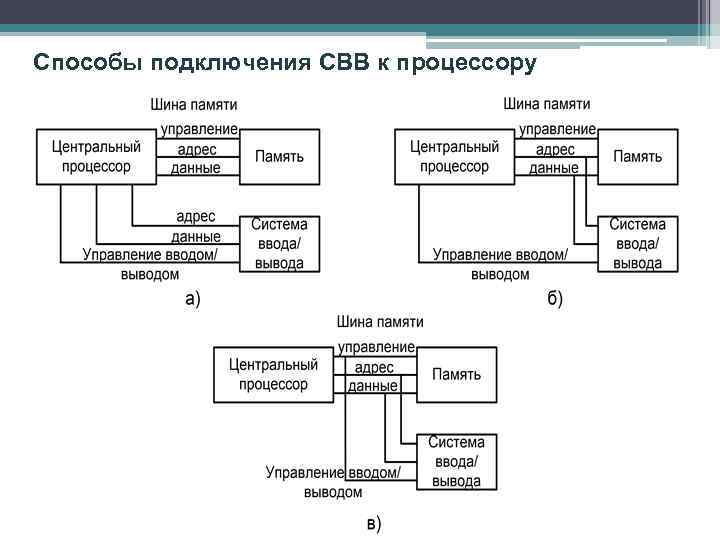

Способы подключения СВВ к процессору

Способы подключения СВВ к процессору

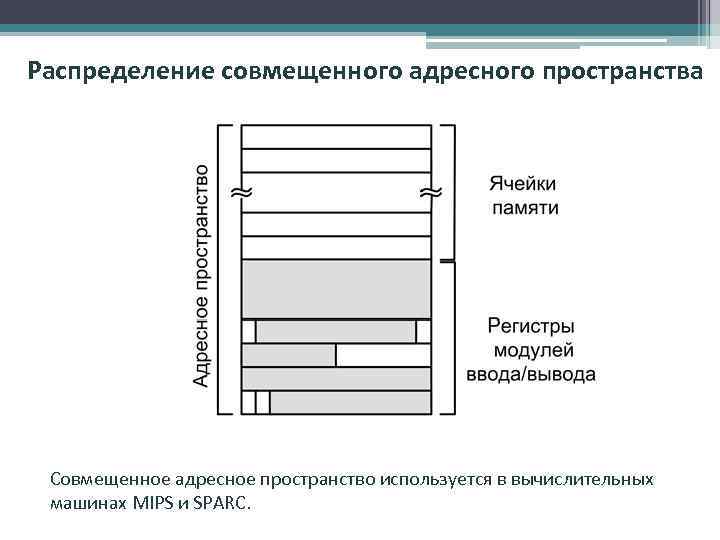

Распределение совмещенного адресного пространства Совмещенное адресное пространство используется в вычислительных машинах MIPS и SPARC.

Распределение совмещенного адресного пространства Совмещенное адресное пространство используется в вычислительных машинах MIPS и SPARC.

Достоинства совмещенного адресного пространства: - расширение набора команд для обращения к внешним устройствам позволяет сократить длину программы и повысить быстродействие; - значительное увеличение количества подключаемых внешних устройств; - возможность внепроцессорного обмена данными между внешними устройствами, если в системе команд есть команды пересылки между ячейками памяти; - возможность обмена информацией не только с аккумулятором, но и с любым регистром центрального процессора. Недостатки совмещенного адресного пространства: - сокращение области адресного пространства памяти; - усложнение декодирующих схем адресов в СВВ; - трудности распознавания операций передачи информации при вводе/выводе среди других операций. Сложности в чтении и отладке программы; - трудности при построении СВВ на простых модулях ввода/вывода: сигналы управления не смогут координировать сложную процедуру ввода/вывода. Поэтому МВВ часто должны генерировать дополнительные сигналы под управлением программы.

Достоинства совмещенного адресного пространства: - расширение набора команд для обращения к внешним устройствам позволяет сократить длину программы и повысить быстродействие; - значительное увеличение количества подключаемых внешних устройств; - возможность внепроцессорного обмена данными между внешними устройствами, если в системе команд есть команды пересылки между ячейками памяти; - возможность обмена информацией не только с аккумулятором, но и с любым регистром центрального процессора. Недостатки совмещенного адресного пространства: - сокращение области адресного пространства памяти; - усложнение декодирующих схем адресов в СВВ; - трудности распознавания операций передачи информации при вводе/выводе среди других операций. Сложности в чтении и отладке программы; - трудности при построении СВВ на простых модулях ввода/вывода: сигналы управления не смогут координировать сложную процедуру ввода/вывода. Поэтому МВВ часто должны генерировать дополнительные сигналы под управлением программы.

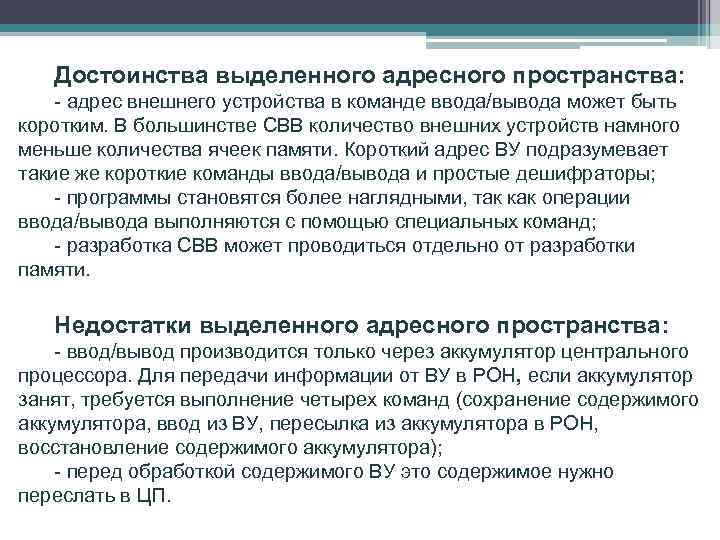

Достоинства выделенного адресного пространства: - адрес внешнего устройства в команде ввода/вывода может быть коротким. В большинстве СВВ количество внешних устройств намного меньше количества ячеек памяти. Короткий адрес ВУ подразумевает такие же короткие команды ввода/вывода и простые дешифраторы; - программы становятся более наглядными, так как операции ввода/вывода выполняются с помощью специальных команд; - разработка СВВ может проводиться отдельно от разработки памяти. Недостатки выделенного адресного пространства: - ввод/вывод производится только через аккумулятор центрального процессора. Для передачи информации от ВУ в РОН, если аккумулятор занят, требуется выполнение четырех команд (сохранение содержимого аккумулятора, ввод из ВУ, пересылка из аккумулятора в РОН, восстановление содержимого аккумулятора); - перед обработкой содержимого ВУ это содержимое нужно переслать в ЦП.

Достоинства выделенного адресного пространства: - адрес внешнего устройства в команде ввода/вывода может быть коротким. В большинстве СВВ количество внешних устройств намного меньше количества ячеек памяти. Короткий адрес ВУ подразумевает такие же короткие команды ввода/вывода и простые дешифраторы; - программы становятся более наглядными, так как операции ввода/вывода выполняются с помощью специальных команд; - разработка СВВ может проводиться отдельно от разработки памяти. Недостатки выделенного адресного пространства: - ввод/вывод производится только через аккумулятор центрального процессора. Для передачи информации от ВУ в РОН, если аккумулятор занят, требуется выполнение четырех команд (сохранение содержимого аккумулятора, ввод из ВУ, пересылка из аккумулятора в РОН, восстановление содержимого аккумулятора); - перед обработкой содержимого ВУ это содержимое нужно переслать в ЦП.

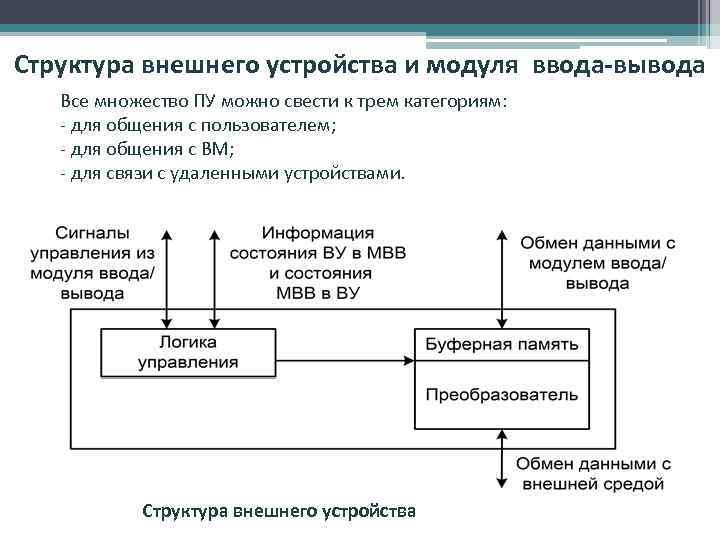

Структура внешнего устройства и модуля ввода-вывода Все множество ПУ можно свести к трем категориям: - для общения с пользователем; - для общения с ВМ; - для связи с удаленными устройствами. Структура внешнего устройства

Структура внешнего устройства и модуля ввода-вывода Все множество ПУ можно свести к трем категориям: - для общения с пользователем; - для общения с ВМ; - для связи с удаленными устройствами. Структура внешнего устройства

Структура модуля ввода/вывода

Структура модуля ввода/вывода

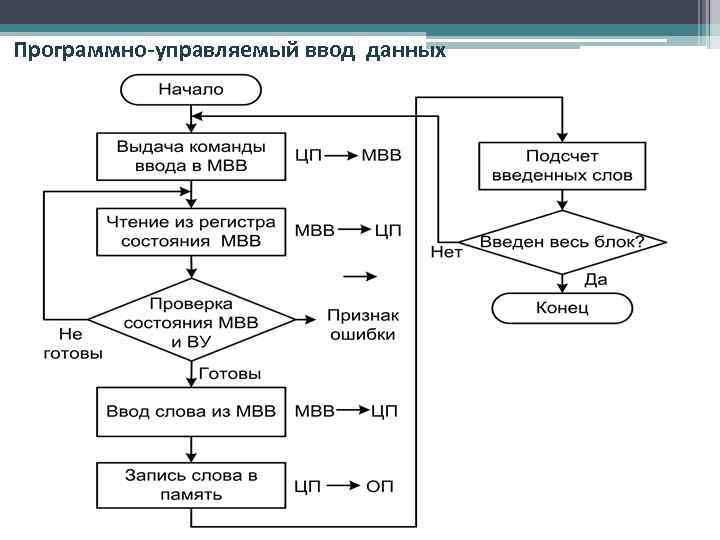

Программно-управляемый ввод данных

Программно-управляемый ввод данных

Ввод данных по прерыванию

Ввод данных по прерыванию

Организация прямого доступа к памяти

Организация прямого доступа к памяти

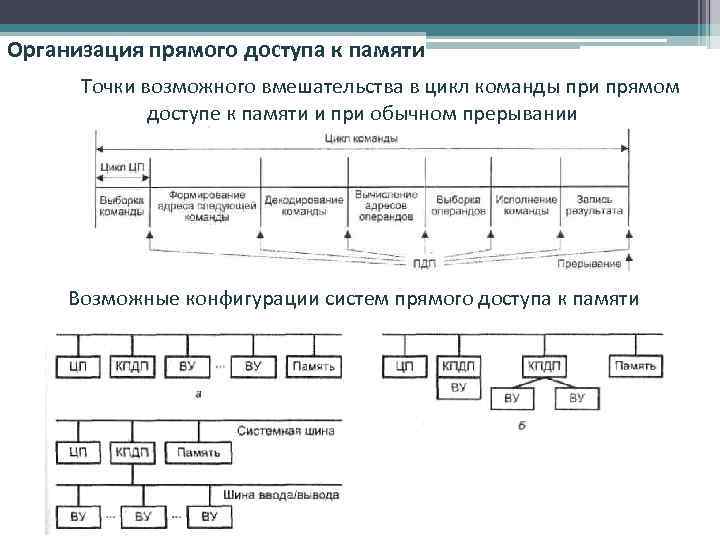

Организация прямого доступа к памяти Точки возможного вмешательства в цикл команды при прямом доступе к памяти и при обычном прерывании Возможные конфигурации систем прямого доступа к памяти

Организация прямого доступа к памяти Точки возможного вмешательства в цикл команды при прямом доступе к памяти и при обычном прерывании Возможные конфигурации систем прямого доступа к памяти

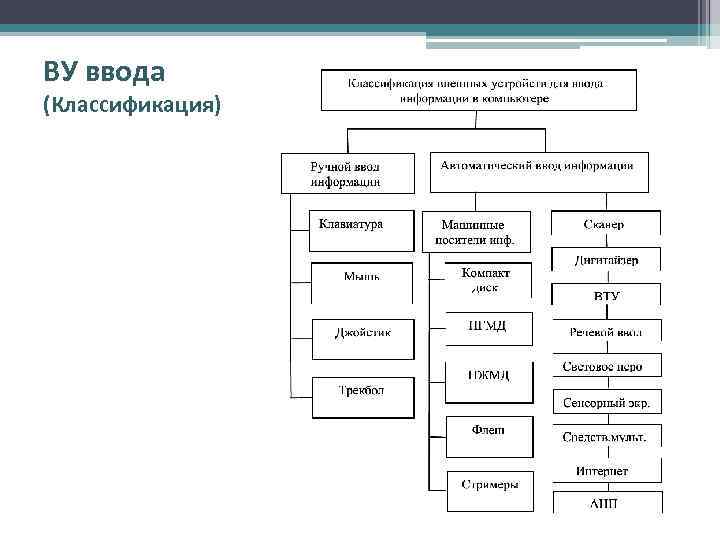

ВУ ввода (Классификация)

ВУ ввода (Классификация)

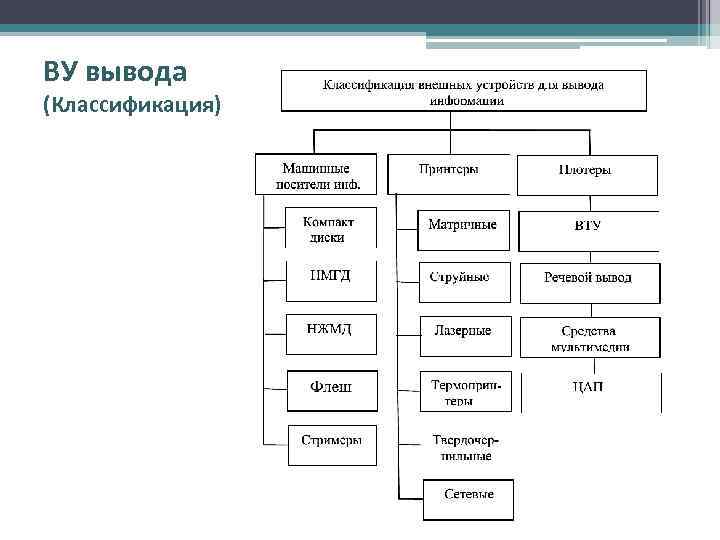

ВУ вывода (Классификация)

ВУ вывода (Классификация)

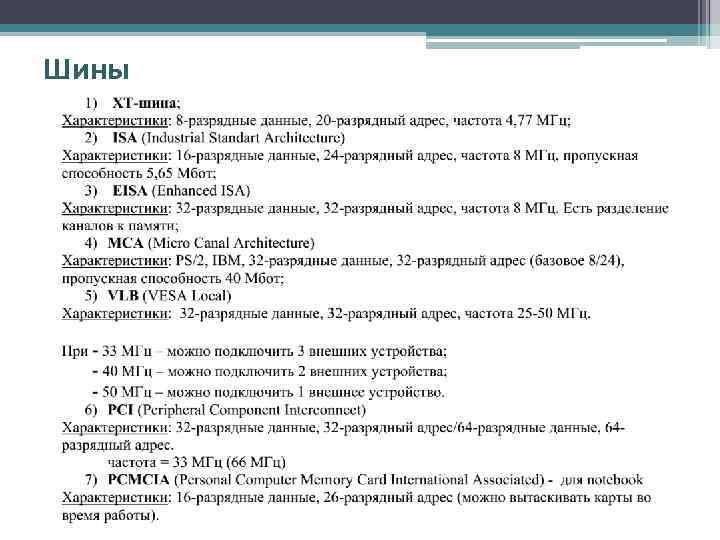

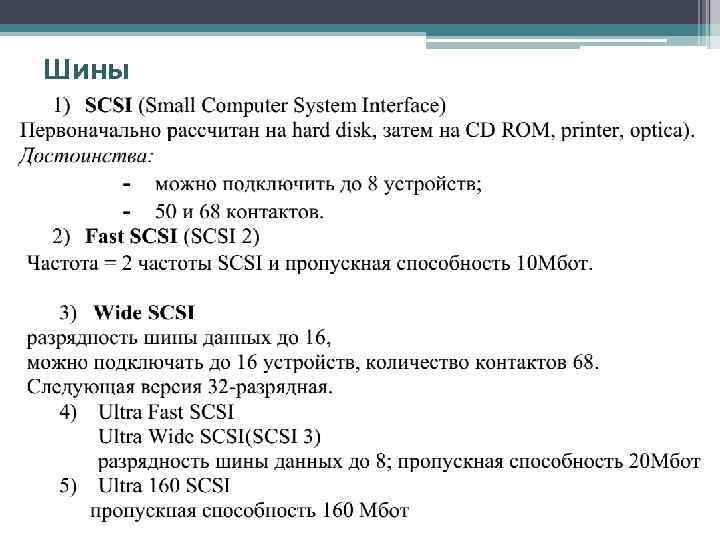

Шины

Шины

Шины

Шины

Интерфейсы (Подсистемы ввода-вывода)

Интерфейсы (Подсистемы ввода-вывода)

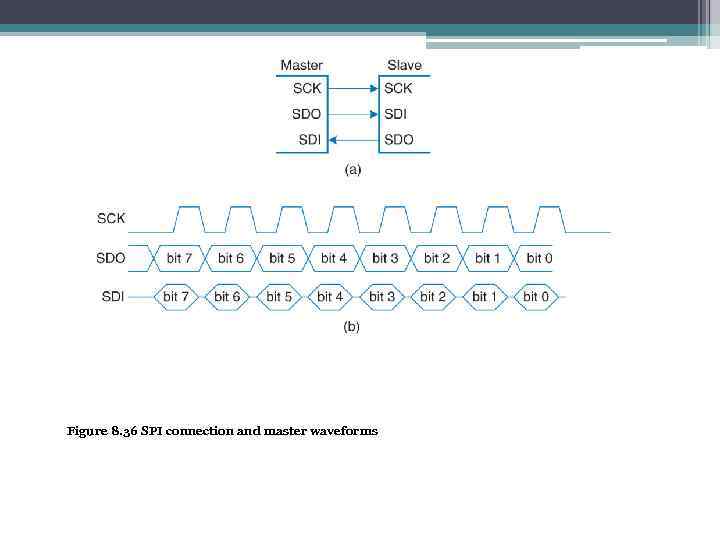

Figure 8. 36 SPI connection and master waveforms

Figure 8. 36 SPI connection and master waveforms

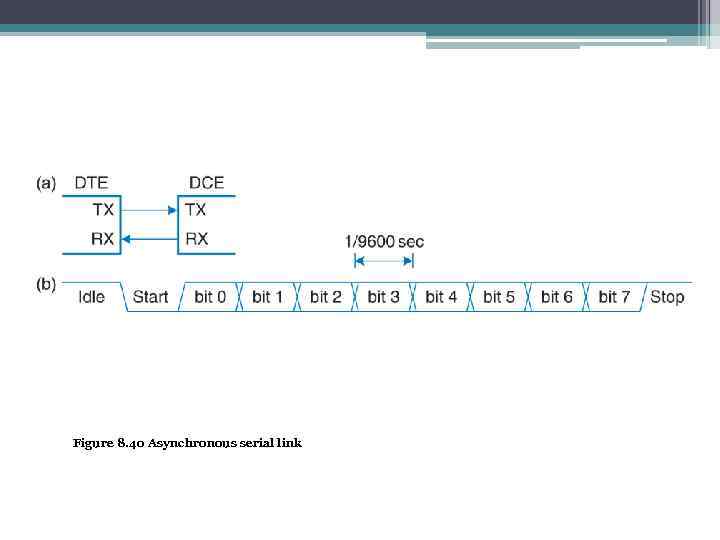

Figure 8. 40 Asynchronous serial link

Figure 8. 40 Asynchronous serial link

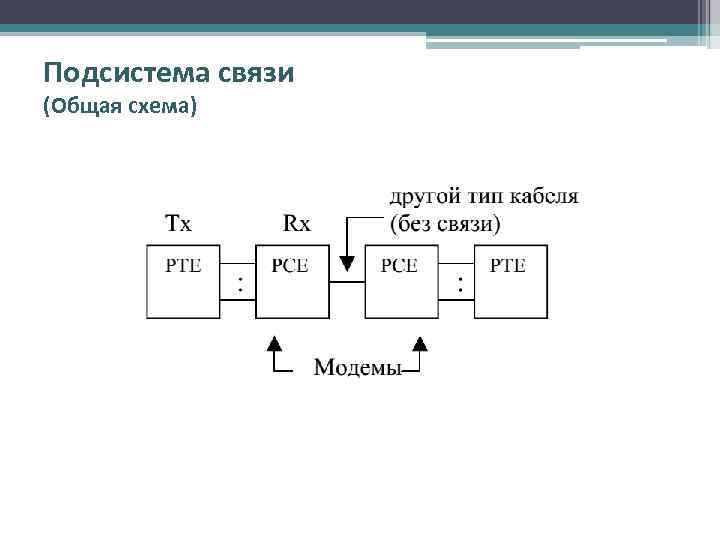

Подсистема связи (Общая схема)

Подсистема связи (Общая схема)

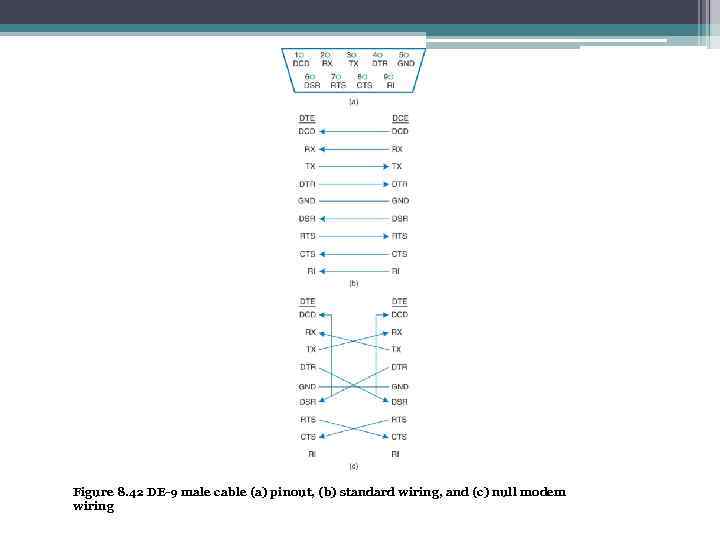

Figure 8. 42 DE-9 male cable (a) pinout, (b) standard wiring, and (c) null modem wiring

Figure 8. 42 DE-9 male cable (a) pinout, (b) standard wiring, and (c) null modem wiring

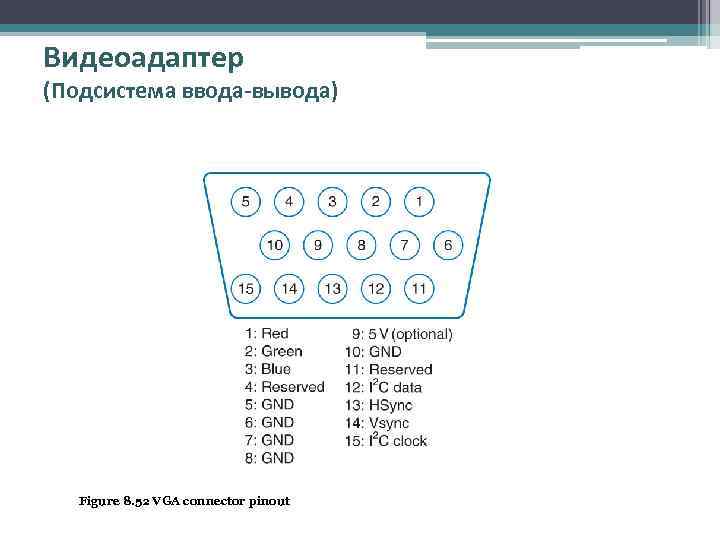

Видеоадаптер (Подсистема ввода-вывода) Figure 8. 52 VGA connector pinout

Видеоадаптер (Подсистема ввода-вывода) Figure 8. 52 VGA connector pinout

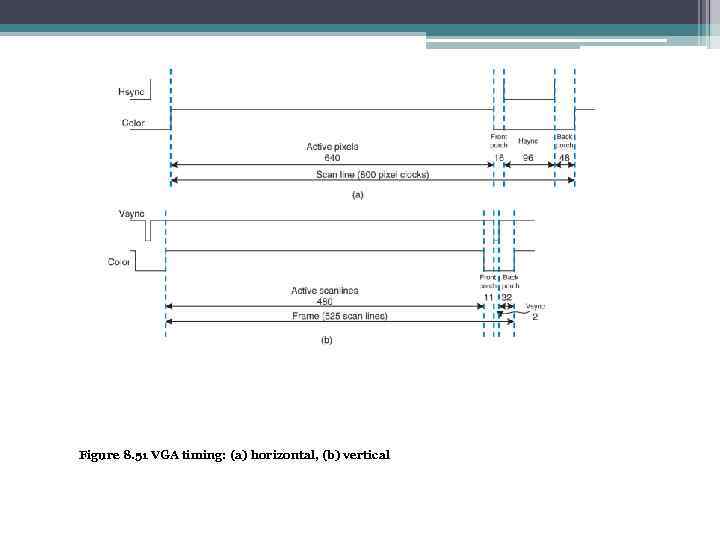

Figure 8. 51 VGA timing: (a) horizontal, (b) vertical

Figure 8. 51 VGA timing: (a) horizontal, (b) vertical

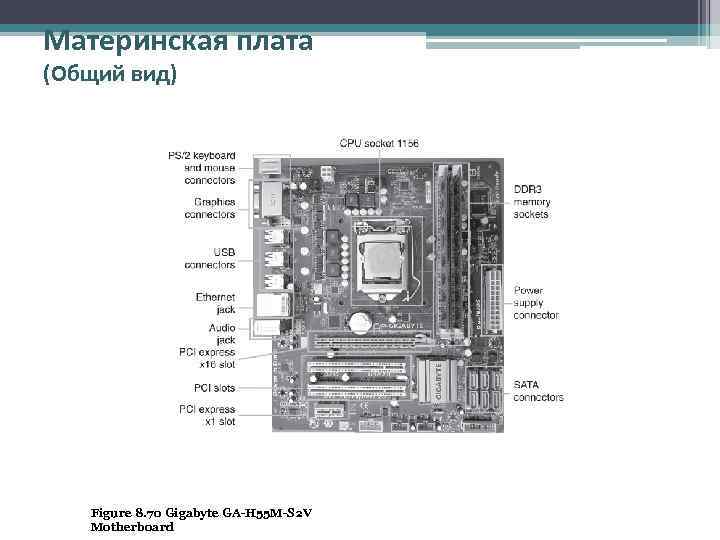

Материнская плата (Общий вид) Figure 8. 70 Gigabyte GA-H 55 M-S 2 V Motherboard

Материнская плата (Общий вид) Figure 8. 70 Gigabyte GA-H 55 M-S 2 V Motherboard

Copyright © 2013 Elsevier Inc. All rights reserved. Figure 8. 70 Gigabyte GA-H 55 M-S 2 V Motherboard

Copyright © 2013 Elsevier Inc. All rights reserved. Figure 8. 70 Gigabyte GA-H 55 M-S 2 V Motherboard

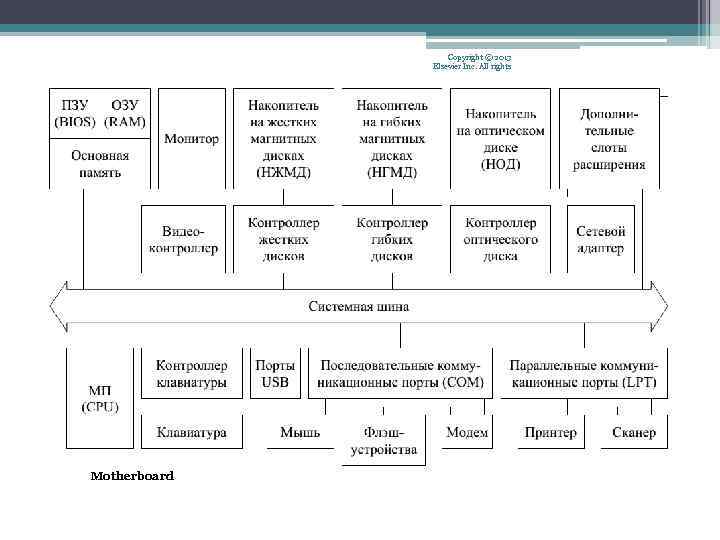

Компьютер (Общая схема)

Компьютер (Общая схема)

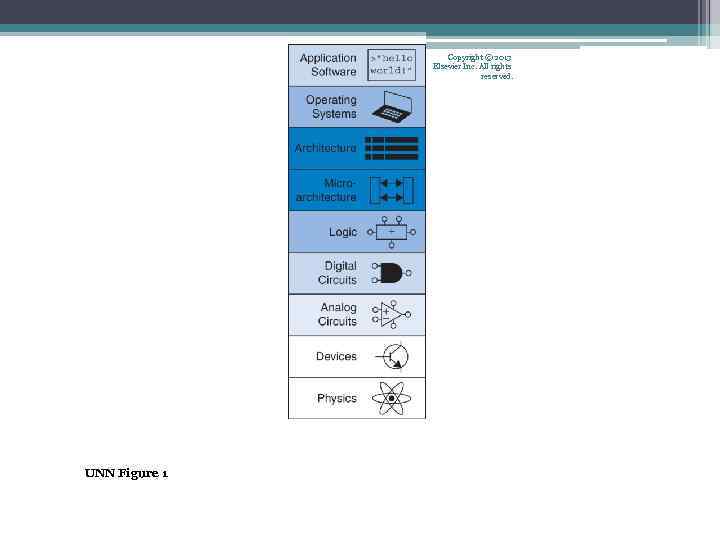

Copyright © 2013 Elsevier Inc. All rights reserved. UNN Figure 1

Copyright © 2013 Elsevier Inc. All rights reserved. UNN Figure 1