0b6a5b15fd385730df7af607e0d954ef.ppt

- Количество слайдов: 30

© KLMH Физическое Проектирование СБИС: от Разбиения Графов до Оптимизации Временных Характеристик Глава 1 – Введение Авторы книги: VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 1 Lienig Andrew B. Kahng, Jens Lienig, Igor L. Markov, Jin Hu

© KLMH Глава 1 – Введение Системы Автоматизированного Проектирования (САПР) 1. 2 Маршруты проектирования СБИС 1. 3 Стили проектирования СБИС 1. 4 Уровни раскладки и правила проектирования 1. 5 Задачи оптимизации при физическом проектировании 1. 6 Алгоритмы и сложность алгоритмических задач 1. 7 Терминология теории графов 1. 8 Общая терминология САПР VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 2 Lienig 1. 1

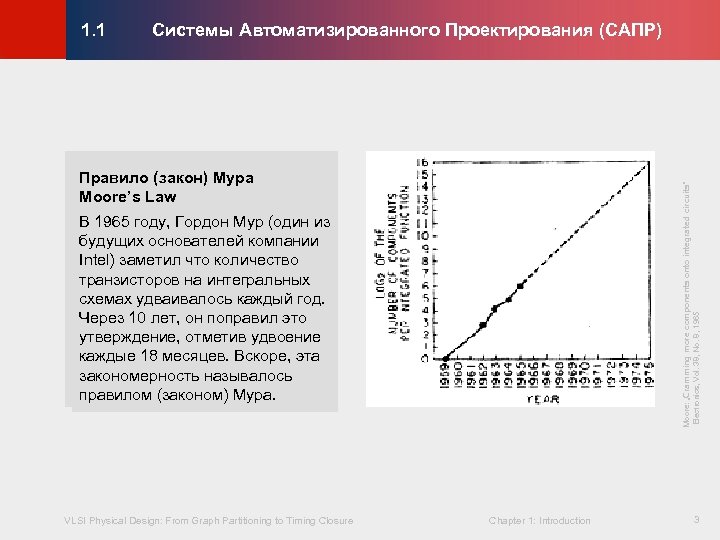

Системы Автоматизированного Проектирования (САПР) © KLMH 1. 1 В 1965 году, Гордон Мур (один из будущих основателей компании Intel) заметил что количество транзисторов на интегральных схемах удваивалось каждый год. Через 10 лет, он поправил это утверждение, отметив удвоение каждые 18 месяцев. Вскоре, эта закономерность называлось правилом (законом) Мура. VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 3 Lienig Moore: „Cramming more components onto integrated circuits" Electronics, Vol. 38, No. 8, 1965 Правило (закон) Мура Moore’s Law

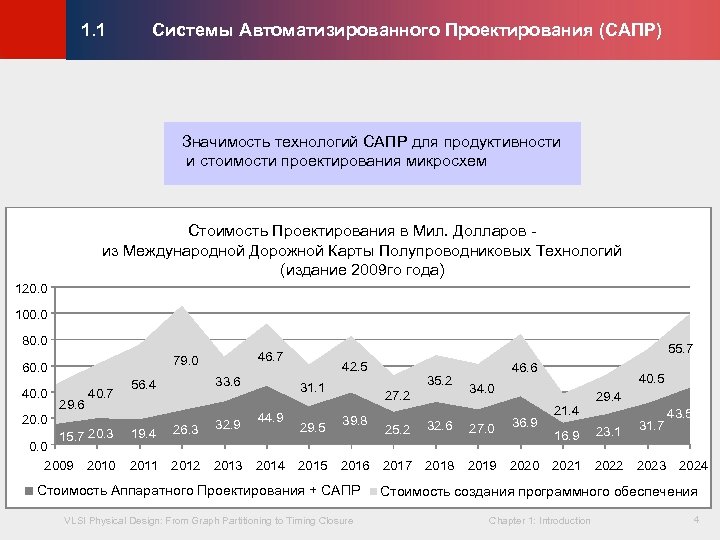

Системы Автоматизированного Проектирования (САПР) © KLMH 1. 1 Значимость технологий САПР для продуктивности и стоимости проектирования микросхем Стоимость Проектирования в Мил. Долларов из Международной Дорожной Карты Полупроводниковых Технологий (издание 2009 го года) 120. 0 100. 0 80. 0 40. 0 29. 6 40. 7 15. 7 20. 3 0. 0 2009 2010 33. 6 56. 4 26. 3 32. 9 2011 2012 2013 19. 4 42. 5 31. 1 44. 9 2014 29. 5 2015 35. 2 27. 2 39. 8 2016 Стоимость Аппаратного Проектирования + САПР VLSI Physical Design: From Graph Partitioning to Timing Closure 46. 6 40. 5 34. 0 25. 2 32. 6 27. 0 36. 9 2017 2018 2019 2020 21. 4 29. 4 16. 9 23. 1 31. 7 2021 2022 2023 43. 5 2024 Стоимость создания программного обеспечения Chapter 1: Introduction 4 Lienig 60. 0 55. 7 46. 7 79. 0

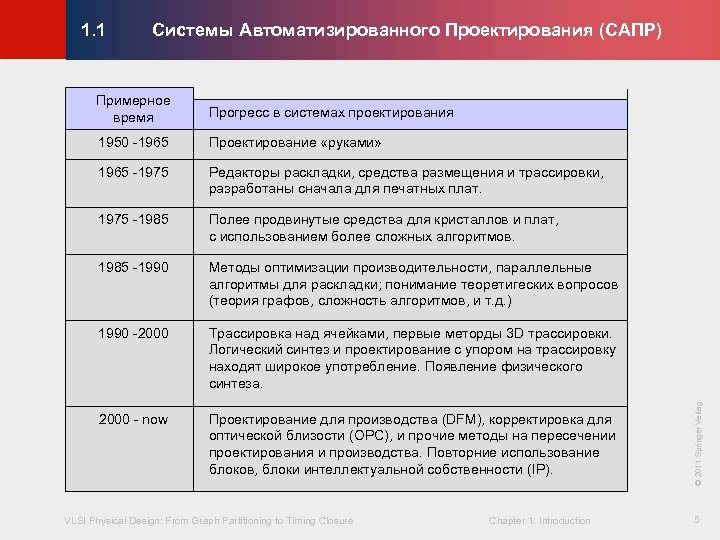

Системы Автоматизированного Проектирования (САПР) © KLMH 1. 1 1950 -1965 Проектирование «руками» 1965 -1975 Редакторы раскладки, средства размещения и трассировки, разработаны сначала для печатных плат. 1975 -1985 Полее продвинутые средства для кристаллов и плат, с использованием более сложных алгоритмов. 1985 -1990 Методы оптимизации производительности, параллельные алгоритмы для раскладки; понимание теоретигеских вопросов (теория графов, сложность алгоритмов, и т. д. ) 1990 -2000 Трассировка над ячейками, первые меторды 3 D трассировки. Логический синтез и проектирование с упором на трассировку находят широкое употребление. Появление физического синтеза. 2000 - now Проектирование для производства (DFM), корректировка для оптической близости (OPC), и прочие методы на пересечении проектирования и производства. Повторние использование блоков, блоки интеллектуальной собственности (IP). VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction © 2011 Springer Verlag Прогресс в системах проектирования 5 Lienig Примерное время

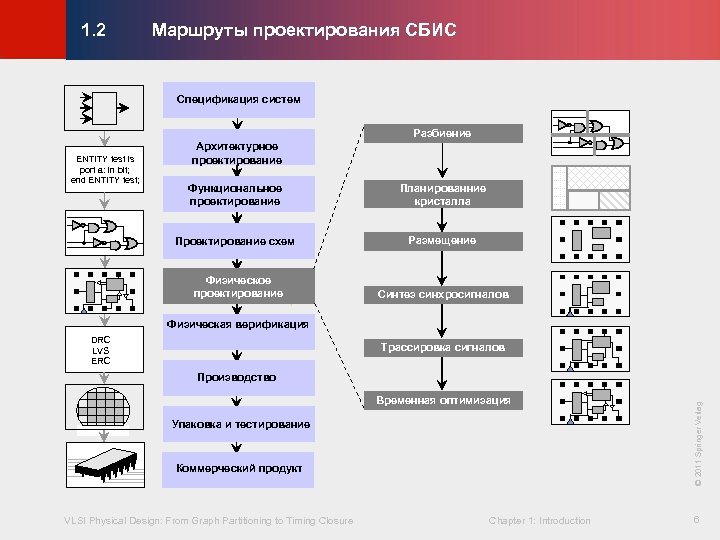

Маршруты проектирования СБИС © KLMH 1. 2 Спецификация систем Разбиение ENTITY test is port a: in bit; end ENTITY test; Архитектурное проектирование Функциональное проектирование Планированние кристалла Проектирование схем Размещение Физическое проектирование Синтез синхросигналов Физическая верификация DRC LVS ERC Трассировка сигналов Упаковка и тестирование Коммерческий продукт VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 6 Lienig Временная оптимизация © 2011 Springer Verlag Производство

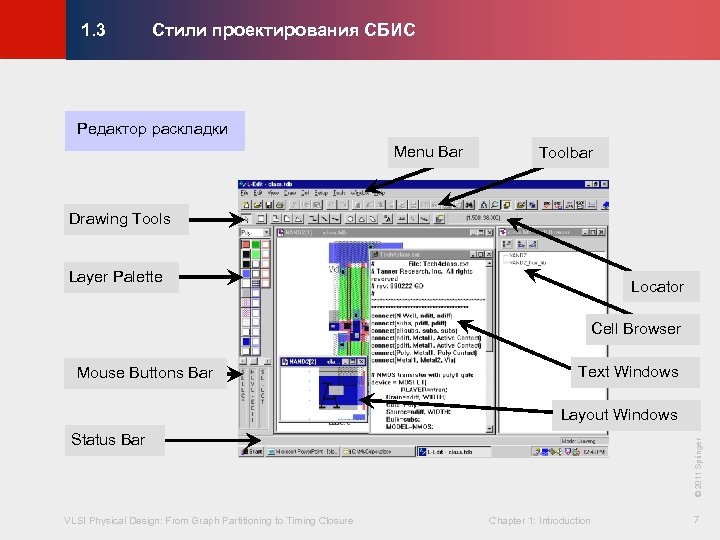

Стили проектирования СБИС © KLMH 1. 3 Редактор раскладки Menu Bar Toolbar Drawing Tools Layer Palette Locator Cell Browser Mouse Buttons Bar Text Windows Layout Windows Chapter 1: Introduction 7 Lienig VLSI Physical Design: From Graph Partitioning to Timing Closure © 2011 Springer Status Bar

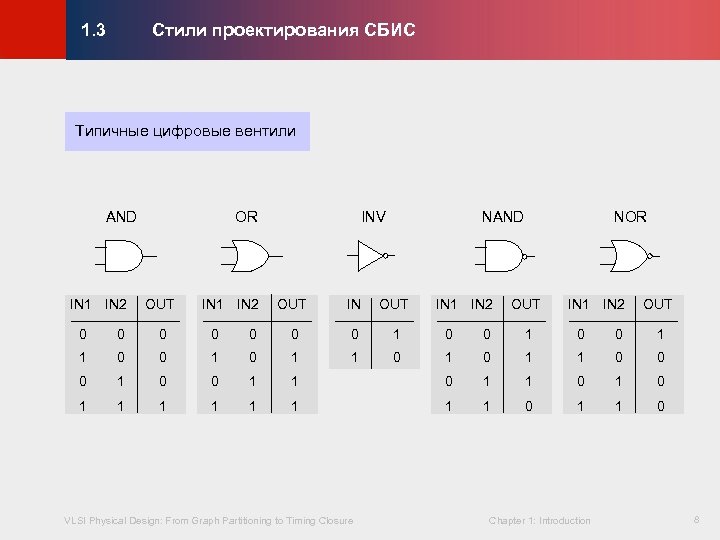

Стили проектирования СБИС © KLMH 1. 3 Типичные цифровые вентили AND IN 1 IN 2 OR OUT IN 1 IN 2 INV NAND OUT IN 1 IN 2 NOR OUT IN 1 IN 2 OUT 0 0 0 1 1 0 0 1 0 1 1 0 0 0 1 1 1 0 0 1 1 1 1 1 0 VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 8 Lienig 0

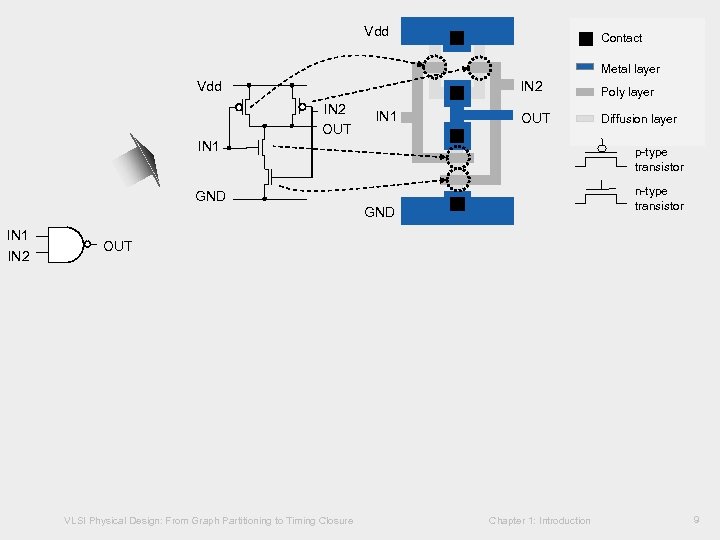

VLSI Design Styles Vdd Contact Metal layer Vdd IN 2 OUT IN 1 Poly layer OUT Diffusion layer IN 1 GND IN 2 p-type transistor n-type transistor GND OUT VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 9 Lienig IN 1 © KLMH 1. 3

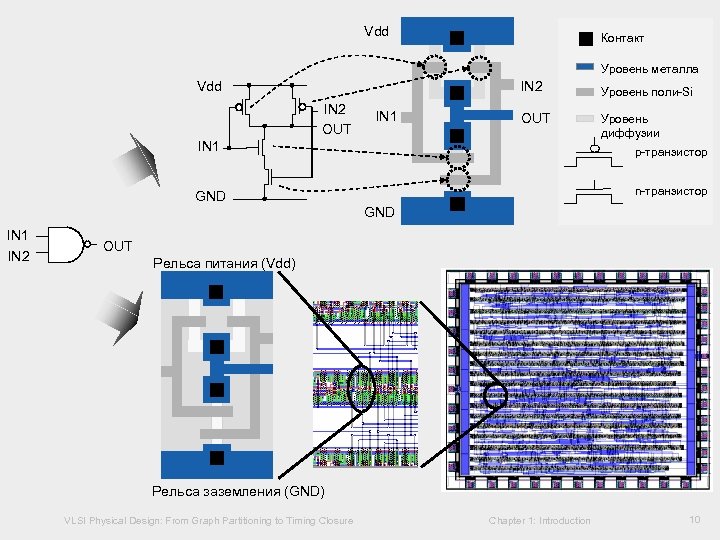

1. 3 VLSI Design Styles Vdd Контакт Vdd IN 2 OUT IN 1 GND IN 2 Уровень диффузии p-транзистор n-транзистор GND OUT Рельса питания (Vdd) Рельса заземления (GND) VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 10 Lienig IN 1 Уровень поли-Si © KLMH Уровень металла

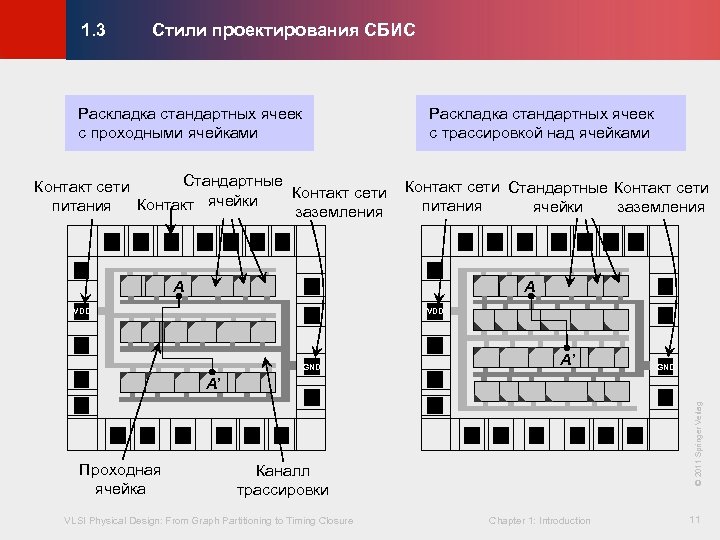

Стили проектирования СБИС © KLMH 1. 3 Раскладка стандартных ячеек с проходными ячейками Раскладка стандартных ячеек с трассировкой над ячейками Стандартные Контакт сети Контакт ячейки питания заземления Контакт сети Стандартные Контакт сети питания ячейки заземления A A VDD GND A’ GND Каналл трассировки VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 11 Lienig Проходная ячейка © 2011 Springer Verlag A’

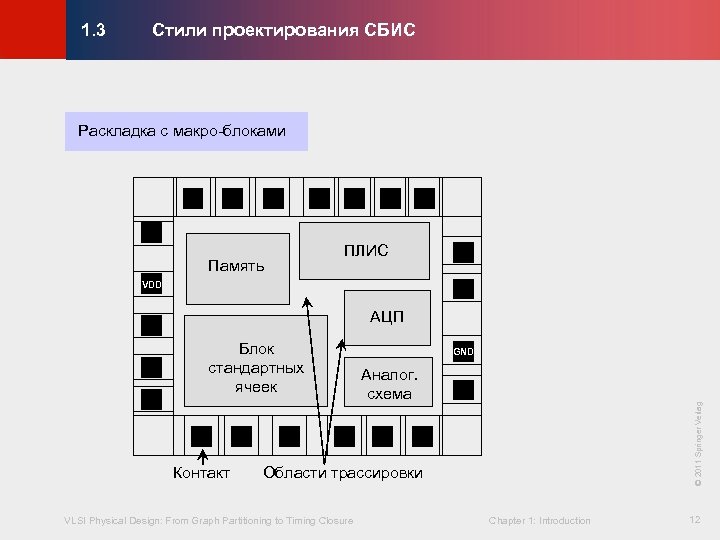

Стили проектирования СБИС © KLMH 1. 3 Раскладка с макро-блоками Память ПЛИС VDD АЦП Аналог. схема © 2011 Springer Verlag Контакт GND Области трассировки VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 12 Lienig Блок стандартных ячеек

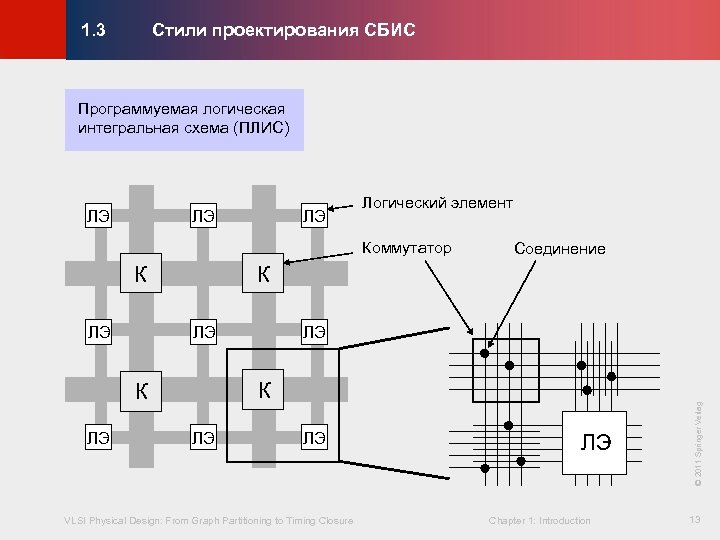

Стили проектирования СБИС © KLMH 1. 3 Программуемая логическая интегральная схема (ПЛИС) ЛЭ LB Коммутатор К SB ЛЭ LB SB К ЛЭ LB VLSI Physical Design: From Graph Partitioning to Timing Closure ЛЭ Chapter 1: Introduction © 2011 Springer Verlag SB К ЛЭ LB Соединение 13 Lienig ЛЭ LB Логический элемент

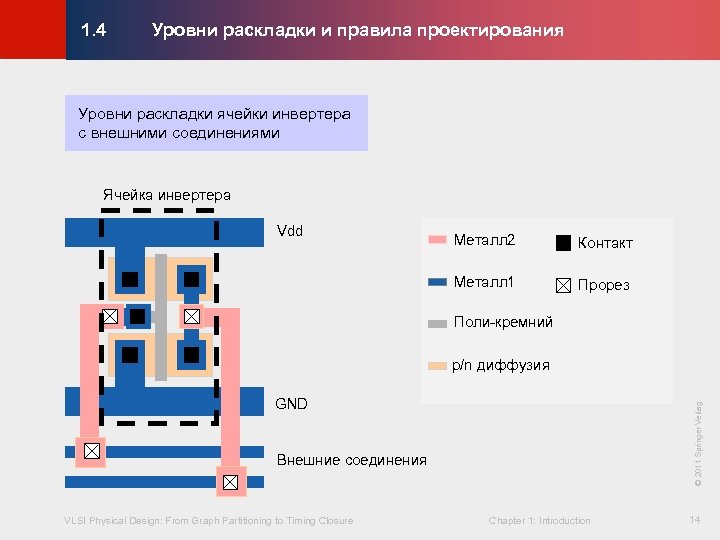

Уровни раскладки и правила проектирования © KLMH 1. 4 Уровни раскладки ячейки инвертера с внешними соединениями Ячейка инвертера Vdd Металл 2 Контакт Металл 1 Прорез Поли-кремний p/n диффузия Внешние соединения VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 14 Lienig © 2011 Springer Verlag GND

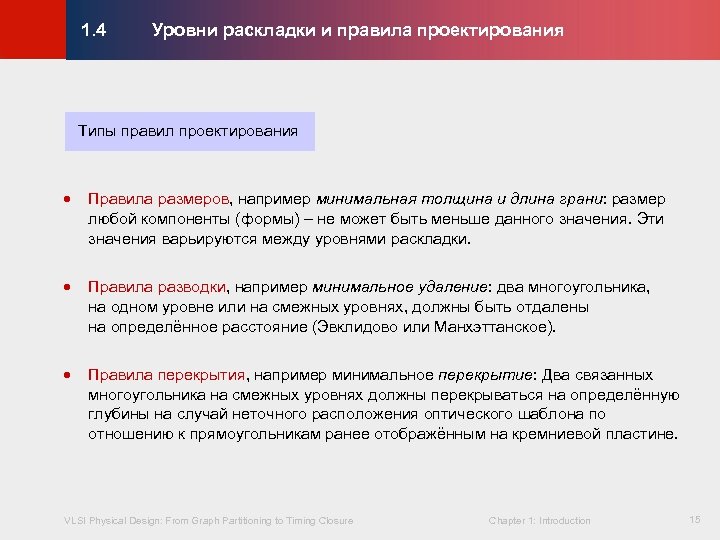

Уровни раскладки и правила проектирования © KLMH 1. 4 Типы правил проектирования Правила размеров, например минимальная толщина и длина грани: размер любой компоненты (формы) – не может быть меньше данного значения. Эти значения варьируются между уровнями раскладки. · Правила разводки, например минимальное удаление: два многоугольника, на одном уровне или на смежных уровнях, должны быть отдалены на определённое расстояние (Эвклидово или Манхэттанское). · Правила перекрытия, например минимальное перекрытие: Два связанных многоугольника на смежных уровнях должны перекрываться на определённую глубины на случай неточного расположения оптического шаблона по отношению к прямоугольникам ранее отображённым на кремниевой пластине. VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 15 Lienig ·

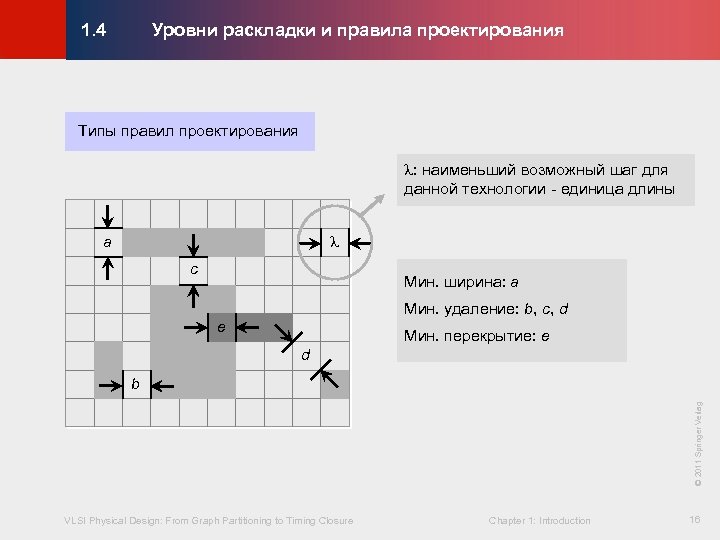

Уровни раскладки и правила проектирования © KLMH 1. 4 Типы правил проектирования : наименьший возможный шаг для данной технологии - единица длины a c Мин. ширина: a Мин. удаление: b, c, d e Мин. перекрытие: e d VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 16 Lienig © 2011 Springer Verlag b

Оптимизация физического проектирования © KLMH 1. 5 Типы ограничений Технологические ограничения делают возможным производство для конкретного узла технологии и выведены из деталей технологии. Например, мин. ширина и мин. удалние между прямоугольниками. · Электрические ограничения обеспечивают желаемые электрические соединения и переключения, например, соблюдения временных ограничений на задержку сигнала а также непревышение максимума ёмкости нагрузки. · Геометрические ограничения по методологии проектирования добавляются чтобы уменьшить общую сложность процесса проектирования. Наприме, использование предпочтительных направлений проводов на каждом уровне металла, и размещение стандартных ячеек в строках. VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 17 Lienig ·

Алгоритмы и сложность © KLMH 1. 6 Сложность по времени · Сложность по времени: время выполнения алгоритма как функция естественной метрики размера задачи (входных данных), позволяет сравнить разные алгоритмы · Сложность представляется асимптотически, по отношению к размеру входных данных n, с использованием символики О-большого или просто O(…) · Время работы t(n) считается порядка f (n), записывается как t(n) = O(f (n)) в случае когда имеет место для k>0 Пример: t(n) = 7 n! + n 2 + 100, тогда t(n) = O(n!) потому что n! растёт быстрее других слагаемых при n . VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 18 Lienig · (достаточное условие, не общее определение)

Алгоритмы и сложность © KLMH 1. 6 Сложность по времени · Пример: полный перебор всевозможных размещений - Даётся: n стандартных ячеек - Задача: разместить n ячеек в одной строке с наименьшей длиной проводов, используя полный перебор - Решение: пространство возможных решений состоит из n! размещений. Если перечисление и оценка длины проводов каждого возможного размещения занимает 1 s, то при n = 20, чтобы найти оптимальное решение требуется 77, 147 лет! · Для многих задач физического проектирования, наилучшие известные алгоритмы требуют экспоненциального времени по n, например O(n!), O(nn), или O(2 n). · Многие такое задачи NP-трудные (NP: non-deterministic polynomial time) - Известные алгоритмы не могут обеспечить оптимальные решения за разумное время VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 19 Lienig Þ Эвристики (как правило) находят почти-оптимальные решения

Алгоритмы и сложность © KLMH 1. 6 Эвристические алгоритмы · Детерминистические: все решения принимаемые алгоритмом можно повторить, так как они не случайны. · Стохастические: Некоторые решения принимаемются алгоритмом случайно, т. е. , с использованием (псевдо-)случайных чисел. Таким образом, запуская алгоритм два раза, с большой вероятностью получим два разных решения. Пример: алгоритм моделирования отжига. · По своей структуре, эвристический алгоритм может быть - Конструктивными: компоненты решения добавляются последовательно пока не готово полное решение. VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 20 Lienig - Итеративные: начиная с полного решения, улучшаем его пока улучшения возможны.

Алгоритмы и сложность © KLMH 1. 6 Эвристические алгоритмы Исходная задача Конструктивный алгоритм Исходная конфигурация Итеративное улучшение Проверить критерий продолжить окончания закончить VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 21 Lienig Вернуть наилучшее найденное решение

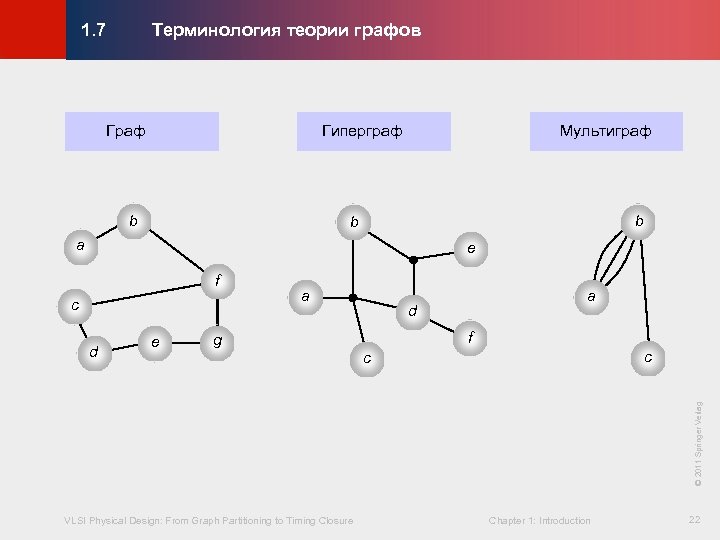

Терминология теории графов © KLMH 1. 7 Граф Гиперграф b Мультиграф b b a e f c g a d f c c VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 22 Lienig © 2011 Springer Verlag d e a

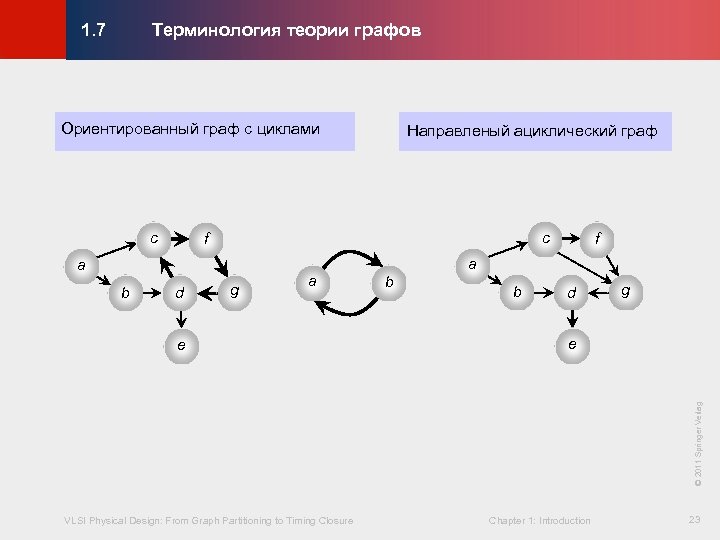

Терминология теории графов © KLMH 1. 7 Ориентированный граф с циклами c c f a b Направленый ациклический граф d g a a b d g e VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 23 Lienig © 2011 Springer Verlag e b f

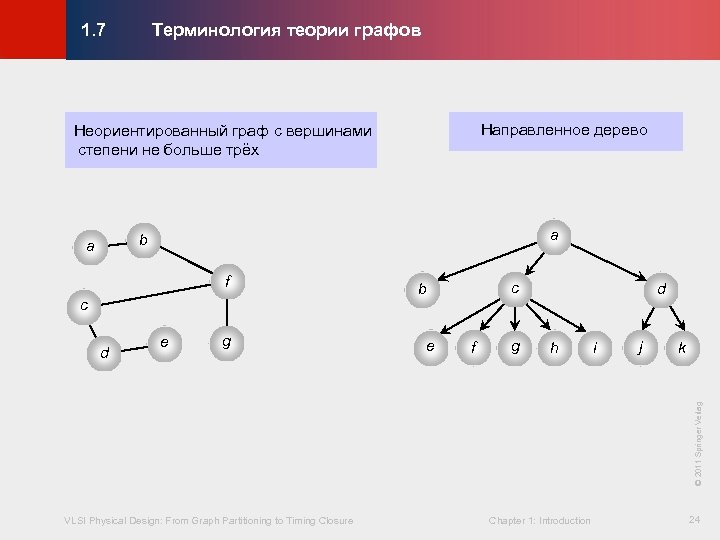

Терминология теории графов © KLMH 1. 7 Направленное дерево Неориентированный граф с вершинами степени не больше трёх a b a f c e g e f g d h i j k VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 24 Lienig © 2011 Springer Verlag d c b

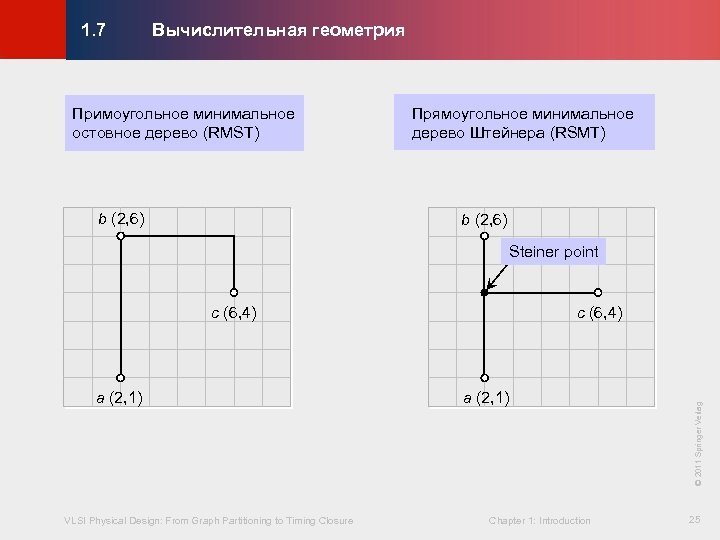

Вычислительная геометрия © KLMH 1. 7 Примоугольное минимальное остовное дерево (RMST) b (2, 6) Прямоугольное минимальное дерево Штейнера (RSMT) b (2, 6) Steiner point VLSI Physical Design: From Graph Partitioning to Timing Closure a (2, 1) Chapter 1: Introduction © 2011 Springer Verlag a (2, 1) c (6, 4) 25 Lienig c (6, 4)

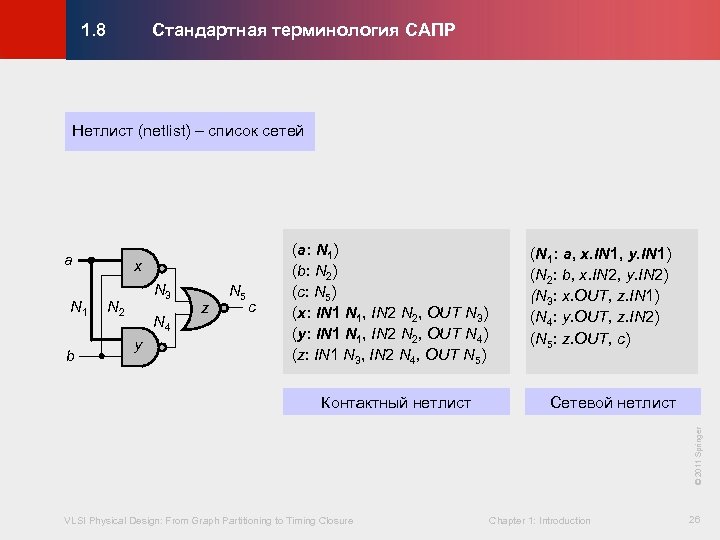

Стандартная терминология САПР © KLMH 1. 8 Нетлист (netlist) – список сетей a N 1 b x N 3 N 2 N 4 y z N 5 c (a: N 1) (b: N 2) (c: N 5) (x: IN 1 N 1, IN 2 N 2, OUT N 3) (y: IN 1 N 1, IN 2 N 2, OUT N 4) (z: IN 1 N 3, IN 2 N 4, OUT N 5) Сетевой нетлист VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 26 Lienig © 2011 Springer Контактный нетлист (N 1: a, x. IN 1, y. IN 1) (N 2: b, x. IN 2, y. IN 2) (N 3: x. OUT, z. IN 1) (N 4: y. OUT, z. IN 2) (N 5: z. OUT, c)

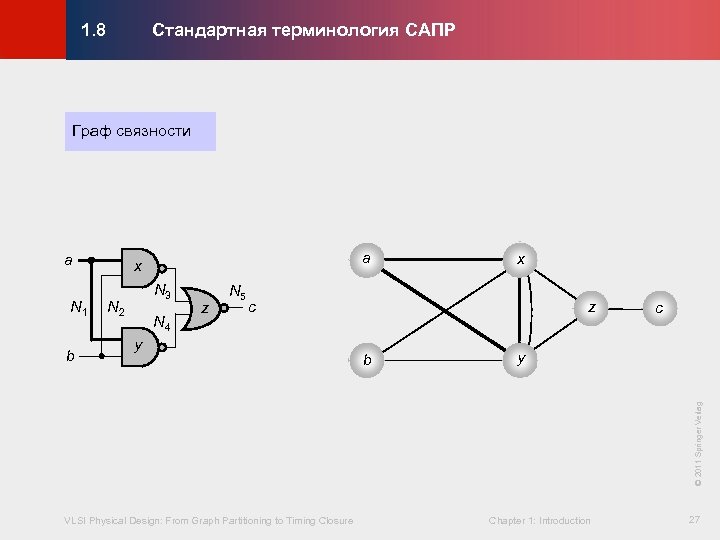

Стандартная терминология САПР © KLMH 1. 8 Граф связности a N 1 N 3 N 2 N 4 z N 5 x c y z b c y VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 27 Lienig © 2011 Springer Verlag b a x

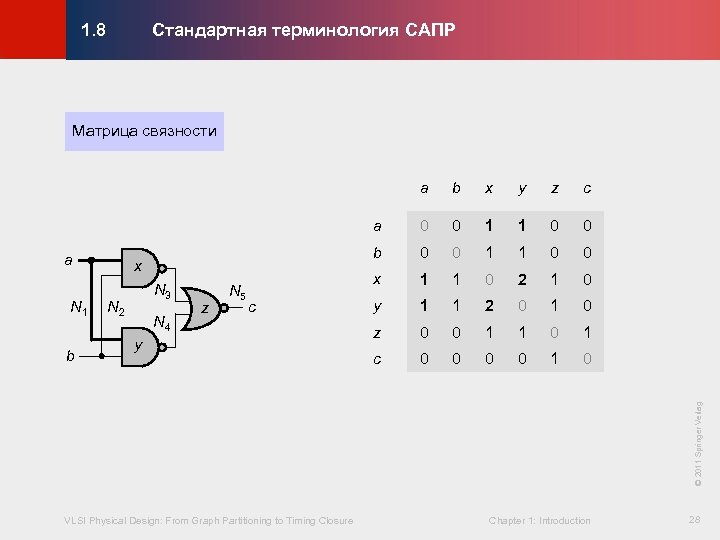

Стандартная терминология САПР © KLMH 1. 8 Матрица связности a N 1 N 2 N 4 z N 5 y c 0 0 1 1 0 0 x c z 1 1 0 2 1 0 y 1 1 2 0 1 0 z 0 0 1 1 0 1 c 0 0 1 0 VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 28 Lienig © 2011 Springer Verlag b N 3 y b x x a a b

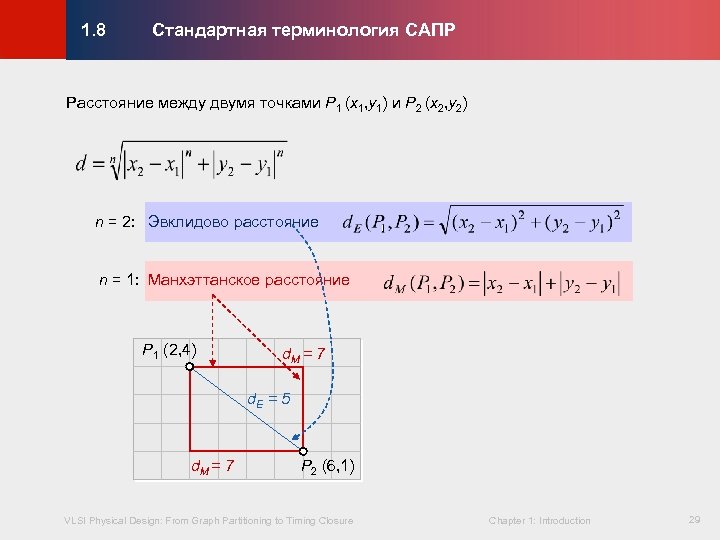

Стандартная терминология САПР © KLMH 1. 8 Расстояние между двумя точками P 1 (x 1, y 1) и P 2 (x 2, y 2) n = 2: Эвклидово расстояние n = 1: Манхэттанское расстояние P 1 (2, 4) d. M = 7 d. E = 5 P 2 (6, 1) VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 29 Lienig d. M = 7

© KLMH Итоги Главы 1 · Прозводство полупроводниковых кристаллов быстро росло с 1960 х годов - Экспоненциальное падение размера, стоимости и мощности транзисторов · Проектирование кристалла невозможно без упрощения и автомаизации - Построчная раскладка со стандартными ячейками и правилами проектирования - Исторически, каждый шаг в маршруте проектировки был автоматизирован разделньно при помощи специализированного ПО для САПР · ПО использует сложные алгоритмы - Многие задачи физического проектирования NP-трудны – решаются при помощи эвристик которые (обычно) находят почти-оптимальные алгоритмы - Детерминистические и стохастические алгоритмы - Конструктивные алгоритмы и итеративное улучшение - Алгоритмы на графах – работают со связностью схемы VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction 30 Lienig - Алгоритмы вычислительной геометрии – работают с раскладкой схемы

0b6a5b15fd385730df7af607e0d954ef.ppt