АВСиКС ЛК2.ppt

- Количество слайдов: 24

Классификация вычислительных систем • Одним из наиболее распространенных способов классификации ЭВМ является систематика Флинна (Flynn). • Данная классификация уделяет основное внимание способам взаимодействия последовательностей (потоков) выполняемых команд и обрабатываемых данных. • Систематика Флинна выделяет следующие основные типы систем: – – SISD (Single Instruction, Single Data) SIMD (Single Instruction, Multiple Data) MISD (Multiple Instruction, Single Data) MIMD (Multiple Instruction, Multiple Data) 1

Системы типа SISD • Системы типа SISD ( «Single Instruction, Single Data» или «Один поток команд, одни данные» ) – системы, в которых существует одиночный поток команд и одиночный поток данных. • Исторически первыми появились ЭВМ именно этого типа. • К SISD можно отнести обычные последовательные ЭВМ (однопроцессорные, одноядерные). • Только SISD-системы в полной мере соответствуют принципам программного управления фон Неймана, поскольку в таких системах процессор по очереди выбирает команды программы и также по очереди обрабатывает данные. • Теоретически SISD-системы могут в полной мере соответствовать классической архитектуре ЭВМ фон Неймана. • Следует однако заметить, что современные однопроцессорные ЭВМ уже не в полной мере соответствуют этой архитектуре. 2

Однопроцессорные архитектуры ЭВМ Среди однопроцессорных ЭВМ SISD-архитектуры можно выделить следующие категории: – ЭВМ с CISC-процессорами – ЭВМ с RISC-процессорами – ЭВМ с суперскалярной архитектурой, которая в свою очередь может быть реализована в следующих вариантах: Классификация ЭВМ архитектуры SISD • аппаратно; • программно (VLIW-процессоры). 3

Архитектура CISC • Компьютеры с CISC (Complex Instruction Set Computer) архитектурой имеют комплексную (полную) систему команд, под управлением которой выполняются всевозможные операции типа «память-память» , «память-регистр» , «регистр — память» , «регистр — регистр» . • Данная архитектура характеризуется: – – – большим числом команд (часто более 200); переменной длиной команд (например, от 1 до 11 байт); значительным числом способов адресации и форматов команд; сложностью команд и многотактностыо их выполнения; наличием микропрограммного управления, что снижает быстродействие и усложняет процессор. • Обмен с памятью в процессе выполнения команды делает практически невозможной глубокую конвейеризацию арифметики, что ограничивает тактовую частоту процессора, а значит, и его производительность. • Процессоры семейства x 86 относятся к CISC-процессорам*. 4

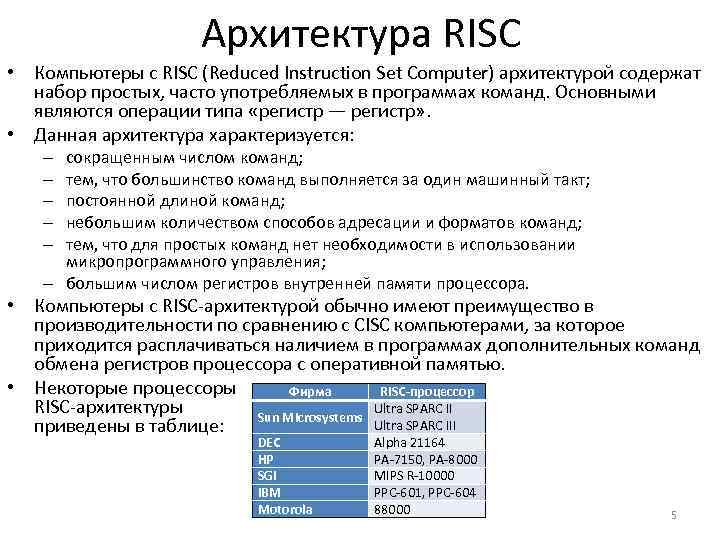

Архитектура RISC • Компьютеры с RISC (Reduced Instruction Set Computer) архитектурой содержат набор простых, часто употребляемых в программах команд. Основными являются операции типа «регистр — регистр» . • Данная архитектура характеризуется: сокращенным числом команд; тем, что большинство команд выполняется за один машинный такт; постоянной длиной команд; небольшим количеством способов адресации и форматов команд; тем, что для простых команд нет необходимости в использовании микропрограммного управления; – большим числом регистров внутренней памяти процессора. – – – • Компьютеры с RISC-архитектурой обычно имеют преимущество в производительности по сравнению с CISC компьютерами, за которое приходится расплачиваться наличием в программах дополнительных команд обмена регистров процессора с оперативной памятью. • Некоторые процессоры Фирма RISC-процессор RISC-архитектуры Ultra SPARC II Sun Microsystems Ultra SPARC III приведены в таблице: DEC HP SGI IBM Motorola Alpha 21164 PA-7150, PA-8000 MIPS R-10000 PPC-601, PPC-604 88000 5

Суперскалярная обработка • В архитектуру суперскалярного процессора закладываются средства, позволяющие одновременно выполнять две или более скалярные операции, т. е. команды обработки пары чисел. • Суперскалярная обработка позволяет увеличить производительность компьютера пропорционально числу одновременно выполняемых операций. • Способы реализации суперскалярной обработки могут быть разными: – Первый способ применяется как в CISC, так и в RISC процессорах и заключается в чисто аппаратном механизме выборки из буфера инструкций (или кэша инструкций) несвязанных команд и параллельном запуске их на исполнение. – Второй способ – программный – будет рассмотрен далее. 6

Аппаратная реализация суперскалярной архитектуры • Аппаратная реализация суперскалярности может применяется как в CISC, так и в RISC – процессорах. • Она заключается в аппаратном механизме выборки из буфера инструкций (или кэша инструкций) несвязанных команд и параллельном запуске их на исполнение. • Этот метод хорош тем, что он «прозрачен» для программиста, составление программ для подобных процессоров не требует никаких специальных усилий, ответственность за параллельное выполнение операций возлагается в основном на аппаратные средства. • Современные процессоры семейства x 86 имеют аппаратно реализованную суперскалярную архитектуру. Процессор Digital Alpha Power PC 620 Power PC 604 с Ultra SPARC HP PA-8000 HPPA-7300 LC Mips R 10000 Mips R 5000 i 486 Pentium Pro Тактовая частота, Мгц 500 225 250 180 160 200 180 25 200 Число транзисторов, млн. 9, 3 6, 9 5, 1 3, 8 3, 9 9, 2 5, 9 3, 6 1, 2 5, 5 Максимальное число команд на цикл 4 4 4 2 3 Среднее число команд на цикл 1, 0 1, 8 1, 5 1, 36 2, 4 1, 35 1, 78 0, 89 0, 45 1, 76 Максимальное и среднее число команд, выполняемых в одном машинном цикле 7

Программная реализация суперскалярной архитектуры • Программная реализация суперскалярности заключается в кардинальной перестройке всего процесса трансляции и исполнения программ: – Уже на этапе подготовки программы компилятор группирует несвязанные операции в пакеты, содержимое которых строго соответствует структуре процессора. Например, если процессор содержит функционально независимые устройства (сложения, умножения, сдвига и деления), то максимум, что компилятор может «уложить» в один пакет - это четыре разнотипные операции: сложение, умножение, сдвиг и деление. – Сформированные пакеты операций преобразуются компилятором в командные слова, которые по сравнению с обычными инструкциями выглядят очень большими. Отсюда и название этих суперкоманд и соответствующей им архитектуры - VLIW (Very Large Instruction Word очень широкое командное слово). • В теории затраты на формирование суперкоманд должны окупаться скоростью их выполнения и простотой аппаратуры процессора, с которого снята вся «интеллектуальная» работа по поиску параллелизма несвязанных операций. • На практике внедрение VLIW-архитектуры затрудняется значительными проблемами эффективной компиляции. 8

Системы типа SIMD • Системы типа SIMD (Single Instruction, Multiple Data) – системы c одиночным потоком команд и множественным потоком данных. • Большинство представителей этого класса являются многопроцессорными вычислительными системами, в которых в каждый момент времени может выполняться одна и та же команда для обработки нескольких информационных элементов. • Возможны два способа построения компьютеров этого класса: – матричная структура; – векторно-конвейерная обработка. • Примером векторного суперкомпьютера архитектуры SIMD может служить игровая приставка Sony Play. Station 3 с процессором Cell. Sony Play. Station 3 9

Матричные структуры • Суть матричной структуры заключается в том, что имеется множество процессорных элементов, исполняющих одну и ту же команду над различными элементами вектора, объединенных коммутатором. • Основная проблема заключается в программировании обмена данными между процессорными элементами через коммутатор. • Примером векторных супер-ЭВМ с матричной структурой является знаменитая в свое время система ILLIAC-IV. ЭВМ ILLIAC-IV 10

Векторно-конвейерные ЭВМ • • В отличие от матричной, векторноконвейерная структура компьютера содержит конвейер операций, на котором обрабатываются параллельно элементы векторов и полученные результаты последовательно записываются в единую память. При этом отпадает необходимость в коммутаторе процессорных элементов, служащем камнем преткновения в матричных компьютерах. Векторно-конвейерную структуру имеют однопроцессорные супер-ЭВМ серии VP фирмы Fujitsu; серии S компании Hitachi; C 90, М 90, Т 90 фирмы Cray Research; Cray-3, Cray-4 фирмы Cray Computer и т. д. Общим для всех векторных суперкомпьютеров является наличие в системе команд векторных операций. Для их выполнения используются векторные регистры. Cray T 90 11

Элементы SIMD-архитектуры в процессорах семейства x 86 • Примерами внедрения элементов SIMD-архитектуры в SISDсистемы является появление в системе команд процессоров семейства x 86 наборов инструкций MMX и SSE/SSE 2/SSE 3/SSE 4. • Эти инструкции предназначены для ускорения выполнения мультимедийных и коммуникационных программ. • В ММХ используются 4 новых типа данных и 57 новых инструкций. • Команды ММХ выполняют одну и ту же функцию с различными частями данных, например, 8 байт графических данных передаются в процессор как одно упакованное 64 -х разрядное число и обрабатываются одной командой. • Команды MMX используют восемь 64 -разрядных регистров, «физически» размещенных в мантиссах регистров с плавающей запятой, и используются в том же режиме процессора, что и команды с плавающей запятой. • Команды SSE позволяют работать со 128 -битными данными. 12

Системы типа MISD • MISD (Multiple Instruction, Single Data) – системы, в которых существует множественный поток команд и одиночный поток данных. • Относительно этого типа систем нет единого мнения: – ряд специалистов считает, что примеров конкретных ЭВМ, соответствующих данному типу вычислительных систем, не существует и введение подобного класса предпринимается для полноты классификации; – другие относят к данному типу, например, систолические вычислительные системы или системы с конвейерной обработкой данных. 13

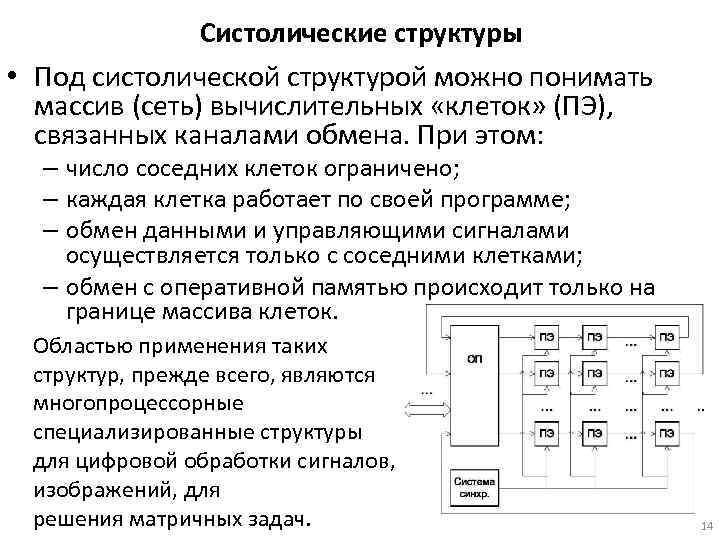

Систолические структуры • Под систолической структурой можно понимать массив (сеть) вычислительных «клеток» (ПЭ), связанных каналами обмена. При этом: – число соседних клеток ограничено; – каждая клетка работает по своей программе; – обмен данными и управляющими сигналами осуществляется только с соседними клетками; – обмен с оперативной памятью происходит только на границе массива клеток. Областью применения таких структур, прежде всего, являются многопроцессорные специализированные структуры для цифровой обработки сигналов, изображений, для решения матричных задач. 14

Систолические алгоритмы Для эффективной реализации вычислений в систолической структуре необходимы так называемые систолические алгоритмы, рассчитанные на аппаратную систолическую реализацию. Они должны удовлетворять определенным требованиям, среди которых: 1. Регулярность, однонаправленность графа вычислений (потокового графа) алгоритма. 2. Ацикличность алгоритма. 3. Возможность разбиения алгоритма на этапы одинаковой сложности и длительности выполнения для построения конвейера. 4. Возможность распараллеливания вычислений. 5. Отсутствие необходимости в больших объемах памяти для сохранения промежуточных результатов и накопления информации. 6. Локальность пересылок информации, отсутствие необходимости в длинных пересылках. 7. Минимальное количество развилок в алгоритме. 8. Минимальное количество входных и выходных точек алгоритма. 9. Минимальное количество разных типов вычислений и операций, используемых в алгоритме. 10. Возможность разбиения алгоритма на подалгоритмы меньшей размерности, и с другой стороны - наращивания алгоритма для решения задач большей размерности. 11. Гарантированная сходимость вычислений за заданное число шагов (итераций). 12. . 15

Системы типа MIMD • MIMD (Multiple Instruction, Multiple Data) – системы c множественным потоком команд и множественным потоком данных. К подобному классу относится большинство параллельных многопроцессорных вычислительных систем. • Для класса MIMD предложена практически общепризнанная структурная схема, в которой дальнейшее разделение типов многопроцессорных систем основывается на используемых способах организации оперативной памяти в этих системах. • Такой подход позволяет различать два важных типа многопроцессорных систем: – multiprocessors (мультипроцессоры или системы с общей разделяемой памятью); – multicomputers (мультикомпьютеры или системы с распределенной памятью). 16

Классификация многопроцессорных вычислительных систем 17

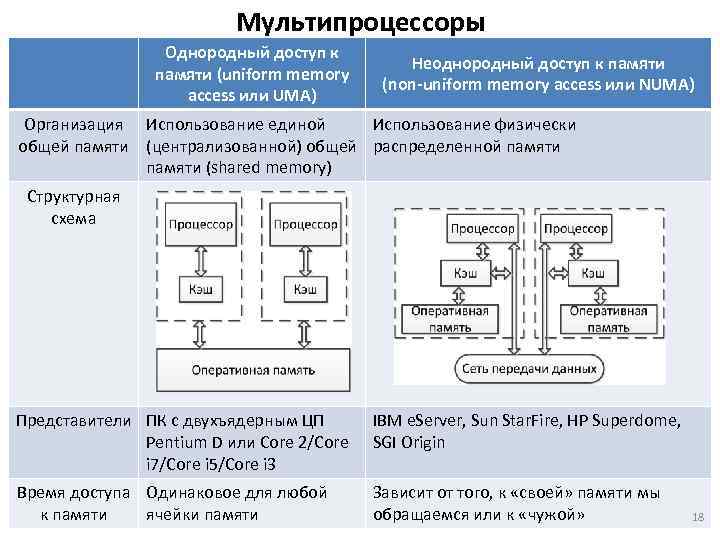

Мультипроцессоры Однородный доступ к Неоднородный доступ общей памяти: При дальнейшей классификации мультипроцессоров учитывается способ построенияк памяти (uniform memory (non-uniform memory access или NUMA) access или UMA) Организация Использование единой Использование физически общей памяти (централизованной) общей распределенной памяти (shared memory) Структурная схема Представители ПК с двухъядерным ЦП Pentium D или Core 2/Core i 7/Core i 5/Core i 3 IBM e. Server, Sun Star. Fire, HP Superdome, SGI Origin Время доступа Одинаковое для любой к памяти ячейки памяти Зависит от того, к «своей» памяти мы обращаемся или к «чужой» 18

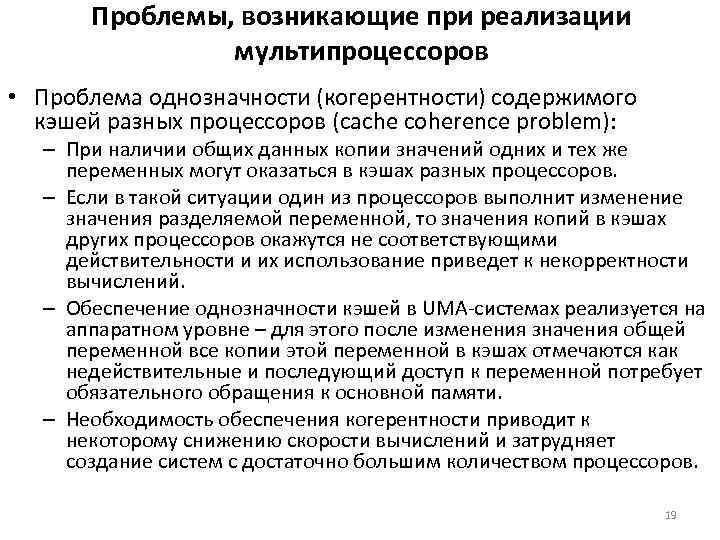

Проблемы, возникающие при реализации мультипроцессоров • Проблема однозначности (когерентности) содержимого кэшей разных процессоров (cache coherence problem): – При наличии общих данных копии значений одних и тех же переменных могут оказаться в кэшах разных процессоров. – Если в такой ситуации один из процессоров выполнит изменение значения разделяемой переменной, то значения копий в кэшах других процессоров окажутся не соответствующими действительности и их использование приведет к некорректности вычислений. – Обеспечение однозначности кэшей в UMA-системах реализуется на аппаратном уровне – для этого после изменения значения общей переменной все копии этой переменной в кэшах отмечаются как недействительные и последующий доступ к переменной потребует обязательного обращения к основной памяти. – Необходимость обеспечения когерентности приводит к некоторому снижению скорости вычислений и затрудняет создание систем с достаточно большим количеством процессоров. 19

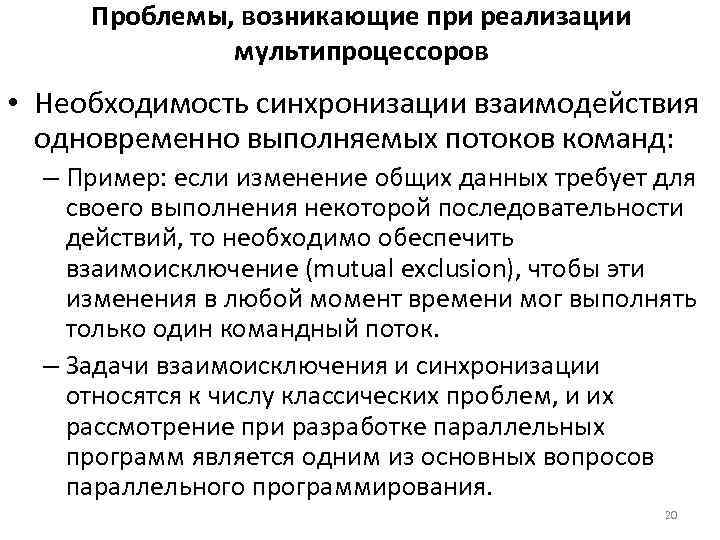

Проблемы, возникающие при реализации мультипроцессоров • Необходимость синхронизации взаимодействия одновременно выполняемых потоков команд: – Пример: если изменение общих данных требует для своего выполнения некоторой последовательности действий, то необходимо обеспечить взаимоисключение (mutual exclusion), чтобы эти изменения в любой момент времени мог выполнять только один командный поток. – Задачи взаимоисключения и синхронизации относятся к числу классических проблем, и их рассмотрение при разработке параллельных программ является одним из основных вопросов параллельного программирования. 20

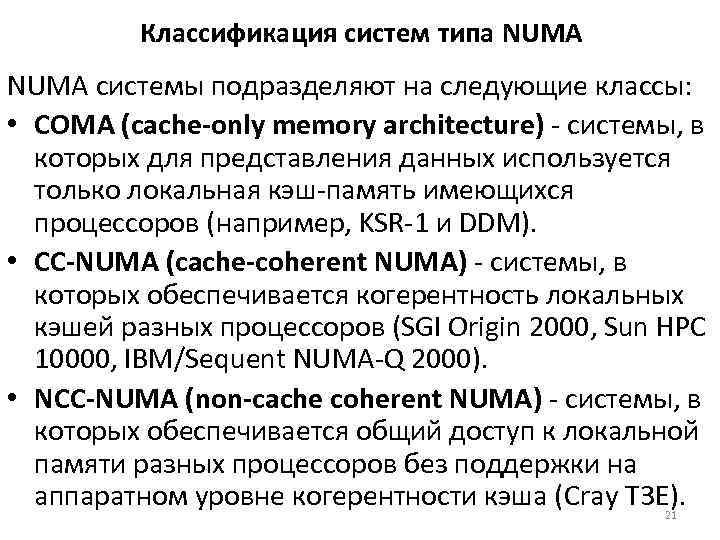

Классификация систем типа NUMA системы подразделяют на следующие классы: • COMA (cache-only memory architecture) - системы, в которых для представления данных используется только локальная кэш-память имеющихся процессоров (например, KSR-1 и DDM). • CC-NUMA (cache-coherent NUMA) - системы, в которых обеспечивается когерентность локальных кэшей разных процессоров (SGI Origin 2000, Sun HPC 10000, IBM/Sequent NUMA-Q 2000). • NCC-NUMA (non-cache coherent NUMA) - системы, в которых обеспечивается общий доступ к локальной памяти разных процессоров без поддержки на аппаратном уровне когерентности кэша (Cray T 3 E). 21

Особенности использования систем типа NUMA • Использование распределенной общей памяти упрощает проблемы создания мультипроцессоров (известны примеры систем с несколькими тысячами процессоров, тогда как для UMA систем их число обычно не превышает нескольких десятков). • Однако возникающие при этом проблемы эффективного использования распределенной памяти (время доступа к локальной и удаленной памяти может различаться на несколько порядков) приводят к существенному повышению сложности параллельного программирования. 22

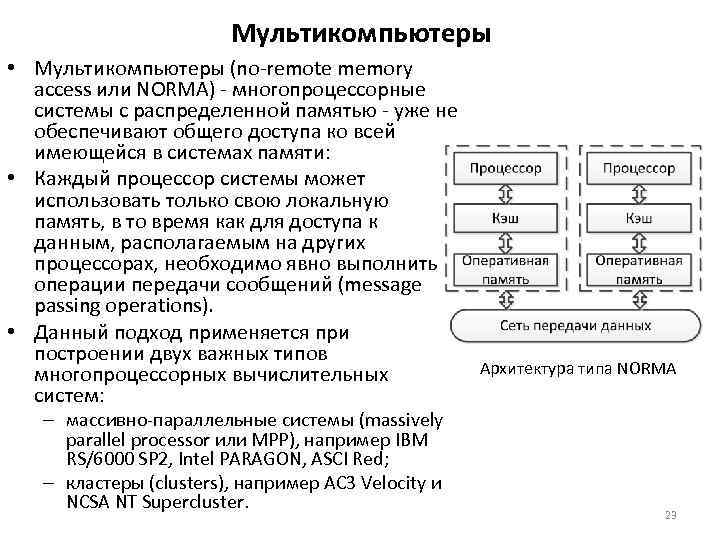

Мультикомпьютеры • Мультикомпьютеры (no-remote memory access или NORMA) - многопроцессорные системы с распределенной памятью - уже не обеспечивают общего доступа ко всей имеющейся в системах памяти: • Каждый процессор системы может использовать только свою локальную память, в то время как для доступа к данным, располагаемым на других процессорах, необходимо явно выполнить операции передачи сообщений (message passing operations). • Данный подход применяется при построении двух важных типов многопроцессорных вычислительных систем: – массивно-параллельные системы (massively parallel processor или MPP), например IBM RS/6000 SP 2, Intel PARAGON, ASCI Red; – кластеры (clusters), например AC 3 Velocity и NCSA NT Supercluster. Архитектура типа NORMA 23

Что такое кластер? • • Под кластером обычно понимается множество отдельных компьютеров, объединенных в сеть, для которых при помощи специальных аппаратно-программных средств обеспечивается возможность унифицированного управления (single system image), надежного функционирования (availability) и эффективного использования (performance). Кластеры могут быть образованы на базе уже существующих у потребителей отдельных компьютеров либо же сконструированы из типовых компьютерных элементов, что обычно не требует значительных финансовых затрат. Организация взаимодействия вычислительных узлов кластера при помощи передачи сообщений приводит к значительным временным задержкам, что накладывает ограничения на тип разрабатываемых параллельных алгоритмов и программ. Основным преимуществом кластеров, объясняющим взрывной рост их популярности в последние годы является тот факт, что кластеры весьма дёшевы (разумеется, по меркам суперкомпьютеров). Суперкомпьютер «СКИФ Мономах» Вл. ГУ (цена первой очереди около $1 млн. ) 24

АВСиКС ЛК2.ppt