Презентация архитектуры.ppt

- Количество слайдов: 91

Классификация ЭВМ. План: 1. По принципу действия; 2. По этапу создания и элементарной базе; 3. По назначению; 4. По размеру вычислительной мощности

Классификация ЭВМ. План: 1. По принципу действия; 2. По этапу создания и элементарной базе; 3. По назначению; 4. По размеру вычислительной мощности

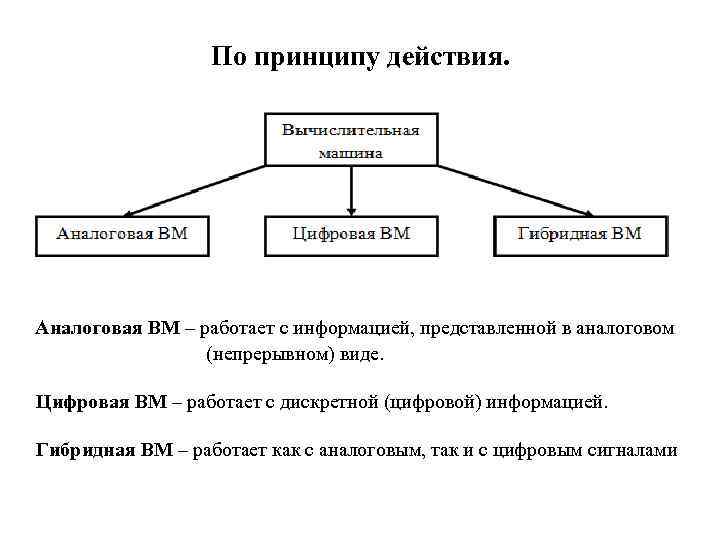

По принципу действия. Аналоговая ВМ – работает с информацией, представленной в аналоговом (непрерывном) виде. Цифровая ВМ – работает с дискретной (цифровой) информацией. Гибридная ВМ – работает как с аналоговым, так и с цифровым сигналами

По принципу действия. Аналоговая ВМ – работает с информацией, представленной в аналоговом (непрерывном) виде. Цифровая ВМ – работает с дискретной (цифровой) информацией. Гибридная ВМ – работает как с аналоговым, так и с цифровым сигналами

По этапу создания и элементарной базе. • Первое поколение: 50 – е годы. ЭВМ на электронно-вакуумных лампах; • Второе поколение: 60 –е годы. ЭВМ на полупроводниковых приборах (транзисторах); • Третье поколение: 70 – е годы. ЭВМ на интегральных схемах с малой и средней степенью интеграции (тысячи транзисторов в одном корпусе); • Четвертое поколение: 80 – 90 – е годы. ЭВМ на микросхемах со сверхбольшой интеграцией, основная из которых микропроцессор; • Пятое поколение: Настоящее время. Компьютер со многими десятками параллельно работающих микропроцессоров; • Шестое поколение. Оптоэлектронные компьютеры с массовым параллелизмом и нейтронной структурой.

По этапу создания и элементарной базе. • Первое поколение: 50 – е годы. ЭВМ на электронно-вакуумных лампах; • Второе поколение: 60 –е годы. ЭВМ на полупроводниковых приборах (транзисторах); • Третье поколение: 70 – е годы. ЭВМ на интегральных схемах с малой и средней степенью интеграции (тысячи транзисторов в одном корпусе); • Четвертое поколение: 80 – 90 – е годы. ЭВМ на микросхемах со сверхбольшой интеграцией, основная из которых микропроцессор; • Пятое поколение: Настоящее время. Компьютер со многими десятками параллельно работающих микропроцессоров; • Шестое поколение. Оптоэлектронные компьютеры с массовым параллелизмом и нейтронной структурой.

По назначению.

По назначению.

По размеру вычислительной мощности.

По размеру вычислительной мощности.

Принцип действия ЭВМ. План: 1. Структура ЭВМ; 2. Основные характеристики ЭВМ; 3. Понятие о системе программного обеспе-чения (ПО).

Принцип действия ЭВМ. План: 1. Структура ЭВМ; 2. Основные характеристики ЭВМ; 3. Понятие о системе программного обеспе-чения (ПО).

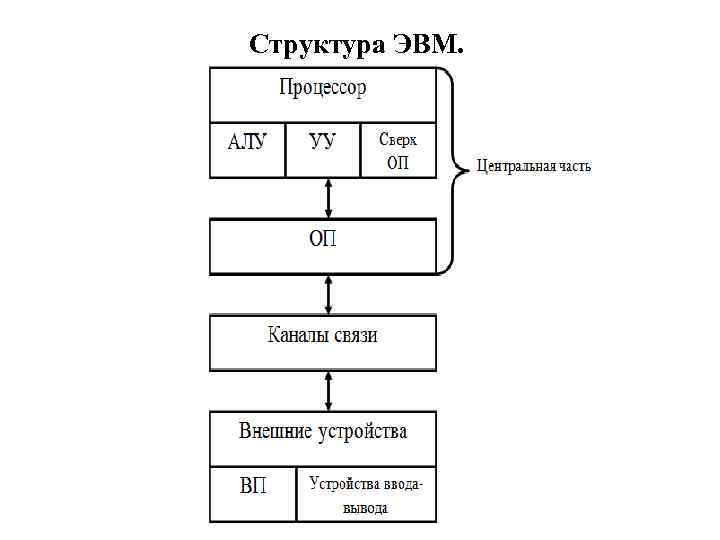

Структура ЭВМ.

Структура ЭВМ.

1. Процессор – основной вычислительный блок ПК. В его состав входят: 1. 1 Арифметико-логическое устройство (АЛУ) – выполняет простейшие арифметические и логические действия. Устройство 1. 2 управления (УУ) – управляет работой процессора и служит для связи с другими узлами. 1. 3 Сверх оперативная память (ОП) – внутренняя память МП, содержащая алгоритмы запуска процессора. 2. Оперативная память (ОП) – энергозависимая память ПК в которой хранятся команды и данные. Вместе с МП образуют центральную часть ЭВМ. 3. Каналы связи – предназначены для связи центральной части с внешними устройствами. 4. Внешние устройства: 4. 1 Внешняя память (ВП) – не энергозависимая память, обладающая большой емкостью, но малым быстродействием по сравнению с ОП. 4. 2 Устройства ввода-вывода (клавиатура и другие).

1. Процессор – основной вычислительный блок ПК. В его состав входят: 1. 1 Арифметико-логическое устройство (АЛУ) – выполняет простейшие арифметические и логические действия. Устройство 1. 2 управления (УУ) – управляет работой процессора и служит для связи с другими узлами. 1. 3 Сверх оперативная память (ОП) – внутренняя память МП, содержащая алгоритмы запуска процессора. 2. Оперативная память (ОП) – энергозависимая память ПК в которой хранятся команды и данные. Вместе с МП образуют центральную часть ЭВМ. 3. Каналы связи – предназначены для связи центральной части с внешними устройствами. 4. Внешние устройства: 4. 1 Внешняя память (ВП) – не энергозависимая память, обладающая большой емкостью, но малым быстродействием по сравнению с ОП. 4. 2 Устройства ввода-вывода (клавиатура и другие).

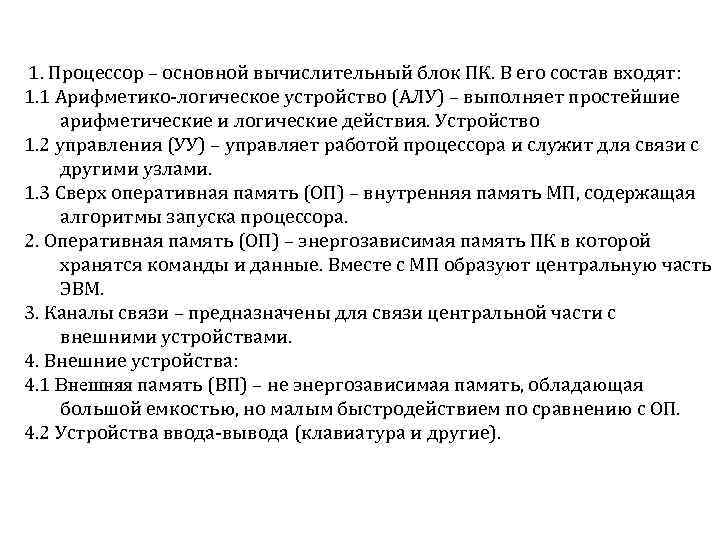

Основные характеристики ЭВМ. 1. Длина машинного слова (8, 16, 32 бит); 2. Тактовая чистота; 3. Емкость ОП; 4. Коэффициент эффективности:

Основные характеристики ЭВМ. 1. Длина машинного слова (8, 16, 32 бит); 2. Тактовая чистота; 3. Емкость ОП; 4. Коэффициент эффективности:

Понятие о системе ПО. Ач – апаратная часть; ОС – операционные системы; ППП – пакет прикладных программ; Утилиты – текстовые программы Утилиты ОС Ач ППП

Понятие о системе ПО. Ач – апаратная часть; ОС – операционные системы; ППП – пакет прикладных программ; Утилиты – текстовые программы Утилиты ОС Ач ППП

Позиционные системы счисления. План: 1. Понятие о системе счисления; 2. Перевод чисел из одной системы счисления в другую; 3. Из десятеричной в двоичною; 4. Из двоичной в шестнадцатеричную и обратно; 5. Из двоичной в десятеричную

Позиционные системы счисления. План: 1. Понятие о системе счисления; 2. Перевод чисел из одной системы счисления в другую; 3. Из десятеричной в двоичною; 4. Из двоичной в шестнадцатеричную и обратно; 5. Из двоичной в десятеричную

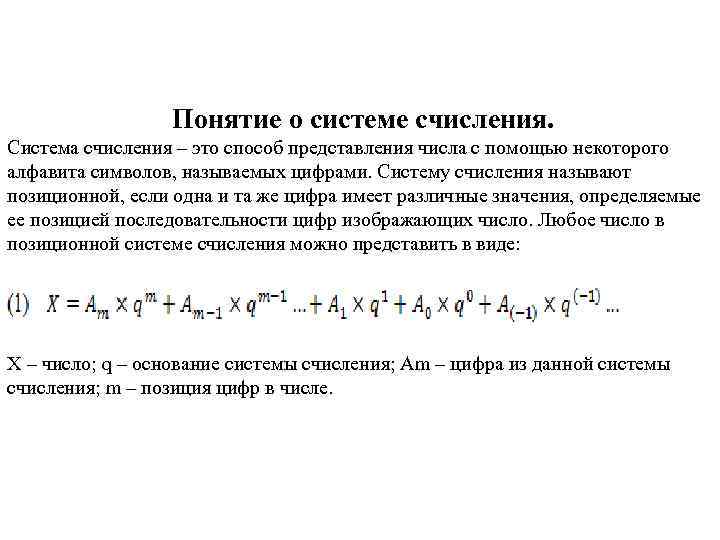

Понятие о системе счисления. Система счисления – это способ представления числа с помощью некоторого алфавита символов, называемых цифрами. Систему счисления называют позиционной, если одна и та же цифра имеет различные значения, определяемые ее позицией последовательности цифр изображающих число. Любое число в позиционной системе счисления можно представить в виде: X – число; q – основание системы счисления; Am – цифра из данной системы счисления; m – позиция цифр в числе.

Понятие о системе счисления. Система счисления – это способ представления числа с помощью некоторого алфавита символов, называемых цифрами. Систему счисления называют позиционной, если одна и та же цифра имеет различные значения, определяемые ее позицией последовательности цифр изображающих число. Любое число в позиционной системе счисления можно представить в виде: X – число; q – основание системы счисления; Am – цифра из данной системы счисления; m – позиция цифр в числе.

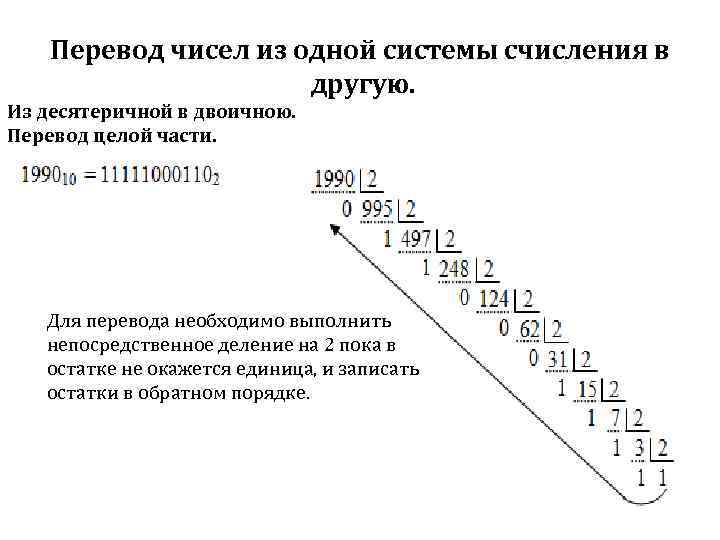

Перевод чисел из одной системы счисления в другую. Из десятеричной в двоичною. Перевод целой части. Для перевода необходимо выполнить непосредственное деление на 2 пока в остатке не окажется единица, и записать остатки в обратном порядке.

Перевод чисел из одной системы счисления в другую. Из десятеричной в двоичною. Перевод целой части. Для перевода необходимо выполнить непосредственное деление на 2 пока в остатке не окажется единица, и записать остатки в обратном порядке.

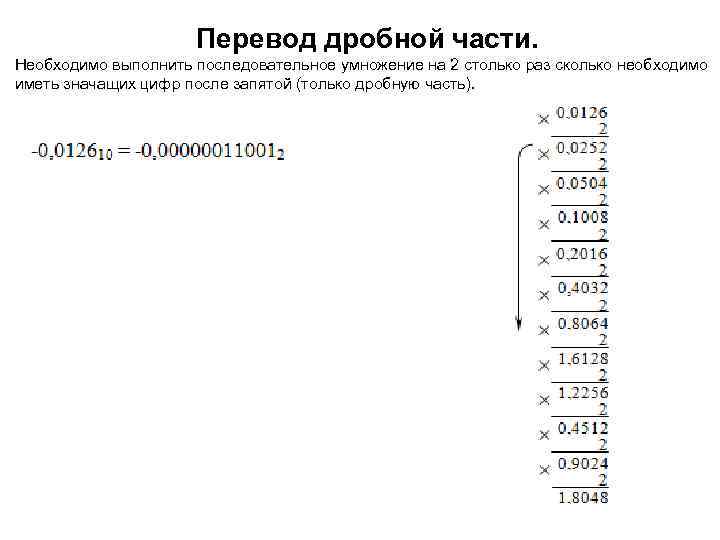

Перевод дробной части. Необходимо выполнить последовательное умножение на 2 столько раз сколько необходимо иметь значащих цифр после запятой (только дробную часть).

Перевод дробной части. Необходимо выполнить последовательное умножение на 2 столько раз сколько необходимо иметь значащих цифр после запятой (только дробную часть).

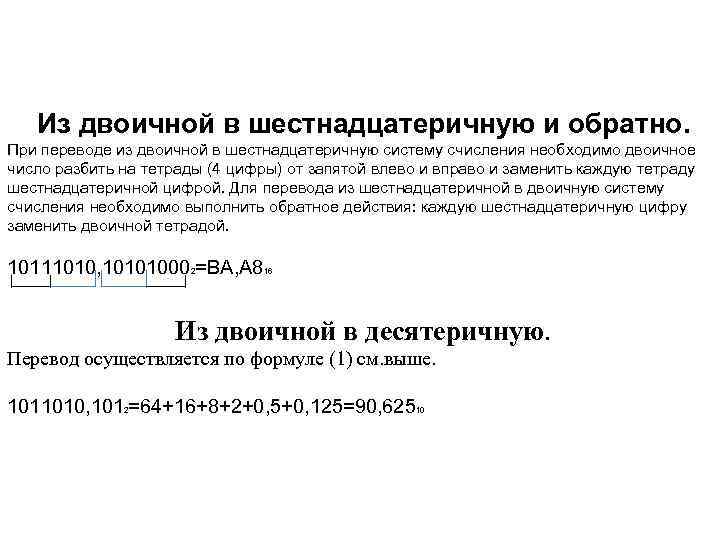

Из двоичной в шестнадцатеричную и обратно. При переводе из двоичной в шестнадцатеричную систему счисления необходимо двоичное число разбить на тетрады (4 цифры) от запятой влево и вправо и заменить каждую тетраду шестнадцатеричной цифрой. Для перевода из шестнадцатеричной в двоичную систему счисления необходимо выполнить обратное действия: каждую шестнадцатеричную цифру заменить двоичной тетрадой. 10111010, 10101000 =BA, A 8 2 16 Из двоичной в десятеричную. Перевод осуществляется по формуле (1) см. выше. 1011010, 101 =64+16+8+2+0, 5+0, 125=90, 625 2 10

Из двоичной в шестнадцатеричную и обратно. При переводе из двоичной в шестнадцатеричную систему счисления необходимо двоичное число разбить на тетрады (4 цифры) от запятой влево и вправо и заменить каждую тетраду шестнадцатеричной цифрой. Для перевода из шестнадцатеричной в двоичную систему счисления необходимо выполнить обратное действия: каждую шестнадцатеричную цифру заменить двоичной тетрадой. 10111010, 10101000 =BA, A 8 2 16 Из двоичной в десятеричную. Перевод осуществляется по формуле (1) см. выше. 1011010, 101 =64+16+8+2+0, 5+0, 125=90, 625 2 10

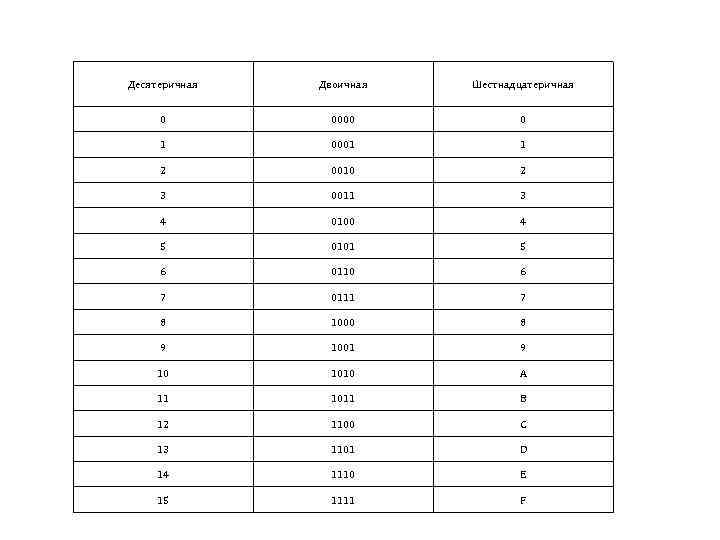

Десятеричная Двоичная Шестнадцатеричная 0 0000 0 1 0001 1 2 0010 2 3 0011 3 4 0100 4 5 0101 5 6 0110 6 7 0111 7 8 1000 8 9 1001 9 10 1010 A 11 1011 B 12 1100 C 13 1101 D 14 1110 E 15 1111 F

Десятеричная Двоичная Шестнадцатеричная 0 0000 0 1 0001 1 2 0010 2 3 0011 3 4 0100 4 5 0101 5 6 0110 6 7 0111 7 8 1000 8 9 1001 9 10 1010 A 11 1011 B 12 1100 C 13 1101 D 14 1110 E 15 1111 F

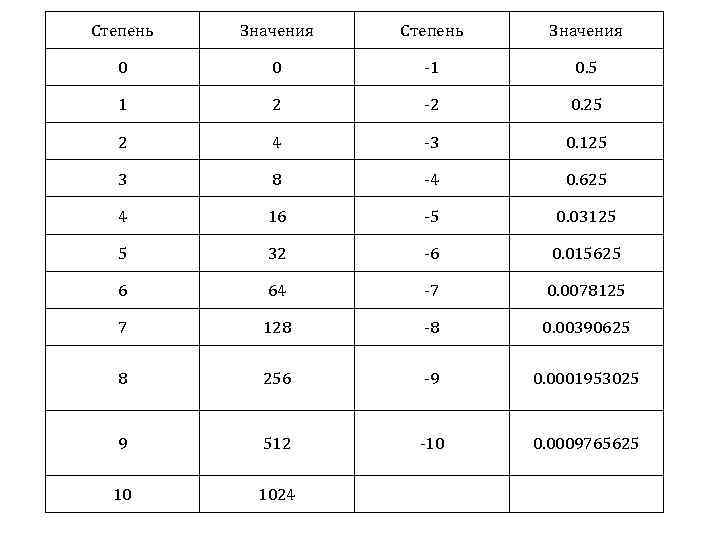

Степень Значения 0 0 -1 0. 5 1 2 -2 0. 25 2 4 -3 0. 125 3 8 -4 0. 625 4 16 -5 0. 03125 5 32 -6 0. 015625 6 64 -7 0. 0078125 7 128 -8 0. 00390625 8 256 -9 0. 0001953025 9 512 -10 0. 0009765625 10 1024

Степень Значения 0 0 -1 0. 5 1 2 -2 0. 25 2 4 -3 0. 125 3 8 -4 0. 625 4 16 -5 0. 03125 5 32 -6 0. 015625 6 64 -7 0. 0078125 7 128 -8 0. 00390625 8 256 -9 0. 0001953025 9 512 -10 0. 0009765625 10 1024

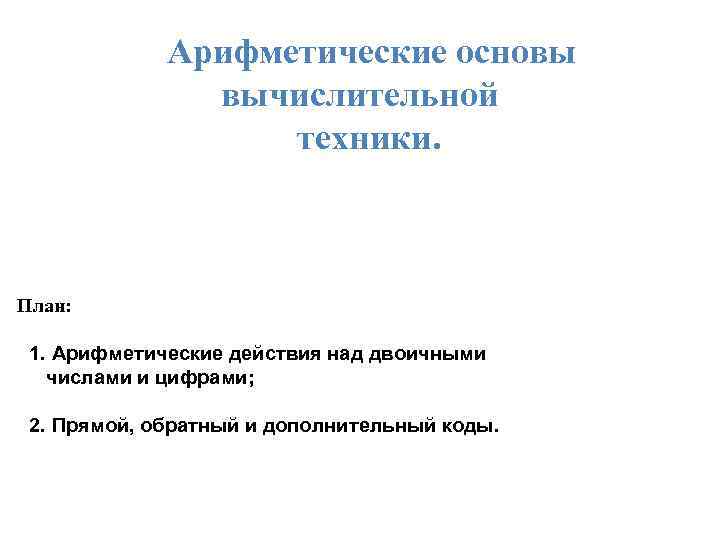

Арифметические основы вычислительной техники. План: 1. Арифметические действия над двоичными числами и цифрами; 2. Прямой, обратный и дополнительный коды.

Арифметические основы вычислительной техники. План: 1. Арифметические действия над двоичными числами и цифрами; 2. Прямой, обратный и дополнительный коды.

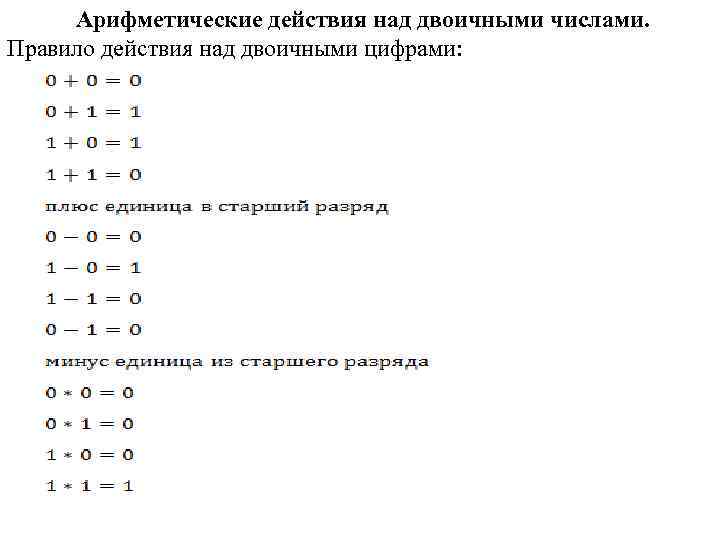

Арифметические действия над двоичными числами. Правило действия над двоичными цифрами:

Арифметические действия над двоичными числами. Правило действия над двоичными цифрами:

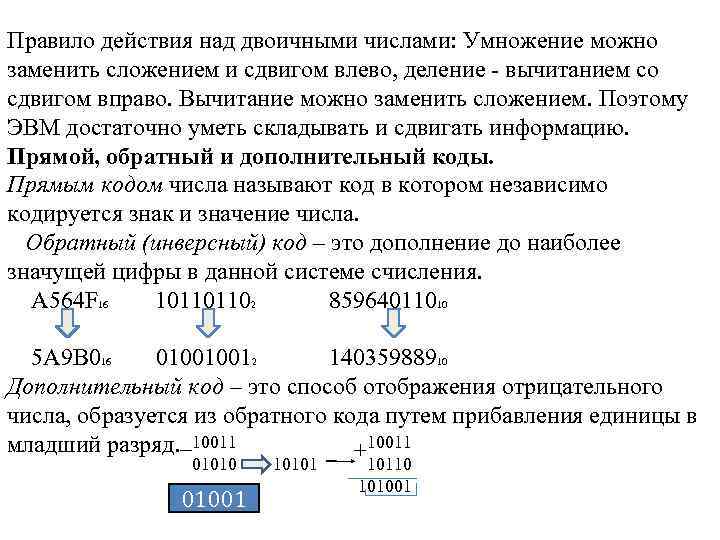

Правило действия над двоичными числами: Умножение можно заменить сложением и сдвигом влево, деление - вычитанием со сдвигом вправо. Вычитание можно заменить сложением. Поэтому ЭВМ достаточно уметь складывать и сдвигать информацию. Прямой, обратный и дополнительный коды. Прямым кодом числа называют код в котором независимо кодируется знак и значение числа. Обратный (инверсный) код – это дополнение до наиболее значущей цифры в данной системе счисления. А 564 F 16 101101102 85964011010 5 A 9 B 016 010010012 14035988910 Дополнительный код – это способ отображения отрицательного числа, образуется из обратного кода путем прибавления единицы в 10011 младший разряд. 10011 01010 01001 10110 101001

Правило действия над двоичными числами: Умножение можно заменить сложением и сдвигом влево, деление - вычитанием со сдвигом вправо. Вычитание можно заменить сложением. Поэтому ЭВМ достаточно уметь складывать и сдвигать информацию. Прямой, обратный и дополнительный коды. Прямым кодом числа называют код в котором независимо кодируется знак и значение числа. Обратный (инверсный) код – это дополнение до наиболее значущей цифры в данной системе счисления. А 564 F 16 101101102 85964011010 5 A 9 B 016 010010012 14035988910 Дополнительный код – это способ отображения отрицательного числа, образуется из обратного кода путем прибавления единицы в 10011 младший разряд. 10011 01010 01001 10110 101001

Логические основы. План: 1. Понятие алгебры логики; 2. Простейшие логические функции; 3. Основные правила преобразования формул.

Логические основы. План: 1. Понятие алгебры логики; 2. Простейшие логические функции; 3. Основные правила преобразования формул.

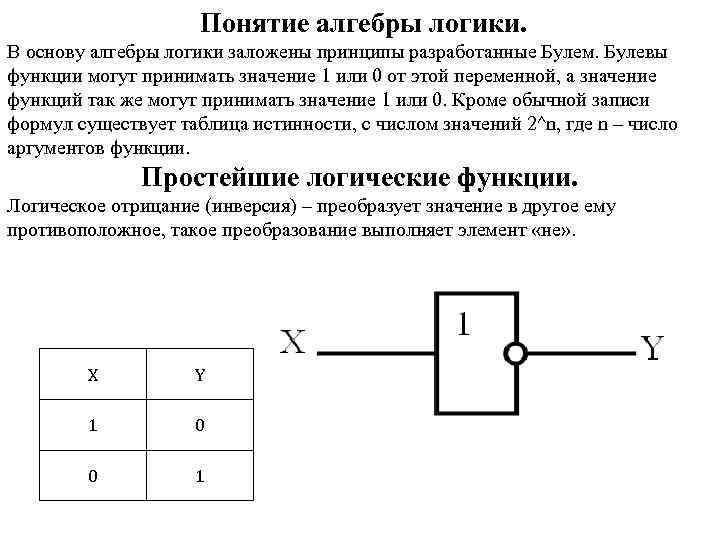

Понятие алгебры логики. В основу алгебры логики заложены принципы разработанные Булем. Булевы функции могут принимать значение 1 или 0 от этой переменной, а значение функций так же могут принимать значение 1 или 0. Кроме обычной записи формул существует таблица истинности, с числом значений 2^n, где n – число аргументов функции. Простейшие логические функции. Логическое отрицание (инверсия) – преобразует значение в другое ему противоположное, такое преобразование выполняет элемент «не» . X Y 1 0 0 1

Понятие алгебры логики. В основу алгебры логики заложены принципы разработанные Булем. Булевы функции могут принимать значение 1 или 0 от этой переменной, а значение функций так же могут принимать значение 1 или 0. Кроме обычной записи формул существует таблица истинности, с числом значений 2^n, где n – число аргументов функции. Простейшие логические функции. Логическое отрицание (инверсия) – преобразует значение в другое ему противоположное, такое преобразование выполняет элемент «не» . X Y 1 0 0 1

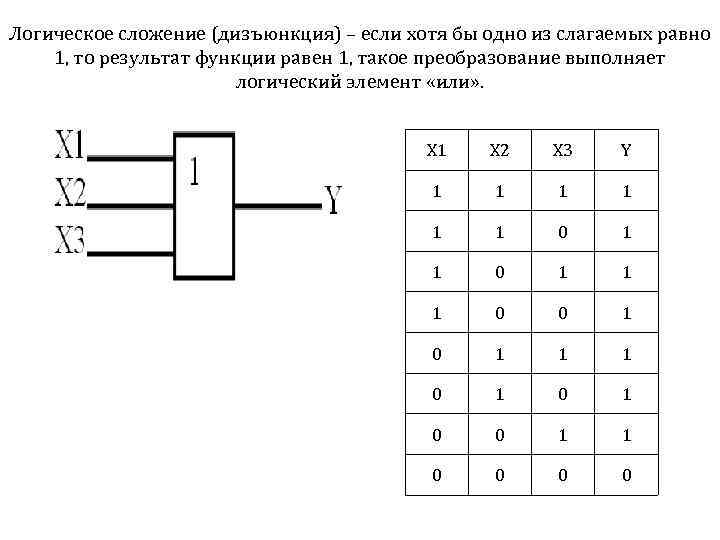

Логическое сложение (дизъюнкция) – если хотя бы одно из слагаемых равно 1, то результат функции равен 1, такое преобразование выполняет логический элемент «или» . X 1 X 2 X 3 Y 1 1 1 0 0 1 1 1 0 1 0 0 1 1 0 0

Логическое сложение (дизъюнкция) – если хотя бы одно из слагаемых равно 1, то результат функции равен 1, такое преобразование выполняет логический элемент «или» . X 1 X 2 X 3 Y 1 1 1 0 0 1 1 1 0 1 0 0 1 1 0 0

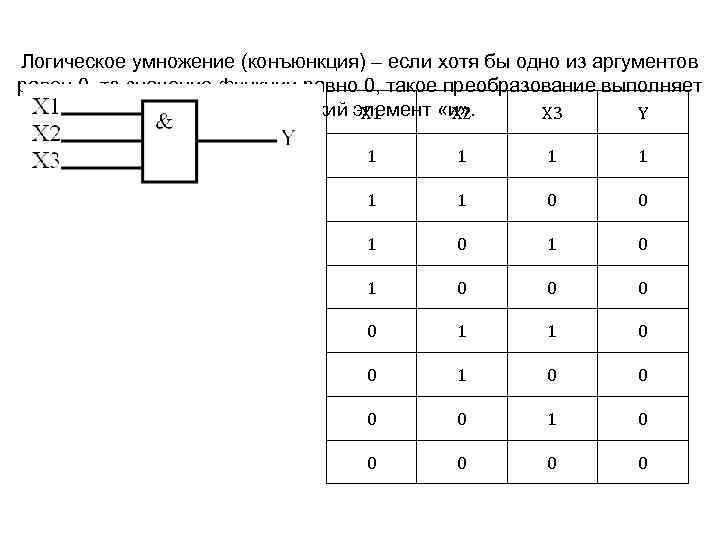

Логическое умножение (конъюнкция) – если хотя бы одно из аргументов равен 0, то значение функции равно 0, такое преобразование выполняет логический элемент «и» . X 1 X 2 X 3 Y 1 1 1 0 0 1 0 1 0 0 1 1 0 0 0 0 1 0 0 0

Логическое умножение (конъюнкция) – если хотя бы одно из аргументов равен 0, то значение функции равно 0, такое преобразование выполняет логический элемент «и» . X 1 X 2 X 3 Y 1 1 1 0 0 1 0 1 0 0 1 1 0 0 0 0 1 0 0 0

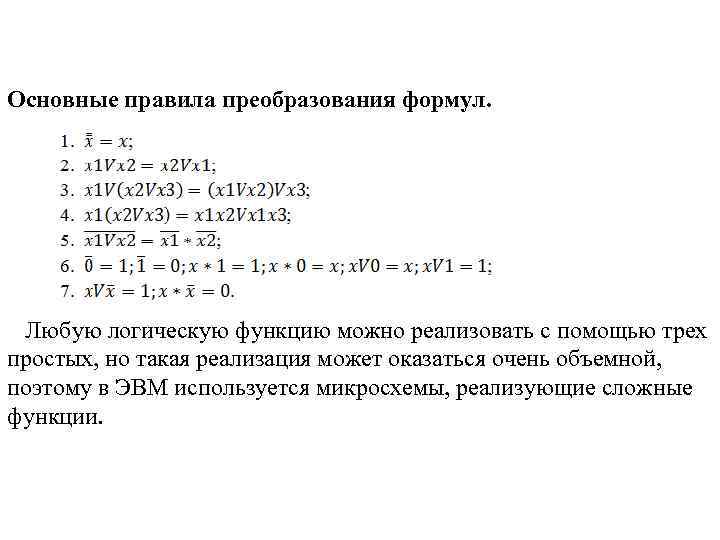

Основные правила преобразования формул. Любую логическую функцию можно реализовать с помощью трех простых, но такая реализация может оказаться очень объемной, поэтому в ЭВМ используется микросхемы, реализующие сложные функции.

Основные правила преобразования формул. Любую логическую функцию можно реализовать с помощью трех простых, но такая реализация может оказаться очень объемной, поэтому в ЭВМ используется микросхемы, реализующие сложные функции.

Основные типовые элементы ЭВМ. План: 1. Запись информации в регистр; 2. Передача информации от одного регистра в другой; 3. Сдвигающий регистр.

Основные типовые элементы ЭВМ. План: 1. Запись информации в регистр; 2. Передача информации от одного регистра в другой; 3. Сдвигающий регистр.

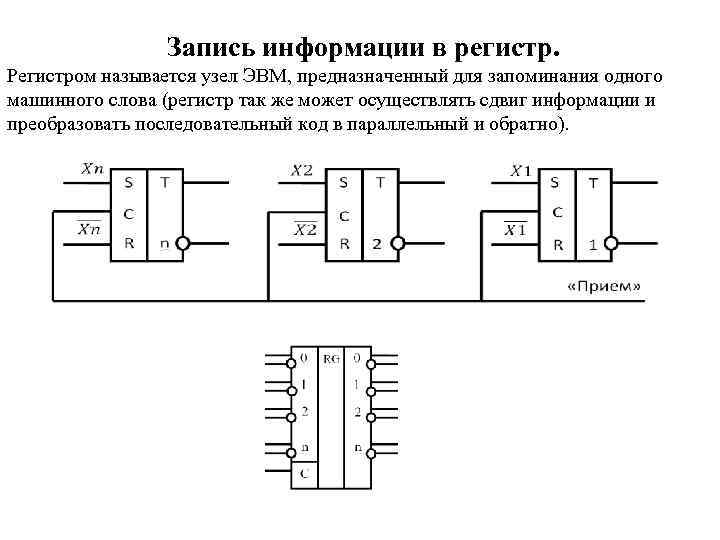

Запись информации в регистр. Регистром называется узел ЭВМ, предназначенный для запоминания одного машинного слова (регистр так же может осуществлять сдвиг информации и преобразовать последовательный код в параллельный и обратно).

Запись информации в регистр. Регистром называется узел ЭВМ, предназначенный для запоминания одного машинного слова (регистр так же может осуществлять сдвиг информации и преобразовать последовательный код в параллельный и обратно).

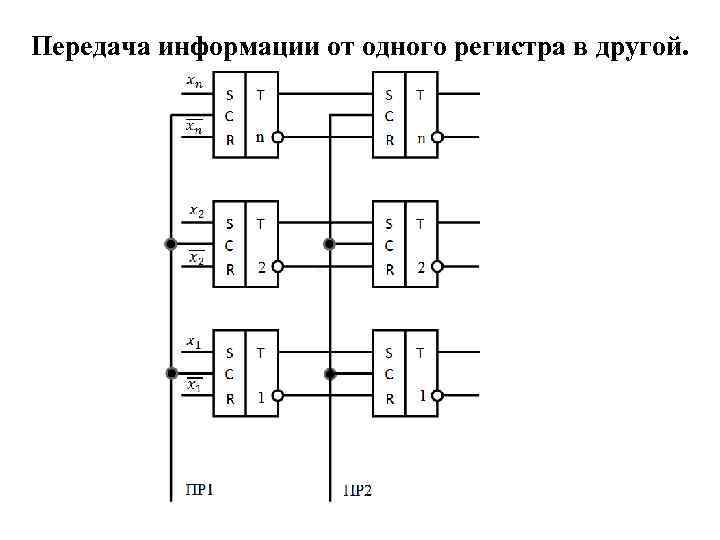

Передача информации от одного регистра в другой.

Передача информации от одного регистра в другой.

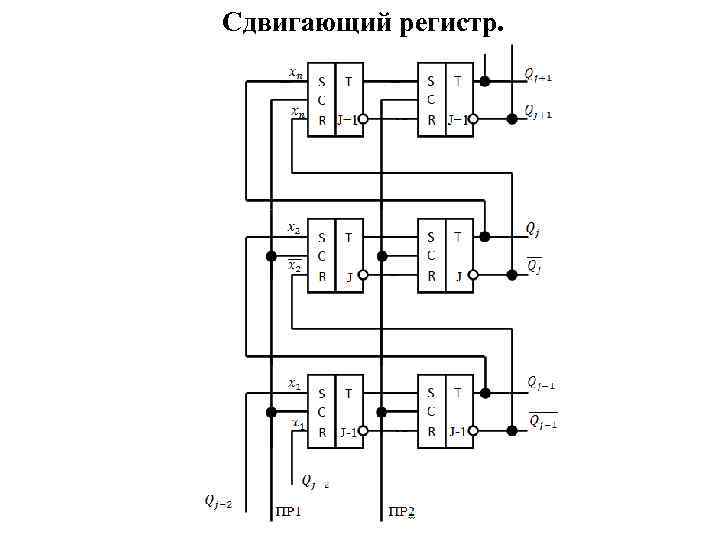

Сдвигающий регистр.

Сдвигающий регистр.

Дешифраторы. План: 1. Структурная схема дешифратора; 2. Каскадный дешифратор.

Дешифраторы. План: 1. Структурная схема дешифратора; 2. Каскадный дешифратор.

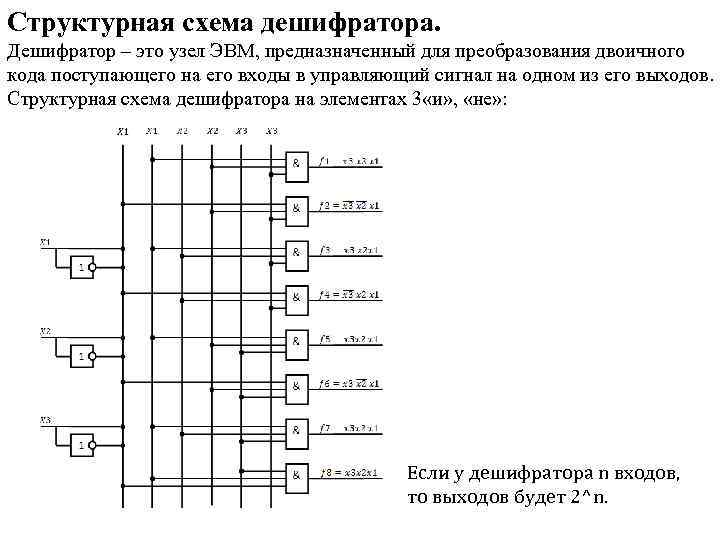

Структурная схема дешифратора. Дешифратор – это узел ЭВМ, предназначенный для преобразования двоичного кода поступающего на его входы в управляющий сигнал на одном из его выходов. Структурная схема дешифратора на элементах 3 «и» , «не» : Если у дешифратора n входов, то выходов будет 2^n.

Структурная схема дешифратора. Дешифратор – это узел ЭВМ, предназначенный для преобразования двоичного кода поступающего на его входы в управляющий сигнал на одном из его выходов. Структурная схема дешифратора на элементах 3 «и» , «не» : Если у дешифратора n входов, то выходов будет 2^n.

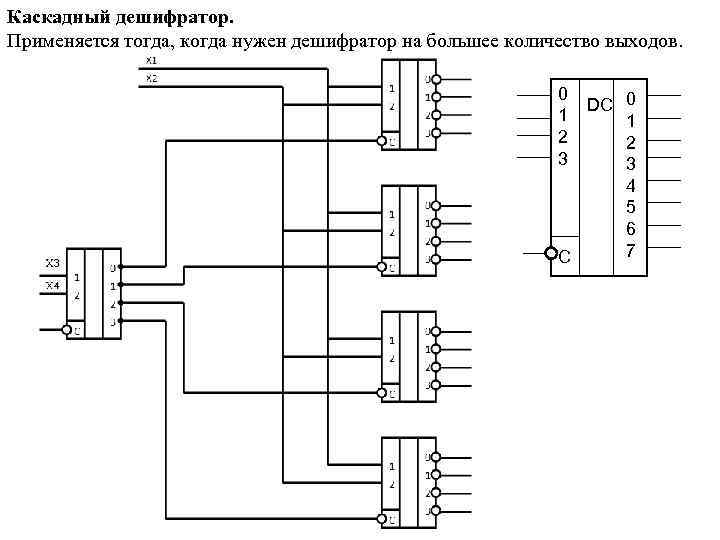

Каскадный дешифратор. Применяется тогда, когда нужен дешифратор на большее количество выходов. 0 1 2 3 DC 0 1 2 3 4 5 6 7 С

Каскадный дешифратор. Применяется тогда, когда нужен дешифратор на большее количество выходов. 0 1 2 3 DC 0 1 2 3 4 5 6 7 С

Счетчики. План: 1. Счетчик с последовательным переносом; 2. Счетчик с параллельным переносом; 3. Реверсивный счетчик.

Счетчики. План: 1. Счетчик с последовательным переносом; 2. Счетчик с параллельным переносом; 3. Реверсивный счетчик.

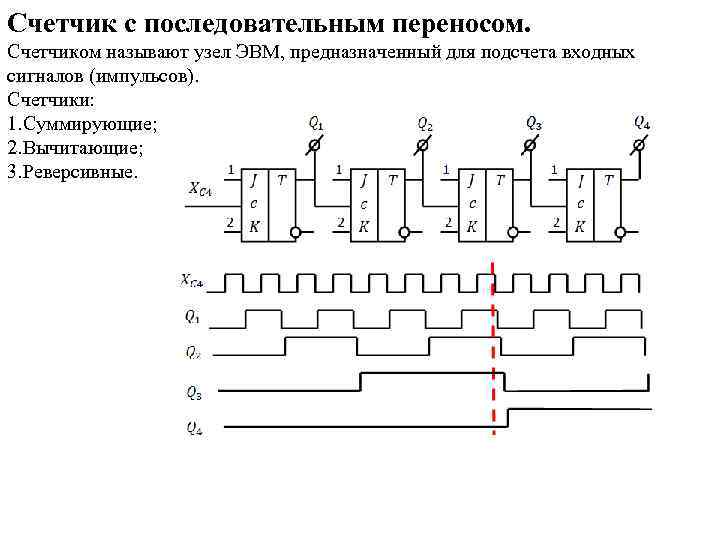

Счетчик с последовательным переносом. Счетчиком называют узел ЭВМ, предназначенный для подсчета входных сигналов (импульсов). Счетчики: 1. Суммирующие; 2. Вычитающие; 3. Реверсивные.

Счетчик с последовательным переносом. Счетчиком называют узел ЭВМ, предназначенный для подсчета входных сигналов (импульсов). Счетчики: 1. Суммирующие; 2. Вычитающие; 3. Реверсивные.

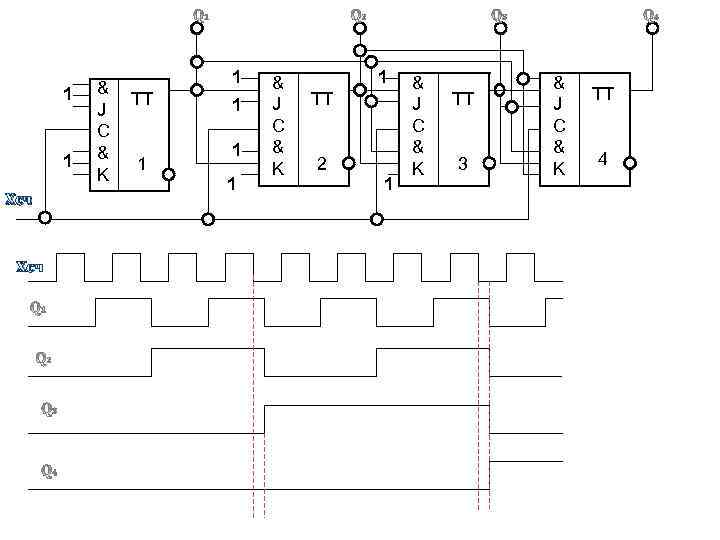

1 1 Хсч & J C & K 1 ТТ 1 1 & J C & K 1 ТТ 2 1 & J C & K ТТ 3 & J C & K ТТ 4

1 1 Хсч & J C & K 1 ТТ 1 1 & J C & K 1 ТТ 2 1 & J C & K ТТ 3 & J C & K ТТ 4

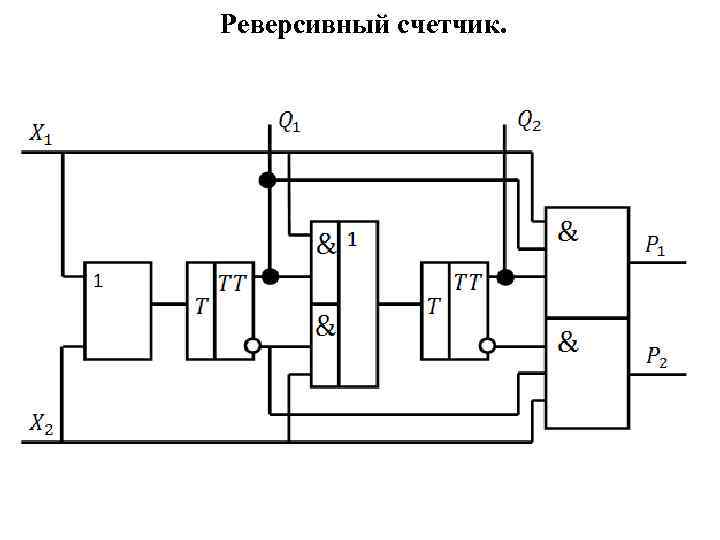

Реверсивный счетчик.

Реверсивный счетчик.

Сумматоры. План: 1. Одноразрядный сумматор; 2. Сумматор с поразрядным последовательным переносом.

Сумматоры. План: 1. Одноразрядный сумматор; 2. Сумматор с поразрядным последовательным переносом.

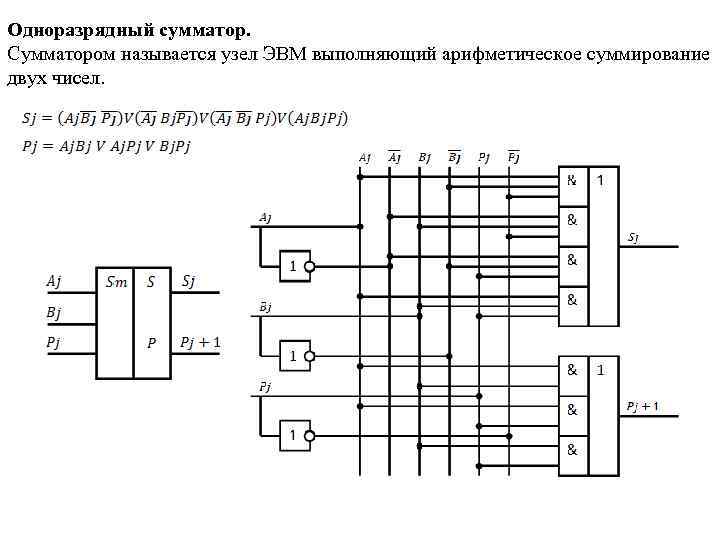

Одноразрядный сумматор. Сумматором называется узел ЭВМ выполняющий арифметическое суммирование двух чисел.

Одноразрядный сумматор. Сумматором называется узел ЭВМ выполняющий арифметическое суммирование двух чисел.

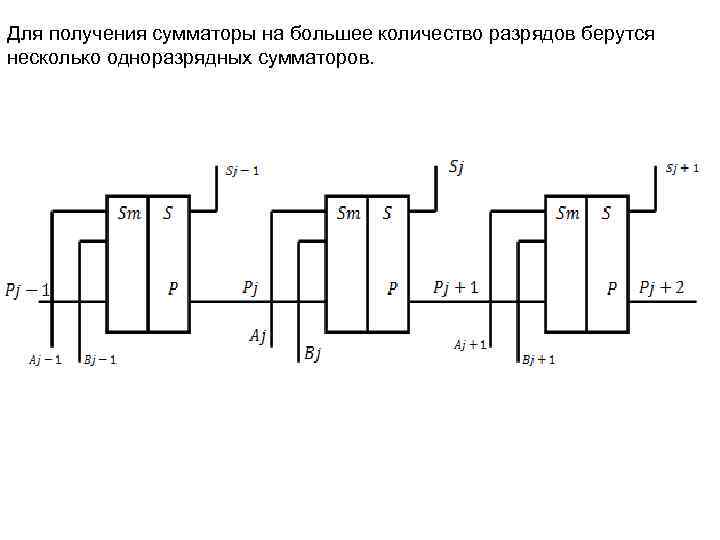

Для получения сумматоры на большее количество разрядов берутся несколько одноразрядных сумматоров.

Для получения сумматоры на большее количество разрядов берутся несколько одноразрядных сумматоров.

Мультиплексоры и демультиплексоры. План: 1. Мультиплексоры; 2. Демультиплексоры.

Мультиплексоры и демультиплексоры. План: 1. Мультиплексоры; 2. Демультиплексоры.

Мультиплексоры. Мультиплексором называется схема осуществляющая подачу сигнала с одного из информационных входов в одну выходную линию.

Мультиплексоры. Мультиплексором называется схема осуществляющая подачу сигнала с одного из информационных входов в одну выходную линию.

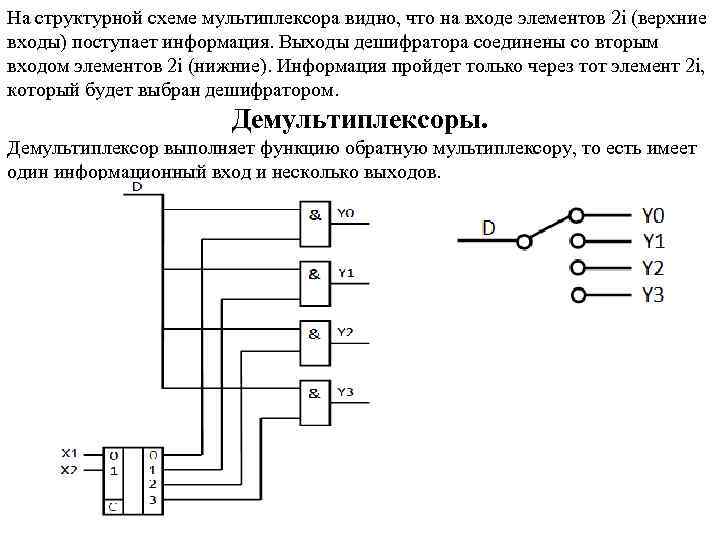

На структурной схеме мультиплексора видно, что на входе элементов 2 i (верхние входы) поступает информация. Выходы дешифратора соединены со вторым входом элементов 2 i (нижние). Информация пройдет только через тот элемент 2 i, который будет выбран дешифратором. Демультиплексоры. Демультиплексор выполняет функцию обратную мультиплексору, то есть имеет один информационный вход и несколько выходов.

На структурной схеме мультиплексора видно, что на входе элементов 2 i (верхние входы) поступает информация. Выходы дешифратора соединены со вторым входом элементов 2 i (нижние). Информация пройдет только через тот элемент 2 i, который будет выбран дешифратором. Демультиплексоры. Демультиплексор выполняет функцию обратную мультиплексору, то есть имеет один информационный вход и несколько выходов.

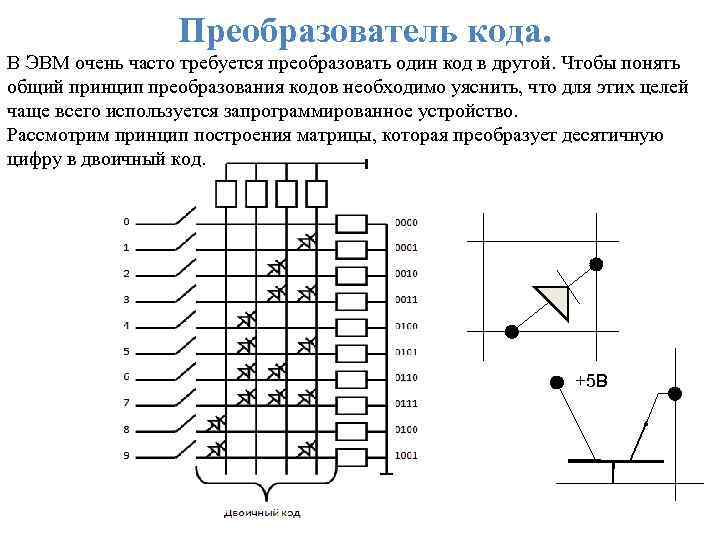

Преобразователь кода. В ЭВМ очень часто требуется преобразовать один код в другой. Чтобы понять общий принцип преобразования кодов необходимо уяснить, что для этих целей чаще всего используется запрограммированное устройство. Рассмотрим принцип построения матрицы, которая преобразует десятичную цифру в двоичный код. +5 В

Преобразователь кода. В ЭВМ очень часто требуется преобразовать один код в другой. Чтобы понять общий принцип преобразования кодов необходимо уяснить, что для этих целей чаще всего используется запрограммированное устройство. Рассмотрим принцип построения матрицы, которая преобразует десятичную цифру в двоичный код. +5 В

Узлы контроля. План: 1. Сумматор по модулю 2; 2. Контроль по методу «чет-нечет» ; 3. Узел контроля «по совпадению» .

Узлы контроля. План: 1. Сумматор по модулю 2; 2. Контроль по методу «чет-нечет» ; 3. Узел контроля «по совпадению» .

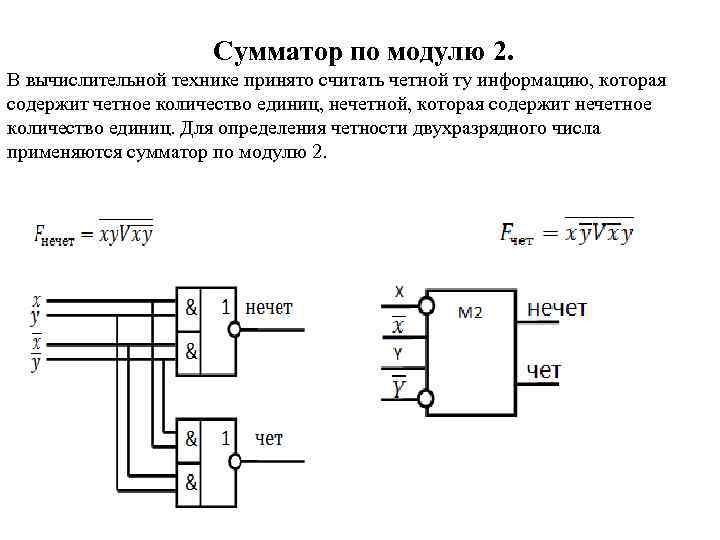

Сумматор по модулю 2. В вычислительной технике принято считать четной ту информацию, которая содержит четное количество единиц, нечетной, которая содержит нечетное количество единиц. Для определения четности двухразрядного числа применяются сумматор по модулю 2.

Сумматор по модулю 2. В вычислительной технике принято считать четной ту информацию, которая содержит четное количество единиц, нечетной, которая содержит нечетное количество единиц. Для определения четности двухразрядного числа применяются сумматор по модулю 2.

Контроль по методу «чет-нечет» .

Контроль по методу «чет-нечет» .

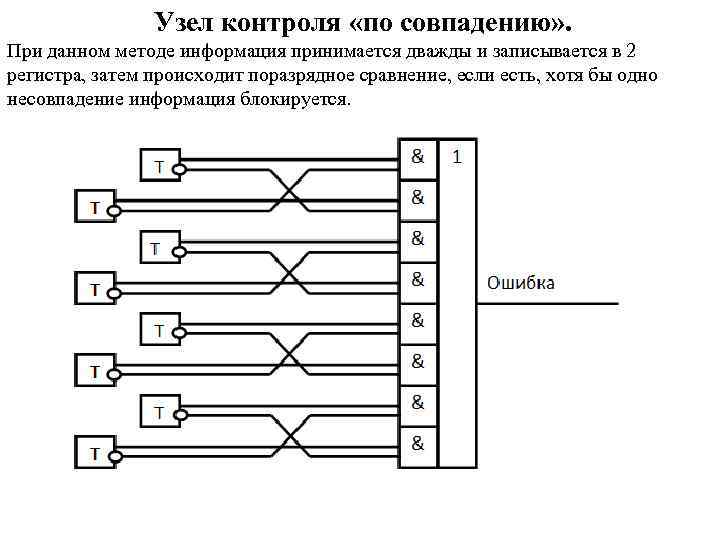

Узел контроля «по совпадению» . При данном методе информация принимается дважды и записывается в 2 регистра, затем происходит поразрядное сравнение, если есть, хотя бы одно несовпадение информация блокируется.

Узел контроля «по совпадению» . При данном методе информация принимается дважды и записывается в 2 регистра, затем происходит поразрядное сравнение, если есть, хотя бы одно несовпадение информация блокируется.

Память. План: 1. Основные характеристики памяти; 2. Классификация памяти; 3. Способы организации.

Память. План: 1. Основные характеристики памяти; 2. Классификация памяти; 3. Способы организации.

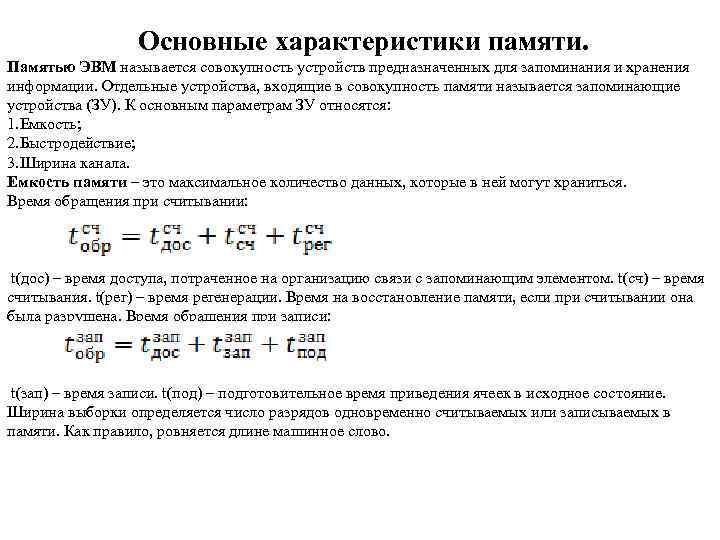

Основные характеристики памяти. Памятью ЭВМ называется совокупность устройств предназначенных для запоминания и хранения информации. Отдельные устройства, входящие в совокупность памяти называется запоминающие устройства (ЗУ). К основным параметрам ЗУ относятся: 1. Емкость; 2. Быстродействие; 3. Ширина канала. Емкость памяти – это максимальное количество данных, которые в ней могут храниться. Время обращения при считывании: t(дос) – время доступа, потраченное на организацию связи с запоминающим элементом. t(сч) – время считывания. t(рег) – время регенерации. Время на восстановление памяти, если при считывании она была разрушена. Время обращения при записи: t(зап) – время записи. t(под) – подготовительное время приведения ячеек в исходное состояние. Ширина выборки определяется число разрядов одновременно считываемых или записываемых в памяти. Как правило, ровняется длине машинное слово.

Основные характеристики памяти. Памятью ЭВМ называется совокупность устройств предназначенных для запоминания и хранения информации. Отдельные устройства, входящие в совокупность памяти называется запоминающие устройства (ЗУ). К основным параметрам ЗУ относятся: 1. Емкость; 2. Быстродействие; 3. Ширина канала. Емкость памяти – это максимальное количество данных, которые в ней могут храниться. Время обращения при считывании: t(дос) – время доступа, потраченное на организацию связи с запоминающим элементом. t(сч) – время считывания. t(рег) – время регенерации. Время на восстановление памяти, если при считывании она была разрушена. Время обращения при записи: t(зап) – время записи. t(под) – подготовительное время приведения ячеек в исходное состояние. Ширина выборки определяется число разрядов одновременно считываемых или записываемых в памяти. Как правило, ровняется длине машинное слово.

Классификация памяти. ЗУ с произвольным доступом – время доступа не зависит от времени расположения участка памяти (ОП). ЗУ с циклическим доступом – возможность обращения к некоторым участкам носителя циклически повторяется (магнитный диск). ЗУ с последовательным доступом – производится последовательный просмотр участков памяти, пока нужный участок не займет нужное положение (магнитная лента).

Классификация памяти. ЗУ с произвольным доступом – время доступа не зависит от времени расположения участка памяти (ОП). ЗУ с циклическим доступом – возможность обращения к некоторым участкам носителя циклически повторяется (магнитный диск). ЗУ с последовательным доступом – производится последовательный просмотр участков памяти, пока нужный участок не займет нужное положение (магнитная лента).

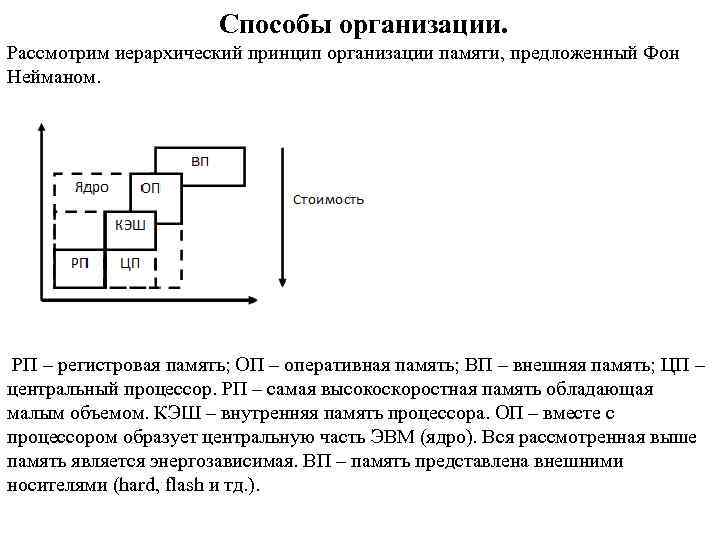

Способы организации. Рассмотрим иерархический принцип организации памяти, предложенный Фон Нейманом. РП – регистровая память; ОП – оперативная память; ВП – внешняя память; ЦП – центральный процессор. РП – самая высокоскоростная память обладающая малым объемом. КЭШ – внутренняя память процессора. ОП – вместе с процессором образует центральную часть ЭВМ (ядро). Вся рассмотренная выше память является энергозависимая. ВП – память представлена внешними носителями (hard, flash и тд. ).

Способы организации. Рассмотрим иерархический принцип организации памяти, предложенный Фон Нейманом. РП – регистровая память; ОП – оперативная память; ВП – внешняя память; ЦП – центральный процессор. РП – самая высокоскоростная память обладающая малым объемом. КЭШ – внутренняя память процессора. ОП – вместе с процессором образует центральную часть ЭВМ (ядро). Вся рассмотренная выше память является энергозависимая. ВП – память представлена внешними носителями (hard, flash и тд. ).

Оперативные запоминающие устройства (ОЗУ). План: 1. Структура ЗУ типа 2 D; 2. Структура ЗУ типа 3 D; 3. ЗУ с мультиплексарной передачей адресов

Оперативные запоминающие устройства (ОЗУ). План: 1. Структура ЗУ типа 2 D; 2. Структура ЗУ типа 3 D; 3. ЗУ с мультиплексарной передачей адресов

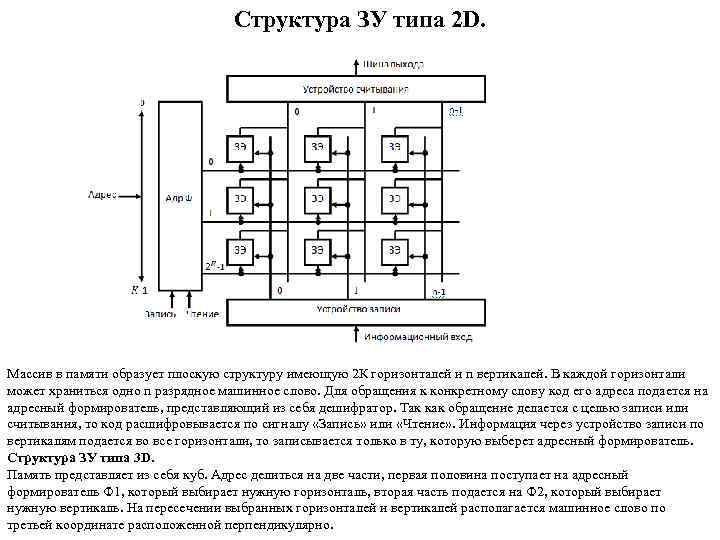

Структура ЗУ типа 2 D. Массив в памяти образует плоскую структуру имеющую 2 К горизонталей и n вертикалей. В каждой горизонтали может храниться одно n разрядное машинное слово. Для обращения к конкретному слову код его адреса подается на адресный формирователь, представляющий из себя дешифратор. Так как обращение делается с целью записи или считывания, то код расшифровывается по сигналу «Запись» или «Чтение» . Информация через устройство записи по вертикалям подается во все горизонтали, то записывается только в ту, которую выберет адресный формирователь. Структура ЗУ типа 3 D. Память представляет из себя куб. Адрес делиться на две части, первая половина поступает на адресный формирователь Ф 1, который выбирает нужную горизонталь, вторая часть подается на Ф 2, который выбирает нужную вертикаль. На пересечении выбранных горизонталей и вертикалей располагается машинное слово по третьей координате расположенной перпендикулярно.

Структура ЗУ типа 2 D. Массив в памяти образует плоскую структуру имеющую 2 К горизонталей и n вертикалей. В каждой горизонтали может храниться одно n разрядное машинное слово. Для обращения к конкретному слову код его адреса подается на адресный формирователь, представляющий из себя дешифратор. Так как обращение делается с целью записи или считывания, то код расшифровывается по сигналу «Запись» или «Чтение» . Информация через устройство записи по вертикалям подается во все горизонтали, то записывается только в ту, которую выберет адресный формирователь. Структура ЗУ типа 3 D. Память представляет из себя куб. Адрес делиться на две части, первая половина поступает на адресный формирователь Ф 1, который выбирает нужную горизонталь, вторая часть подается на Ф 2, который выбирает нужную вертикаль. На пересечении выбранных горизонталей и вертикалей располагается машинное слово по третьей координате расположенной перпендикулярно.

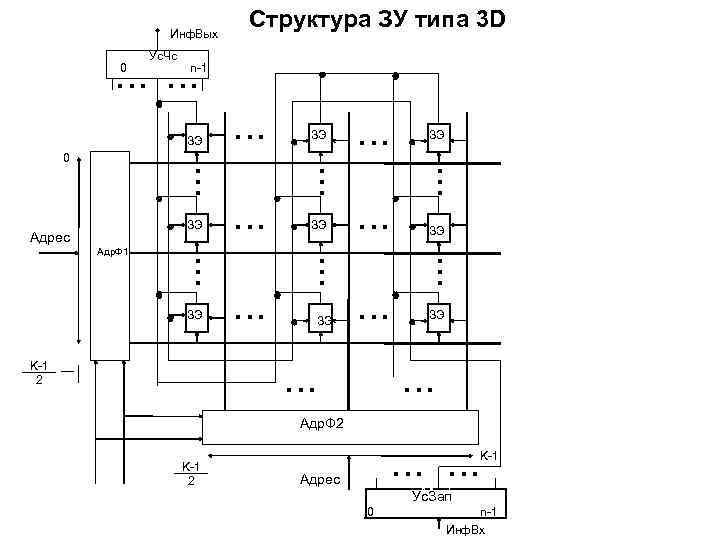

Инф. Вых Ус. Чс Структура ЗУ типа 3 D … … 0 n-1 ЗЭ … ЗЭ ЗЭ … . . . 0 Адрес Адр. Ф 1 . . . K-1 2 . . . ЗЭ … ЗЭ . . . … ЗЭ … . . . … Адр. Ф 2 А K-1 2 … … K-1 Адрес M, . / Ус. Зап 0 n-1 Инф. Вх

Инф. Вых Ус. Чс Структура ЗУ типа 3 D … … 0 n-1 ЗЭ … ЗЭ ЗЭ … . . . 0 Адрес Адр. Ф 1 . . . K-1 2 . . . ЗЭ … ЗЭ . . . … ЗЭ … . . . … Адр. Ф 2 А K-1 2 … … K-1 Адрес M, . / Ус. Зап 0 n-1 Инф. Вх

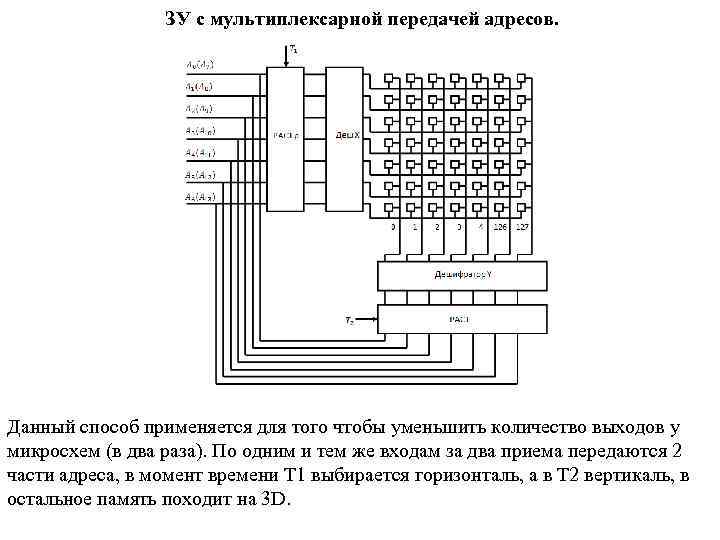

ЗУ с мультиплексарной передачей адресов. Данный способ применяется для того чтобы уменьшить количество выходов у микросхем (в два раза). По одним и тем же входам за два приема передаются 2 части адреса, в момент времени Т 1 выбирается горизонталь, а в T 2 вертикаль, в остальное память походит на 3 D.

ЗУ с мультиплексарной передачей адресов. Данный способ применяется для того чтобы уменьшить количество выходов у микросхем (в два раза). По одним и тем же входам за два приема передаются 2 части адреса, в момент времени Т 1 выбирается горизонталь, а в T 2 вертикаль, в остальное память походит на 3 D.

Постоянные запоминающие устройства(ПЗУ). План: 1. ПЗУ с плавкой выжигаемой перемычкой; 2. ПЗУ с пробивным pn – переходом; 3. Перепрограммирование ПЗУ.

Постоянные запоминающие устройства(ПЗУ). План: 1. ПЗУ с плавкой выжигаемой перемычкой; 2. ПЗУ с пробивным pn – переходом; 3. Перепрограммирование ПЗУ.

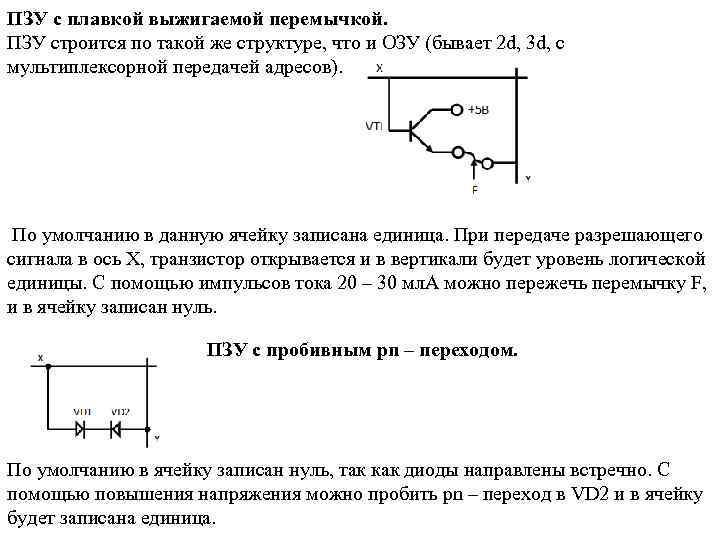

ПЗУ с плавкой выжигаемой перемычкой. ПЗУ строится по такой же структуре, что и ОЗУ (бывает 2 d, 3 d, с мультиплексорной передачей адресов). По умолчанию в данную ячейку записана единица. При передаче разрешающего сигнала в ось X, транзистор открывается и в вертикали будет уровень логической единицы. С помощью импульсов тока 20 – 30 мл. А можно пережечь перемычку F, и в ячейку записан нуль. ПЗУ с пробивным pn – переходом. По умолчанию в ячейку записан нуль, так как диоды направлены встречно. С помощью повышения напряжения можно пробить pn – переход в VD 2 и в ячейку будет записана единица.

ПЗУ с плавкой выжигаемой перемычкой. ПЗУ строится по такой же структуре, что и ОЗУ (бывает 2 d, 3 d, с мультиплексорной передачей адресов). По умолчанию в данную ячейку записана единица. При передаче разрешающего сигнала в ось X, транзистор открывается и в вертикали будет уровень логической единицы. С помощью импульсов тока 20 – 30 мл. А можно пережечь перемычку F, и в ячейку записан нуль. ПЗУ с пробивным pn – переходом. По умолчанию в ячейку записан нуль, так как диоды направлены встречно. С помощью повышения напряжения можно пробить pn – переход в VD 2 и в ячейку будет записана единица.

Перепрограммирование ПЗУ. По умолчанию записана единица. При отсутствии потенциала на селекторном затворе (СЗ) между стоком и истоком подается высокое напряжение и плавающий затвор становиться заряженным отрицательно. Под действием ультрафиолетового света происходит удаление отрицательного заряда с плавающего затвора и в ячейку вместо нуля записывается единица.

Перепрограммирование ПЗУ. По умолчанию записана единица. При отсутствии потенциала на селекторном затворе (СЗ) между стоком и истоком подается высокое напряжение и плавающий затвор становиться заряженным отрицательно. Под действием ультрафиолетового света происходит удаление отрицательного заряда с плавающего затвора и в ячейку вместо нуля записывается единица.

Внешние запоминающие устройства (ВЗУ). План: 1. Устройство магнитной головки; 2. Запись информации; 3. Считывание информации; 4. Стирание информации; 5. Кодирование команд.

Внешние запоминающие устройства (ВЗУ). План: 1. Устройство магнитной головки; 2. Запись информации; 3. Считывание информации; 4. Стирание информации; 5. Кодирование команд.

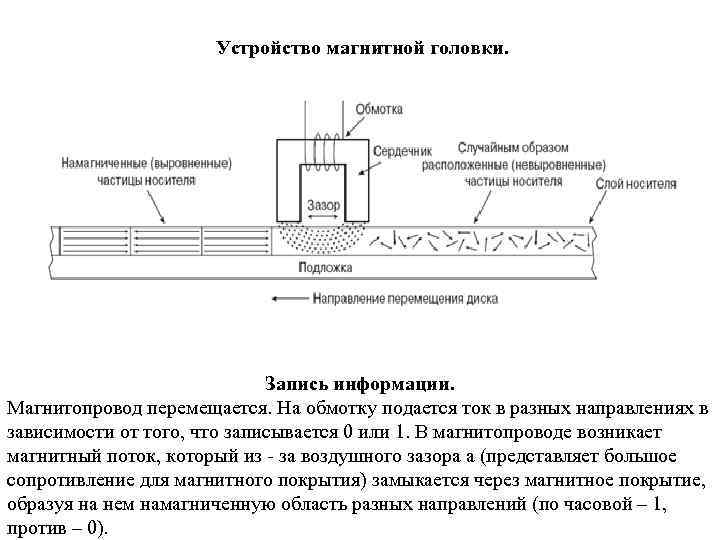

Устройство магнитной головки. Запись информации. Магнитопровод перемещается. На обмотку подается ток в разных направлениях в зависимости от того, что записывается 0 или 1. В магнитопроводе возникает магнитный поток, который из - за воздушного зазора a (представляет большое сопротивление для магнитного покрытия) замыкается через магнитное покрытие, образуя на нем намагниченную область разных направлений (по часовой – 1, против – 0).

Устройство магнитной головки. Запись информации. Магнитопровод перемещается. На обмотку подается ток в разных направлениях в зависимости от того, что записывается 0 или 1. В магнитопроводе возникает магнитный поток, который из - за воздушного зазора a (представляет большое сопротивление для магнитного покрытия) замыкается через магнитное покрытие, образуя на нем намагниченную область разных направлений (по часовой – 1, против – 0).

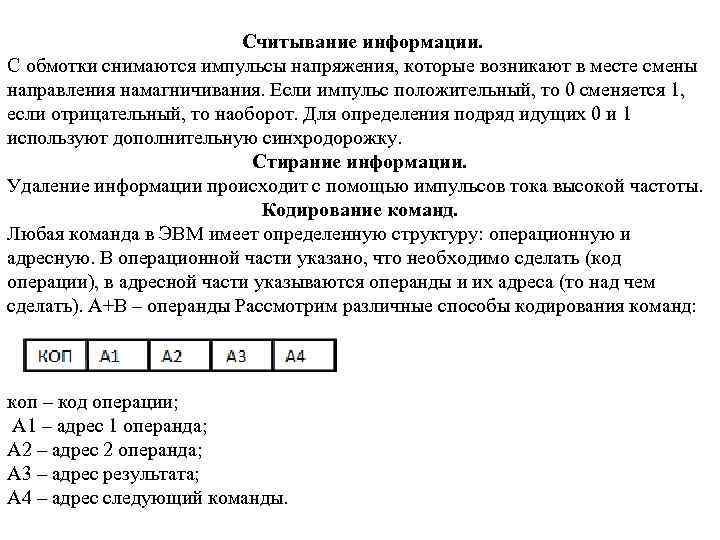

Считывание информации. С обмотки снимаются импульсы напряжения, которые возникают в месте смены направления намагничивания. Если импульс положительный, то 0 сменяется 1, если отрицательный, то наоборот. Для определения подряд идущих 0 и 1 используют дополнительную синхродорожку. Стирание информации. Удаление информации происходит с помощью импульсов тока высокой частоты. Кодирование команд. Любая команда в ЭВМ имеет определенную структуру: операционную и адресную. В операционной части указано, что необходимо сделать (код операции), в адресной части указываются операнды и их адреса (то над чем сделать). A+B – операнды Рассмотрим различные способы кодирования команд: коп – код операции; A 1 – адрес 1 операнда; A 2 – адрес 2 операнда; A 3 – адрес результата; A 4 – адрес следующий команды.

Считывание информации. С обмотки снимаются импульсы напряжения, которые возникают в месте смены направления намагничивания. Если импульс положительный, то 0 сменяется 1, если отрицательный, то наоборот. Для определения подряд идущих 0 и 1 используют дополнительную синхродорожку. Стирание информации. Удаление информации происходит с помощью импульсов тока высокой частоты. Кодирование команд. Любая команда в ЭВМ имеет определенную структуру: операционную и адресную. В операционной части указано, что необходимо сделать (код операции), в адресной части указываются операнды и их адреса (то над чем сделать). A+B – операнды Рассмотрим различные способы кодирования команд: коп – код операции; A 1 – адрес 1 операнда; A 2 – адрес 2 операнда; A 3 – адрес результата; A 4 – адрес следующий команды.

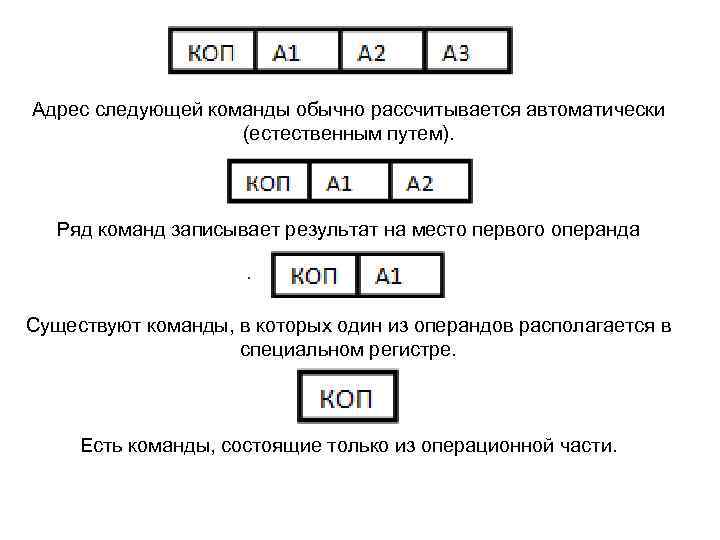

Адрес следующей команды обычно рассчитывается автоматически (естественным путем). Ряд команд записывает результат на место первого операнда Существуют команды, в которых один из операндов располагается в специальном регистре. Есть команды, состоящие только из операционной части.

Адрес следующей команды обычно рассчитывается автоматически (естественным путем). Ряд команд записывает результат на место первого операнда Существуют команды, в которых один из операндов располагается в специальном регистре. Есть команды, состоящие только из операционной части.

Способы адресации. План: 1. Непосредственная адресация; 2. Прямая адресация; 3. Относительная адресация; 4. Косвенная адресация; 5. Стековая адресация.

Способы адресации. План: 1. Непосредственная адресация; 2. Прямая адресация; 3. Относительная адресация; 4. Косвенная адресация; 5. Стековая адресация.

Непосредственная адресация. В адресной части содержится сам операнд, а не его адрес. Прямая адресация. В адресной части содержится адрес ячейки памяти, в которой находится сам операнд. Относительная адресация. Связана с операндом адреса с помощью расчета (адресации с базированием). Косвенная адресация. В ячейке хранится адрес, по которому хранится операнд. Стековая адресация. Работает по принципу «первый пришел последний ушел» .

Непосредственная адресация. В адресной части содержится сам операнд, а не его адрес. Прямая адресация. В адресной части содержится адрес ячейки памяти, в которой находится сам операнд. Относительная адресация. Связана с операндом адреса с помощью расчета (адресации с базированием). Косвенная адресация. В ячейке хранится адрес, по которому хранится операнд. Стековая адресация. Работает по принципу «первый пришел последний ушел» .

Наименование и структура процессора. План: 1. Структура процессора; 2. Алгоритм работы.

Наименование и структура процессора. План: 1. Структура процессора; 2. Алгоритм работы.

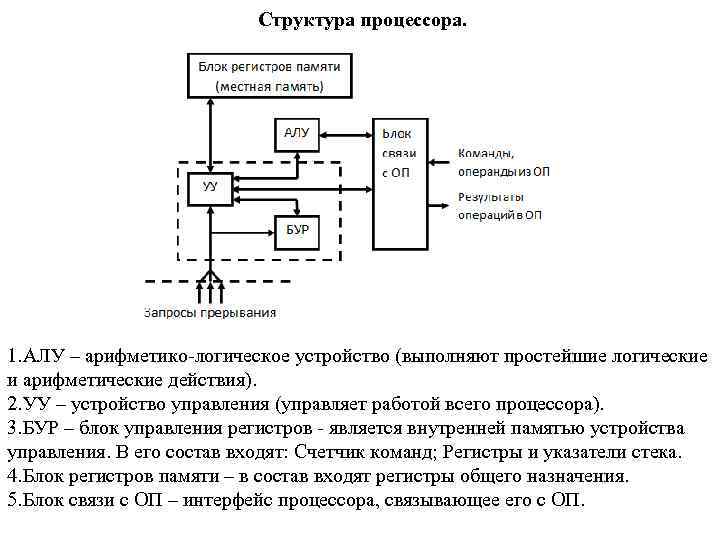

Структура процессора. 1. АЛУ – арифметико-логическое устройство (выполняют простейшие логические и арифметические действия). 2. УУ – устройство управления (управляет работой всего процессора). 3. БУР – блок управления регистров - является внутренней памятью устройства управления. В его состав входят: Счетчик команд; Регистры и указатели стека. 4. Блок регистров памяти – в состав входят регистры общего назначения. 5. Блок связи с ОП – интерфейс процессора, связывающее его с ОП.

Структура процессора. 1. АЛУ – арифметико-логическое устройство (выполняют простейшие логические и арифметические действия). 2. УУ – устройство управления (управляет работой всего процессора). 3. БУР – блок управления регистров - является внутренней памятью устройства управления. В его состав входят: Счетчик команд; Регистры и указатели стека. 4. Блок регистров памяти – в состав входят регистры общего назначения. 5. Блок связи с ОП – интерфейс процессора, связывающее его с ОП.

Алгоритм работы. 1. Процессор загружает из памяти новую команду. 2. Процессор производит расчет адреса следующей команды (к текущему адресу прибавляется длина выборной команды). 3. Производиться декодирование команды. 4. Рассчитывается адрес операндов. 5. Производиться загрузка операндов из ОП в местную. 6. Выполняются команды. 7. Результат отправляется в ОП. 8. Алгоритм повторяется заново.

Алгоритм работы. 1. Процессор загружает из памяти новую команду. 2. Процессор производит расчет адреса следующей команды (к текущему адресу прибавляется длина выборной команды). 3. Производиться декодирование команды. 4. Рассчитывается адрес операндов. 5. Производиться загрузка операндов из ОП в местную. 6. Выполняются команды. 7. Результат отправляется в ОП. 8. Алгоритм повторяется заново.

Регистровая структура микромроцессора. План: 1. Регистры общего назначения; 2. Сегментные регистры; 3. Регистры флагов и указатели команд.

Регистровая структура микромроцессора. План: 1. Регистры общего назначения; 2. Сегментные регистры; 3. Регистры флагов и указатели команд.

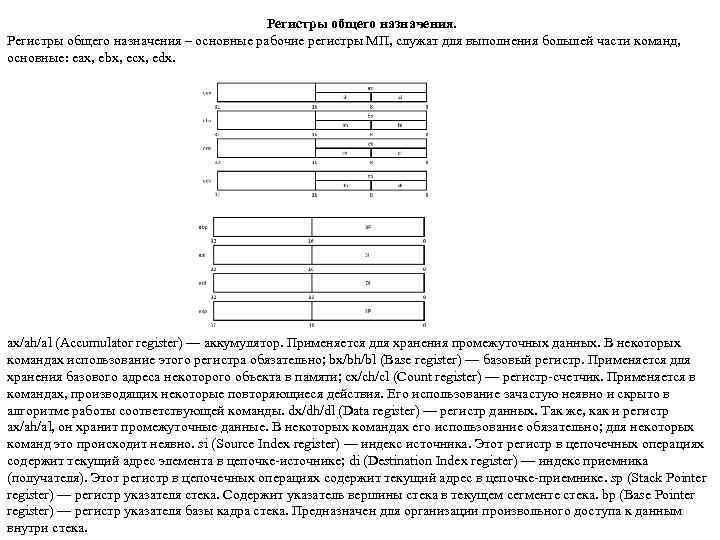

Регистры общего назначения – основные рабочие регистры МП, служат для выполнения большей части команд, основные: eax, ebx, ecx, edx. ax/ah/al (Accumulator register) — аккумулятор. Применяется для хранения промежуточных данных. В некоторых командах использование этого регистра обязательно; bx/bh/bl (Base register) — базовый регистр. Применяется для хранения базового адреса некоторого объекта в памяти; cx/ch/cl (Count register) — регистр-счетчик. Применяется в командах, производящих некоторые повторяющиеся действия. Его использование зачастую неявно и скрыто в алгоритме работы соответствующей команды. dx/dh/dl (Data register) — регистр данных. Так же, как и регистр ax/ah/al, он хранит промежуточные данные. В некоторых командах его использование обязательно; для некоторых команд это происходит неявно. si (Source Index register) — индекс источника. Этот регистр в цепочечных операциях содержит текущий адрес элемента в цепочке-источнике; di (Destination Index register) — индекс приемника (получателя). Этот регистр в цепочечных операциях содержит текущий адрес в цепочке-приемнике. sp (Stack Pointer register) — регистр указателя стека. Содержит указатель вершины стека в текущем сегменте стека. bp (Base Pointer register) — регистр указателя базы кадра стека. Предназначен для организации произвольного доступа к данным внутри стека.

Регистры общего назначения – основные рабочие регистры МП, служат для выполнения большей части команд, основные: eax, ebx, ecx, edx. ax/ah/al (Accumulator register) — аккумулятор. Применяется для хранения промежуточных данных. В некоторых командах использование этого регистра обязательно; bx/bh/bl (Base register) — базовый регистр. Применяется для хранения базового адреса некоторого объекта в памяти; cx/ch/cl (Count register) — регистр-счетчик. Применяется в командах, производящих некоторые повторяющиеся действия. Его использование зачастую неявно и скрыто в алгоритме работы соответствующей команды. dx/dh/dl (Data register) — регистр данных. Так же, как и регистр ax/ah/al, он хранит промежуточные данные. В некоторых командах его использование обязательно; для некоторых команд это происходит неявно. si (Source Index register) — индекс источника. Этот регистр в цепочечных операциях содержит текущий адрес элемента в цепочке-источнике; di (Destination Index register) — индекс приемника (получателя). Этот регистр в цепочечных операциях содержит текущий адрес в цепочке-приемнике. sp (Stack Pointer register) — регистр указателя стека. Содержит указатель вершины стека в текущем сегменте стека. bp (Base Pointer register) — регистр указателя базы кадра стека. Предназначен для организации произвольного доступа к данным внутри стека.

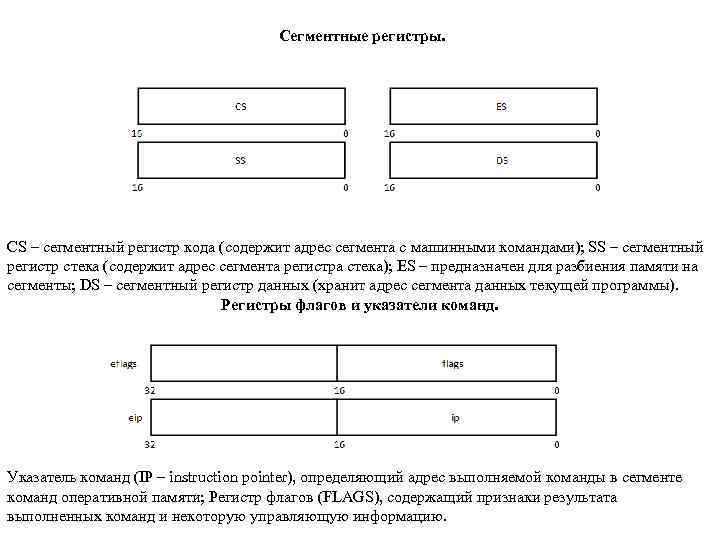

Сегментные регистры. CS – сегментный регистр кода (содержит адрес сегмента с машинными командами); SS – сегментный регистр стека (содержит адрес сегмента регистра стека); ES – предназначен для разбиения памяти на сегменты; DS – сегментный регистр данных (хранит адрес сегмента данных текущей программы). Регистры флагов и указатели команд. Указатель команд (IP – instruction pointer), определяющий адрес выполняемой команды в сегменте команд оперативной памяти; Регистр флагов (FLAGS), содержащий признаки результата выполненных команд и некоторую управляющую информацию.

Сегментные регистры. CS – сегментный регистр кода (содержит адрес сегмента с машинными командами); SS – сегментный регистр стека (содержит адрес сегмента регистра стека); ES – предназначен для разбиения памяти на сегменты; DS – сегментный регистр данных (хранит адрес сегмента данных текущей программы). Регистры флагов и указатели команд. Указатель команд (IP – instruction pointer), определяющий адрес выполняемой команды в сегменте команд оперативной памяти; Регистр флагов (FLAGS), содержащий признаки результата выполненных команд и некоторую управляющую информацию.

Устройство управления(УУ). План: 1. УУ с микропрограммным уровнем управления; 2. УУ на жесткой логике.

Устройство управления(УУ). План: 1. УУ с микропрограммным уровнем управления; 2. УУ на жесткой логике.

УУ с микропрограммным уровнем управления. Процессор выполняет команды, из которых состоит программа. Каждая команда выполняется по микропрограмме. Микропрограмма состоит из микрокоманд, выполняя которые процессор выполнят команду. Ко. П – код операции; Рг К – регистр команд; Рг АМк – регистр адреса микрокоманд; Сх ФАМк – схема формирования адреса микрокоманды ; ШЗг УП – шина загрузки управляющей памяти; УП – управляющая память; СС – синхросигнал; Рг Мк – регистр микрокоманд.

УУ с микропрограммным уровнем управления. Процессор выполняет команды, из которых состоит программа. Каждая команда выполняется по микропрограмме. Микропрограмма состоит из микрокоманд, выполняя которые процессор выполнят команду. Ко. П – код операции; Рг К – регистр команд; Рг АМк – регистр адреса микрокоманд; Сх ФАМк – схема формирования адреса микрокоманды ; ШЗг УП – шина загрузки управляющей памяти; УП – управляющая память; СС – синхросигнал; Рг Мк – регистр микрокоманд.

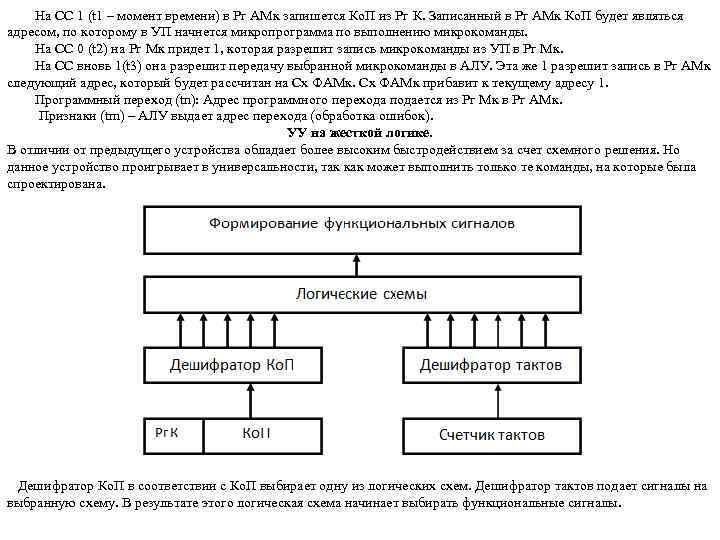

На СС 1 (t 1 – момент времени) в Рг АМк запишется Ко. П из Рг К. Записанный в Рг АМк Ко. П будет являться адресом, по которому в УП начнется микропрограмма по выполнению микрокоманды. На СС 0 (t 2) на Рг Мк придет 1, которая разрешит запись микрокоманды из УП в Рг Мк. На СС вновь 1(t 3) она разрешит передачу выбранной микрокоманды в АЛУ. Эта же 1 разрешит запись в Рг АМк следующий адрес, который будет рассчитан на Сх ФАМк прибавит к текущему адресу 1. Программный переход (tn): Адрес программного перехода подается из Рг Мк в Рг АМк. Признаки (tm) – АЛУ выдает адрес перехода (обработка ошибок). УУ на жесткой логике. В отличии от предыдущего устройства обладает более высоким быстродействием за счет схемного решения. Но данное устройство проигрывает в универсальности, так как может выполнить только те команды, на которые была спроектирована. Дешифратор Ко. П в соответствии с Ко. П выбирает одну из логических схем. Дешифратор тактов подает сигналы на выбранную схему. В результате этого логическая схема начинает выбирать функциональные сигналы.

На СС 1 (t 1 – момент времени) в Рг АМк запишется Ко. П из Рг К. Записанный в Рг АМк Ко. П будет являться адресом, по которому в УП начнется микропрограмма по выполнению микрокоманды. На СС 0 (t 2) на Рг Мк придет 1, которая разрешит запись микрокоманды из УП в Рг Мк. На СС вновь 1(t 3) она разрешит передачу выбранной микрокоманды в АЛУ. Эта же 1 разрешит запись в Рг АМк следующий адрес, который будет рассчитан на Сх ФАМк прибавит к текущему адресу 1. Программный переход (tn): Адрес программного перехода подается из Рг Мк в Рг АМк. Признаки (tm) – АЛУ выдает адрес перехода (обработка ошибок). УУ на жесткой логике. В отличии от предыдущего устройства обладает более высоким быстродействием за счет схемного решения. Но данное устройство проигрывает в универсальности, так как может выполнить только те команды, на которые была спроектирована. Дешифратор Ко. П в соответствии с Ко. П выбирает одну из логических схем. Дешифратор тактов подает сигналы на выбранную схему. В результате этого логическая схема начинает выбирать функциональные сигналы.

Арифметико-логические устройства(АЛУ). План: 1. Схема АЛУ комбинационного типа; 2. АЛУ с магистральной структурой; 3. Схема АЛУ на основах блоков памяти.

Арифметико-логические устройства(АЛУ). План: 1. Схема АЛУ комбинационного типа; 2. АЛУ с магистральной структурой; 3. Схема АЛУ на основах блоков памяти.

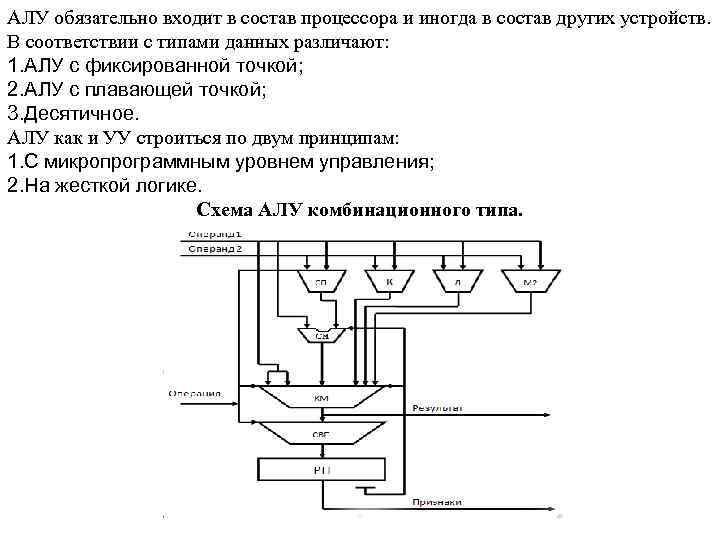

АЛУ обязательно входит в состав процессора и иногда в состав других устройств. В соответствии с типами данных различают: 1. АЛУ с фиксированной точкой; 2. АЛУ с плавающей точкой; 3. Десятичное. АЛУ как и УУ строиться по двум принципам: 1. С микропрограммным уровнем управления; 2. На жесткой логике. Схема АЛУ комбинационного типа.

АЛУ обязательно входит в состав процессора и иногда в состав других устройств. В соответствии с типами данных различают: 1. АЛУ с фиксированной точкой; 2. АЛУ с плавающей точкой; 3. Десятичное. АЛУ как и УУ строиться по двум принципам: 1. С микропрограммным уровнем управления; 2. На жесткой логике. Схема АЛУ комбинационного типа.

Рассмотрим АЛУ комбинационного типа, построенное на жесткой логике: 1. СП – преобразователь операнда в дополнительный код; 2. К – схема конъюнкции; 3. Д – схема дизъюнкции; 4. М 2 – сумматор по модулю 2; 5. СМ – сумматор; 6. КМ – коммутатор; 7. СВП – схема выработки признаков; 8. РП – регистр признаков. Операнды подаются сразу на все вычислительные блоки (СП, К, Д, М 2, СМ) с выходов которых готовые результаты поступают на коммутатор. В соответствии с кодом операции коммутатор выбирает готовый результат. Если готового результата нет, то в работу включается СВП и РП и расчет продолжиться до тех пор, пока не получиться нужный результат. Данное АЛУ работает быстро, так как имеет сразу несколько готовых результатов, но является дорогостоящим из-за сложности и избыточностью элементов схем. АЛУ с магистральной структурой.

Рассмотрим АЛУ комбинационного типа, построенное на жесткой логике: 1. СП – преобразователь операнда в дополнительный код; 2. К – схема конъюнкции; 3. Д – схема дизъюнкции; 4. М 2 – сумматор по модулю 2; 5. СМ – сумматор; 6. КМ – коммутатор; 7. СВП – схема выработки признаков; 8. РП – регистр признаков. Операнды подаются сразу на все вычислительные блоки (СП, К, Д, М 2, СМ) с выходов которых готовые результаты поступают на коммутатор. В соответствии с кодом операции коммутатор выбирает готовый результат. Если готового результата нет, то в работу включается СВП и РП и расчет продолжиться до тех пор, пока не получиться нужный результат. Данное АЛУ работает быстро, так как имеет сразу несколько готовых результатов, но является дорогостоящим из-за сложности и избыточностью элементов схем. АЛУ с магистральной структурой.

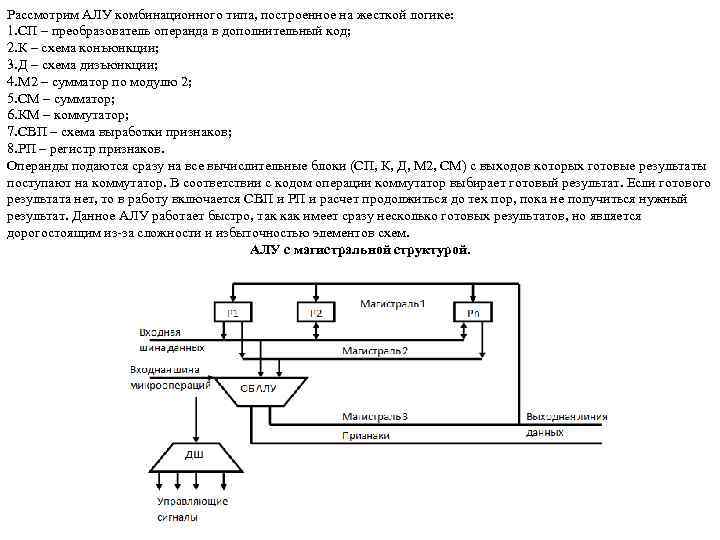

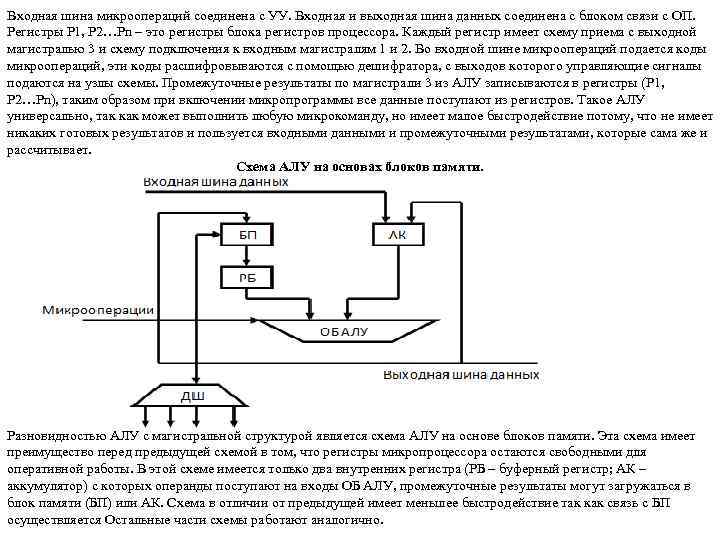

Входная шина микроопераций соединена с УУ. Входная и выходная шина данных соединена с блоком связи с ОП. Регистры Р 1, Р 2…Рn – это регистры блока регистров процессора. Каждый регистр имеет схему приема с выходной магистралью 3 и схему подключения к входным магистралям 1 и 2. Во входной шине микроопераций подается коды микроопераций, эти коды расшифровываются с помощью дешифратора, с выходов которого управляющие сигналы подаются на узлы схемы. Промежуточные результаты по магистрали 3 из АЛУ записываются в регистры (Р 1, Р 2…Рn), таким образом при включении микропрограммы все данные поступают из регистров. Такое АЛУ универсально, так как может выполнить любую микрокоманду, но имеет малое быстродействие потому, что не имеет никаких готовых результатов и пользуется входными данными и промежуточными результатами, которые сама же и рассчитывает. Схема АЛУ на основах блоков памяти. Разновидностью АЛУ с магистральной структурой является схема АЛУ на основе блоков памяти. Эта схема имеет преимущество перед предыдущей схемой в том, что регистры микропроцессора остаются свободными для оперативной работы. В этой схеме имеется только два внутренних регистра (РБ – буферный регистр; АК – аккумулятор) с которых операнды поступают на входы ОБ АЛУ, промежуточные результаты могут загружаться в блок памяти (БП) или АК. Схема в отличии от предыдущей имеет меньшее быстродействие так как связь с БП осуществляется Остальные части схемы работают аналогично.

Входная шина микроопераций соединена с УУ. Входная и выходная шина данных соединена с блоком связи с ОП. Регистры Р 1, Р 2…Рn – это регистры блока регистров процессора. Каждый регистр имеет схему приема с выходной магистралью 3 и схему подключения к входным магистралям 1 и 2. Во входной шине микроопераций подается коды микроопераций, эти коды расшифровываются с помощью дешифратора, с выходов которого управляющие сигналы подаются на узлы схемы. Промежуточные результаты по магистрали 3 из АЛУ записываются в регистры (Р 1, Р 2…Рn), таким образом при включении микропрограммы все данные поступают из регистров. Такое АЛУ универсально, так как может выполнить любую микрокоманду, но имеет малое быстродействие потому, что не имеет никаких готовых результатов и пользуется входными данными и промежуточными результатами, которые сама же и рассчитывает. Схема АЛУ на основах блоков памяти. Разновидностью АЛУ с магистральной структурой является схема АЛУ на основе блоков памяти. Эта схема имеет преимущество перед предыдущей схемой в том, что регистры микропроцессора остаются свободными для оперативной работы. В этой схеме имеется только два внутренних регистра (РБ – буферный регистр; АК – аккумулятор) с которых операнды поступают на входы ОБ АЛУ, промежуточные результаты могут загружаться в блок памяти (БП) или АК. Схема в отличии от предыдущей имеет меньшее быстродействие так как связь с БП осуществляется Остальные части схемы работают аналогично.

Организация систем прерывания. План: 1. Состояние процессора; 2. Система прерывания программ; 3. Характеристика систем прерывания; 4. Процедура прерывания.

Организация систем прерывания. План: 1. Состояние процессора; 2. Система прерывания программ; 3. Характеристика систем прерывания; 4. Процедура прерывания.

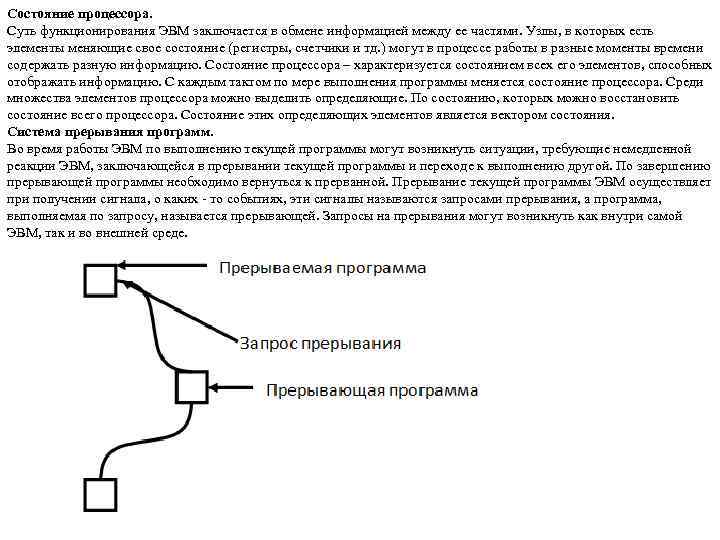

Состояние процессора. Суть функционирования ЭВМ заключается в обмене информацией между ее частями. Узлы, в которых есть элементы меняющие свое состояние (регистры, счетчики и тд. ) могут в процессе работы в разные моменты времени содержать разную информацию. Состояние процессора – характеризуется состоянием всех его элементов, способных отображать информацию. С каждым тактом по мере выполнения программы меняется состояние процессора. Среди множества элементов процессора можно выделить определяющие. По состоянию, которых можно восстановить состояние всего процессора. Состояние этих определяющих элементов является вектором состояния. Система прерывания программ. Во время работы ЭВМ по выполнению текущей программы могут возникнуть ситуации, требующие немедленной реакции ЭВМ, заключающейся в прерывании текущей программы и переходе к выполнению другой. По завершению прерывающей программы необходимо вернуться к прерванной. Прерывание текущей программы ЭВМ осуществляет при получении сигнала, о каких - то событиях, эти сигналы называются запросами прерывания, а программа, выполняемая по запросу, называется прерывающей. Запросы на прерывания могут возникнуть как внутри самой ЭВМ, так и во внешней среде.

Состояние процессора. Суть функционирования ЭВМ заключается в обмене информацией между ее частями. Узлы, в которых есть элементы меняющие свое состояние (регистры, счетчики и тд. ) могут в процессе работы в разные моменты времени содержать разную информацию. Состояние процессора – характеризуется состоянием всех его элементов, способных отображать информацию. С каждым тактом по мере выполнения программы меняется состояние процессора. Среди множества элементов процессора можно выделить определяющие. По состоянию, которых можно восстановить состояние всего процессора. Состояние этих определяющих элементов является вектором состояния. Система прерывания программ. Во время работы ЭВМ по выполнению текущей программы могут возникнуть ситуации, требующие немедленной реакции ЭВМ, заключающейся в прерывании текущей программы и переходе к выполнению другой. По завершению прерывающей программы необходимо вернуться к прерванной. Прерывание текущей программы ЭВМ осуществляет при получении сигнала, о каких - то событиях, эти сигналы называются запросами прерывания, а программа, выполняемая по запросу, называется прерывающей. Запросы на прерывания могут возникнуть как внутри самой ЭВМ, так и во внешней среде.

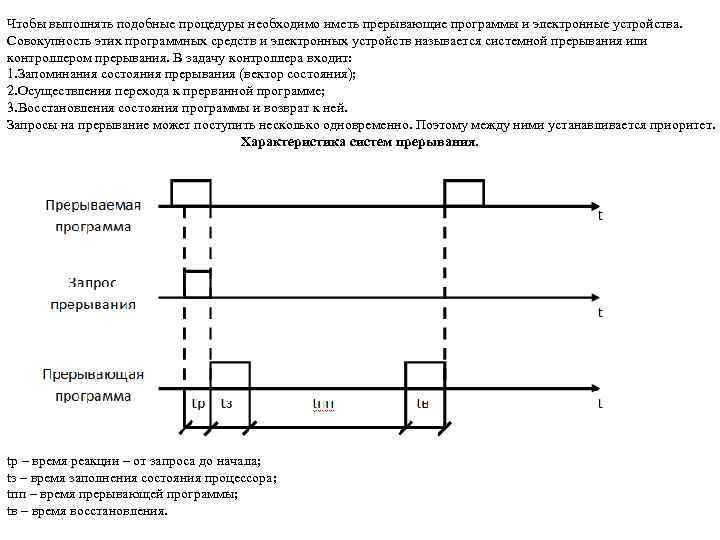

Чтобы выполнять подобные процедуры необходимо иметь прерывающие программы и электронные устройства. Совокупность этих программных средств и электронных устройств называется системной прерывания или контроллером прерывания. В задачу контроллера входит: 1. Запоминания состояния прерывания (вектор состояния); 2. Осуществления перехода к прерванной программе; 3. Восстановления состояния программы и возврат к ней. Запросы на прерывание может поступить несколько одновременно. Поэтому между ними устанавливается приоритет. Характеристика систем прерывания. tp – время реакции – от запроса до начала; tз – время заполнения состояния процессора; tпп – время прерывающей программы; tв – время восстановления.

Чтобы выполнять подобные процедуры необходимо иметь прерывающие программы и электронные устройства. Совокупность этих программных средств и электронных устройств называется системной прерывания или контроллером прерывания. В задачу контроллера входит: 1. Запоминания состояния прерывания (вектор состояния); 2. Осуществления перехода к прерванной программе; 3. Восстановления состояния программы и возврат к ней. Запросы на прерывание может поступить несколько одновременно. Поэтому между ними устанавливается приоритет. Характеристика систем прерывания. tp – время реакции – от запроса до начала; tз – время заполнения состояния процессора; tпп – время прерывающей программы; tв – время восстановления.

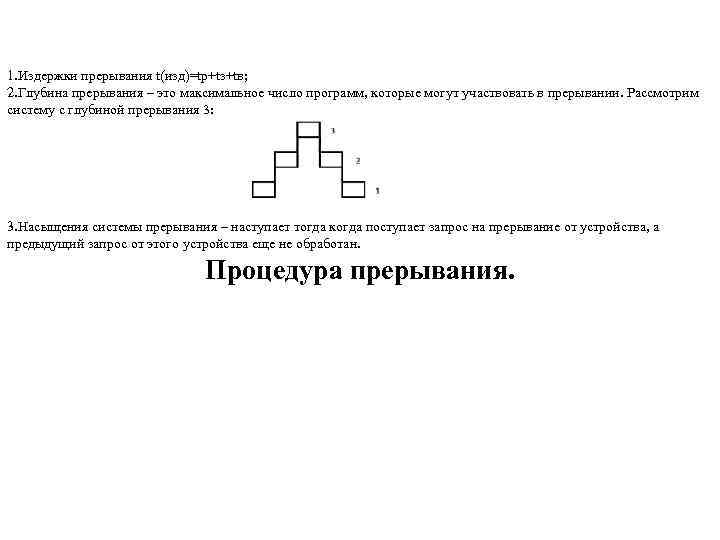

1. Издержки прерывания t(изд)=tp+tз+tв; 2. Глубина прерывания – это максимальное число программ, которые могут участвовать в прерывании. Рассмотрим систему с глубиной прерывания 3: 3. Насыщения системы прерывания – наступает тогда когда поступает запрос на прерывание от устройства, а предыдущий запрос от этого устройства еще не обработан. Процедура прерывания.

1. Издержки прерывания t(изд)=tp+tз+tв; 2. Глубина прерывания – это максимальное число программ, которые могут участвовать в прерывании. Рассмотрим систему с глубиной прерывания 3: 3. Насыщения системы прерывания – наступает тогда когда поступает запрос на прерывание от устройства, а предыдущий запрос от этого устройства еще не обработан. Процедура прерывания.

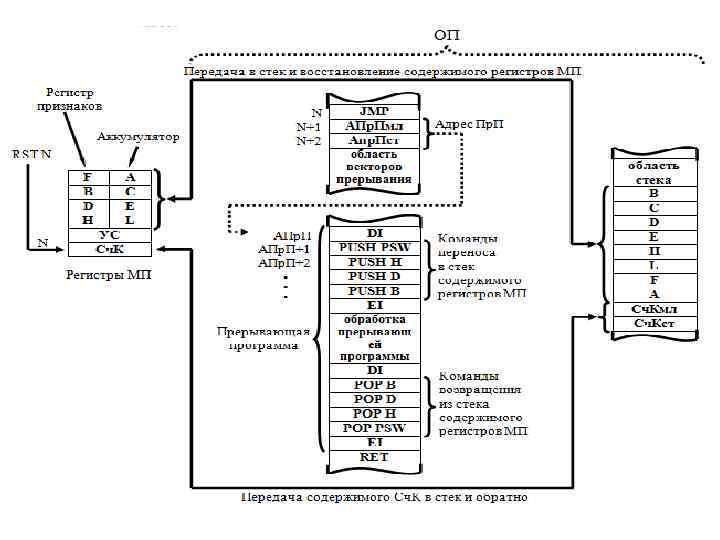

Процедура прерывания начинается с команды RST N. По этой команде содержимое счетчика команд Сч. К отправляется в стек, а в счетчик команд загружается адрес N. Процессор, закончив текущую команду, начинает выполнять команду по адресу N, это JMP. По команде JMP в счетчик команд отправляется два следующие за JMP байта, в них содержится адрес прерывающей программы АПр. П. Прерывающая программа начинается с команды DI, которая запрещает действие следующего прерывания, т. е. следующая команда RST будет игнорирована. Затем идут четыре команды PUSH, отправляющие попарно регистры микропроцессора в стек. PUSH PSW – A и F PUSH H – L и H PUSH D – E и D PUSH B – C и B После завершения этих команд выполняется команда EI, отменяющая действие команда DI. После завершения сохранения регистров микропроцессора выполняется программа обработки прерывания. Затем выполняется процесс возврата из стека значения регистров микропроцессора. Для этого предназначены четыре команды POP возвращающие значение регистров попарно в обратном порядке. POP B – B и C POP D – D и E POP H – H и L POP PSW – F и A Команды также ограничены командами DI и EI. Заканчивается процедура прерывания командой RET, которая возвращает содержимое счетчика команд из стека.

Процедура прерывания начинается с команды RST N. По этой команде содержимое счетчика команд Сч. К отправляется в стек, а в счетчик команд загружается адрес N. Процессор, закончив текущую команду, начинает выполнять команду по адресу N, это JMP. По команде JMP в счетчик команд отправляется два следующие за JMP байта, в них содержится адрес прерывающей программы АПр. П. Прерывающая программа начинается с команды DI, которая запрещает действие следующего прерывания, т. е. следующая команда RST будет игнорирована. Затем идут четыре команды PUSH, отправляющие попарно регистры микропроцессора в стек. PUSH PSW – A и F PUSH H – L и H PUSH D – E и D PUSH B – C и B После завершения этих команд выполняется команда EI, отменяющая действие команда DI. После завершения сохранения регистров микропроцессора выполняется программа обработки прерывания. Затем выполняется процесс возврата из стека значения регистров микропроцессора. Для этого предназначены четыре команды POP возвращающие значение регистров попарно в обратном порядке. POP B – B и C POP D – D и E POP H – H и L POP PSW – F и A Команды также ограничены командами DI и EI. Заканчивается процедура прерывания командой RET, которая возвращает содержимое счетчика команд из стека.

Основные понятия об интерфейсах. План: 1. Требования, предъявляемые к интерфейсу; 2. Прямой доступ к памяти

Основные понятия об интерфейсах. План: 1. Требования, предъявляемые к интерфейсу; 2. Прямой доступ к памяти

Требования, предъявляемые к интерфейсу. По мимо процессора и основной памяти образующий ядро ЭВМ. В состав ЭВМ входят периферийные устройства внешняя память, устройства ввода – вывода и другие). Связь устройств друг с другом осуществляется с помощью сопряжений которые в ЭВМ называются интерфейсами. Интерфейс представляет собой совокупность: 1. Электронных схем и их сигналов; 2. Линий и шин; 3. Алгоритмов и программ. Интерфейс должен решать следующие задачи: 1. Возможность расширения периферии ЭВМ; 2. Параллельность в работе ее ядра и периферии; 3. Совместимость в работе различных устройств независимо от их особенностей; 4. Автоматическое распознавание ядром ЭВМ различных ситуаций и реакций на них. Эти задачи решаются по средствам модульности и унификации. Модульность заключается в том, что отдельные устройства выполнены в виде конструктивно законченных изделий (модулей) которые легко объединяются в ЭВМ. К унификации относится: 1. Унификация форматов данных; 2. Унификация устройств; 3. Унификация команд.

Требования, предъявляемые к интерфейсу. По мимо процессора и основной памяти образующий ядро ЭВМ. В состав ЭВМ входят периферийные устройства внешняя память, устройства ввода – вывода и другие). Связь устройств друг с другом осуществляется с помощью сопряжений которые в ЭВМ называются интерфейсами. Интерфейс представляет собой совокупность: 1. Электронных схем и их сигналов; 2. Линий и шин; 3. Алгоритмов и программ. Интерфейс должен решать следующие задачи: 1. Возможность расширения периферии ЭВМ; 2. Параллельность в работе ее ядра и периферии; 3. Совместимость в работе различных устройств независимо от их особенностей; 4. Автоматическое распознавание ядром ЭВМ различных ситуаций и реакций на них. Эти задачи решаются по средствам модульности и унификации. Модульность заключается в том, что отдельные устройства выполнены в виде конструктивно законченных изделий (модулей) которые легко объединяются в ЭВМ. К унификации относится: 1. Унификация форматов данных; 2. Унификация устройств; 3. Унификация команд.

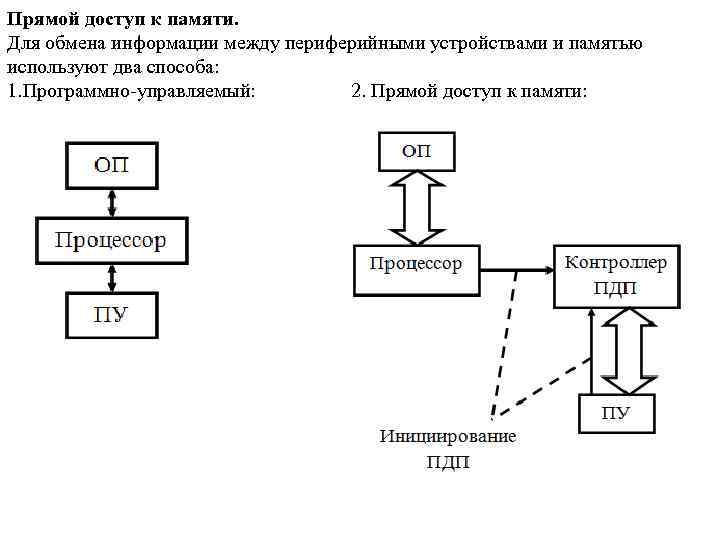

Прямой доступ к памяти. Для обмена информации между периферийными устройствами и памятью используют два способа: 1. Программно-управляемый: 2. Прямой доступ к памяти:

Прямой доступ к памяти. Для обмена информации между периферийными устройствами и памятью используют два способа: 1. Программно-управляемый: 2. Прямой доступ к памяти:

Каналы ввода – вывода. План: 1. Мультиплексный канал; 2. Селекторный канал.

Каналы ввода – вывода. План: 1. Мультиплексный канал; 2. Селекторный канал.

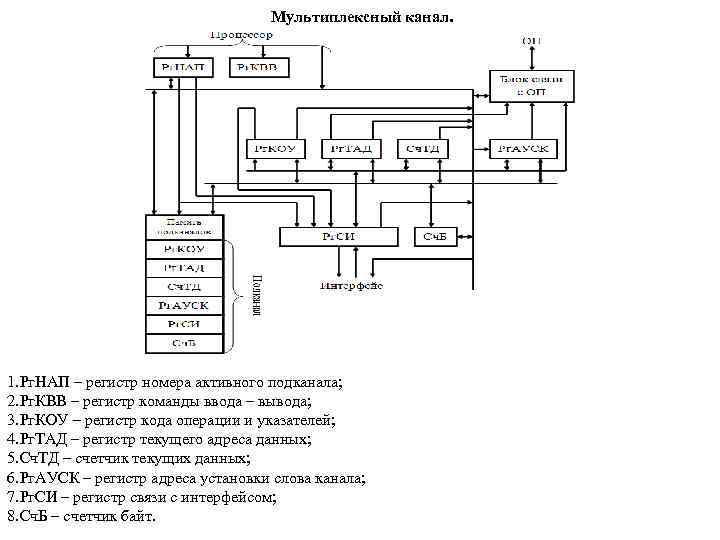

Мультиплексный канал. 1. Рг. НАП – регистр номера активного подканала; 2. Рг. КВВ – регистр команды ввода – вывода; 3. Рг. КОУ – регистр кода операции и указателей; 4. Рг. ТАД – регистр текущего адреса данных; 5. Сч. ТД – счетчик текущих данных; 6. Рг. АУСК – регистр адреса установки слова канала; 7. Рг. СИ – регистр связи с интерфейсом; 8. Сч. Б – счетчик байт.

Мультиплексный канал. 1. Рг. НАП – регистр номера активного подканала; 2. Рг. КВВ – регистр команды ввода – вывода; 3. Рг. КОУ – регистр кода операции и указателей; 4. Рг. ТАД – регистр текущего адреса данных; 5. Сч. ТД – счетчик текущих данных; 6. Рг. АУСК – регистр адреса установки слова канала; 7. Рг. СИ – регистр связи с интерфейсом; 8. Сч. Б – счетчик байт.

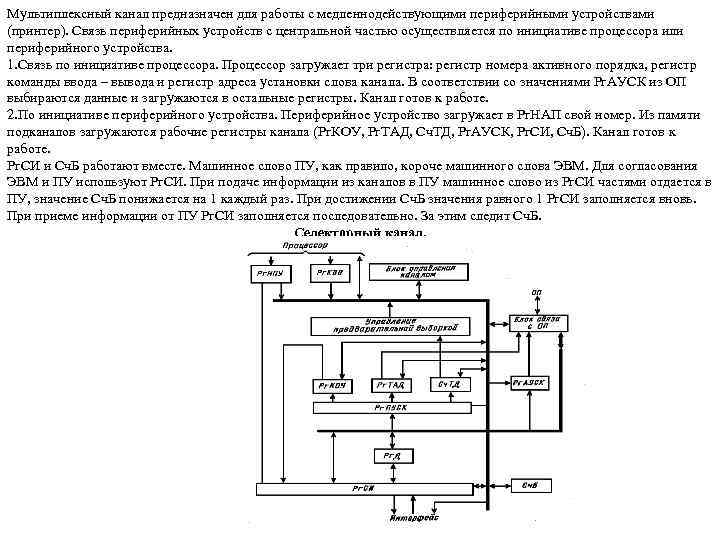

Мультиплексный канал предназначен для работы с медленнодействующими периферийными устройствами (принтер). Связь периферийных устройств с центральной частью осуществляется по инициативе процессора или периферийного устройства. 1. Связь по инициативе процессора. Процессор загружает три регистра: регистр номера активного порядка, регистр команды ввода – вывода и регистр адреса установки слова канала. В соответствии со значениями Рг. АУСК из ОП выбираются данные и загружаются в остальные регистры. Канал готов к работе. 2. По инициативе периферийного устройства. Периферийное устройство загружает в Рг. НАП свой номер. Из памяти подканалов загружаются рабочие регистры канала (Рг. КОУ, Рг. ТАД, Сч. ТД, Рг. АУСК, Рг. СИ, Сч. Б). Канал готов к работе. Рг. СИ и Сч. Б работают вместе. Машинное слово ПУ, как правило, короче машинного слова ЭВМ. Для согласования ЭВМ и ПУ используют Рг. СИ. При подаче информации из каналов в ПУ машинное слово из Рг. СИ частями отдается в ПУ, значение Сч. Б понижается на 1 каждый раз. При достижении Сч. Б значения равного 1 Рг. СИ заполняется вновь. При приеме информации от ПУ Рг. СИ заполняется последовательно. За этим следит Сч. Б. Селекторный канал.

Мультиплексный канал предназначен для работы с медленнодействующими периферийными устройствами (принтер). Связь периферийных устройств с центральной частью осуществляется по инициативе процессора или периферийного устройства. 1. Связь по инициативе процессора. Процессор загружает три регистра: регистр номера активного порядка, регистр команды ввода – вывода и регистр адреса установки слова канала. В соответствии со значениями Рг. АУСК из ОП выбираются данные и загружаются в остальные регистры. Канал готов к работе. 2. По инициативе периферийного устройства. Периферийное устройство загружает в Рг. НАП свой номер. Из памяти подканалов загружаются рабочие регистры канала (Рг. КОУ, Рг. ТАД, Сч. ТД, Рг. АУСК, Рг. СИ, Сч. Б). Канал готов к работе. Рг. СИ и Сч. Б работают вместе. Машинное слово ПУ, как правило, короче машинного слова ЭВМ. Для согласования ЭВМ и ПУ используют Рг. СИ. При подаче информации из каналов в ПУ машинное слово из Рг. СИ частями отдается в ПУ, значение Сч. Б понижается на 1 каждый раз. При достижении Сч. Б значения равного 1 Рг. СИ заполняется вновь. При приеме информации от ПУ Рг. СИ заполняется последовательно. За этим следит Сч. Б. Селекторный канал.