Без имени 111.ppt

- Количество слайдов: 15

Кэш-память Выполнила ученица 9 «Е» класса: Протченко Екатерина

Кэш-память Выполнила ученица 9 «Е» класса: Протченко Екатерина

![Введение Кэш или кеш (англ. cache, от фр. cacher — «прятать» ; произносится [kæʃ] Введение Кэш или кеш (англ. cache, от фр. cacher — «прятать» ; произносится [kæʃ]](https://present5.com/presentation/27681042_47101951/image-2.jpg) Введение Кэш или кеш (англ. cache, от фр. cacher — «прятать» ; произносится [kæʃ] — «кэш» ) — промежуточный буфер с быстрым доступом, содержащий информацию, которая может быть запрошена с наибольшей вероятностью. Доступ к данным в кэше идёт быстрее, чем выборка исходных данных из оперативной (ОЗУ) и быстрее внешней (жёсткий диск или твердотельный накопитель) памяти, за счёт чего уменьшается среднее время доступа и увеличивается общая производительность компьютерной системы. Доступ к данным , хранящимся в кэше программным путем на процессорах линейки [x 86] невозможен.

Введение Кэш или кеш (англ. cache, от фр. cacher — «прятать» ; произносится [kæʃ] — «кэш» ) — промежуточный буфер с быстрым доступом, содержащий информацию, которая может быть запрошена с наибольшей вероятностью. Доступ к данным в кэше идёт быстрее, чем выборка исходных данных из оперативной (ОЗУ) и быстрее внешней (жёсткий диск или твердотельный накопитель) памяти, за счёт чего уменьшается среднее время доступа и увеличивается общая производительность компьютерной системы. Доступ к данным , хранящимся в кэше программным путем на процессорах линейки [x 86] невозможен.

История Впервые слово «кэш» в компьютерном контексте было использовано в 1967 году во время подготовки статьи для публикации в журнале «IBM Systems Journal» . Статья касалась усовершенствования памяти в разрабатываемой модели 85 из серии IBM System/360. Редактор журнала Лайл Джонсон попросил придумать более описательный термин, нежели «высокоскоростной буфер» , но из-за отсутствия идей сам предложил слово «кэш» . Статья была опубликована в начале 1968 года, авторы были премированы IBM, их работа получила распространение и впоследствии была улучшена, а слово «кэш» вскоре стало использоваться в компьютерной литературе как общепринятый термин.

История Впервые слово «кэш» в компьютерном контексте было использовано в 1967 году во время подготовки статьи для публикации в журнале «IBM Systems Journal» . Статья касалась усовершенствования памяти в разрабатываемой модели 85 из серии IBM System/360. Редактор журнала Лайл Джонсон попросил придумать более описательный термин, нежели «высокоскоростной буфер» , но из-за отсутствия идей сам предложил слово «кэш» . Статья была опубликована в начале 1968 года, авторы были премированы IBM, их работа получила распространение и впоследствии была улучшена, а слово «кэш» вскоре стало использоваться в компьютерной литературе как общепринятый термин.

данных из основной памяти. Если большая часть запросов в память будет обрабатываться кэшем, средняя задержка обращения к памяти будет приближаться к задержкам работы кэша. Когда процессору нужно обратиться в память для чтения или записи данных, он сначала проверяет, доступна ли их копия в кэше. В случае успеха проверки процессор производит операцию используя кэш, что быстрее использования более медленной основной памяти. Подробнее о задержках памяти см. Задержки (англ. SDRAM latency) SDRAM: t. CAS, t. RCD, t. RP, t. RAS Когда процессору нужно обратиться в память для чтения или записи данных, он сначала проверяет, доступна ли их копия в кэше. В случае успеха проверки процессор производит операцию используя кэш, что быстрее использования более Кэш микропроцессора

данных из основной памяти. Если большая часть запросов в память будет обрабатываться кэшем, средняя задержка обращения к памяти будет приближаться к задержкам работы кэша. Когда процессору нужно обратиться в память для чтения или записи данных, он сначала проверяет, доступна ли их копия в кэше. В случае успеха проверки процессор производит операцию используя кэш, что быстрее использования более медленной основной памяти. Подробнее о задержках памяти см. Задержки (англ. SDRAM latency) SDRAM: t. CAS, t. RCD, t. RP, t. RAS Когда процессору нужно обратиться в память для чтения или записи данных, он сначала проверяет, доступна ли их копия в кэше. В случае успеха проверки процессор производит операцию используя кэш, что быстрее использования более Кэш микропроцессора

Функционирование кэша Кэш — это память с большей скоростью доступа, предназначенная для ускорения обращения к данным, содержащимся постоянно в памяти с меньшей скоростью доступа (далее «основная память» ). Кэширование применяется ЦПУ, жёсткими дисками, браузерами, веб-серверами, службами DNS и WINS. Кэш состоит из набора записей. Каждая запись ассоциирована с элементом данных или блоком данных (небольшой части данных), которая является копией элемента данных в основной памяти. Каждая запись имеет идентификатор, определяющий соответствие между элементами данных в кэше и их копиями в основной памяти.

Функционирование кэша Кэш — это память с большей скоростью доступа, предназначенная для ускорения обращения к данным, содержащимся постоянно в памяти с меньшей скоростью доступа (далее «основная память» ). Кэширование применяется ЦПУ, жёсткими дисками, браузерами, веб-серверами, службами DNS и WINS. Кэш состоит из набора записей. Каждая запись ассоциирована с элементом данных или блоком данных (небольшой части данных), которая является копией элемента данных в основной памяти. Каждая запись имеет идентификатор, определяющий соответствие между элементами данных в кэше и их копиями в основной памяти.

Кэш центрального процессора Ряд моделей центральных процессоров (ЦП) обладают собственным кэшем, для того чтобы минимизировать доступ к оперативной памяти (ОЗУ), которая медленнее, чем регистры. Кэш-память может давать значительный выигрыш в производительности, в случае когда тактовая частота ОЗУ значительно меньше тактовой частоты ЦП. Тактовая частота для кэш-памяти обычно ненамного меньше частоты ЦП. В процессорах с поддержкой виртуальной адресации часто вводят небольшой быстродействующий буфер трансляций адресов (TLB). Его скорость важна, т. к. он опрашивается на каждом обращении в память. Уровни кэша Кэш центрального процессора разделён на несколько уровней. В универсальном процессоре в настоящее время число уровней может достигать 3. Кэш-память уровня N+1 как правило больше по размеру и медленнее по скорости доступа и передаче данных, чем кэш-память уровня N

Кэш центрального процессора Ряд моделей центральных процессоров (ЦП) обладают собственным кэшем, для того чтобы минимизировать доступ к оперативной памяти (ОЗУ), которая медленнее, чем регистры. Кэш-память может давать значительный выигрыш в производительности, в случае когда тактовая частота ОЗУ значительно меньше тактовой частоты ЦП. Тактовая частота для кэш-памяти обычно ненамного меньше частоты ЦП. В процессорах с поддержкой виртуальной адресации часто вводят небольшой быстродействующий буфер трансляций адресов (TLB). Его скорость важна, т. к. он опрашивается на каждом обращении в память. Уровни кэша Кэш центрального процессора разделён на несколько уровней. В универсальном процессоре в настоящее время число уровней может достигать 3. Кэш-память уровня N+1 как правило больше по размеру и медленнее по скорости доступа и передаче данных, чем кэш-память уровня N

Самой быстрой памятью является кэш первого уровня — L 1 -cache. По сути, она является неотъемлемой частью процессора, поскольку расположена на одном с ним кристалле и входит в состав функциональных блоков. В современных процессорах обычно кэш L 1 разделен на два кэша, кэш команд (инструкций) и кэш данных (Гарвардская архитектура). Большинство процессоров без L 1 кэша не могут функционировать. L 1 кэш работает на частоте процессора, и, в общем случае, обращение к нему может производиться каждый такт. Зачастую является возможным выполнять несколько операций чтения/записи одновременно. Латентность доступа обычно равна 2− 4 тактам ядра. Объём обычно невелик — не более 384 Кбайт. Вторым по быстродействию является L 2 -cache — кэш второго уровня, обычно он расположен на кристалле, как и L 1. В старых процессорах — набор микросхем на системной плате. Объём L 2 кэша от 128 Кбайт до 1− 12 Мбайт. В современных многоядерных процессорах кэш второго уровня, находясь на том же кристалле, является памятью раздельного пользования — при общем объёме кэша в n. M Мбайт на каждое ядро приходится по n. M/n. C Мбайта, где n. C количество ядер процессора. Обычно латентность L 2 кэша, расположенного на кристалле ядра, составляет от 8 до 20 тактов ядра. Кэш третьего уровня наименее быстродействующий, но он может быть очень внушительного размера — более 24 Мбайт. L 3 кэш медленнее предыдущих кэшей, но всё равно значительно быстрее, чем оперативная память. В многопроцессорных системах находится в общем пользовании и предназначен для синхронизации данных различных L 2. Иногда существует и 4 уровень кэша, обыкновенно он расположен в отдельной микросхеме. Применение кэша 4 уровня оправдано только для высоко производительных серверов и мейнфреймов.

Самой быстрой памятью является кэш первого уровня — L 1 -cache. По сути, она является неотъемлемой частью процессора, поскольку расположена на одном с ним кристалле и входит в состав функциональных блоков. В современных процессорах обычно кэш L 1 разделен на два кэша, кэш команд (инструкций) и кэш данных (Гарвардская архитектура). Большинство процессоров без L 1 кэша не могут функционировать. L 1 кэш работает на частоте процессора, и, в общем случае, обращение к нему может производиться каждый такт. Зачастую является возможным выполнять несколько операций чтения/записи одновременно. Латентность доступа обычно равна 2− 4 тактам ядра. Объём обычно невелик — не более 384 Кбайт. Вторым по быстродействию является L 2 -cache — кэш второго уровня, обычно он расположен на кристалле, как и L 1. В старых процессорах — набор микросхем на системной плате. Объём L 2 кэша от 128 Кбайт до 1− 12 Мбайт. В современных многоядерных процессорах кэш второго уровня, находясь на том же кристалле, является памятью раздельного пользования — при общем объёме кэша в n. M Мбайт на каждое ядро приходится по n. M/n. C Мбайта, где n. C количество ядер процессора. Обычно латентность L 2 кэша, расположенного на кристалле ядра, составляет от 8 до 20 тактов ядра. Кэш третьего уровня наименее быстродействующий, но он может быть очень внушительного размера — более 24 Мбайт. L 3 кэш медленнее предыдущих кэшей, но всё равно значительно быстрее, чем оперативная память. В многопроцессорных системах находится в общем пользовании и предназначен для синхронизации данных различных L 2. Иногда существует и 4 уровень кэша, обыкновенно он расположен в отдельной микросхеме. Применение кэша 4 уровня оправдано только для высоко производительных серверов и мейнфреймов.

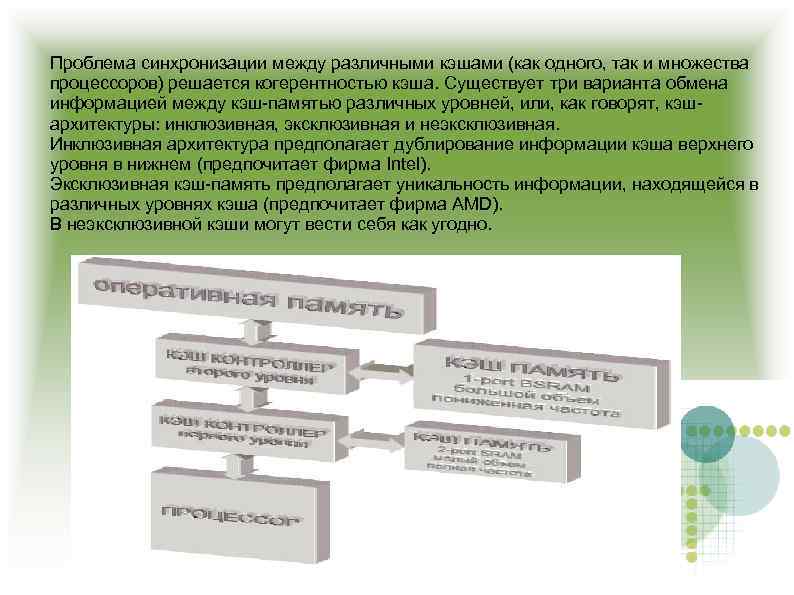

Проблема синхронизации между различными кэшами (как одного, так и множества процессоров) решается когерентностью кэша. Существует три варианта обмена информацией между кэш-памятью различных уровней, или, как говорят, кэшархитектуры: инклюзивная, эксклюзивная и неэксклюзивная. Инклюзивная архитектура предполагает дублирование информации кэша верхнего уровня в нижнем (предпочитает фирма Intel). Эксклюзивная кэш-память предполагает уникальность информации, находящейся в различных уровнях кэша (предпочитает фирма AMD). В неэксклюзивной кэши могут вести себя как угодно.

Проблема синхронизации между различными кэшами (как одного, так и множества процессоров) решается когерентностью кэша. Существует три варианта обмена информацией между кэш-памятью различных уровней, или, как говорят, кэшархитектуры: инклюзивная, эксклюзивная и неэксклюзивная. Инклюзивная архитектура предполагает дублирование информации кэша верхнего уровня в нижнем (предпочитает фирма Intel). Эксклюзивная кэш-память предполагает уникальность информации, находящейся в различных уровнях кэша (предпочитает фирма AMD). В неэксклюзивной кэши могут вести себя как угодно.

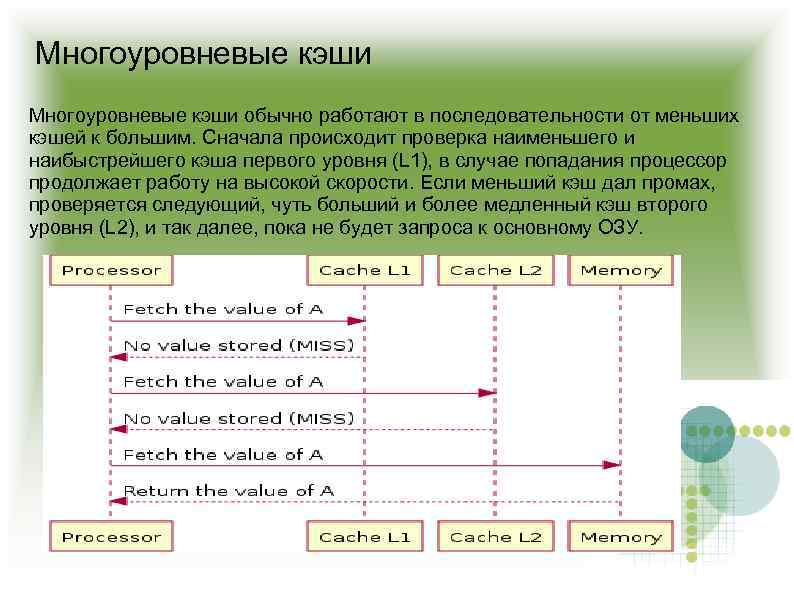

Многоуровневые кэши обычно работают в последовательности от меньших кэшей к большим. Сначала происходит проверка наименьшего и наибыстрейшего кэша первого уровня (L 1), в случае попадания процессор продолжает работу на высокой скорости. Если меньший кэш дал промах, проверяется следующий, чуть больший и более медленный кэш второго уровня (L 2), и так далее, пока не будет запроса к основному ОЗУ.

Многоуровневые кэши обычно работают в последовательности от меньших кэшей к большим. Сначала происходит проверка наименьшего и наибыстрейшего кэша первого уровня (L 1), в случае попадания процессор продолжает работу на высокой скорости. Если меньший кэш дал промах, проверяется следующий, чуть больший и более медленный кэш второго уровня (L 2), и так далее, пока не будет запроса к основному ОЗУ.

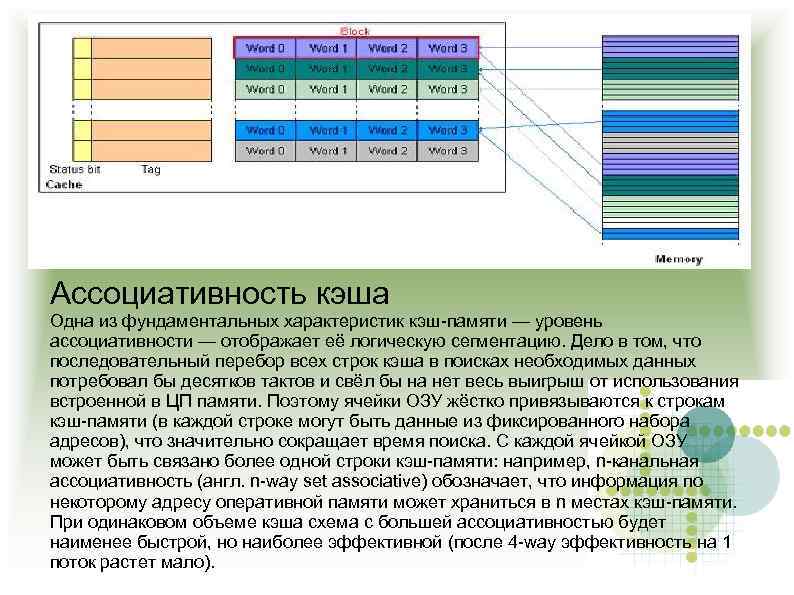

Ассоциативность кэша Одна из фундаментальных характеристик кэш-памяти — уровень ассоциативности — отображает её логическую сегментацию. Дело в том, что последовательный перебор всех строк кэша в поисках необходимых данных потребовал бы десятков тактов и свёл бы на нет весь выигрыш от использования встроенной в ЦП памяти. Поэтому ячейки ОЗУ жёстко привязываются к строкам кэш-памяти (в каждой строке могут быть данные из фиксированного набора адресов), что значительно сокращает время поиска. С каждой ячейкой ОЗУ может быть связано более одной строки кэш-памяти: например, n-канальная ассоциативность (англ. n-way set associative) обозначает, что информация по некоторому адресу оперативной памяти может храниться в n местах кэш-памяти. При одинаковом объеме кэша схема с большей ассоциативностью будет наименее быстрой, но наиболее эффективной (после 4 -way эффективность на 1 поток растет мало).

Ассоциативность кэша Одна из фундаментальных характеристик кэш-памяти — уровень ассоциативности — отображает её логическую сегментацию. Дело в том, что последовательный перебор всех строк кэша в поисках необходимых данных потребовал бы десятков тактов и свёл бы на нет весь выигрыш от использования встроенной в ЦП памяти. Поэтому ячейки ОЗУ жёстко привязываются к строкам кэш-памяти (в каждой строке могут быть данные из фиксированного набора адресов), что значительно сокращает время поиска. С каждой ячейкой ОЗУ может быть связано более одной строки кэш-памяти: например, n-канальная ассоциативность (англ. n-way set associative) обозначает, что информация по некоторому адресу оперативной памяти может храниться в n местах кэш-памяти. При одинаковом объеме кэша схема с большей ассоциативностью будет наименее быстрой, но наиболее эффективной (после 4 -way эффективность на 1 поток растет мало).

«Кэш жертв» (англ. Victim cache или Victim buffer) — это небольшой специализированный кэш, хранящий те кэш-линии, которые были недавно вытеснены из основного кэша микропроцессора при их замещении. Данный кэш располагается между основным кэшем и его англ. refill path. Обычно кэш жертв является полностью ассоциативным и служит для уменьшения количества конфликтных промахов (conflict miss). Многие часто используемые программы не требуют полного ассоциативного отображения для всех попыток доступа к памяти. По статистике, только небольшая доля обращений к памяти потребует высокой степени ассоциативности. Именно для таких обращений служит кэш жертв, предоставляющий высокую ассоциативность для подобных редких запросов. Был предложен Norman Jouppi (DEC) в 1990. Размер такого кеша может составлять от 4 до 16 кеш-линий Кэш трасс — это механизм для увеличения пропускной способности загрузки инструкций и для уменьшения тепловыделения (в случае Pentium 4) за счет хранения декодированных трасс инструкций. Таким образом этот кэш исключал работу декодера при повторном исполнении недавно выполнявшегося кода.

«Кэш жертв» (англ. Victim cache или Victim buffer) — это небольшой специализированный кэш, хранящий те кэш-линии, которые были недавно вытеснены из основного кэша микропроцессора при их замещении. Данный кэш располагается между основным кэшем и его англ. refill path. Обычно кэш жертв является полностью ассоциативным и служит для уменьшения количества конфликтных промахов (conflict miss). Многие часто используемые программы не требуют полного ассоциативного отображения для всех попыток доступа к памяти. По статистике, только небольшая доля обращений к памяти потребует высокой степени ассоциативности. Именно для таких обращений служит кэш жертв, предоставляющий высокую ассоциативность для подобных редких запросов. Был предложен Norman Jouppi (DEC) в 1990. Размер такого кеша может составлять от 4 до 16 кеш-линий Кэш трасс — это механизм для увеличения пропускной способности загрузки инструкций и для уменьшения тепловыделения (в случае Pentium 4) за счет хранения декодированных трасс инструкций. Таким образом этот кэш исключал работу декодера при повторном исполнении недавно выполнявшегося кода.

Пример кэша (процессорное ядро К 8)

Пример кэша (процессорное ядро К 8)

Кэширование, выполняемое операционной системой Кэш оперативной памяти состоит из следующих элементов: 1. набор страниц оперативной памяти, разделённых на буферы, равные по длине блоку данных соответствующего устройства внешней памяти; 2. набор заголовков буферов, описывающих состояние соответствующего буфера; 3. хеш-таблицы, содержащей соответствие номера блока заголовку; 4. списки свободных буферов Алгоритм работы кэша с отложенной записью Изначально все заголовки буферов помещаются в список свободных буферов. Если процесс намеревается прочитать или модифицировать блок, то он выполняет следующий алгоритм: 1. пытается найти в хеш-таблице заголовок буфера с заданным номером; 2. в случае, если полученный буфер занят, ждёт его освобождения; 3. в случае, если буфер не найден в хеш-таблице, берёт первый буфер из хвоста списка свободных; 4. в случае, если список свободных буферов пуст, то выполняется алгоритм вытеснения (см. ниже); 5. в случае, если полученный буфер помечен как «грязный» , выполняет асинхронную запись содержимого буфера во внешнюю память. 6. удаляет буфер из хеш-таблицы, если он был помещён в неё; 7. помещает буфер в хеш-таблицу с новым номером.

Кэширование, выполняемое операционной системой Кэш оперативной памяти состоит из следующих элементов: 1. набор страниц оперативной памяти, разделённых на буферы, равные по длине блоку данных соответствующего устройства внешней памяти; 2. набор заголовков буферов, описывающих состояние соответствующего буфера; 3. хеш-таблицы, содержащей соответствие номера блока заголовку; 4. списки свободных буферов Алгоритм работы кэша с отложенной записью Изначально все заголовки буферов помещаются в список свободных буферов. Если процесс намеревается прочитать или модифицировать блок, то он выполняет следующий алгоритм: 1. пытается найти в хеш-таблице заголовок буфера с заданным номером; 2. в случае, если полученный буфер занят, ждёт его освобождения; 3. в случае, если буфер не найден в хеш-таблице, берёт первый буфер из хвоста списка свободных; 4. в случае, если список свободных буферов пуст, то выполняется алгоритм вытеснения (см. ниже); 5. в случае, если полученный буфер помечен как «грязный» , выполняет асинхронную запись содержимого буфера во внешнюю память. 6. удаляет буфер из хеш-таблицы, если он был помещён в неё; 7. помещает буфер в хеш-таблицу с новым номером.

Политика записи при кэшировании Существуют две основные политики записи кэш-памяти — сквозная запись (write-through) и отложенная запись (write-back): Сквозная запись — запись производится непосредственно в основную память (и дублируется в кэш), т. е. запись не кэшируется. Отложенная запись — запись данных производится в кэш. Запись же в основную память производится позже (при вытеснении или по истечению времени), группируя в одной операции несколько операций записи в соседние ячейки. Технология обратной записи на некоторое время делает данные в основной памяти неактуальными, для самого ЦП эти неактуальности не заметны, но перед обращением к памяти другого ведущего системной шины (контроллера DMA, bus-master-устройства шины PCI) кэш должен быть записан в память принудительно. При использовании обратной записи в многопроцессорной системе кэши различных ЦП должны быть согласованы (или процессоры должны использовать одну кеш-память).

Политика записи при кэшировании Существуют две основные политики записи кэш-памяти — сквозная запись (write-through) и отложенная запись (write-back): Сквозная запись — запись производится непосредственно в основную память (и дублируется в кэш), т. е. запись не кэшируется. Отложенная запись — запись данных производится в кэш. Запись же в основную память производится позже (при вытеснении или по истечению времени), группируя в одной операции несколько операций записи в соседние ячейки. Технология обратной записи на некоторое время делает данные в основной памяти неактуальными, для самого ЦП эти неактуальности не заметны, но перед обращением к памяти другого ведущего системной шины (контроллера DMA, bus-master-устройства шины PCI) кэш должен быть записан в память принудительно. При использовании обратной записи в многопроцессорной системе кэши различных ЦП должны быть согласованы (или процессоры должны использовать одну кеш-память).

Примечания Литература: Большой толковый словарь русского языка / автор, сост. и гл. ред. С. А. Кузнецов. 2000 г. РАН Институт лингвистических исследований Захаренко Е. Н. , Комарова Л. Н. , Нечаева И. В. Новый словарь иностранных слов. М. : 2003 Толковый словарь по вычислительной технике. Microsoft Press, из-во «Русская Редакция» , 1995 Русский орфографический словарь: около 180 000 слов / Российская академия наук. Институт русского языка им. В. В. Виноградова / О. Е. Иванова, В. В. Лопатин (отв. ред. ), И. В. Нечаева, Л. К. Чельцова. — 2 -е изд. , испр. и доп. — М. : 2004. — 960 с. Першиков В. И. , Савинков В. М. Толковый словарь по информатике / Рецензенты: канд. физ. мат. наук А. С. Марков и д-р физ. -мат. наук И. В. Поттосин — М. : Финансы и статистика, 1991. — 543 с. — 50 000 экз. — ISBN 5 -279 -00367 -0. Борковский А. Б. Англо-русский словарь по программированию и информатике (с толкованиями) — М. : Русский язык, 1990. — 335 с. — 50 050 (доп. ) экз. — ISBN 5 -200 -01169 -3. G. C. Stierhoff, A. G. Davis. A History of the IBM Systems Journal // IEEE Annals of the History of Computing. — январь 1998. — Т. 20. — № 1. — С. 29— 35. — DOI: 10. 1109/85. 646206 Распределенные ОС

Примечания Литература: Большой толковый словарь русского языка / автор, сост. и гл. ред. С. А. Кузнецов. 2000 г. РАН Институт лингвистических исследований Захаренко Е. Н. , Комарова Л. Н. , Нечаева И. В. Новый словарь иностранных слов. М. : 2003 Толковый словарь по вычислительной технике. Microsoft Press, из-во «Русская Редакция» , 1995 Русский орфографический словарь: около 180 000 слов / Российская академия наук. Институт русского языка им. В. В. Виноградова / О. Е. Иванова, В. В. Лопатин (отв. ред. ), И. В. Нечаева, Л. К. Чельцова. — 2 -е изд. , испр. и доп. — М. : 2004. — 960 с. Першиков В. И. , Савинков В. М. Толковый словарь по информатике / Рецензенты: канд. физ. мат. наук А. С. Марков и д-р физ. -мат. наук И. В. Поттосин — М. : Финансы и статистика, 1991. — 543 с. — 50 000 экз. — ISBN 5 -279 -00367 -0. Борковский А. Б. Англо-русский словарь по программированию и информатике (с толкованиями) — М. : Русский язык, 1990. — 335 с. — 50 050 (доп. ) экз. — ISBN 5 -200 -01169 -3. G. C. Stierhoff, A. G. Davis. A History of the IBM Systems Journal // IEEE Annals of the History of Computing. — январь 1998. — Т. 20. — № 1. — С. 29— 35. — DOI: 10. 1109/85. 646206 Распределенные ОС