lect_cash.ppt

- Количество слайдов: 18

Кэш-память

Кэш-память

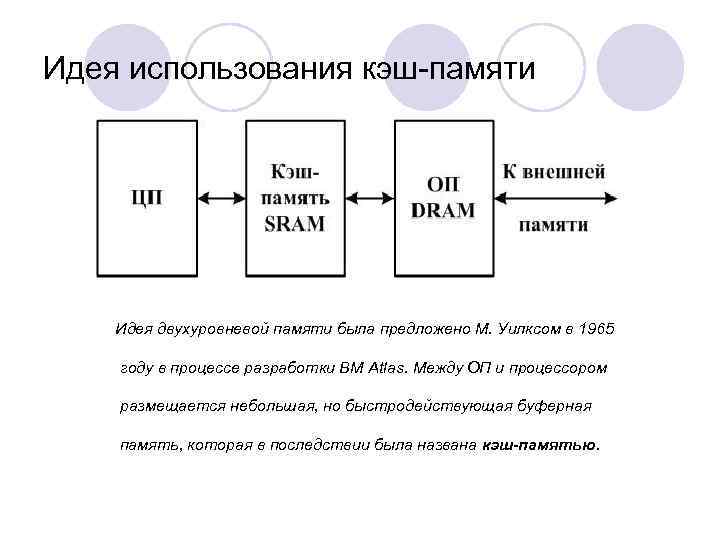

Идея использования кэш-памяти Идея двухуровневой памяти была предложено М. Уилксом в 1965 году в процессе разработки ВМ Atlas. Между ОП и процессором размещается небольшая, но быстродействующая буферная память, которая в последствии была названа кэш-памятью.

Идея использования кэш-памяти Идея двухуровневой памяти была предложено М. Уилксом в 1965 году в процессе разработки ВМ Atlas. Между ОП и процессором размещается небольшая, но быстродействующая буферная память, которая в последствии была названа кэш-памятью.

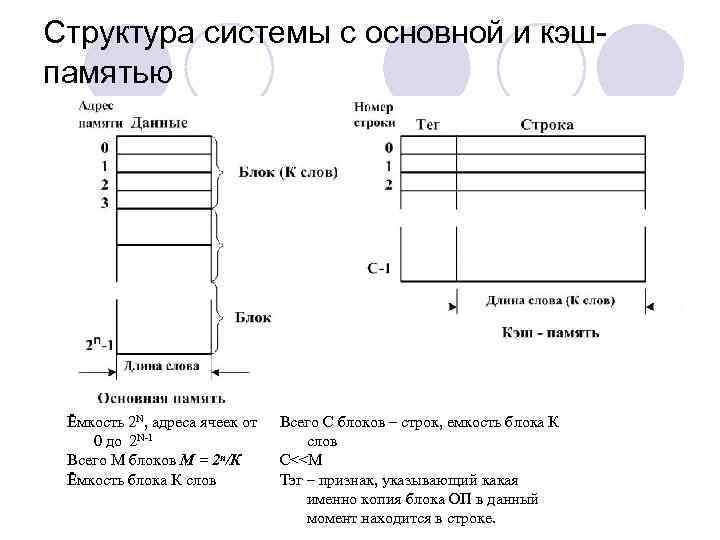

Структура системы с основной и кэшпамятью Ёмкость 2 N, адреса ячеек от 0 до 2 N-1 Всего М блоков М = 2 n/К Ёмкость блока К слов Всего С блоков – строк, емкость блока К слов С<

Структура системы с основной и кэшпамятью Ёмкость 2 N, адреса ячеек от 0 до 2 N-1 Всего М блоков М = 2 n/К Ёмкость блока К слов Всего С блоков – строк, емкость блока К слов С<

ЕМКОСТЬ КЭШ-ПАМЯТИ Выбор емкости кэш-памяти — это всегда определенный компромисс. Реальная эффективность использования кэш-памяти зависит от характера решаемых задач, и невозможно заранее определить, какая ее емкость будет действительно оптимальной.

ЕМКОСТЬ КЭШ-ПАМЯТИ Выбор емкости кэш-памяти — это всегда определенный компромисс. Реальная эффективность использования кэш-памяти зависит от характера решаемых задач, и невозможно заранее определить, какая ее емкость будет действительно оптимальной.

РАЗМЕР СТРОКИ Исследования показывают, что наиболее близким к оптимальному можно признать размер строки равный 4 -8 адресуемым единицам (словам или байтам). На практике размер строки обычно выбирают равным ширине шины данных, связывающей кэш-память с основной памятью.

РАЗМЕР СТРОКИ Исследования показывают, что наиболее близким к оптимальному можно признать размер строки равный 4 -8 адресуемым единицам (словам или байтам). На практике размер строки обычно выбирают равным ширине шины данных, связывающей кэш-память с основной памятью.

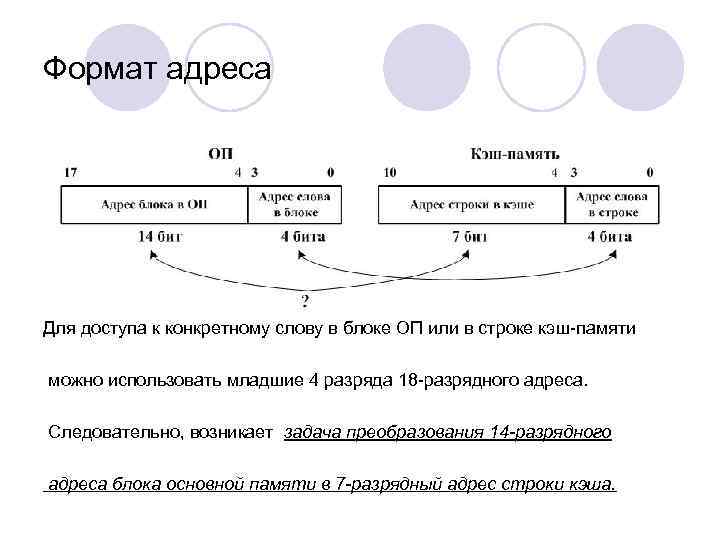

Формат адреса Для доступа к конкретному слову в блоке ОП или в строке кэш-памяти можно использовать младшие 4 разряда 18 -разрядного адреса. Следовательно, возникает задача преобразования 14 -разрядного адреса блока основной памяти в 7 -разрядный адрес строки кэша.

Формат адреса Для доступа к конкретному слову в блоке ОП или в строке кэш-памяти можно использовать младшие 4 разряда 18 -разрядного адреса. Следовательно, возникает задача преобразования 14 -разрядного адреса блока основной памяти в 7 -разрядный адрес строки кэша.

СПОСОБЫ ОТОБРАЖЕНИЯ ОПЕРАТИВНОЙ ПАМЯТИ НА КЭШПАМЯТЬ Наиболее известны три варианта отображения основной памяти на кэшпамять: ¡ прямой; ¡ полностью ассоциативный; частично-ассоциативный, который имеет две модификации — множественно-ассоциативное отображение и отображение секторов. ¡

СПОСОБЫ ОТОБРАЖЕНИЯ ОПЕРАТИВНОЙ ПАМЯТИ НА КЭШПАМЯТЬ Наиболее известны три варианта отображения основной памяти на кэшпамять: ¡ прямой; ¡ полностью ассоциативный; частично-ассоциативный, который имеет две модификации — множественно-ассоциативное отображение и отображение секторов. ¡

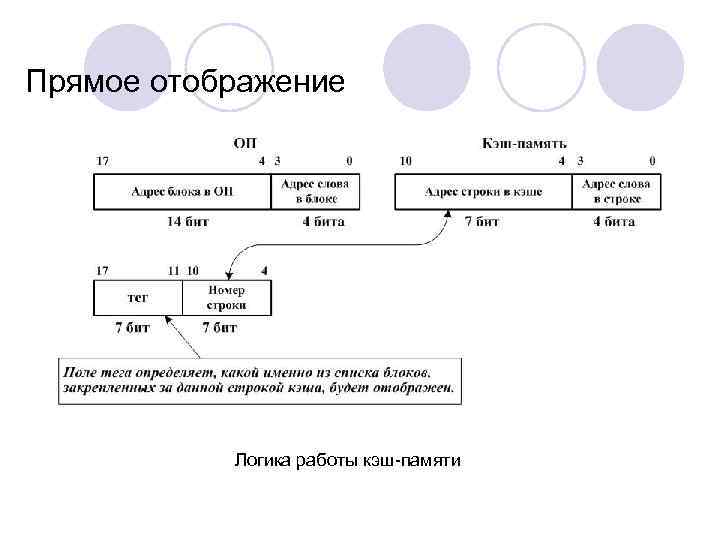

Прямое отображение Логика работы кэш-памяти

Прямое отображение Логика работы кэш-памяти

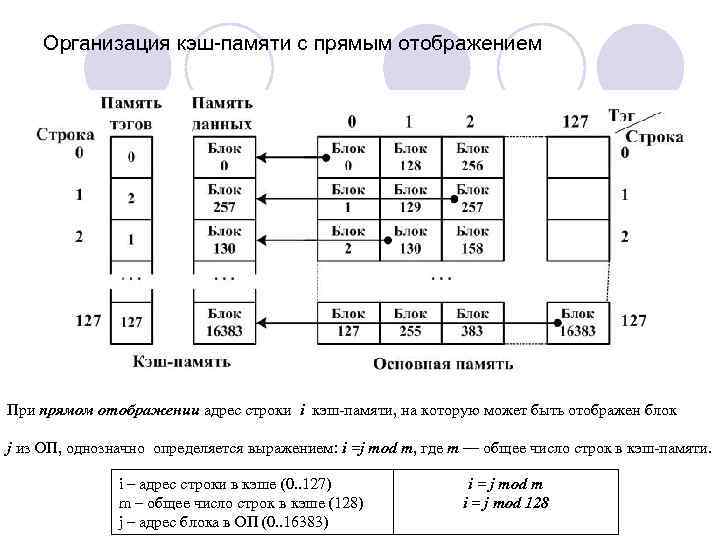

Организация кэш-памяти с прямым отображением При прямом отображении адрес строки i кэш-памяти, на которую может быть отображен блок j из ОП, однозначно определяется выражением: i =j mod т, где т — общее число строк в кэш-памяти. i – адрес строки в кэше (0. . 127) m – общее число строк в кэше (128) j – адрес блока в ОП (0. . 16383) i = j mod m i = j mod 128

Организация кэш-памяти с прямым отображением При прямом отображении адрес строки i кэш-памяти, на которую может быть отображен блок j из ОП, однозначно определяется выражением: i =j mod т, где т — общее число строк в кэш-памяти. i – адрес строки в кэше (0. . 127) m – общее число строк в кэше (128) j – адрес блока в ОП (0. . 16383) i = j mod m i = j mod 128

Полностью ассоциативное отображение Логика работы кэш-памяти

Полностью ассоциативное отображение Логика работы кэш-памяти

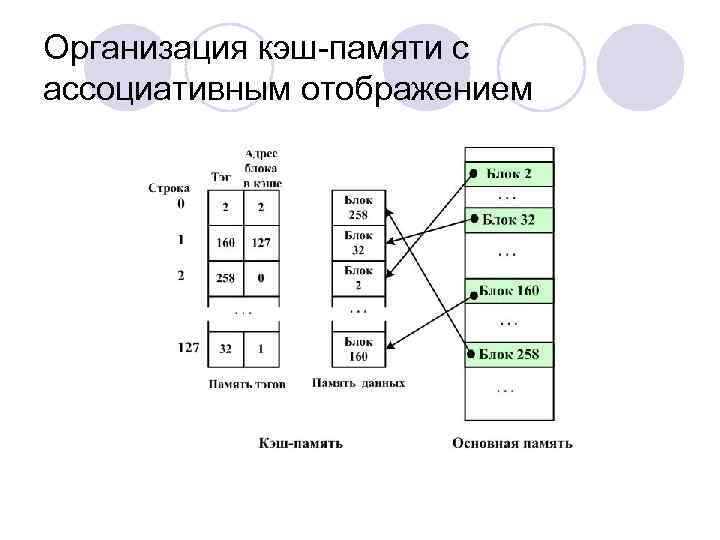

Организация кэш-памяти с ассоциативным отображением

Организация кэш-памяти с ассоциативным отображением

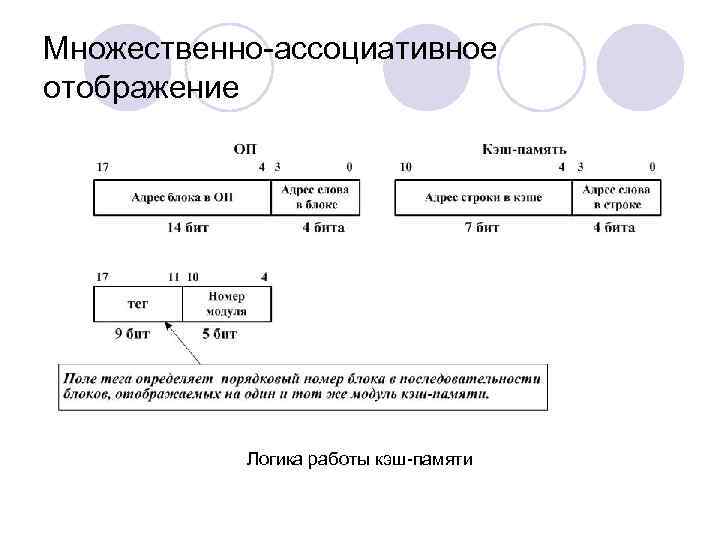

Множественно-ассоциативное отображение Логика работы кэш-памяти

Множественно-ассоциативное отображение Логика работы кэш-памяти

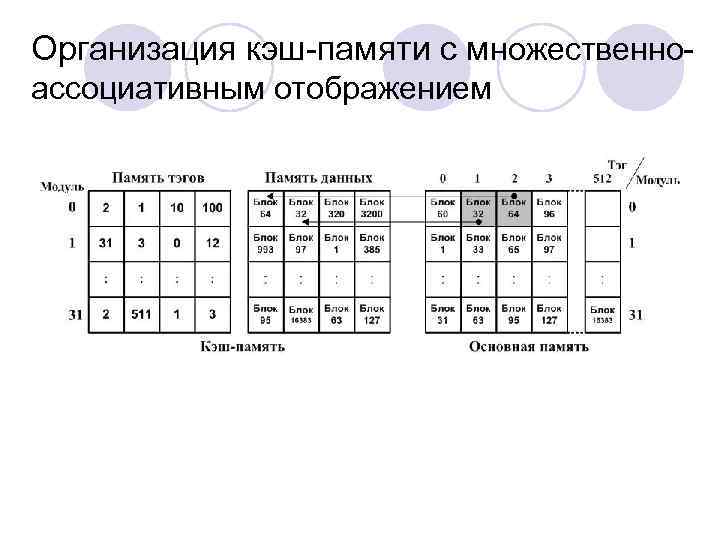

Организация кэш-памяти с множественноассоциативным отображением

Организация кэш-памяти с множественноассоциативным отображением

АЛГОРИТМЫ ЗАМЕЩЕНИЯ ИНФОРМАЦИИ В ЗАПОЛНЕННОЙ КЭШ-ПАМЯТИ Наиболее распространенными являются четыре алгоритма: Наиболее эффективным является алгоритм LRU (Least Recently Used), Другой алгоритм замещения работающий по принципу FIFO (First In First Out – «первый вошел, первый вышел» ), Замена наименее часто использовавшейся строки (LFU – Least Frequently Used), Замещаемая строка выбирается случайным образом – RAND.

АЛГОРИТМЫ ЗАМЕЩЕНИЯ ИНФОРМАЦИИ В ЗАПОЛНЕННОЙ КЭШ-ПАМЯТИ Наиболее распространенными являются четыре алгоритма: Наиболее эффективным является алгоритм LRU (Least Recently Used), Другой алгоритм замещения работающий по принципу FIFO (First In First Out – «первый вошел, первый вышел» ), Замена наименее часто использовавшейся строки (LFU – Least Frequently Used), Замещаемая строка выбирается случайным образом – RAND.

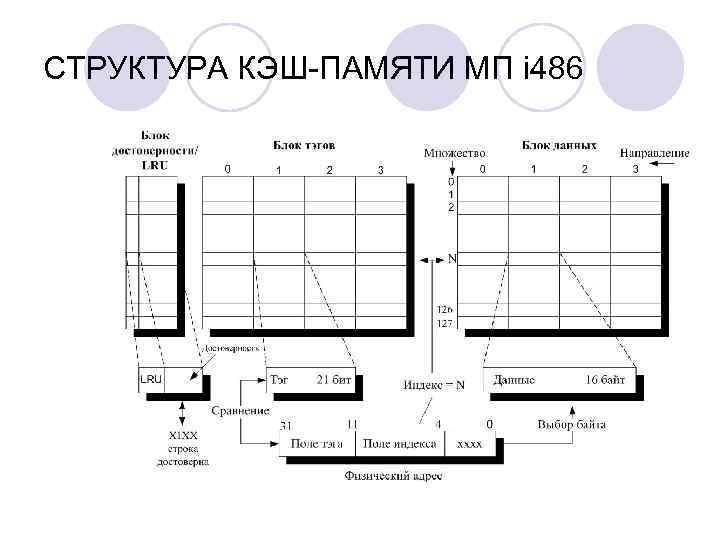

СТРУКТУРА КЭШ-ПАМЯТИ МП i 486

СТРУКТУРА КЭШ-ПАМЯТИ МП i 486

Современная кэш-память Процессор Intel® Pentium® III (256 KБ кэш-памяти L 2): Процессор Intel® Pentium® III содержит две независые кэш-памяти L 1 объемом по 16 КБ(32 KБ (16 KБ/16 KБ) неблокируемая кэш-память L 1). Одна для инструкций, другая для данных. Кэш-память L 1 ускоряет доступ к недавно использованным данным и командам, повышая тем самым общую производительность системы. Кэш-память с усовершенствованной передачей данных и технологией Advanced System Buffering, удовлетворяя более высоким потребностям в пропускной способности, предъявляемым современными серверными окружениями. 256 KБ L 2 кэш-память с усовершенствованной передачей данных (полноскоростная). Кэш-память полная 2 уровня с кодом коррекции ошибок (ECC) или версии, которая включает дискретный, работающей на половине частоты ядра корпус L 2 с ECC.

Современная кэш-память Процессор Intel® Pentium® III (256 KБ кэш-памяти L 2): Процессор Intel® Pentium® III содержит две независые кэш-памяти L 1 объемом по 16 КБ(32 KБ (16 KБ/16 KБ) неблокируемая кэш-память L 1). Одна для инструкций, другая для данных. Кэш-память L 1 ускоряет доступ к недавно использованным данным и командам, повышая тем самым общую производительность системы. Кэш-память с усовершенствованной передачей данных и технологией Advanced System Buffering, удовлетворяя более высоким потребностям в пропускной способности, предъявляемым современными серверными окружениями. 256 KБ L 2 кэш-память с усовершенствованной передачей данных (полноскоростная). Кэш-память полная 2 уровня с кодом коррекции ошибок (ECC) или версии, которая включает дискретный, работающей на половине частоты ядра корпус L 2 с ECC.

That’s all!

That’s all!