f756692945a433acc56df258967ef675.ppt

- Количество слайдов: 19

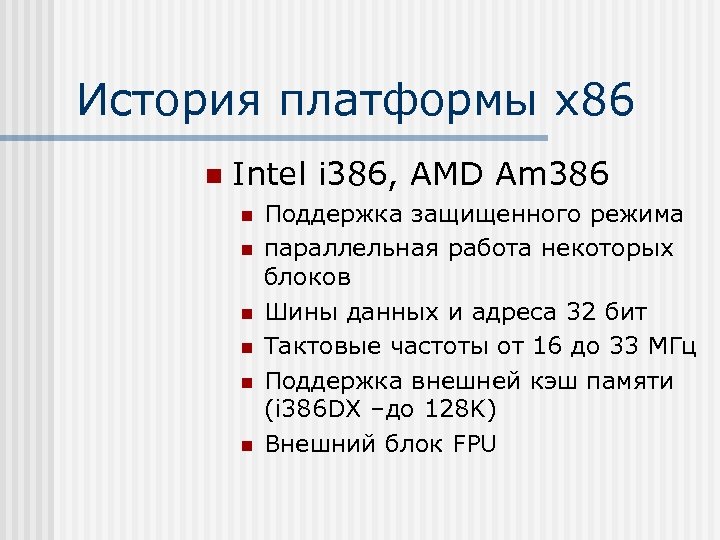

История платформы х86 n Intel i 386, AMD Am 386 n n n Поддержка защищенного режима параллельная работа некоторых блоков Шины данных и адреса 32 бит Тактовые частоты от 16 до 33 МГц Поддержка внешней кэш памяти (i 386 DX –до 128 K) Внешний блок FPU

История платформы х86 n Intel i 386, AMD Am 386 n n n Поддержка защищенного режима параллельная работа некоторых блоков Шины данных и адреса 32 бит Тактовые частоты от 16 до 33 МГц Поддержка внешней кэш памяти (i 386 DX –до 128 K) Внешний блок FPU

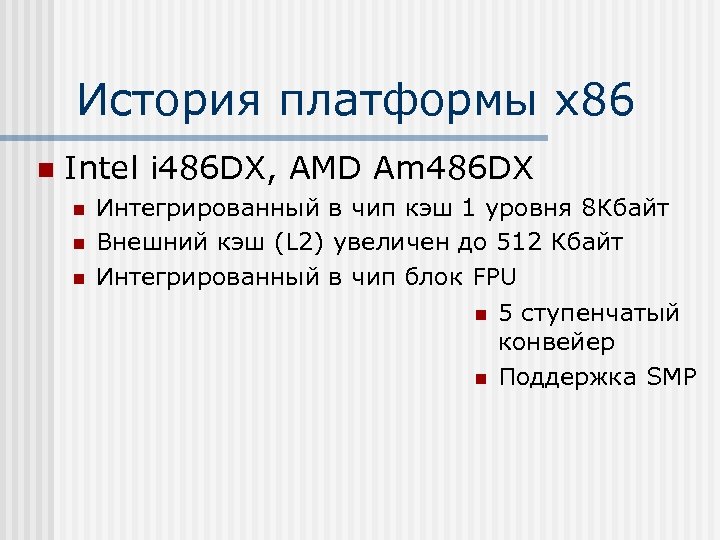

История платформы х86 n Intel i 486 DX, AMD Am 486 DX n n n Интегрированный в чип кэш 1 уровня 8 Кбайт Внешний кэш (L 2) увеличен до 512 Кбайт Интегрированный в чип блок FPU n n 5 ступенчатый конвейер Поддержка SMP

История платформы х86 n Intel i 486 DX, AMD Am 486 DX n n n Интегрированный в чип кэш 1 уровня 8 Кбайт Внешний кэш (L 2) увеличен до 512 Кбайт Интегрированный в чип блок FPU n n 5 ступенчатый конвейер Поддержка SMP

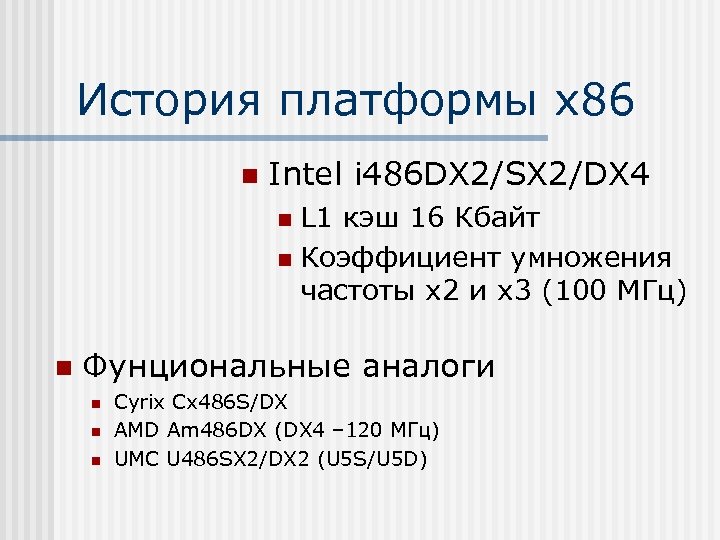

История платформы х86 n Intel i 486 DX 2/SX 2/DX 4 L 1 кэш 16 Кбайт n Коэффициент умножения частоты х2 и х3 (100 МГц) n n Фунциональные аналоги n n n Cyrix Cx 486 S/DX AMD Am 486 DX (DX 4 – 120 МГц) UMC U 486 SX 2/DX 2 (U 5 S/U 5 D)

История платформы х86 n Intel i 486 DX 2/SX 2/DX 4 L 1 кэш 16 Кбайт n Коэффициент умножения частоты х2 и х3 (100 МГц) n n Фунциональные аналоги n n n Cyrix Cx 486 S/DX AMD Am 486 DX (DX 4 – 120 МГц) UMC U 486 SX 2/DX 2 (U 5 S/U 5 D)

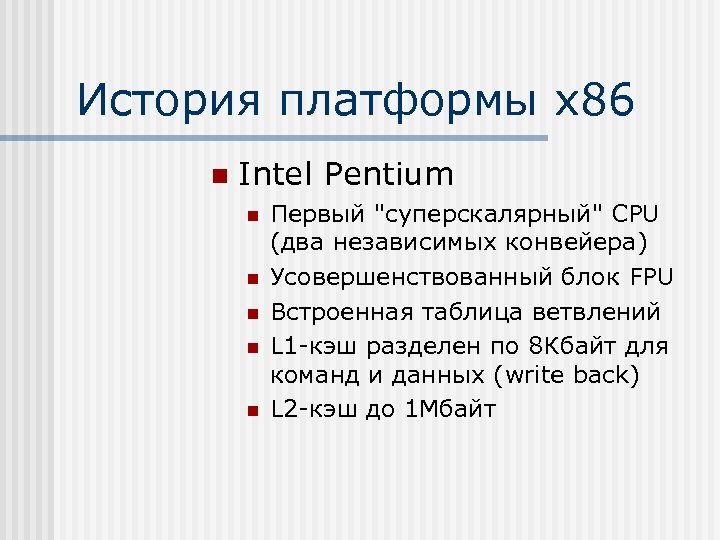

История платформы х86 n Intel Pentium n n n Первый "суперскалярный" CPU (два независимых конвейера) Усовершенствованный блок FPU Встроенная таблица ветвлений L 1 -кэш разделен по 8 Кбайт для команд и данных (write back) L 2 -кэш до 1 Мбайт

История платформы х86 n Intel Pentium n n n Первый "суперскалярный" CPU (два независимых конвейера) Усовершенствованный блок FPU Встроенная таблица ветвлений L 1 -кэш разделен по 8 Кбайт для команд и данных (write back) L 2 -кэш до 1 Мбайт

История платформы х86 n AMD Am 5 x 86, Cyrix 5 x 86 (M 1 SC) n Функциональные аналоги Pentium (устанавливались в платы с соединителем 486 процессоров) n Производительность ниже Pentium

История платформы х86 n AMD Am 5 x 86, Cyrix 5 x 86 (M 1 SC) n Функциональные аналоги Pentium (устанавливались в платы с соединителем 486 процессоров) n Производительность ниже Pentium

История платформы х86 n Intel Pentium Pro (P 6) n n n n Новая процессорная шина Внутренняя архитектура RISC 3 независимых конвейера Оптимизация по 32 бит код Разделенный L 2 -кэш от 256 К до 1 М в чипе Высокая стоимость Ядро процессора легло в основу Pentium II, Celeron, Pentium III

История платформы х86 n Intel Pentium Pro (P 6) n n n n Новая процессорная шина Внутренняя архитектура RISC 3 независимых конвейера Оптимизация по 32 бит код Разделенный L 2 -кэш от 256 К до 1 М в чипе Высокая стоимость Ядро процессора легло в основу Pentium II, Celeron, Pentium III

История платформы х86 n AMD K-5 n n Внутренняя архитектура RISC L 1 -кэш 24 К (16 К для кода и 8 для данных) Низкая производительность блока FPU Впервые AMD применена маркировка процессора в PR(Pentium Rating)

История платформы х86 n AMD K-5 n n Внутренняя архитектура RISC L 1 -кэш 24 К (16 К для кода и 8 для данных) Низкая производительность блока FPU Впервые AMD применена маркировка процессора в PR(Pentium Rating)

История платформы х86 n Intel Pentium MMX n n n Поддержка инструкций для работы с мультимедиа данными (MMX Multi. Media e. Xtensions) Разделенный L 1 -кэш 32 Ксущественно увеличилась производительность Различные напряжения питания ядра и ввода-вывода

История платформы х86 n Intel Pentium MMX n n n Поддержка инструкций для работы с мультимедиа данными (MMX Multi. Media e. Xtensions) Разделенный L 1 -кэш 32 Ксущественно увеличилась производительность Различные напряжения питания ядра и ввода-вывода

История платформы х86 n Cyrix 6 x 86(M 1) n n Общий L 1 -кэш 16 К Cyrix 6 x 86 MX/M-II n Поддержка ММХ

История платформы х86 n Cyrix 6 x 86(M 1) n n Общий L 1 -кэш 16 К Cyrix 6 x 86 MX/M-II n Поддержка ММХ

История платформы х86 n AMD-K 6 n n n AMD K 6 -2 n n Внутренняя архитектура RISC L 1 -кэш 64 К (32 код+32 данные) Частота до 300 МГц Поддержка ММХ Поддержка команд обработки 3 Dграфики (3 DNow!) AMD K 6 -III n L 2 -кэш 256 К на чипе и L 3 -кэш на плате

История платформы х86 n AMD-K 6 n n n AMD K 6 -2 n n Внутренняя архитектура RISC L 1 -кэш 64 К (32 код+32 данные) Частота до 300 МГц Поддержка ММХ Поддержка команд обработки 3 Dграфики (3 DNow!) AMD K 6 -III n L 2 -кэш 256 К на чипе и L 3 -кэш на плате

История платформы х86 n Centaur/IDT Win. Chip/Win. Chip 2 n n n Низкое потребление Поддержка ММХ Послужили основой при разработки процессора компании VIA Cyrix III

История платформы х86 n Centaur/IDT Win. Chip/Win. Chip 2 n n n Низкое потребление Поддержка ММХ Послужили основой при разработки процессора компании VIA Cyrix III

История платформы х86 n Rise m. P 6 n n Низкое потребление 2 конвейера для операций с плавающей точкой 3 блока исполнения MMXинструкций исполнение трех целочисленных инструкций за такт

История платформы х86 n Rise m. P 6 n n Низкое потребление 2 конвейера для операций с плавающей точкой 3 блока исполнения MMXинструкций исполнение трех целочисленных инструкций за такт

История платформы х86 n Pentium II n n n Процессор размещен вместе c L 2 кэш в SECС (Single Edge Contact cartrige) картридже L 2 кэш работает на частоте процессора Объединяет достоинства Pentium Pro и ММХ

История платформы х86 n Pentium II n n n Процессор размещен вместе c L 2 кэш в SECС (Single Edge Contact cartrige) картридже L 2 кэш работает на частоте процессора Объединяет достоинства Pentium Pro и ММХ

История платформы х86 n Celeron (266 -300 МГц) n n n Отсутствует пластмассовый корпус –только плата с чипом (SEPP -Single Edge Processor Packege) L 2 кэш отсутствует Celeron (300 А-466 МГц) n n L 2 кэш 128 Кбайт SEPP и PPGA (Socket 370)

История платформы х86 n Celeron (266 -300 МГц) n n n Отсутствует пластмассовый корпус –только плата с чипом (SEPP -Single Edge Processor Packege) L 2 кэш отсутствует Celeron (300 А-466 МГц) n n L 2 кэш 128 Кбайт SEPP и PPGA (Socket 370)

История платформы х86 n Celeron Tualatin -1, 4 ГГц) n n L 2 кэш 256 Кбайт PPGA 2 (Socket 370) (1, 2

История платформы х86 n Celeron Tualatin -1, 4 ГГц) n n L 2 кэш 256 Кбайт PPGA 2 (Socket 370) (1, 2

История платформы х86 n Pentium III n n n Добавлен набор инструкций SSE (Streaming SIMD Extensions) Корпус SECC /SECC 2 Pentium III в корпусе FC PGA n n 533 МГц-1400 МГц L 2 кэш 256 Кбайт

История платформы х86 n Pentium III n n n Добавлен набор инструкций SSE (Streaming SIMD Extensions) Корпус SECC /SECC 2 Pentium III в корпусе FC PGA n n 533 МГц-1400 МГц L 2 кэш 256 Кбайт

История платформы х86 n Celeron Tualatin -1, 4 ГГц) n n L 2 кэш 256 Кбайт PPGA 2 (Socket 370) (1, 2

История платформы х86 n Celeron Tualatin -1, 4 ГГц) n n L 2 кэш 256 Кбайт PPGA 2 (Socket 370) (1, 2

История платформы х86 n Pentium 4 (0, 18) n n 1, 4 -2, 0 ГГц Quad Pumped Bus 400 L 2 кэш 256 Кбайт Socket 423/478

История платформы х86 n Pentium 4 (0, 18) n n 1, 4 -2, 0 ГГц Quad Pumped Bus 400 L 2 кэш 256 Кбайт Socket 423/478

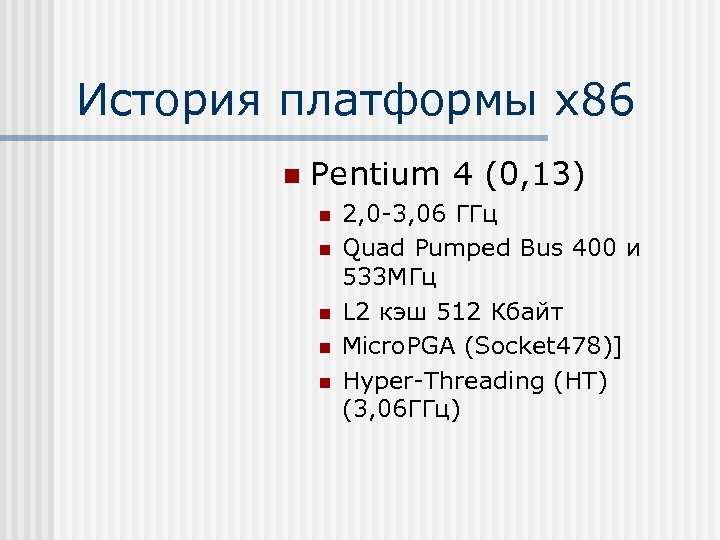

История платформы х86 n Pentium 4 (0, 13) n n n 2, 0 -3, 06 ГГц Quad Pumped Bus 400 и 533 МГц L 2 кэш 512 Кбайт Micro. PGA (Socket 478)] Hyper-Threading (HT) (3, 06 ГГц)

История платформы х86 n Pentium 4 (0, 13) n n n 2, 0 -3, 06 ГГц Quad Pumped Bus 400 и 533 МГц L 2 кэш 512 Кбайт Micro. PGA (Socket 478)] Hyper-Threading (HT) (3, 06 ГГц)