64c6ecc6c36528e5c87a764379ffb536.ppt

- Количество слайдов: 62

Issues in the Design of Wires Avinoam Kolodny Technion – Israel Institute of Technology Intel PVPD Symposium July 2006 1 1

Issues in the Design of Wires Avinoam Kolodny Technion – Israel Institute of Technology Intel PVPD Symposium July 2006 1 1

Thanks to my students and collaborators Anastasia Barger Shay Michaely Konstantin Moiseev Nir Magen Michael Moreinis Arkadiy morgenshtein David Goren Shmuel Wimer Uri Weiser Nachum Shamir Israel Wagner Ran Ginosar Eby Friedman 2 2

Thanks to my students and collaborators Anastasia Barger Shay Michaely Konstantin Moiseev Nir Magen Michael Moreinis Arkadiy morgenshtein David Goren Shmuel Wimer Uri Weiser Nachum Shamir Israel Wagner Ran Ginosar Eby Friedman 2 2

Connectivity and Complexity 3 3

Connectivity and Complexity 3 3

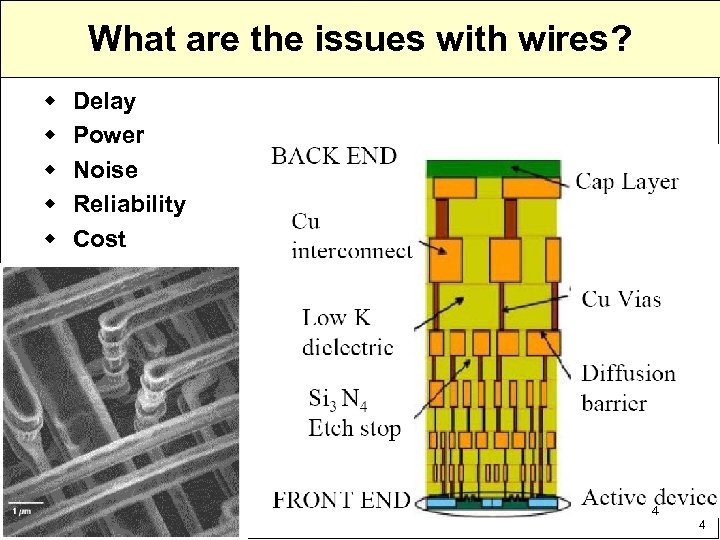

What are the issues with wires? w w w Delay Power Noise Reliability Cost 4 4

What are the issues with wires? w w w Delay Power Noise Reliability Cost 4 4

Scope of this talk w Interconnect delay w Interconnect Power 5 5

Scope of this talk w Interconnect delay w Interconnect Power 5 5

Sizing and spacing of uniform bus wires 6 6

Sizing and spacing of uniform bus wires 6 6

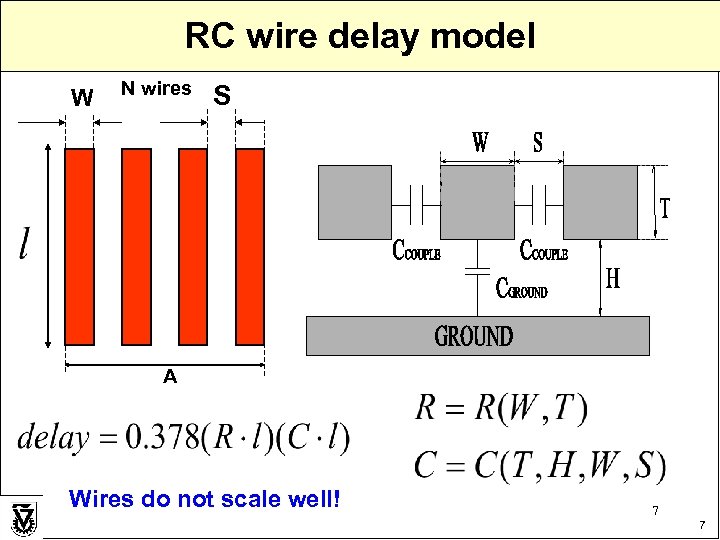

RC wire delay model W N wires S A Wires do not scale well! 7 7

RC wire delay model W N wires S A Wires do not scale well! 7 7

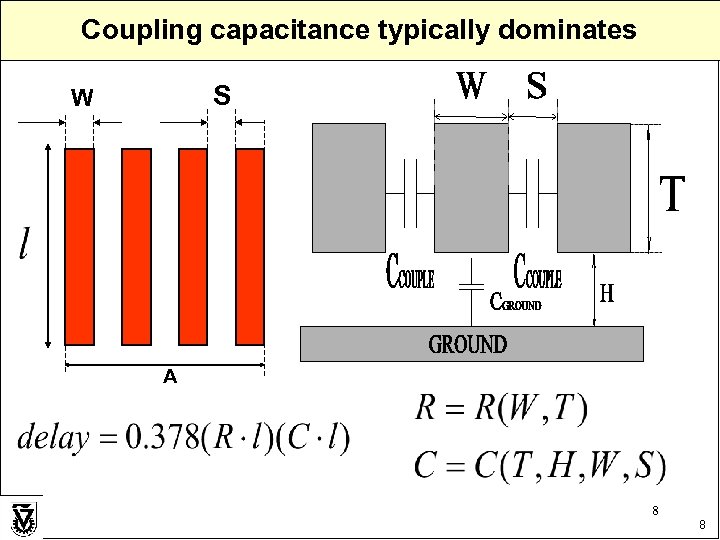

Coupling capacitance typically dominates S W A 8 8

Coupling capacitance typically dominates S W A 8 8

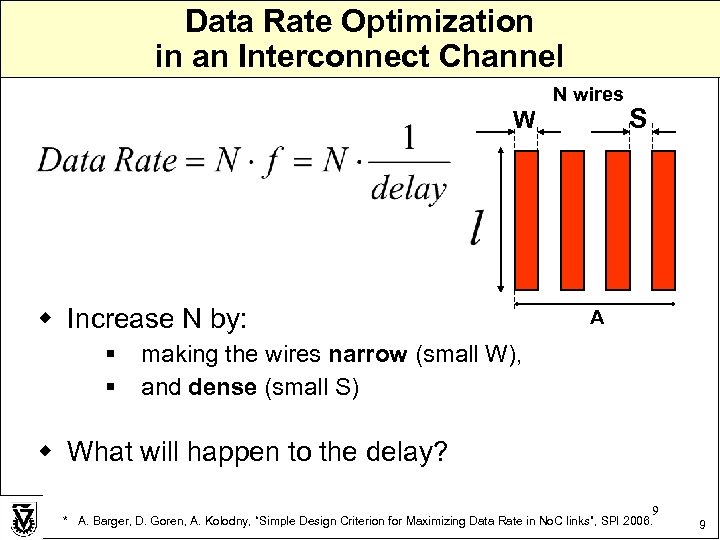

Data Rate Optimization in an Interconnect Channel N wires W w Increase N by: S A § making the wires narrow (small W), § and dense (small S) w What will happen to the delay? 9 * A. Barger, D. Goren, A. Kolodny, “Simple Design Criterion for Maximizing Data Rate in No. C links”, SPI 2006. 9

Data Rate Optimization in an Interconnect Channel N wires W w Increase N by: S A § making the wires narrow (small W), § and dense (small S) w What will happen to the delay? 9 * A. Barger, D. Goren, A. Kolodny, “Simple Design Criterion for Maximizing Data Rate in No. C links”, SPI 2006. 9

![Data Rate vs. Wire Width (W) and Spacing (S) Rough Approximation: S [ m] Data Rate vs. Wire Width (W) and Spacing (S) Rough Approximation: S [ m]](https://present5.com/presentation/64c6ecc6c36528e5c87a764379ffb536/image-10.jpg) Data Rate vs. Wire Width (W) and Spacing (S) Rough Approximation: S [ m] T=1 m, H=1 m, A=60 m, l=2 mm. W [ m] 10 10

Data Rate vs. Wire Width (W) and Spacing (S) Rough Approximation: S [ m] T=1 m, H=1 m, A=60 m, l=2 mm. W [ m] 10 10

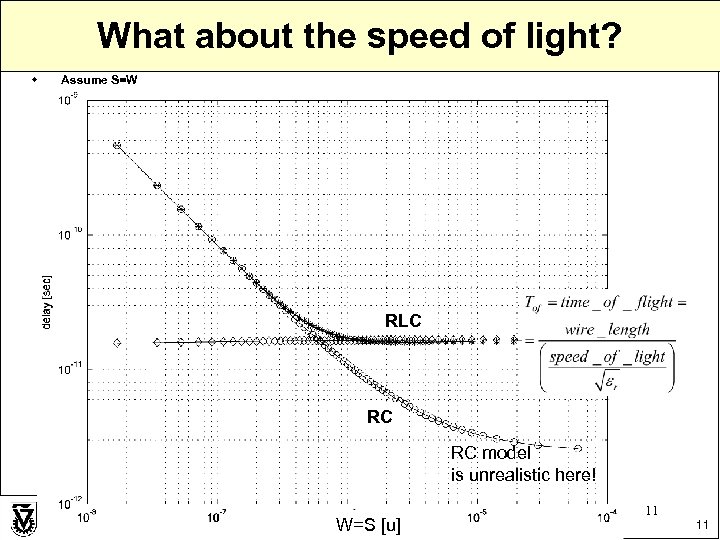

What about the speed of light? w Assume S=W RLC RC RC model is unrealistic here! W=S [u] 11 11

What about the speed of light? w Assume S=W RLC RC RC model is unrealistic here! W=S [u] 11 11

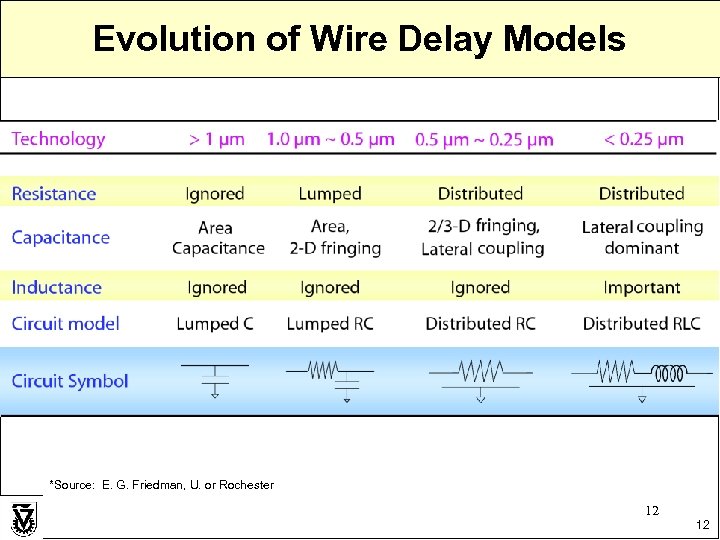

Evolution of Wire Delay Models *Source: E. G. Friedman, U. or Rochester 12 12

Evolution of Wire Delay Models *Source: E. G. Friedman, U. or Rochester 12 12

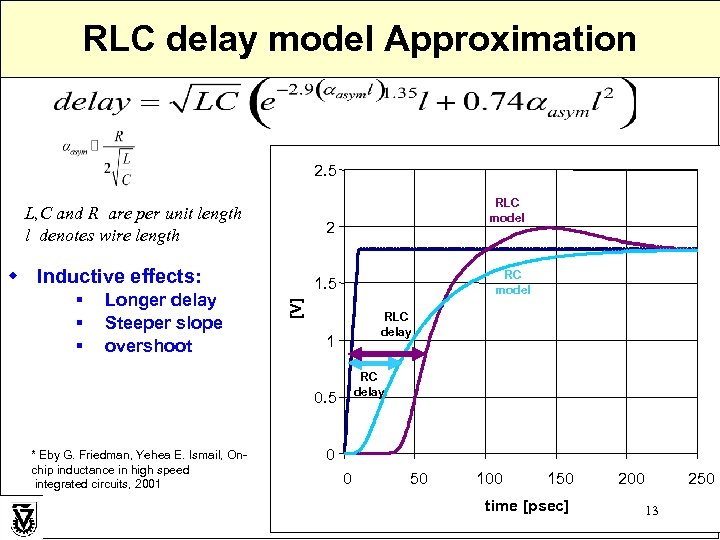

RLC delay model Approximation 2. 5 L, C and R are per unit length l denotes wire length 2 w Inductive effects: Longer delay Steeper slope overshoot RC model 1. 5 [V] § § § RLC model RLC delay 1 RC delay 0. 5 * Eby G. Friedman, Yehea E. Ismail, Onchip inductance in high speed integrated circuits, 2001 0 0 50 100 150 time [psec] 200 250 13 13

RLC delay model Approximation 2. 5 L, C and R are per unit length l denotes wire length 2 w Inductive effects: Longer delay Steeper slope overshoot RC model 1. 5 [V] § § § RLC model RLC delay 1 RC delay 0. 5 * Eby G. Friedman, Yehea E. Ismail, Onchip inductance in high speed integrated circuits, 2001 0 0 50 100 150 time [psec] 200 250 13 13

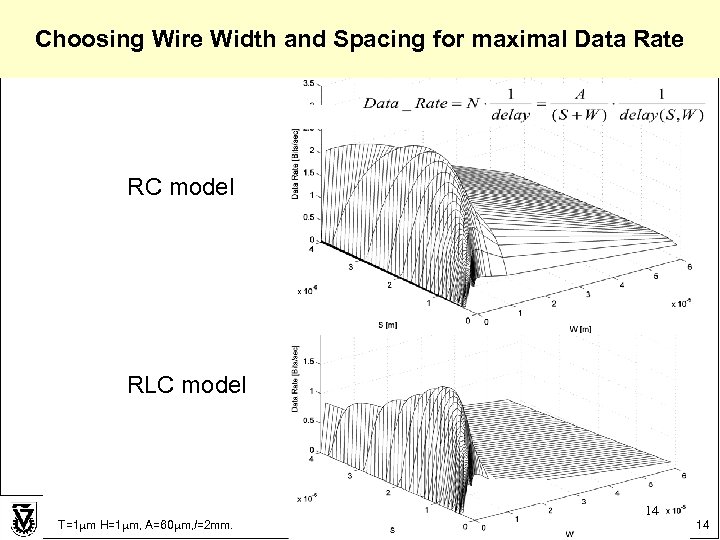

Choosing Wire Width and Spacing for maximal Data Rate RC model RLC model T=1 m H=1 m, A=60 m, l=2 mm. 14 14

Choosing Wire Width and Spacing for maximal Data Rate RC model RLC model T=1 m H=1 m, A=60 m, l=2 mm. 14 14

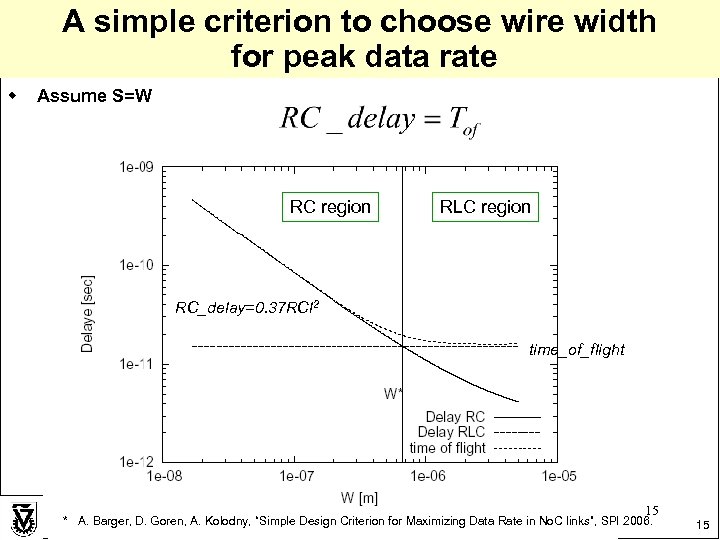

A simple criterion to choose wire width for peak data rate w Assume S=W RC region RLC region RC_delay=0. 37 RCl 2 time_of_flight 15 * A. Barger, D. Goren, A. Kolodny, “Simple Design Criterion for Maximizing Data Rate in No. C links”, SPI 2006. 15

A simple criterion to choose wire width for peak data rate w Assume S=W RC region RLC region RC_delay=0. 37 RCl 2 time_of_flight 15 * A. Barger, D. Goren, A. Kolodny, “Simple Design Criterion for Maximizing Data Rate in No. C links”, SPI 2006. 15

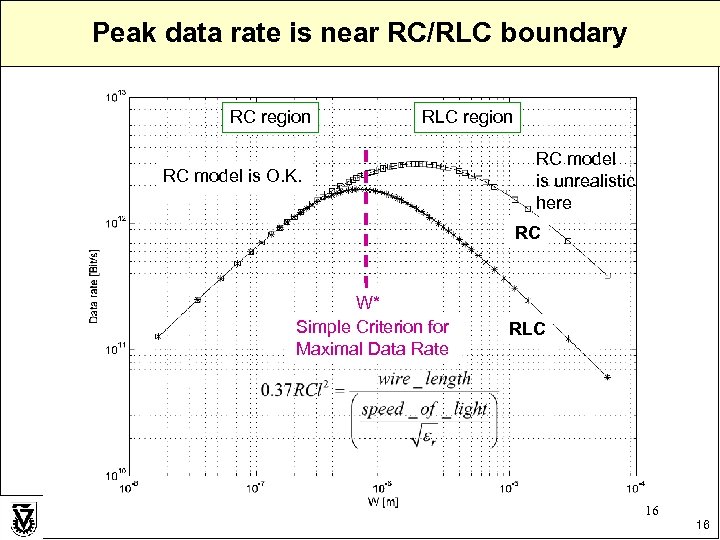

Peak data rate is near RC/RLC boundary RC region RLC region RC model is O. K. RC model is unrealistic here RC W* Simple Criterion for Maximal Data Rate RLC 16 16

Peak data rate is near RC/RLC boundary RC region RLC region RC model is O. K. RC model is unrealistic here RC W* Simple Criterion for Maximal Data Rate RLC 16 16

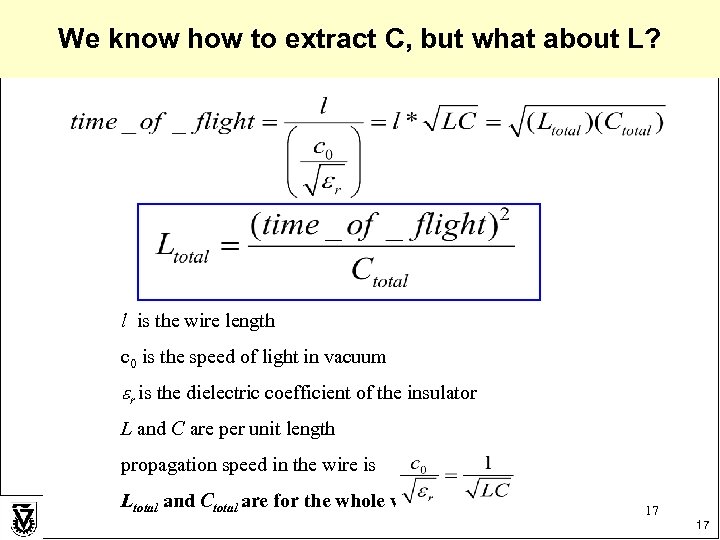

We know how to extract C, but what about L? l is the wire length c 0 is the speed of light in vacuum r is the dielectric coefficient of the insulator L and C are per unit length propagation speed in the wire is Ltotal and Ctotal are for the whole wire 17 17

We know how to extract C, but what about L? l is the wire length c 0 is the speed of light in vacuum r is the dielectric coefficient of the insulator L and C are per unit length propagation speed in the wire is Ltotal and Ctotal are for the whole wire 17 17

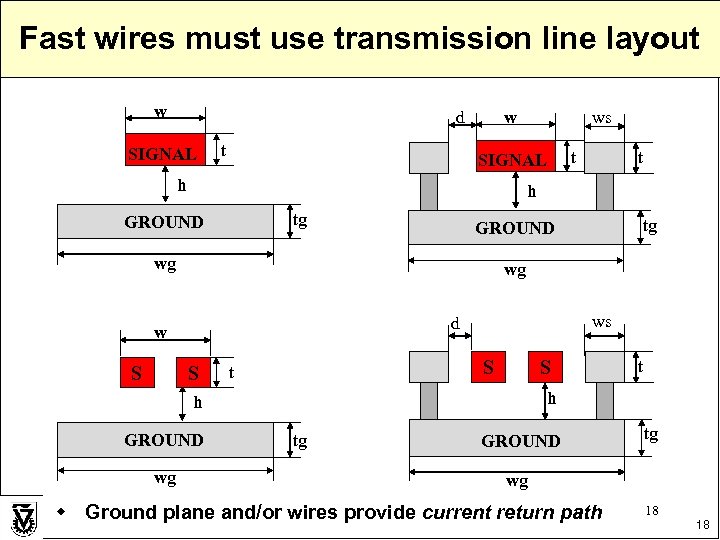

Fast wires must use transmission line layout w d SIGNAL t SIGNAL h tg t tg GROUND wg wg ws d w S S t S GROUND t h h wg t h GROUND S ws w tg GROUND tg wg w Ground plane and/or wires provide current return path 18 18

Fast wires must use transmission line layout w d SIGNAL t SIGNAL h tg t tg GROUND wg wg ws d w S S t S GROUND t h h wg t h GROUND S ws w tg GROUND tg wg w Ground plane and/or wires provide current return path 18 18

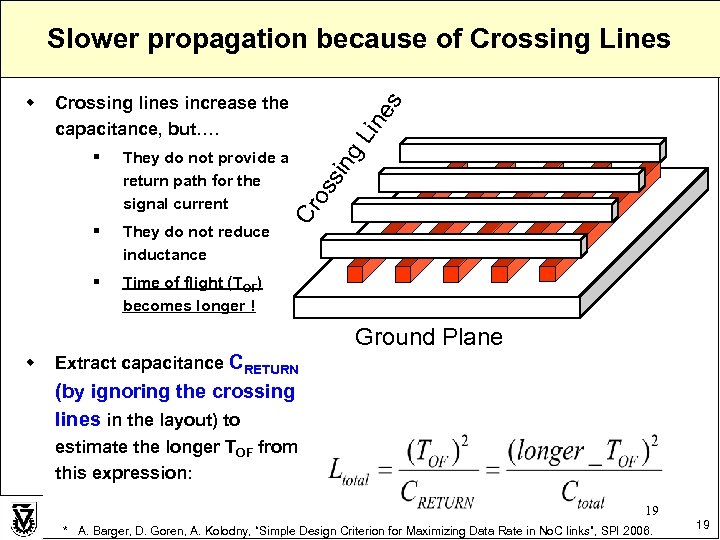

Slower propagation because of Crossing Lines They do not reduce inductance § g § Time of flight (TOF) becomes longer ! sin They do not provide a return path for the signal current Cr § Lin es Crossing lines increase the capacitance, but…. os w Ground Plane w Extract capacitance CRETURN (by ignoring the crossing lines in the layout) to estimate the longer TOF from this expression: 19 * A. Barger, D. Goren, A. Kolodny, “Simple Design Criterion for Maximizing Data Rate in No. C links”, SPI 2006. 19

Slower propagation because of Crossing Lines They do not reduce inductance § g § Time of flight (TOF) becomes longer ! sin They do not provide a return path for the signal current Cr § Lin es Crossing lines increase the capacitance, but…. os w Ground Plane w Extract capacitance CRETURN (by ignoring the crossing lines in the layout) to estimate the longer TOF from this expression: 19 * A. Barger, D. Goren, A. Kolodny, “Simple Design Criterion for Maximizing Data Rate in No. C links”, SPI 2006. 19

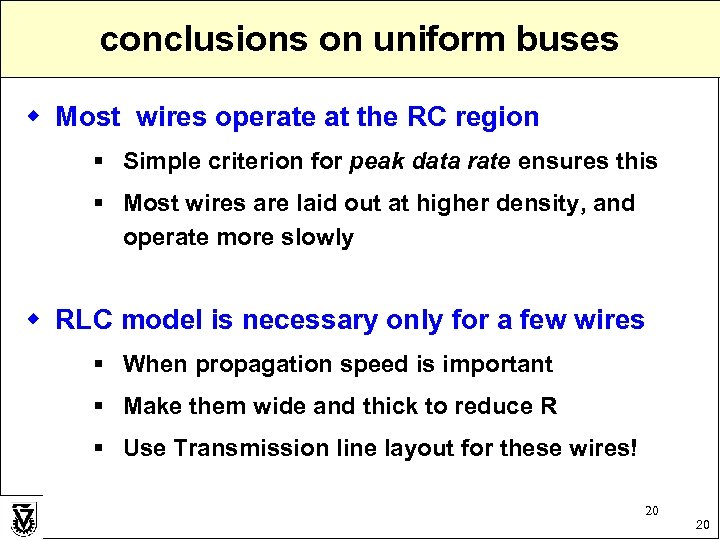

conclusions on uniform buses w Most wires operate at the RC region § Simple criterion for peak data rate ensures this § Most wires are laid out at higher density, and operate more slowly w RLC model is necessary only for a few wires § When propagation speed is important § Make them wide and thick to reduce R § Use Transmission line layout for these wires! 20 20

conclusions on uniform buses w Most wires operate at the RC region § Simple criterion for peak data rate ensures this § Most wires are laid out at higher density, and operate more slowly w RLC model is necessary only for a few wires § When propagation speed is important § Make them wide and thick to reduce R § Use Transmission line layout for these wires! 20 20

Sizing and spacing of individual wires in interconnect channels 21 21

Sizing and spacing of individual wires in interconnect channels 21 21

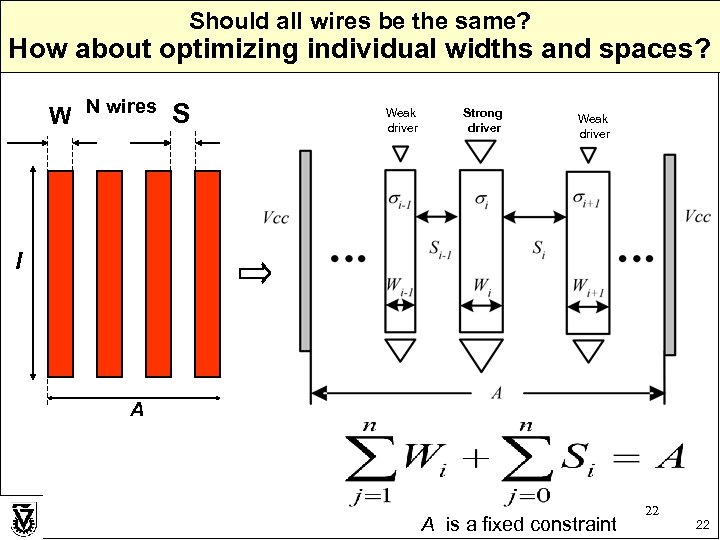

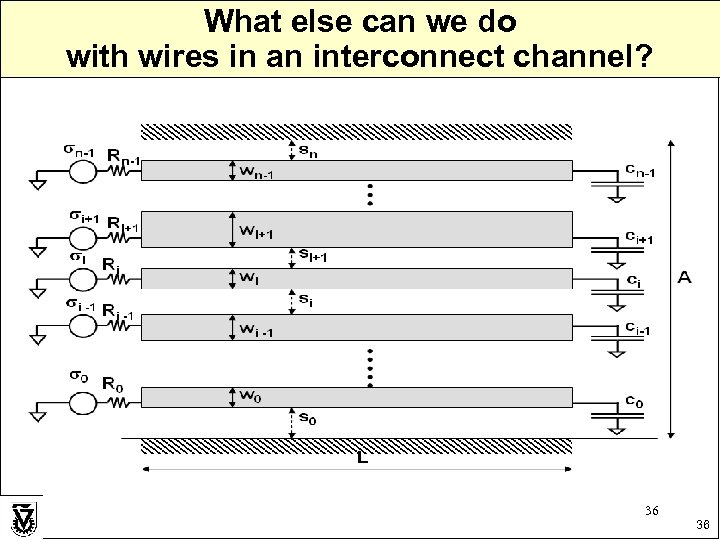

Should all wires be the same? How about optimizing individual widths and spaces? W N wires S Weak driver Strong driver Weak driver l A A is a fixed constraint 22 22

Should all wires be the same? How about optimizing individual widths and spaces? W N wires S Weak driver Strong driver Weak driver l A A is a fixed constraint 22 22

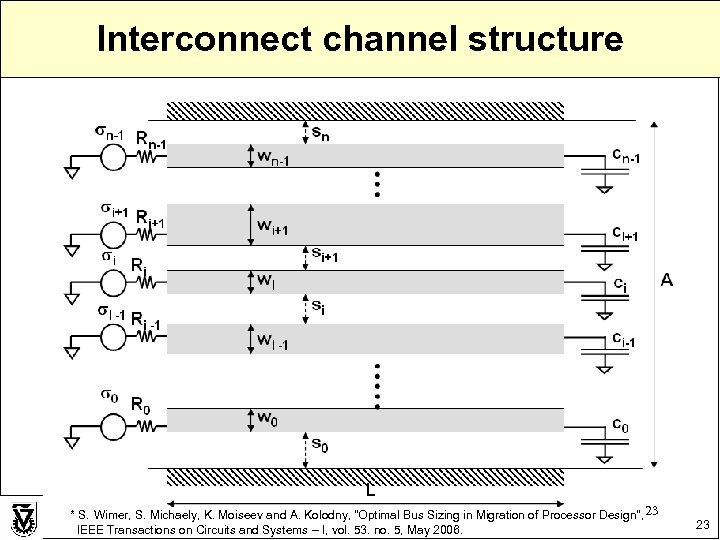

Interconnect channel structure * S. Wimer, S. Michaely, K. Moiseev and A. Kolodny, "Optimal Bus Sizing in Migration of Processor Design", 23 IEEE Transactions on Circuits and Systems – I, vol. 53. no. 5, May 2006. 23

Interconnect channel structure * S. Wimer, S. Michaely, K. Moiseev and A. Kolodny, "Optimal Bus Sizing in Migration of Processor Design", 23 IEEE Transactions on Circuits and Systems – I, vol. 53. no. 5, May 2006. 23

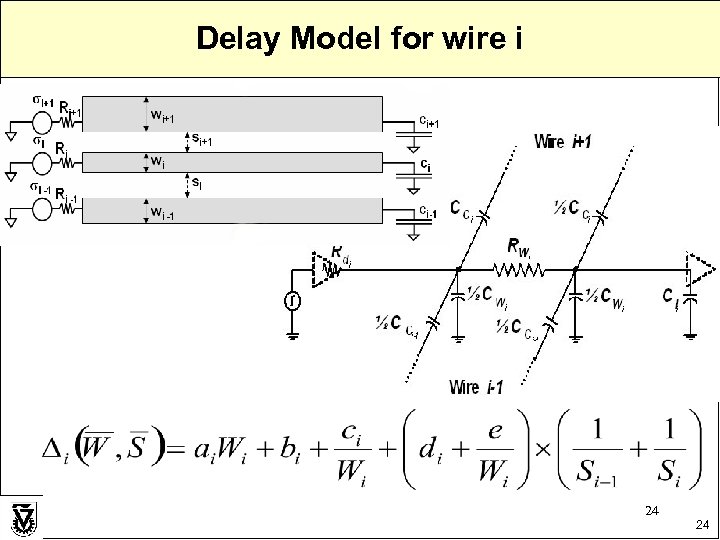

Delay Model for wire i 24 24

Delay Model for wire i 24 24

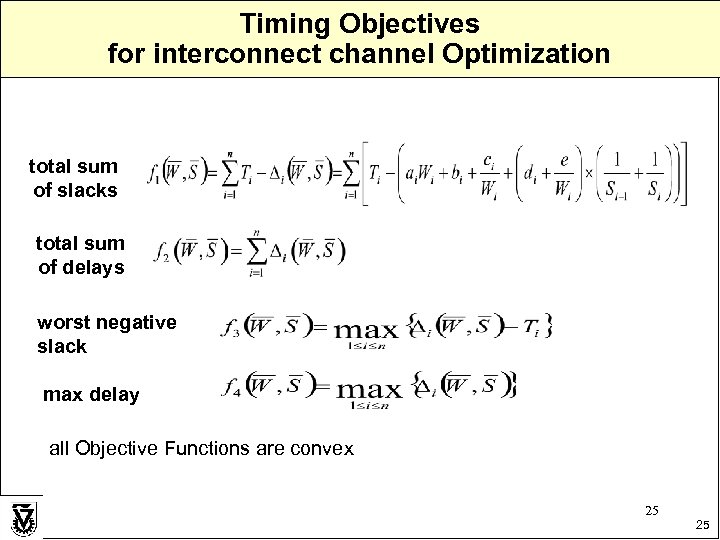

Timing Objectives for interconnect channel Optimization total sum of slacks total sum of delays worst negative slack max delay all Objective Functions are convex 25 25

Timing Objectives for interconnect channel Optimization total sum of slacks total sum of delays worst negative slack max delay all Objective Functions are convex 25 25

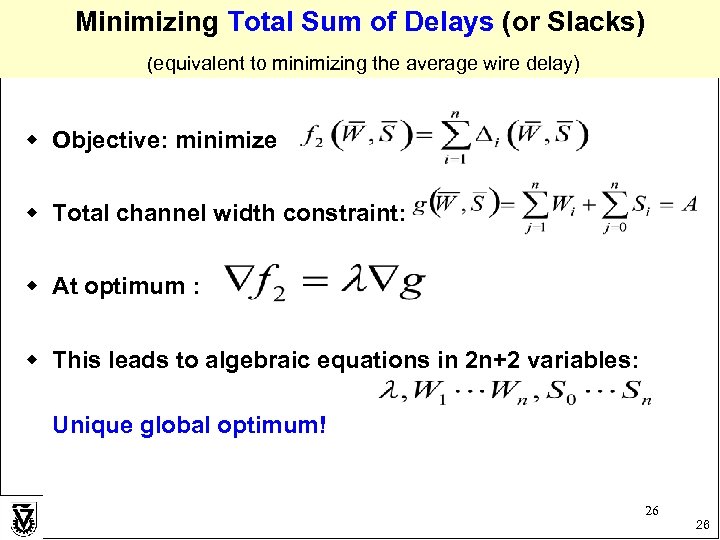

Minimizing Total Sum of Delays (or Slacks) (equivalent to minimizing the average wire delay) w Objective: minimize w Total channel width constraint: w At optimum : w This leads to algebraic equations in 2 n+2 variables: Unique global optimum! 26 26

Minimizing Total Sum of Delays (or Slacks) (equivalent to minimizing the average wire delay) w Objective: minimize w Total channel width constraint: w At optimum : w This leads to algebraic equations in 2 n+2 variables: Unique global optimum! 26 26

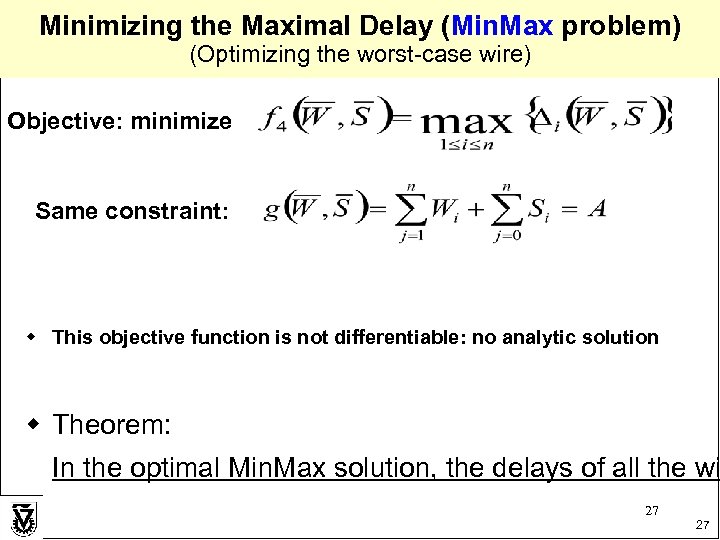

Minimizing the Maximal Delay (Min. Max problem) (Optimizing the worst-case wire) Objective: minimize Same constraint: w This objective function is not differentiable: no analytic solution w Theorem: In the optimal Min. Max solution, the delays of all the wi 27 27

Minimizing the Maximal Delay (Min. Max problem) (Optimizing the worst-case wire) Objective: minimize Same constraint: w This objective function is not differentiable: no analytic solution w Theorem: In the optimal Min. Max solution, the delays of all the wi 27 27

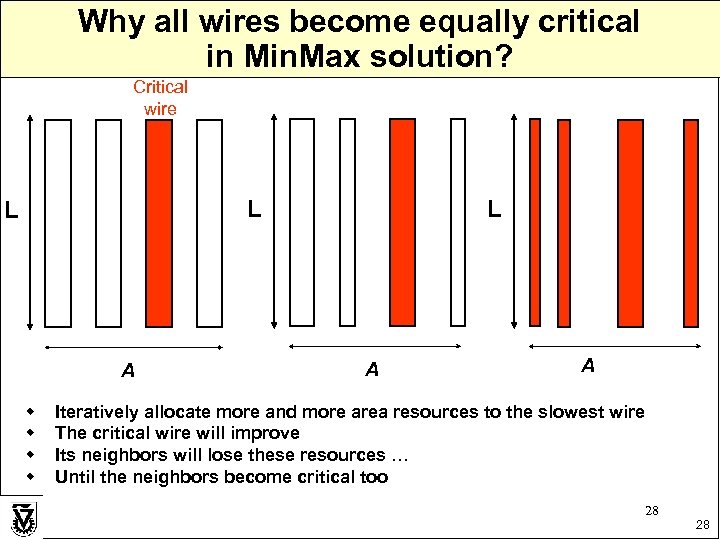

Why all wires become equally critical in Min. Max solution? Critical wire L L A w w L A A Iteratively allocate more and more area resources to the slowest wire The critical wire will improve Its neighbors will lose these resources … Until the neighbors become critical too 28 28

Why all wires become equally critical in Min. Max solution? Critical wire L L A w w L A A Iteratively allocate more and more area resources to the slowest wire The critical wire will improve Its neighbors will lose these resources … Until the neighbors become critical too 28 28

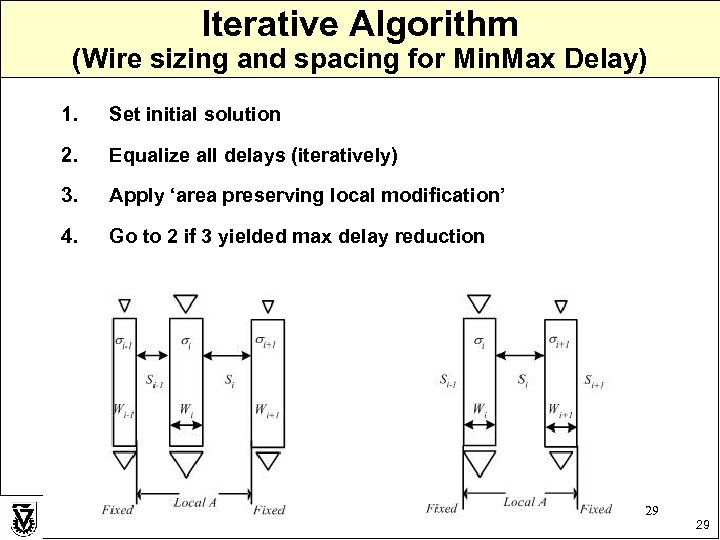

Iterative Algorithm (Wire sizing and spacing for Min. Max Delay) 1. Set initial solution 2. Equalize all delays (iteratively) 3. Apply ‘area preserving local modification’ 4. Go to 2 if 3 yielded max delay reduction 29 29

Iterative Algorithm (Wire sizing and spacing for Min. Max Delay) 1. Set initial solution 2. Equalize all delays (iteratively) 3. Apply ‘area preserving local modification’ 4. Go to 2 if 3 yielded max delay reduction 29 29

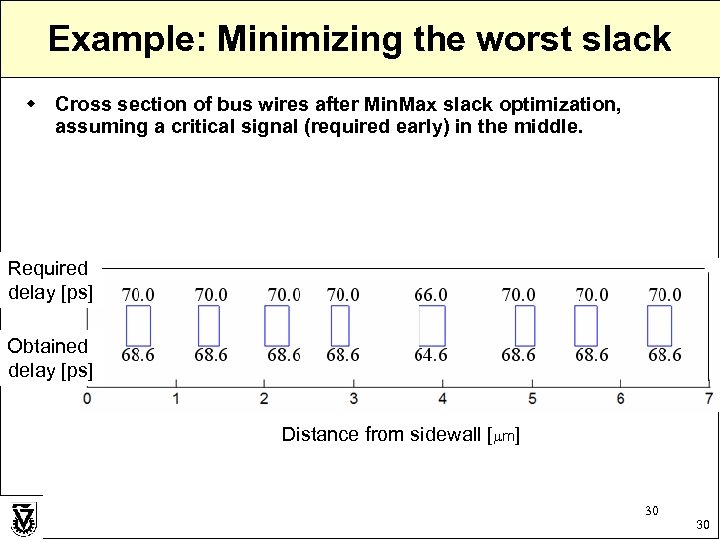

Example: Minimizing the worst slack w Cross section of bus wires after Min. Max slack optimization, assuming a critical signal (required early) in the middle. Required delay [ps] Obtained delay [ps] Distance from sidewall [ m] 30 30

Example: Minimizing the worst slack w Cross section of bus wires after Min. Max slack optimization, assuming a critical signal (required early) in the middle. Required delay [ps] Obtained delay [ps] Distance from sidewall [ m] 30 30

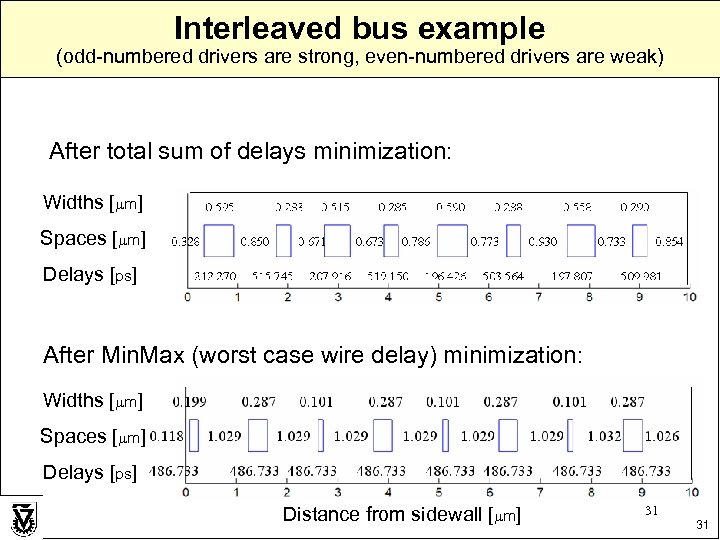

Interleaved bus example (odd-numbered drivers are strong, even-numbered drivers are weak) After total sum of delays minimization: Widths [ m] Spaces [ m] Delays [ps] After Min. Max (worst case wire delay) minimization: Widths [ m] Spaces [ m] Delays [ps] Distance from sidewall [ m] 31 31

Interleaved bus example (odd-numbered drivers are strong, even-numbered drivers are weak) After total sum of delays minimization: Widths [ m] Spaces [ m] Delays [ps] After Min. Max (worst case wire delay) minimization: Widths [ m] Spaces [ m] Delays [ps] Distance from sidewall [ m] 31 31

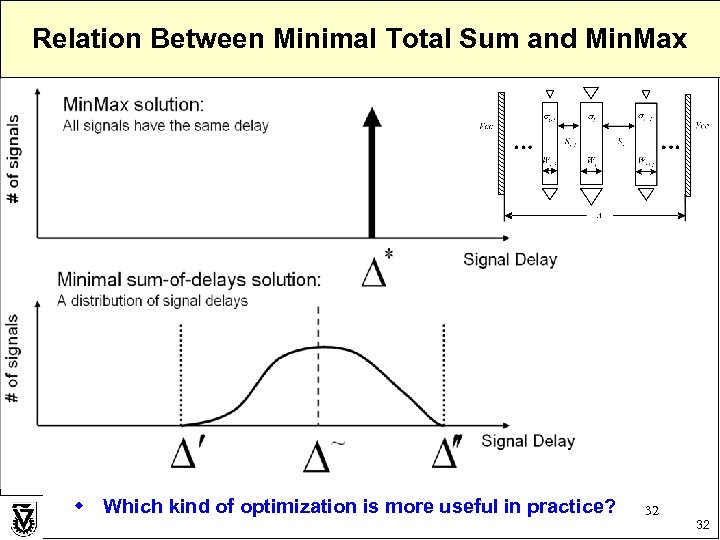

Relation Between Minimal Total Sum and Min. Max w Which kind of optimization is more useful in practice? 32 32

Relation Between Minimal Total Sum and Min. Max w Which kind of optimization is more useful in practice? 32 32

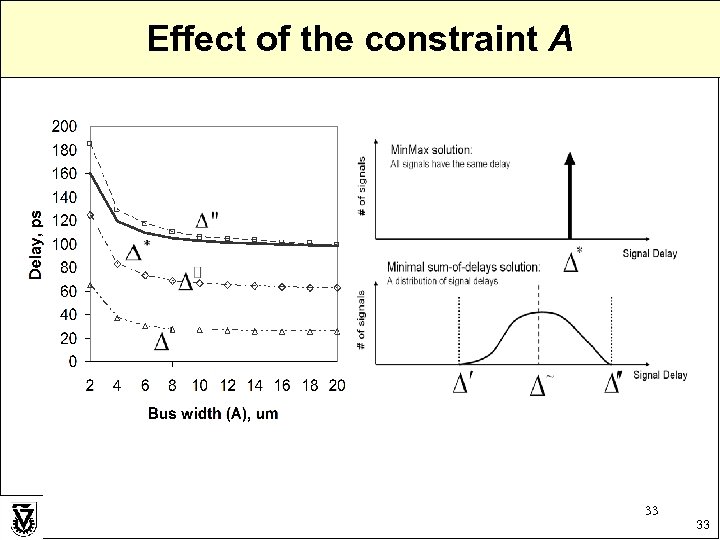

Effect of the constraint A 33 33

Effect of the constraint A 33 33

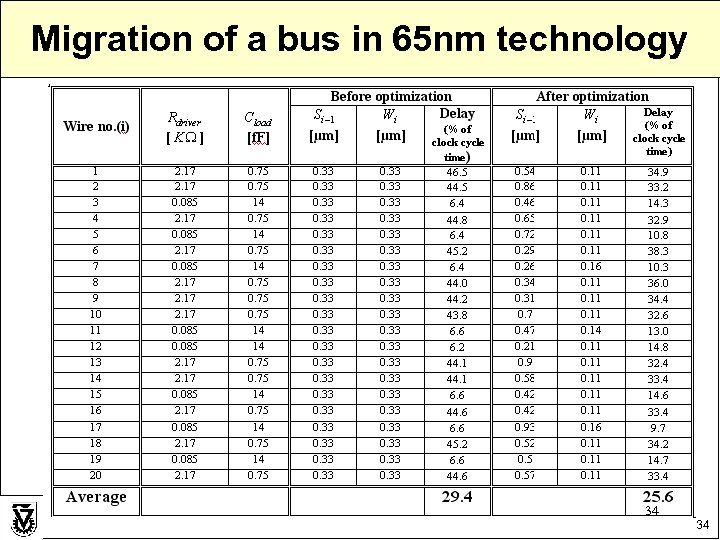

Migration of a bus in 65 nm technology 34 34

Migration of a bus in 65 nm technology 34 34

Conclusions on optimizing individual wire widths and spaces w Some performance improvement by wire sizing/spacing, according to individual signal slack, driver resistance, etc. w Sum-of-delays is a useful objective for minimization § Very appropriate for automated migration of layout to a new process 35 35

Conclusions on optimizing individual wire widths and spaces w Some performance improvement by wire sizing/spacing, according to individual signal slack, driver resistance, etc. w Sum-of-delays is a useful objective for minimization § Very appropriate for automated migration of layout to a new process 35 35

What else can we do with wires in an interconnect channel? 36 36

What else can we do with wires in an interconnect channel? 36 36

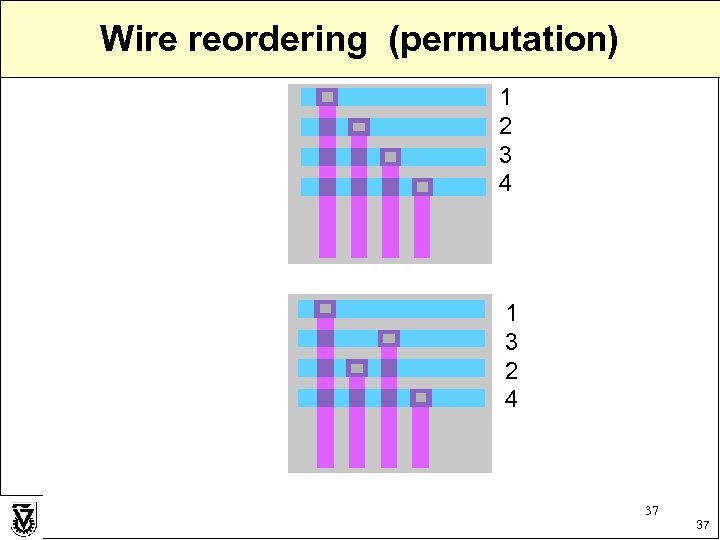

Wire reordering (permutation) 1 2 3 4 1 3 2 4 37 37

Wire reordering (permutation) 1 2 3 4 1 3 2 4 37 37

Reordering of wires to improve the optimal delay 38 38

Reordering of wires to improve the optimal delay 38 38

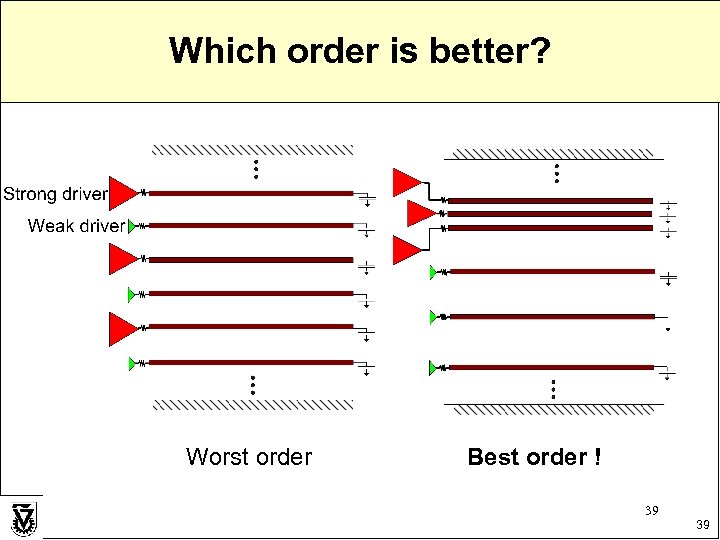

Which order is better? Worst order Best order ! 39 39

Which order is better? Worst order Best order ! 39 39

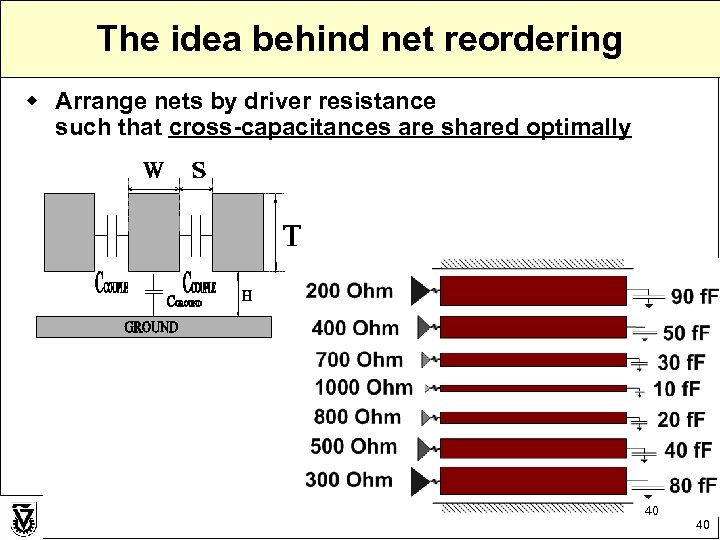

The idea behind net reordering w Arrange nets by driver resistance such that cross-capacitances are shared optimally 40 40

The idea behind net reordering w Arrange nets by driver resistance such that cross-capacitances are shared optimally 40 40

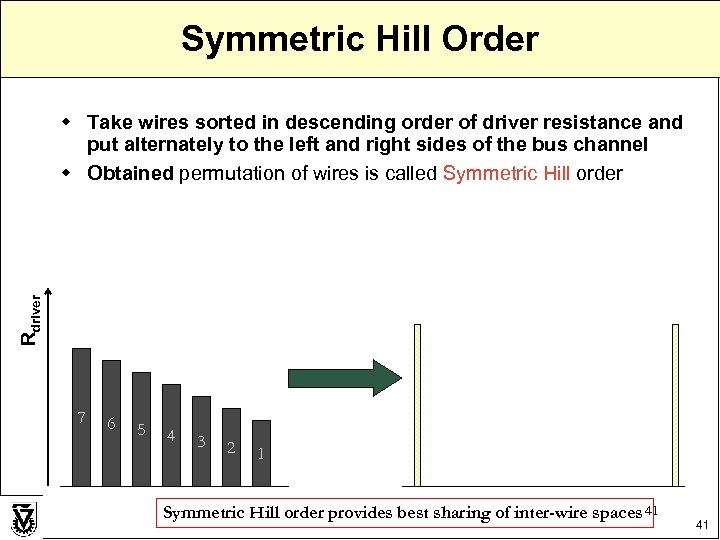

Symmetric Hill Order Rdriver w Take wires sorted in descending order of driver resistance and put alternately to the left and right sides of the bus channel w Obtained permutation of wires is called Symmetric Hill order 7 6 5 4 3 2 1 Symmetric Hill order provides best sharing of inter-wire spaces 41 41

Symmetric Hill Order Rdriver w Take wires sorted in descending order of driver resistance and put alternately to the left and right sides of the bus channel w Obtained permutation of wires is called Symmetric Hill order 7 6 5 4 3 2 1 Symmetric Hill order provides best sharing of inter-wire spaces 41 41

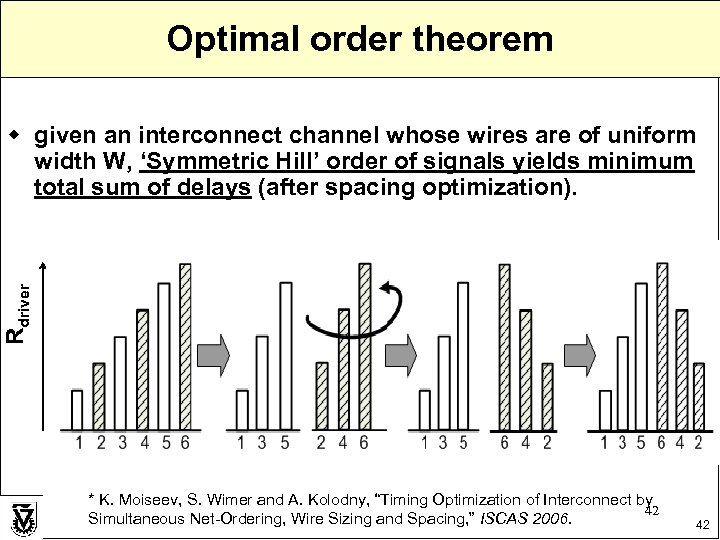

Optimal order theorem Rdriver w given an interconnect channel whose wires are of uniform width W, ‘Symmetric Hill’ order of signals yields minimum total sum of delays (after spacing optimization). * K. Moiseev, S. Wimer and A. Kolodny, “Timing Optimization of Interconnect by 42 Simultaneous Net-Ordering, Wire Sizing and Spacing, ” ISCAS 2006. 42

Optimal order theorem Rdriver w given an interconnect channel whose wires are of uniform width W, ‘Symmetric Hill’ order of signals yields minimum total sum of delays (after spacing optimization). * K. Moiseev, S. Wimer and A. Kolodny, “Timing Optimization of Interconnect by 42 Simultaneous Net-Ordering, Wire Sizing and Spacing, ” ISCAS 2006. 42

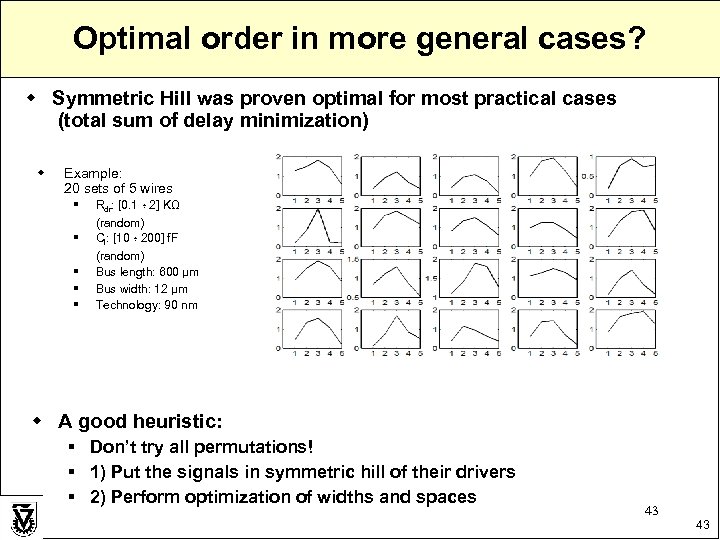

Optimal order in more general cases? w Symmetric Hill was proven optimal for most practical cases (total sum of delay minimization) w Example: 20 sets of 5 wires § § § Rdr: [0. 1 ÷ 2] KΩ (random) Cl: [10 ÷ 200] f. F (random) Bus length: 600 μm Bus width: 12 μm Technology: 90 nm w A good heuristic: § Don’t try all permutations! § 1) Put the signals in symmetric hill of their drivers § 2) Perform optimization of widths and spaces 43 43

Optimal order in more general cases? w Symmetric Hill was proven optimal for most practical cases (total sum of delay minimization) w Example: 20 sets of 5 wires § § § Rdr: [0. 1 ÷ 2] KΩ (random) Cl: [10 ÷ 200] f. F (random) Bus length: 600 μm Bus width: 12 μm Technology: 90 nm w A good heuristic: § Don’t try all permutations! § 1) Put the signals in symmetric hill of their drivers § 2) Perform optimization of widths and spaces 43 43

Symmetric Hill for Min. Max delay? w Not necessarily optimal w BUT: § § § Was found optimal for most practical cases It is a good heuristic In fact, the Min. Max delay is very sensitive to wire reordering w Symmetric hill is also good for reducing delay uncertainty because of crosstalk noise 44 44

Symmetric Hill for Min. Max delay? w Not necessarily optimal w BUT: § § § Was found optimal for most practical cases It is a good heuristic In fact, the Min. Max delay is very sensitive to wire reordering w Symmetric hill is also good for reducing delay uncertainty because of crosstalk noise 44 44

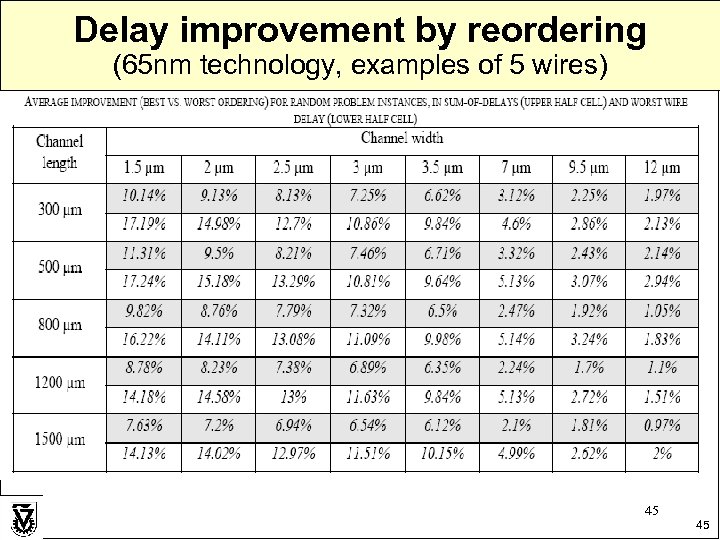

Delay improvement by reordering (65 nm technology, examples of 5 wires) 45 45

Delay improvement by reordering (65 nm technology, examples of 5 wires) 45 45

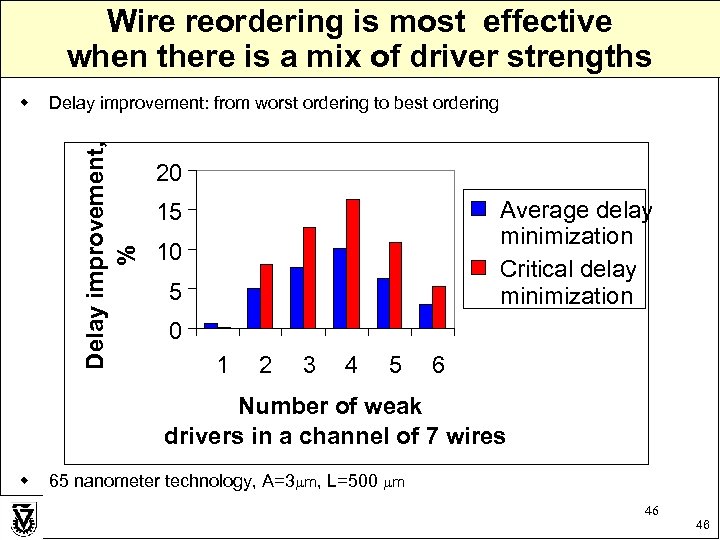

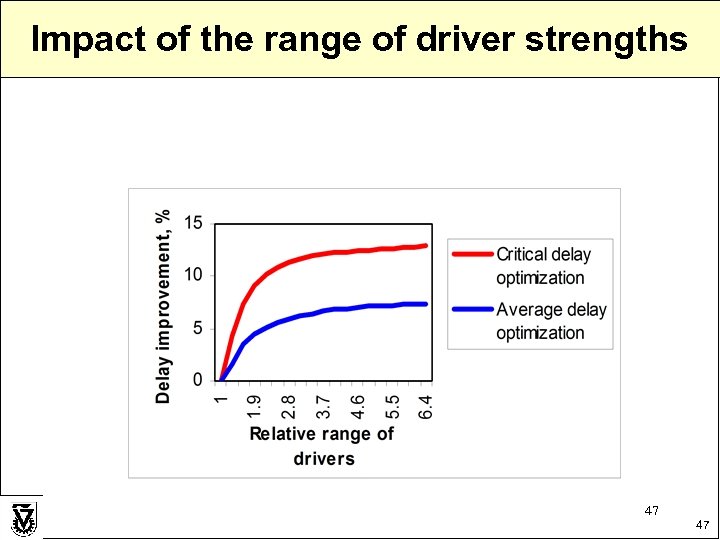

Wire reordering is most effective when there is a mix of driver strengths Delay improvement: from worst ordering to best ordering Delay improvement, % w 20 Average delay minimization Critical delay minimization 15 10 5 0 1 2 3 4 5 6 Number of weak drivers in a channel of 7 wires w 65 nanometer technology, A=3 m, L=500 m 46 46

Wire reordering is most effective when there is a mix of driver strengths Delay improvement: from worst ordering to best ordering Delay improvement, % w 20 Average delay minimization Critical delay minimization 15 10 5 0 1 2 3 4 5 6 Number of weak drivers in a channel of 7 wires w 65 nanometer technology, A=3 m, L=500 m 46 46

Impact of the range of driver strengths 47 47

Impact of the range of driver strengths 47 47

Conclusions on wire reordering w It is yet another degree of freedom! w Can help if there is a mix of driver strengths w Don’t try permutations…. Use Symmetric Hill 48 48

Conclusions on wire reordering w It is yet another degree of freedom! w Can help if there is a mix of driver strengths w Don’t try permutations…. Use Symmetric Hill 48 48

Can we use wire sizing and spacing to reduce power? 49 49

Can we use wire sizing and spacing to reduce power? 49 49

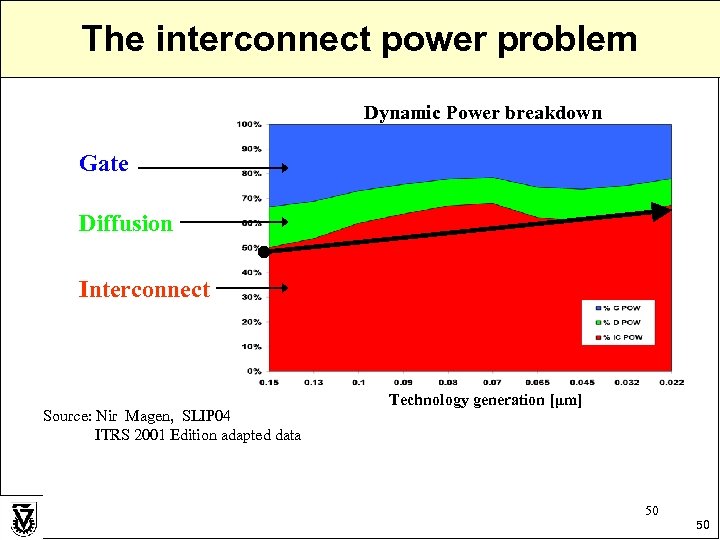

The interconnect power problem Dynamic Power breakdown Gate Diffusion Interconnect Source: Nir Magen, SLIP 04 ITRS 2001 Edition adapted data Technology generation [μm] 50 50

The interconnect power problem Dynamic Power breakdown Gate Diffusion Interconnect Source: Nir Magen, SLIP 04 ITRS 2001 Edition adapted data Technology generation [μm] 50 50

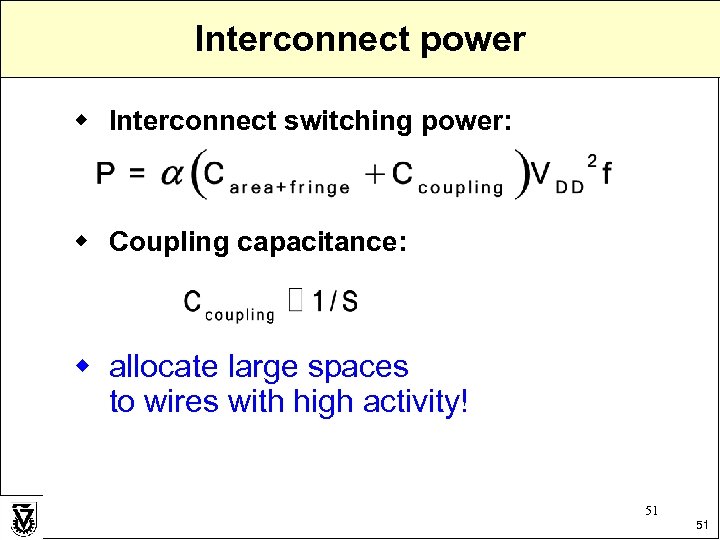

Interconnect power w Interconnect switching power: w Coupling capacitance: w allocate large spaces to wires with high activity! 51 51

Interconnect power w Interconnect switching power: w Coupling capacitance: w allocate large spaces to wires with high activity! 51 51

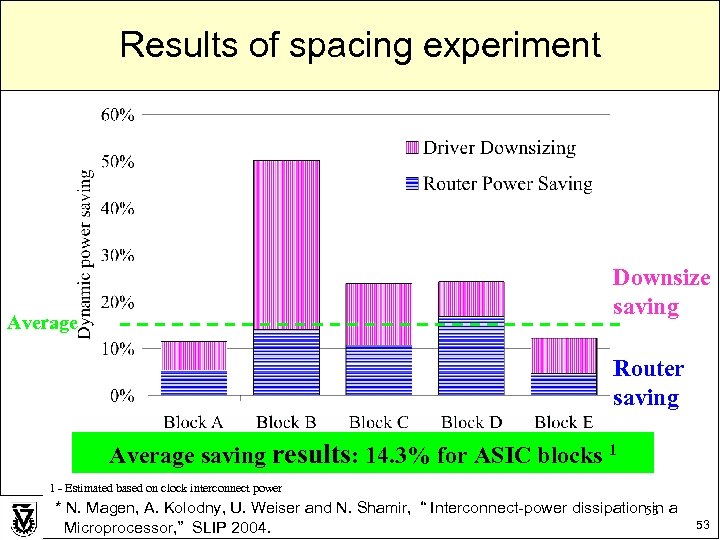

Results of spacing experiment Downsize saving Average Router saving Average saving results: 14. 3% for ASIC blocks 1 1 - Estimated based on clock interconnect power * N. Magen, A. Kolodny, U. Weiser and N. Shamir, “ Interconnect-power dissipation in a 53 Microprocessor, ” SLIP 2004. 53

Results of spacing experiment Downsize saving Average Router saving Average saving results: 14. 3% for ASIC blocks 1 1 - Estimated based on clock interconnect power * N. Magen, A. Kolodny, U. Weiser and N. Shamir, “ Interconnect-power dissipation in a 53 Microprocessor, ” SLIP 2004. 53

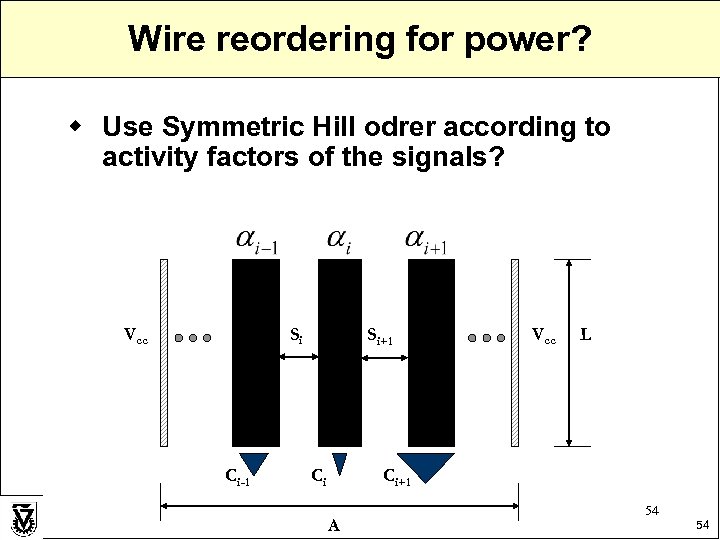

Wire reordering for power? w Use Symmetric Hill odrer according to activity factors of the signals? Vcc Si Ci-1 Si+1 Ci Vcc L Ci+1 A 54 54

Wire reordering for power? w Use Symmetric Hill odrer according to activity factors of the signals? Vcc Si Ci-1 Si+1 Ci Vcc L Ci+1 A 54 54

Conclusions on interconnect power 55 55

Conclusions on interconnect power 55 55

Optimization of drivers and wires together? 56 56

Optimization of drivers and wires together? 56 56

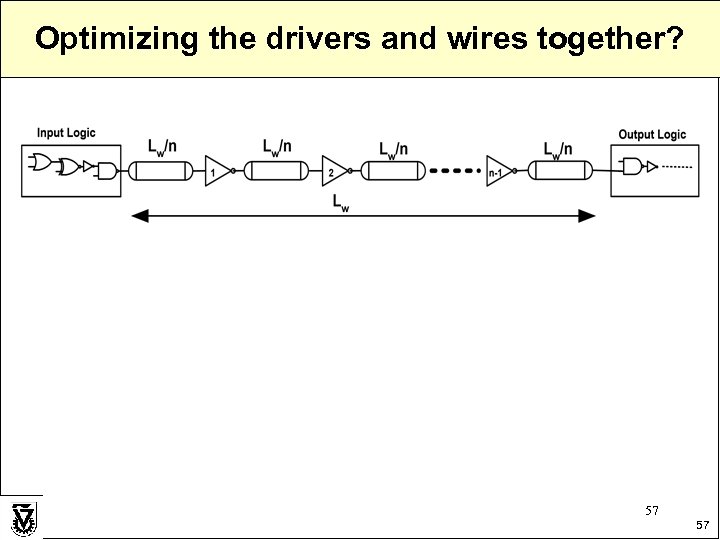

Optimizing the drivers and wires together? 57 57

Optimizing the drivers and wires together? 57 57

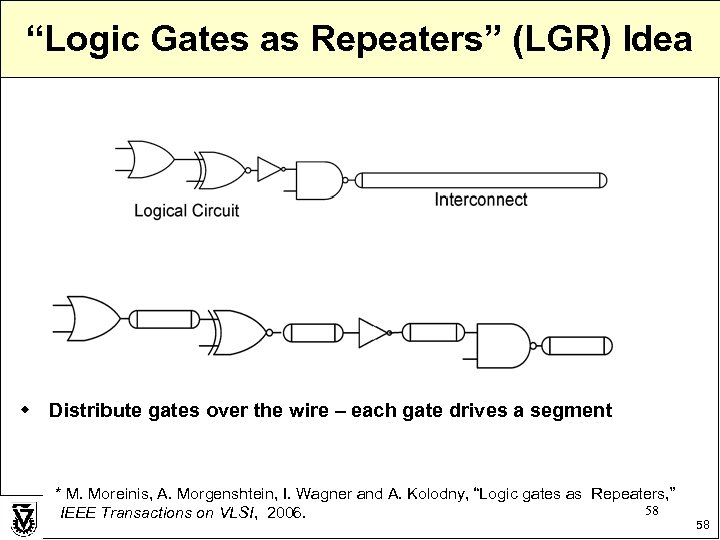

“Logic Gates as Repeaters” (LGR) Idea w Distribute gates over the wire – each gate drives a segment * M. Moreinis, A. Morgenshtein, I. Wagner and A. Kolodny, “Logic gates as Repeaters, ” 58 IEEE Transactions on VLSI, 2006. 58

“Logic Gates as Repeaters” (LGR) Idea w Distribute gates over the wire – each gate drives a segment * M. Moreinis, A. Morgenshtein, I. Wagner and A. Kolodny, “Logic gates as Repeaters, ” 58 IEEE Transactions on VLSI, 2006. 58

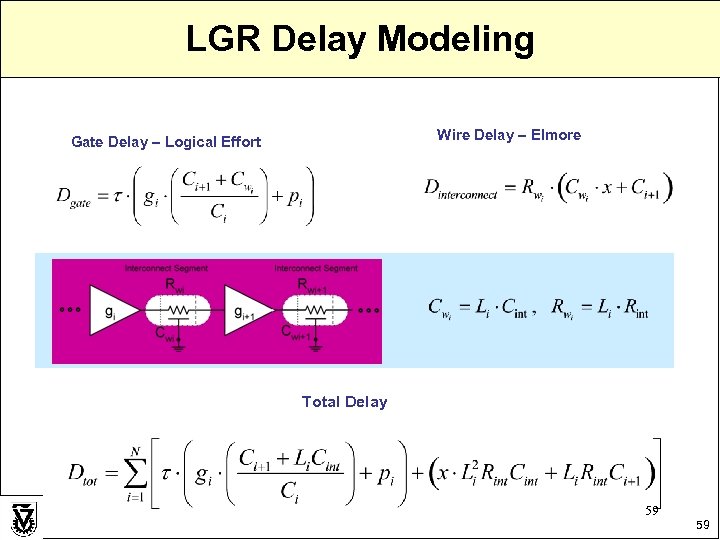

LGR Delay Modeling Wire Delay – Elmore Gate Delay – Logical Effort Total Delay 59 59

LGR Delay Modeling Wire Delay – Elmore Gate Delay – Logical Effort Total Delay 59 59

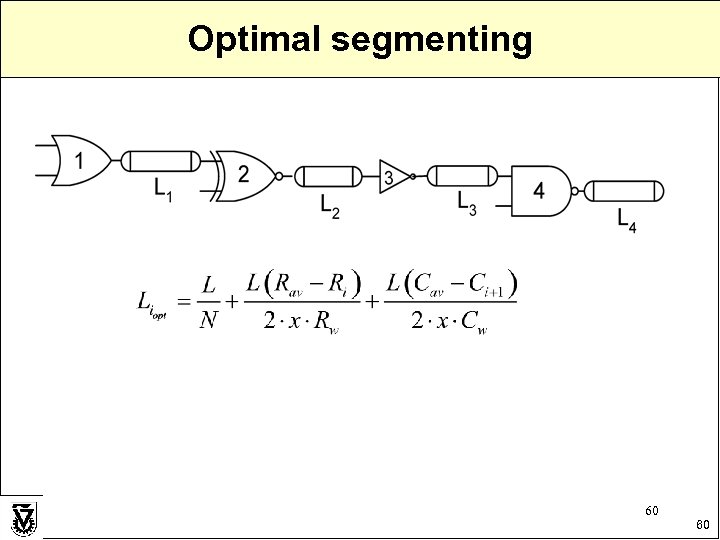

Optimal segmenting 60 60

Optimal segmenting 60 60

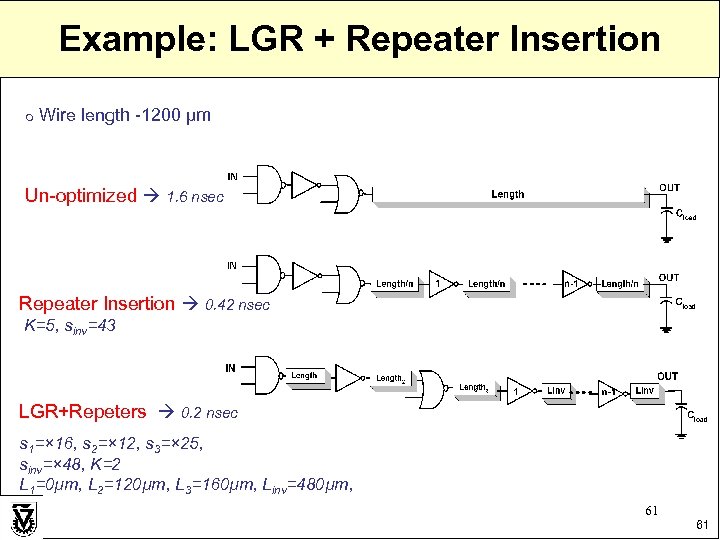

Example: LGR + Repeater Insertion Wire length -1200 µm m Un-optimized 1. 6 nsec Repeater Insertion 0. 42 nsec K=5, sinv=43 LGR+Repeters 0. 2 nsec s 1=× 16, s 2=× 12, s 3=× 25, sinv=× 48, K=2 L 1=0µm, L 2=120µm, L 3=160µm, Linv=480µm, 61 61

Example: LGR + Repeater Insertion Wire length -1200 µm m Un-optimized 1. 6 nsec Repeater Insertion 0. 42 nsec K=5, sinv=43 LGR+Repeters 0. 2 nsec s 1=× 16, s 2=× 12, s 3=× 25, sinv=× 48, K=2 L 1=0µm, L 2=120µm, L 3=160µm, Linv=480µm, 61 61

More work to do w Treat gate sizing and wire optimizations together! w Interesting issues for future research: § § § Signal correlations Minimizing impact of crosstalk Timing / power / noise interactions 62 62

More work to do w Treat gate sizing and wire optimizations together! w Interesting issues for future research: § § § Signal correlations Minimizing impact of crosstalk Timing / power / noise interactions 62 62

Summary • Sizing and spacing of uniform bus wires • Sizing and spacing individual wires • Wire reordering • Speed and Power improvements • Optimizing drivers and wires together • Future convergence of these techniques? 63 63

Summary • Sizing and spacing of uniform bus wires • Sizing and spacing individual wires • Wire reordering • Speed and Power improvements • Optimizing drivers and wires together • Future convergence of these techniques? 63 63