577cbae4dd23abd4017696cbf86ee837.ppt

- Количество слайдов: 27

IP – Based Design Methodology Daniel D. Gajski University of California gajski@uci. edu http: //www. ics. uci. edu/~gajski Copyright Ó 1999 Daniel D. Gajski

Outline • Drivers of IP business • Obstacles to IP success • Possible solutions • Business models • Future Copyright Ó 1999 Daniel D. Gajski

IP Drivers • Product complexity • Market pressure • Expertise shortage • Productivity gap • Business model Copyright Ó 1999 Daniel D. Gajski

Solving Complexity / Productivity Problems 1. IP 2. IP 3. IP 4. IP Copyright Ó 1999 Daniel D. Gajski

Obstacles to IP Success • Partially abstracted design process • Simulation based design flow – Simulation models are not easily synthesizable • IP definition (parameterization, verification, characterization) • IP-centric models for SOC – No separation of computation and communication – Need for encapsulation • Reuse automation – IP do not fit into past methodologies and tools • IP-centric methodology • No clearly defined business models – Volume, value-added and protection Copyright Ó 1999 Daniel D. Gajski

Solving Complexity / Productivity Problems • Higher level of abstraction – Specification – Architecture – Communications – Components (IP) – Tools and methodologies • Standardization – Languages – Models – Protocols – Documentation (IP) Copyright Ó 1999 Daniel D. Gajski

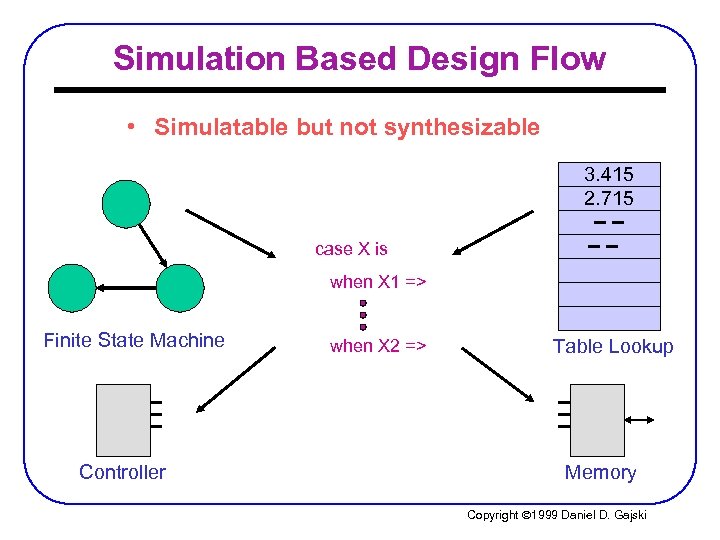

Simulation Based Design Flow • Simulatable but not synthesizable 3. 415 2. 715 case X is when X 1 => Finite State Machine Controller when X 2 => Table Lookup Memory Copyright Ó 1999 Daniel D. Gajski

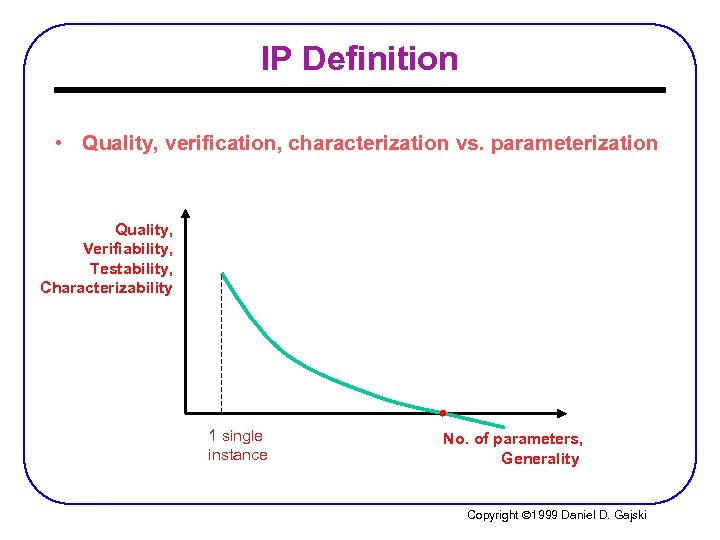

IP Definition • Quality, verification, characterization vs. parameterization Quality, Verifiability, Testability, Characterizability 1 single instance No. of parameters, Generality Copyright Ó 1999 Daniel D. Gajski

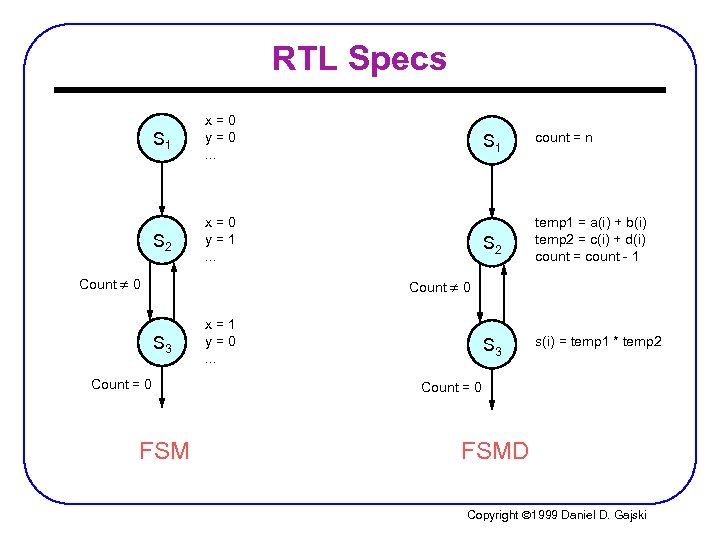

RTL Specs S 1 x=0 y=0. . . S 2 x=0 y=1. . . Count ¹ 0 S 1 count = n S 2 temp 1 = a(i) + b(i) temp 2 = c(i) + d(i) count = count - 1 S 3 s(i) = temp 1 * temp 2 Count ¹ 0 S 3 Count = 0 FSM x=1 y=0. . . Count = 0 FSMD Copyright Ó 1999 Daniel D. Gajski

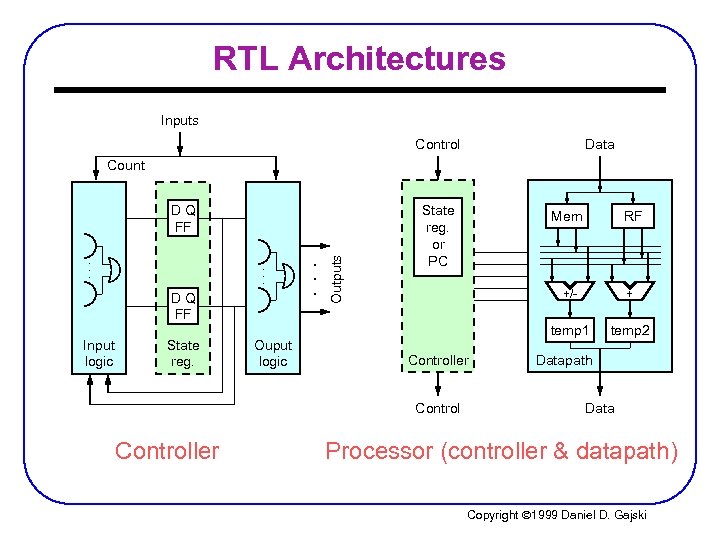

RTL Architectures Inputs Control Data Count DQ FF. . . DQ FF Input logic State reg. Ouput logic . . . Controller RF +/- Controller Mem + temp 1 Outputs . . . State reg. or PC temp 2 Datapath Data Processor (controller & datapath) Copyright Ó 1999 Daniel D. Gajski

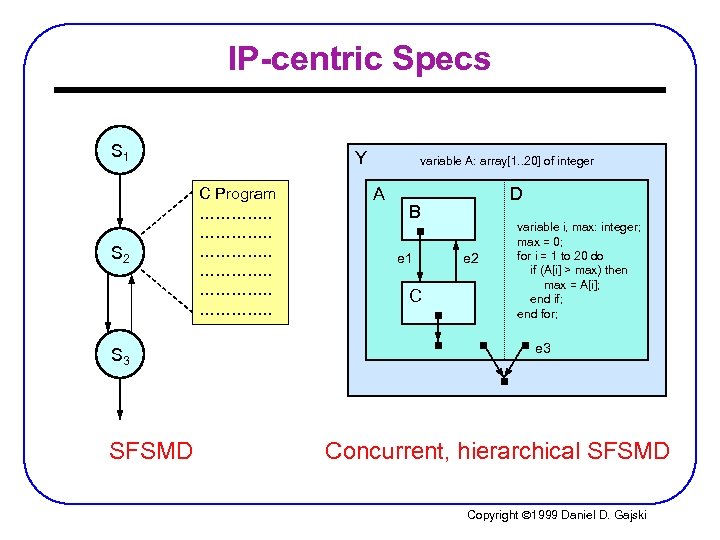

IP-centric Specs S 1 S 2 S 3 SFSMD Y C Program …………. . variable A: array[1. . 20] of integer A D B e 1 C e 2 variable i, max: integer; max = 0; for i = 1 to 20 do if (A[i] > max) then max = A[i]; end if; end for; e 3 Concurrent, hierarchical SFSMD Copyright Ó 1999 Daniel D. Gajski

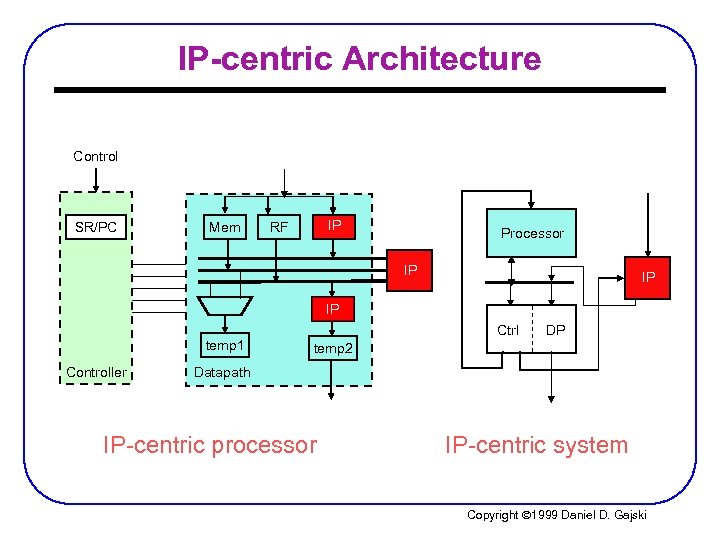

IP-centric Architecture Control SR/PC Mem IP RF RF Processor IP IP Ctrl temp 1 Controller DP temp 2 Datapath IP-centric processor IP-centric system Copyright Ó 1999 Daniel D. Gajski

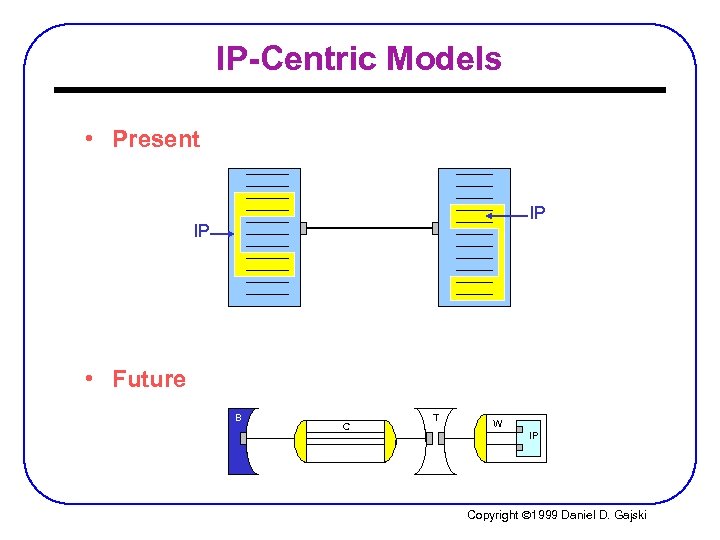

IP-Centric Models • Present IP IP • Future B C T W IP Copyright Ó 1999 Daniel D. Gajski

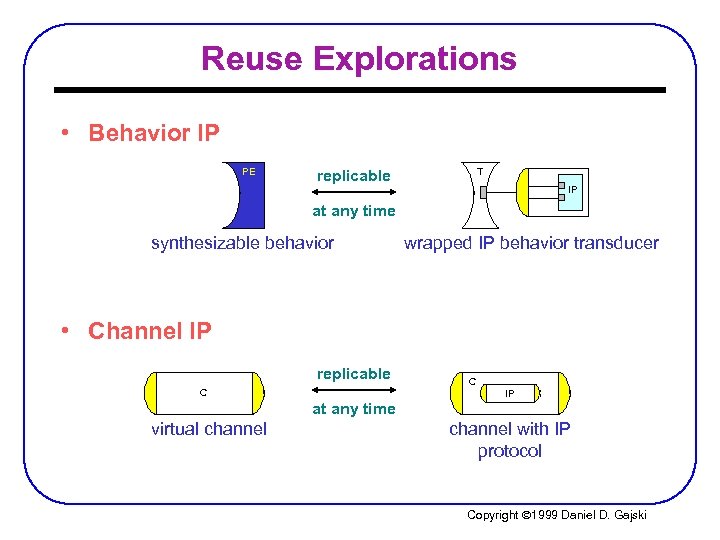

Reuse Explorations • Behavior IP PE T replicable IP at any time synthesizable behavior wrapped IP behavior transducer • Channel IP replicable C C IP at any time virtual channel with IP protocol Copyright Ó 1999 Daniel D. Gajski

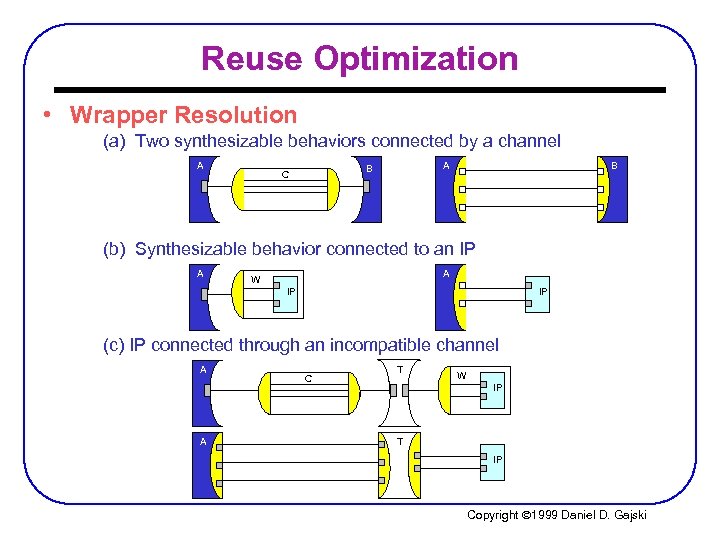

Reuse Optimization • Wrapper Resolution (a) Two synthesizable behaviors connected by a channel A A B C B (b) Synthesizable behavior connected to an IP A A W IP IP (c) IP connected through an incompatible channel A C T W IP B T A T IP Copyright Ó 1999 Daniel D. Gajski

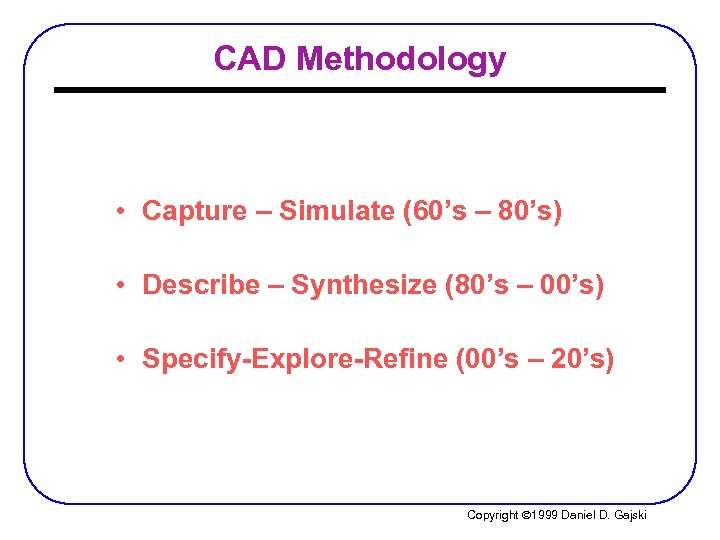

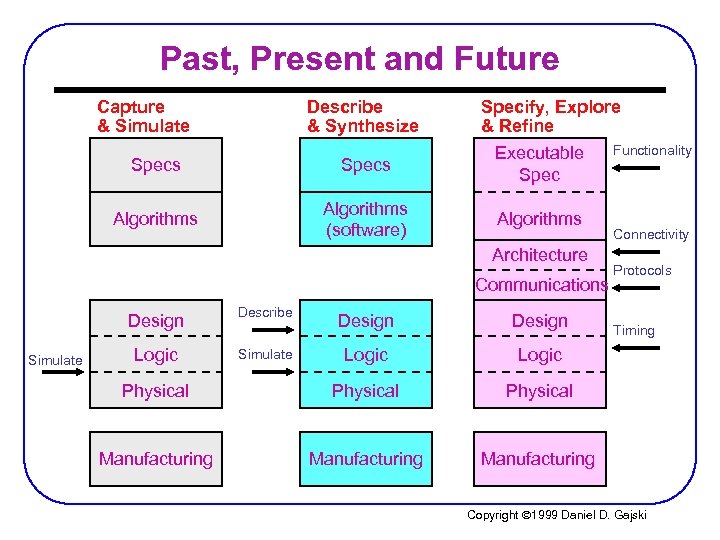

CAD Methodology • Capture – Simulate (60’s – 80’s) • Describe – Synthesize (80’s – 00’s) • Specify-Explore-Refine (00’s – 20’s) Copyright Ó 1999 Daniel D. Gajski

Past, Present and Future Capture & Simulate Describe & Synthesize Specify, Explore & Refine Specs Executable Spec Algorithms (software) Algorithms Architecture Communications Design Simulate Describe Logic Simulate Design Logic Physical Manufacturing Protocols Physical Manufacturing Connectivity Logic Physical Functionality Manufacturing Timing Copyright Ó 1999 Daniel D. Gajski

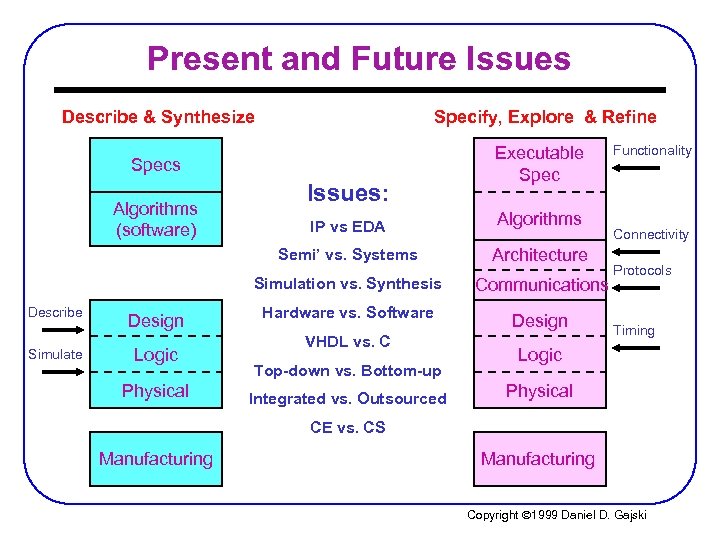

Present and Future Issues Describe & Synthesize Specify, Explore & Refine Specs Algorithms (software) Issues: Executable Spec Simulate Logic Physical Architecture Simulation vs. Synthesis Design Algorithms Semi’ vs. Systems Describe IP vs EDA Communications Hardware vs. Software Design VHDL vs. C Top-down vs. Bottom-up Integrated vs. Outsourced Functionality Connectivity Protocols Timing Logic Physical CE vs. CS Manufacturing Copyright Ó 1999 Daniel D. Gajski

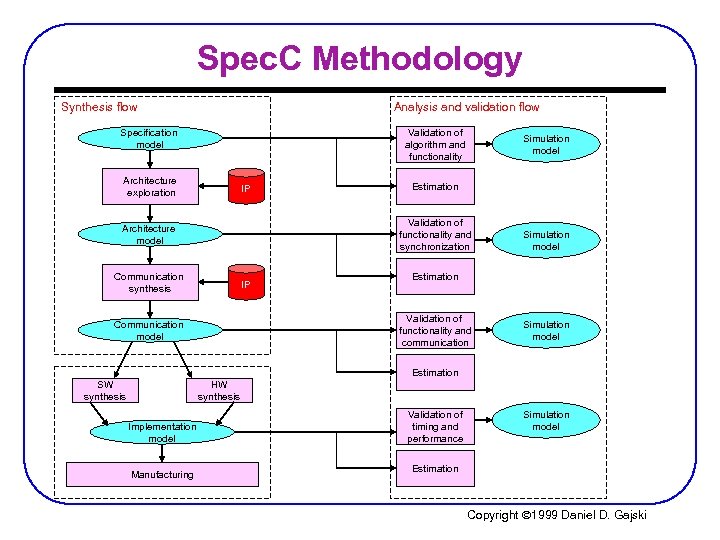

Spec. C Methodology Synthesis flow Analysis and validation flow Validation of algorithm and functionality Specification model Architecture exploration IP Simulation model Estimation Validation of functionality and synchronization Architecture model Communication synthesis IP Estimation Validation of functionality and communication Communication model Simulation model Estimation SW synthesis HW synthesis Implementation model Manufacturing Validation of timing and performance Simulation model Estimation Copyright Ó 1999 Daniel D. Gajski

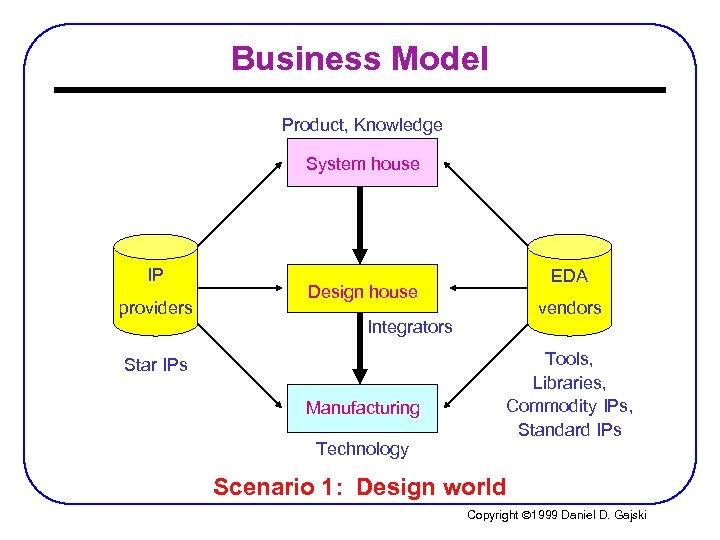

Business Model Product, Knowledge System house IP Providers Commodity IPs, Standard IPs, Star IPs Design house Integrators EDA vendors Tools, Libraries Manufacturing Technology, Libraries Copyright Ó 1999 Daniel D. Gajski

Business Model Product, Knowledge System house IP providers EDA Design house vendors Integrators Star IPs Manufacturing Technology Tools, Libraries, Commodity IPs, Standard IPs Scenario 1: Design world Copyright Ó 1999 Daniel D. Gajski

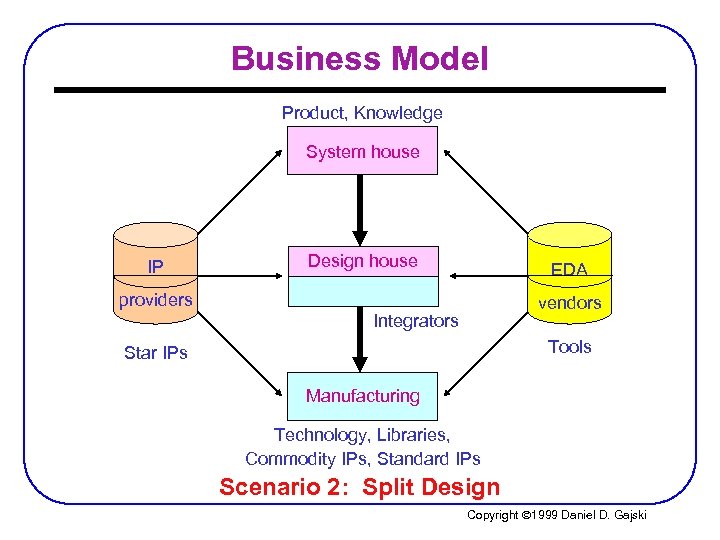

Business Model Product, Knowledge System house IP Design house EDA providers vendors Integrators Tools Star IPs Manufacturing Technology, Libraries, Commodity IPs, Standard IPs Scenario 2: Split Design Copyright Ó 1999 Daniel D. Gajski

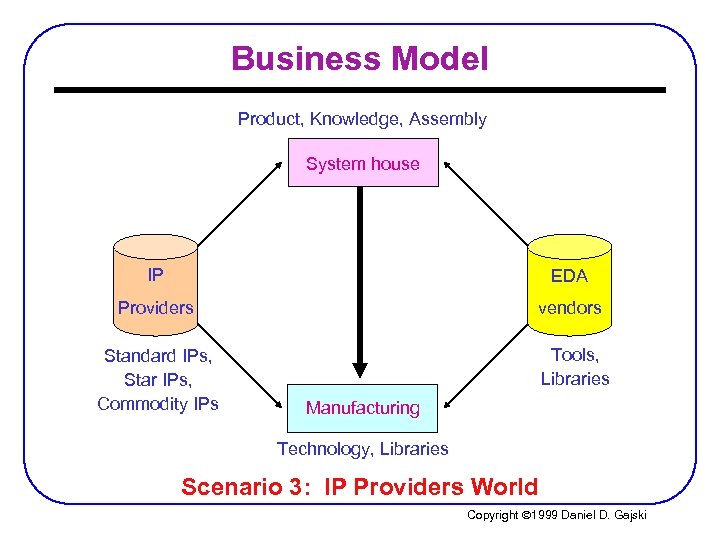

Business Model Product, Knowledge, Assembly System house IP EDA Providers vendors Standard IPs, Star IPs, Commodity IPs Tools, Libraries Manufacturing Technology, Libraries Scenario 3: IP Providers World Copyright Ó 1999 Daniel D. Gajski

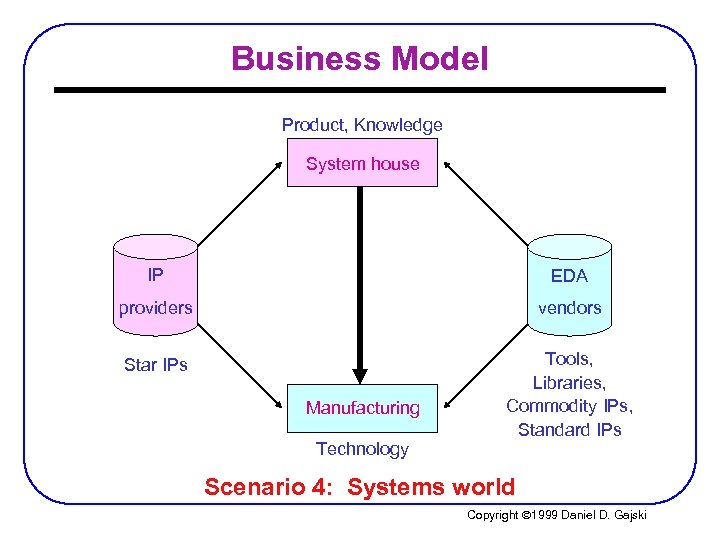

Business Model Product, Knowledge System house IP EDA providers vendors Star IPs Tools, Libraries, Commodity IPs, Standard IPs Manufacturing Technology Scenario 4: Systems world Copyright Ó 1999 Daniel D. Gajski

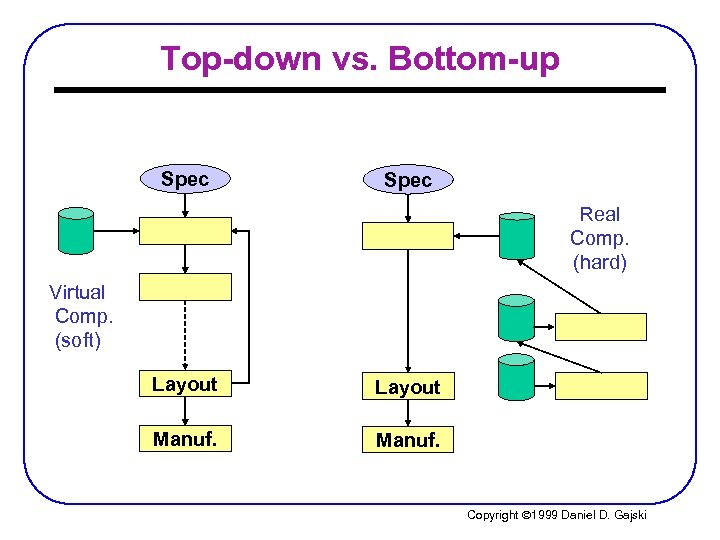

Top-down vs. Bottom-up Spec Real Comp. (hard) Virtual Comp. (soft) Layout Manuf. Copyright Ó 1999 Daniel D. Gajski

Reuse Paradigm • New Languages, guidelines, extensions • Models for exploration (spec, arch, comm, RTL) – Separation of computation & communication – Encapsulation • IP automation standards • Reuse automation (Synthesis with reuse) • IP-centric methodology Copyright Ó 1999 Daniel D. Gajski

Conclusion Copyright Ó 1999 Daniel D. Gajski

577cbae4dd23abd4017696cbf86ee837.ppt