eb89e502ed30fc96fa0e46da9dcc3ec7.ppt

- Количество слайдов: 22

Introduction to Computing Systems from bits & gates to C & beyond Chapter 8 Input/Output I/O basics l Keyboard input l Monitor output l Interrupt driven I/O l DMA l

I/O Basics l Definitions w Input § transfer data from the outside world to the computer: keyboard, mouse, scanner, bar-code reader, etc. w Output § transfer data from the computer to the outside: monitor, printer, LED display, etc. w Peripheral: any I/O device, including disks. l LC-3 8 -2 supports only a keyboard and a monitor Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

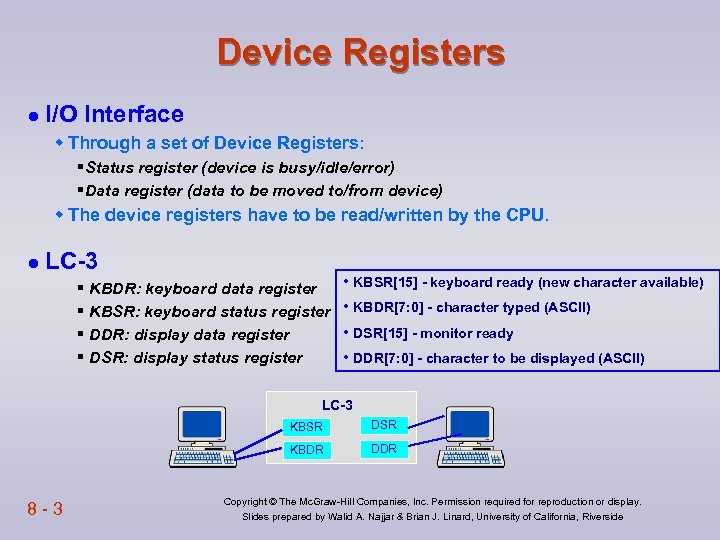

Device Registers l I/O Interface w Through a set of Device Registers: §Status register (device is busy/idle/error) §Data register (data to be moved to/from device) w The device registers have to be read/written by the CPU. l LC-3 § KBDR: keyboard data register § KBSR: keyboard status register § DDR: display data register § DSR: display status register • KBSR[15] - keyboard ready (new character available) • KBDR[7: 0] - character typed (ASCII) • DSR[15] - monitor ready • DDR[7: 0] - character to be displayed (ASCII) LC-3 KBSR KBDR 8 -3 DSR DDR Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

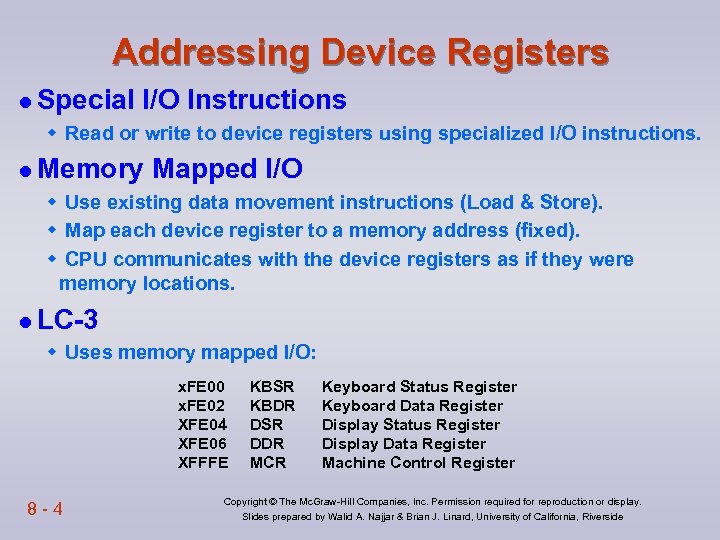

Addressing Device Registers l Special I/O Instructions w Read or write to device registers using specialized I/O instructions. l Memory Mapped I/O w Use existing data movement instructions (Load & Store). w Map each device register to a memory address (fixed). w CPU communicates with the device registers as if they were memory locations. l LC-3 w Uses memory mapped I/O: x. FE 00 x. FE 02 XFE 04 XFE 06 XFFFE 8 -4 KBSR KBDR DSR DDR MCR Keyboard Status Register Keyboard Data Register Display Status Register Display Data Register Machine Control Register Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

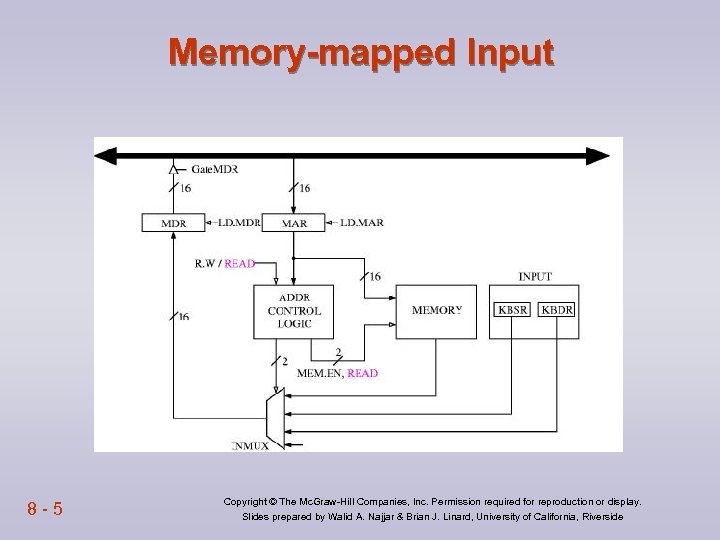

Memory-mapped Input 8 -5 Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

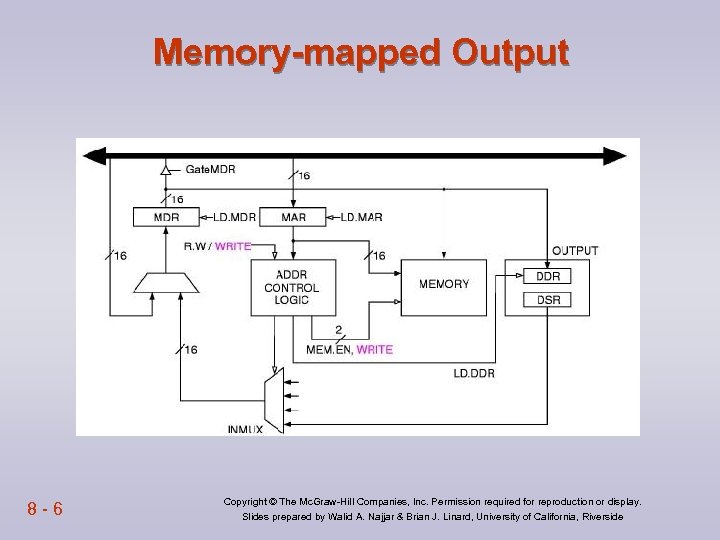

Memory-mapped Output 8 -6 Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

Synchronizing CPU and I/O l Problem w Speed mismatch between CPU and I/O: § CPU runs at up to 2 GHz, while all I/O is much slower. w Example : Keyboard input is both slow, and irregular. w We need a protocol to keep CPU & KBD synchronized. l Two possible solutions: w Polling (handshake synchronization) w Interrupt-driven I/O 8 -7 Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

Synchronizing CPU and I/O - 2 l Polling, w w or handshake synchronization CPU checks the KBD Ready status bit. If set, CPU reads the data register and resets the Ready bit. Start over. Makes CPU-I/O interaction seem to be synchronous. l Interrupt-driven I/O w An external device is allowed to interrupt the CPU and demand attention w The CPU attends to the device in an orderly fashion (more later) 8 -8 Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

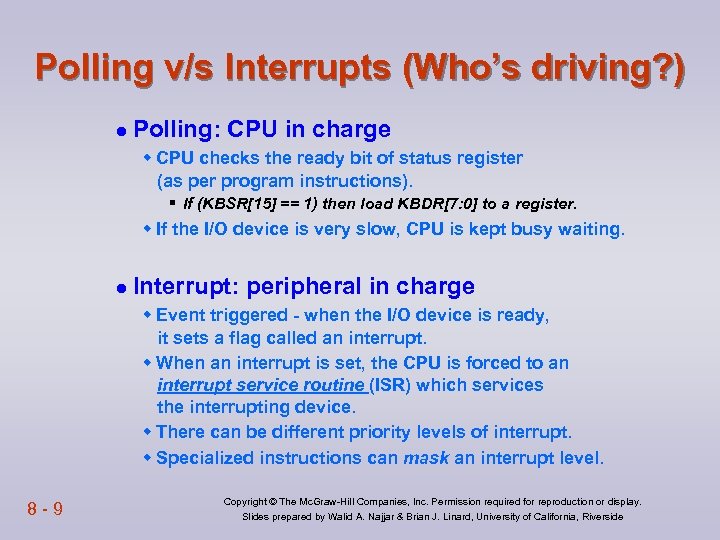

Polling v/s Interrupts (Who’s driving? ) l Polling: CPU in charge w CPU checks the ready bit of status register (as per program instructions). § If (KBSR[15] == 1) then load KBDR[7: 0] to a register. w If the I/O device is very slow, CPU is kept busy waiting. l Interrupt: peripheral in charge w Event triggered - when the I/O device is ready, it sets a flag called an interrupt. w When an interrupt is set, the CPU is forced to an interrupt service routine (ISR) which services the interrupting device. w There can be different priority levels of interrupt. w Specialized instructions can mask an interrupt level. 8 -9 Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

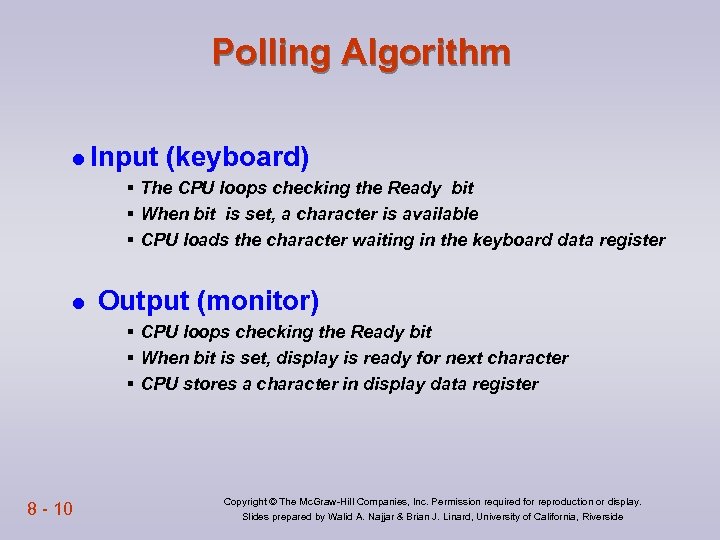

Polling Algorithm l Input (keyboard) § The CPU loops checking the Ready bit § When bit is set, a character is available § CPU loads the character waiting in the keyboard data register l Output (monitor) § CPU loops checking the Ready bit § When bit is set, display is ready for next character § CPU stores a character in display data register 8 - 10 Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

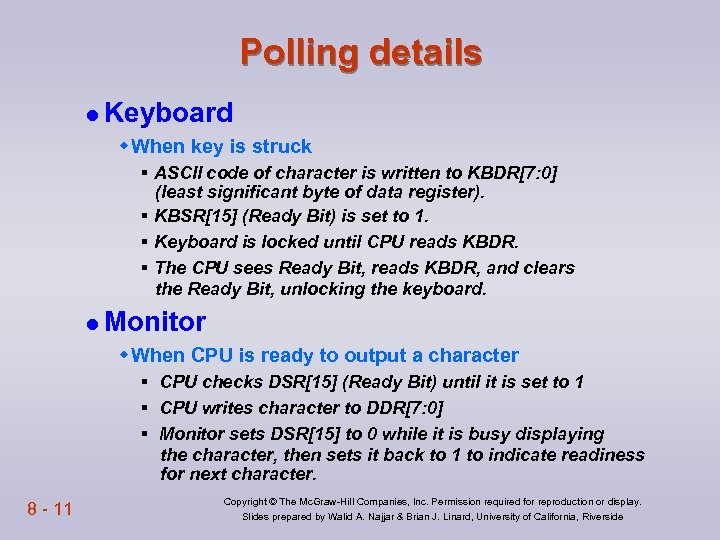

Polling details l Keyboard w When key is struck § ASCII code of character is written to KBDR[7: 0] (least significant byte of data register). § KBSR[15] (Ready Bit) is set to 1. § Keyboard is locked until CPU reads KBDR. § The CPU sees Ready Bit, reads KBDR, and clears the Ready Bit, unlocking the keyboard. l Monitor w When CPU is ready to output a character § CPU checks DSR[15] (Ready Bit) until it is set to 1 § CPU writes character to DDR[7: 0] § Monitor sets DSR[15] to 0 while it is busy displaying the character, then sets it back to 1 to indicate readiness for next character. 8 - 11 Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

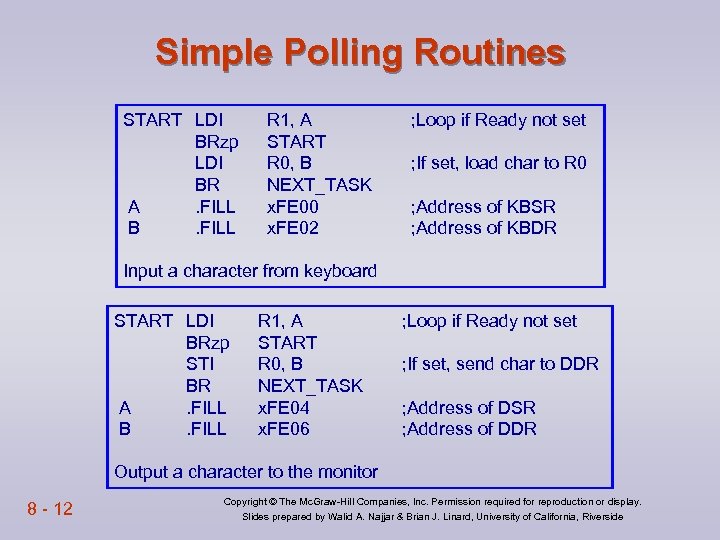

Simple Polling Routines START LDI BRzp LDI BR A. FILL B. FILL R 1, A START R 0, B NEXT_TASK x. FE 00 x. FE 02 ; Loop if Ready not set ; If set, load char to R 0 ; Address of KBSR ; Address of KBDR Input a character from keyboard START LDI BRzp STI BR A. FILL B. FILL R 1, A START R 0, B NEXT_TASK x. FE 04 x. FE 06 ; Loop if Ready not set ; If set, send char to DDR ; Address of DSR ; Address of DDR Output a character to the monitor 8 - 12 Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

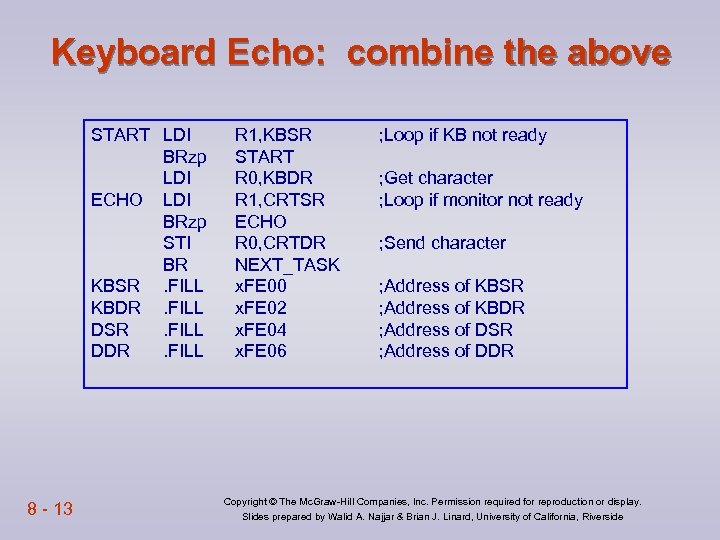

Keyboard Echo: combine the above START LDI BRzp LDI ECHO LDI BRzp STI BR KBSR. FILL KBDR. FILL DSR. FILL DDR. FILL 8 - 13 R 1, KBSR START R 0, KBDR R 1, CRTSR ECHO R 0, CRTDR NEXT_TASK x. FE 00 x. FE 02 x. FE 04 x. FE 06 ; Loop if KB not ready ; Get character ; Loop if monitor not ready ; Send character ; Address of KBSR ; Address of KBDR ; Address of DSR ; Address of DDR Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

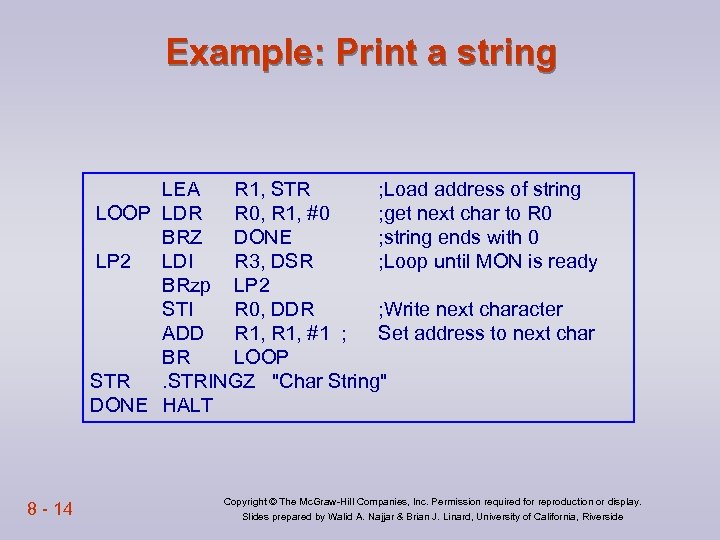

Example: Print a string LEA R 1, STR ; Load address of string LOOP LDR R 0, R 1, #0 ; get next char to R 0 BRZ DONE ; string ends with 0 LP 2 LDI R 3, DSR ; Loop until MON is ready BRzp LP 2 STI R 0, DDR ; Write next character ADD R 1, #1 ; Set address to next char BR LOOP STRINGZ "Char String" DONE HALT 8 - 14 Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

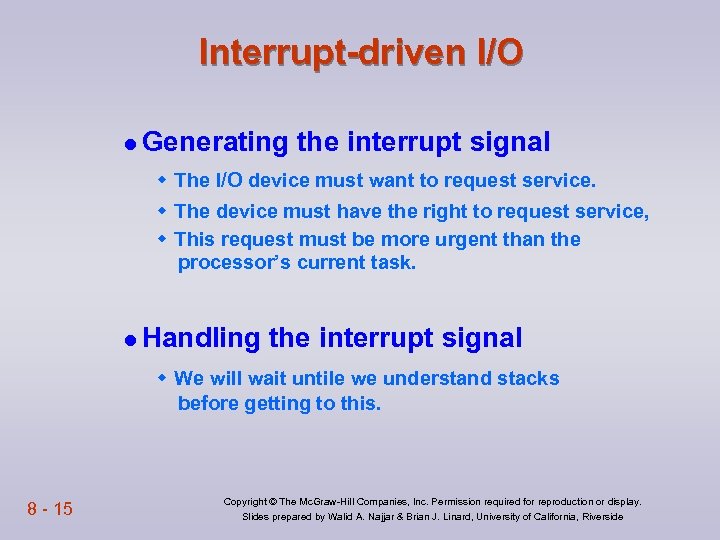

Interrupt-driven I/O l Generating the interrupt signal w The I/O device must want to request service. w The device must have the right to request service, w This request must be more urgent than the processor’s current task. l Handling the interrupt signal w We will wait untile we understand stacks before getting to this. 8 - 15 Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

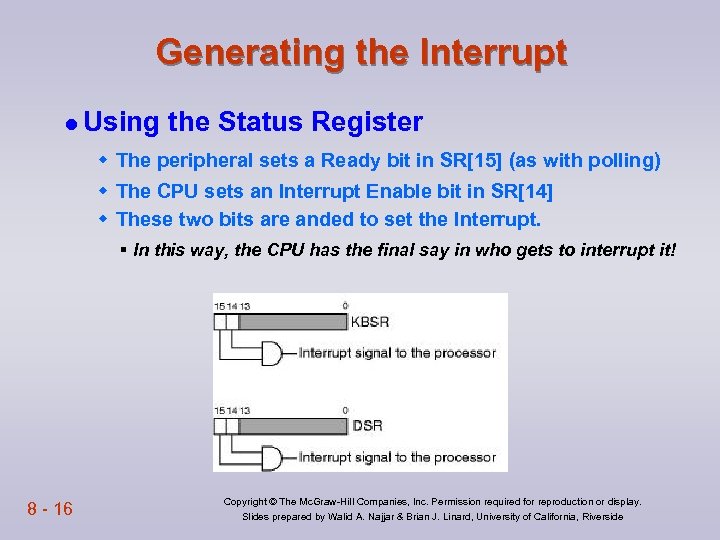

Generating the Interrupt l Using the Status Register w The peripheral sets a Ready bit in SR[15] (as with polling) w The CPU sets an Interrupt Enable bit in SR[14] w These two bits are anded to set the Interrupt. § In this way, the CPU has the final say in who gets to interrupt it! 8 - 16 Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

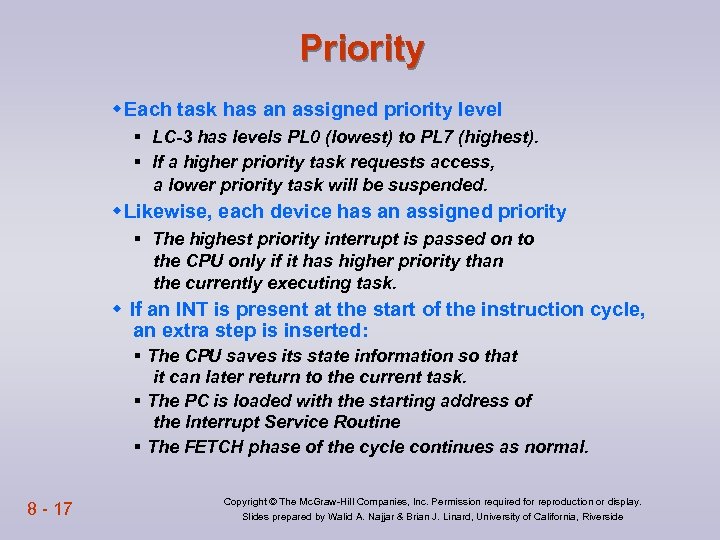

Priority w Each task has an assigned priority level § LC-3 has levels PL 0 (lowest) to PL 7 (highest). § If a higher priority task requests access, a lower priority task will be suspended. w Likewise, each device has an assigned priority § The highest priority interrupt is passed on to the CPU only if it has higher priority than the currently executing task. w If an INT is present at the start of the instruction cycle, an extra step is inserted: § The CPU saves its state information so that it can later return to the current task. § The PC is loaded with the starting address of the Interrupt Service Routine § The FETCH phase of the cycle continues as normal. 8 - 17 Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

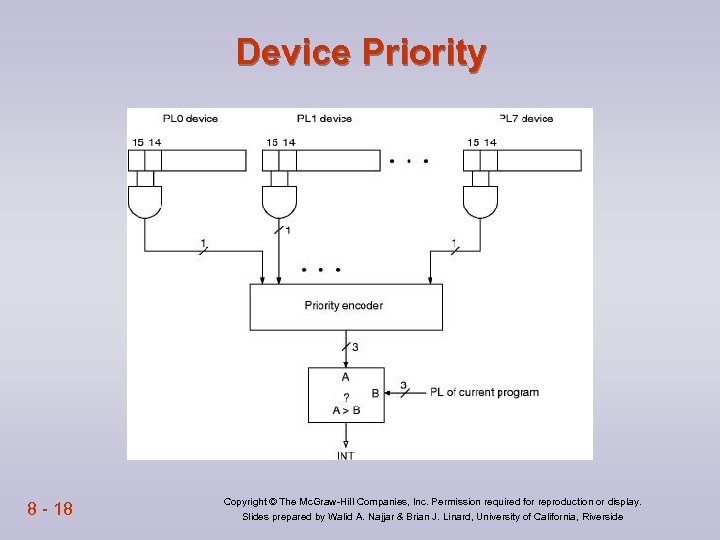

Device Priority 8 - 18 Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

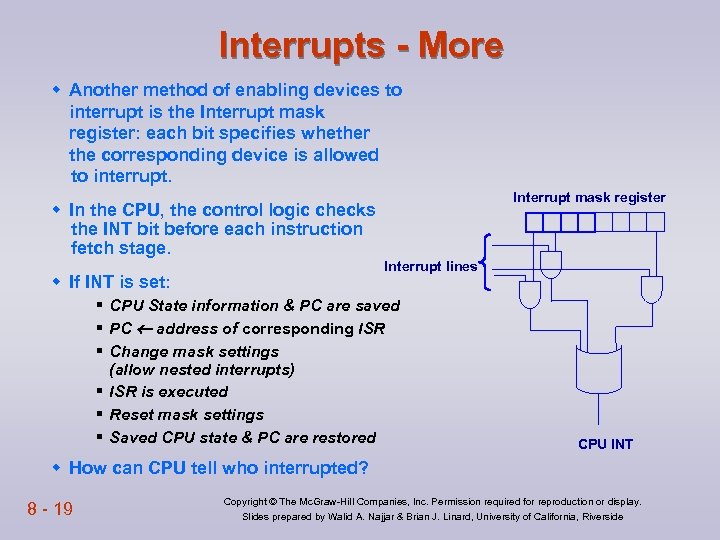

Interrupts - More w Another method of enabling devices to interrupt is the Interrupt mask register: each bit specifies whether the corresponding device is allowed to interrupt. w In the CPU, the control logic checks the INT bit before each instruction fetch stage. w If INT is set: Interrupt mask register Interrupt lines § CPU State information & PC are saved § PC address of corresponding ISR § Change mask settings (allow nested interrupts) § ISR is executed § Reset mask settings § Saved CPU state & PC are restored CPU INT w How can CPU tell who interrupted? 8 - 19 Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

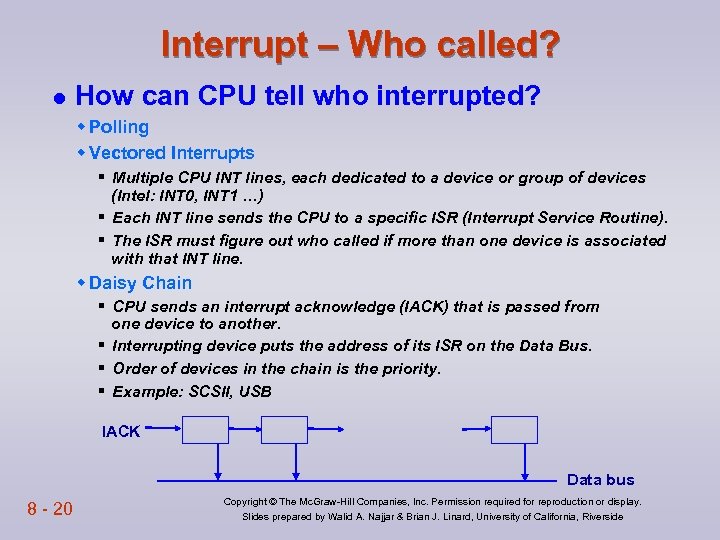

Interrupt – Who called? l How can CPU tell who interrupted? w Polling w Vectored Interrupts § Multiple CPU INT lines, each dedicated to a device or group of devices (Intel: INT 0, INT 1 …) § Each INT line sends the CPU to a specific ISR (Interrupt Service Routine). § The ISR must figure out who called if more than one device is associated with that INT line. w Daisy Chain § CPU sends an interrupt acknowledge (IACK) that is passed from one device to another. § Interrupting device puts the address of its ISR on the Data Bus. § Order of devices in the chain is the priority. § Example: SCSII, USB IACK Data bus 8 - 20 Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

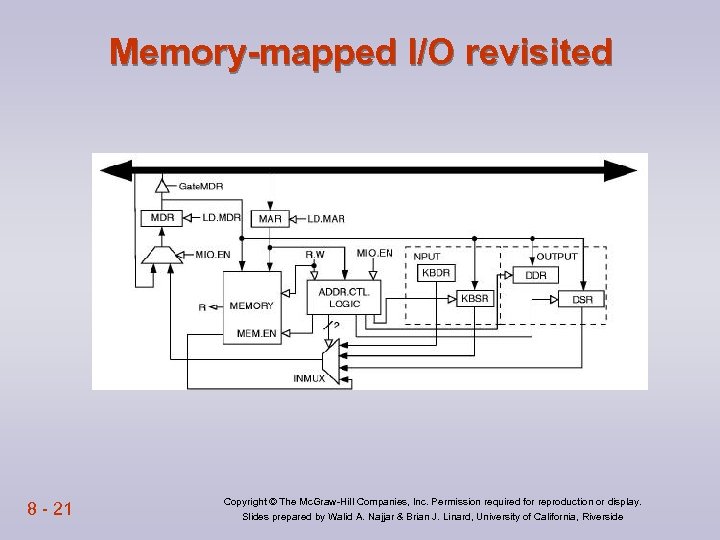

Memory-mapped I/O revisited 8 - 21 Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

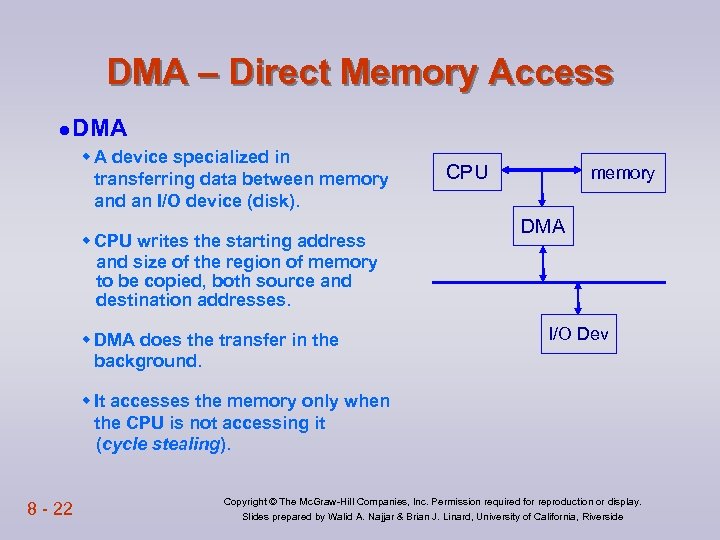

DMA – Direct Memory Access l DMA w A device specialized in transferring data between memory and an I/O device (disk). w CPU writes the starting address and size of the region of memory to be copied, both source and destination addresses. w DMA does the transfer in the background. CPU memory DMA I/O Dev w It accesses the memory only when the CPU is not accessing it (cycle stealing). 8 - 22 Copyright © The Mc. Graw-Hill Companies, Inc. Permission required for reproduction or display. Slides prepared by Walid A. Najjar & Brian J. Linard, University of California, Riverside

eb89e502ed30fc96fa0e46da9dcc3ec7.ppt