95e9643cf0a3cd152aea8b69571779cf.ppt

- Количество слайдов: 51

Intro to IEEE 1149. 1 Boundary -Scan (JTAG) David Lavo lavo@soe. ucsc. edu UC Santa Cruz January 27, 2005 © David Lavo Intro To Boundary-Scan

Outline • • • What is 1149. 1? 1149. 1 Basics Documentation & Resources 1149. 1 for the Designer Extended Uses for the TAP Controller © David Lavo Intro To Boundary-Scan 2

IEEE 1149. 1 Boundary-Scan • Facilitates board testing • Provides an on-chip means of controlling and testing pads • Boundary-scan components can also be used for other test purposes: – Logic and RAM BIST control – Scan chain control – Scan wrapper config. , test modes, etc. © David Lavo Intro To Boundary-Scan 3

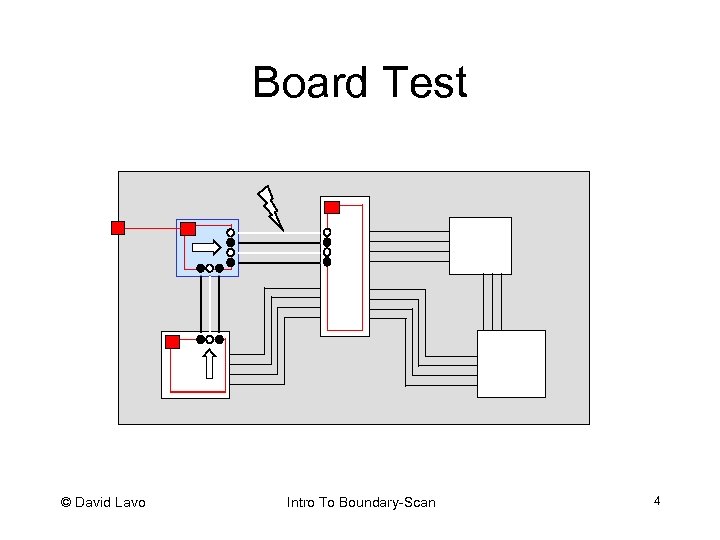

Board Test © David Lavo Intro To Boundary-Scan 4

Pad & Parametric Test • 1149. 1 can be used to control and exercise pads independent of the chip core • Leakage on tri-state outputs • Measure voltage and current for output pads driving 0 or 1 • Test logic levels captured by input pads at various voltages © David Lavo Intro To Boundary-Scan 5

Outline • • • What is 1149. 1? 1149. 1 Basics Documentation & Resources 1149. 1 for the Designer Extended Uses for the TAP Controller © David Lavo Intro To Boundary-Scan 6

1149. 1 Hardware • Test Access Port: 5 pins • TAP Controller – Finite State Machine – Internal registers (Bypass, Instruction, etc. ) – Test control logic • Boundary-Scan Register Chain • Internal Data Registers (Optional) © David Lavo Intro To Boundary-Scan 7

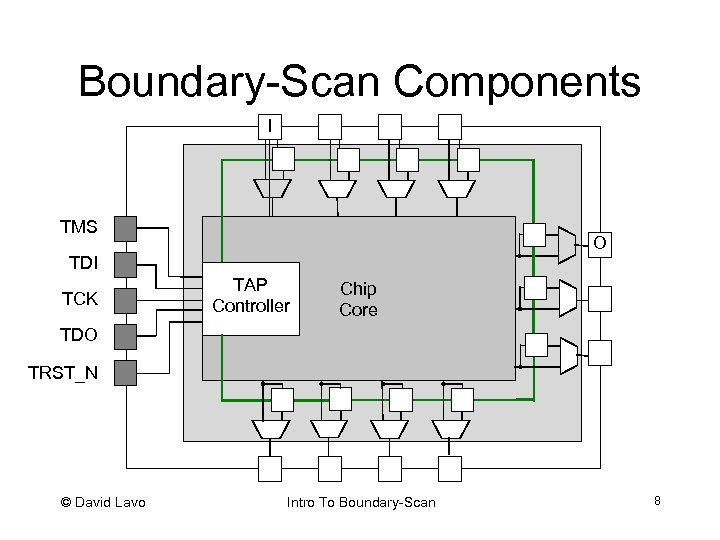

Boundary-Scan Components I TMS O TDI TCK TAP Controller Chip Core TDO TRST_N © David Lavo Intro To Boundary-Scan 8

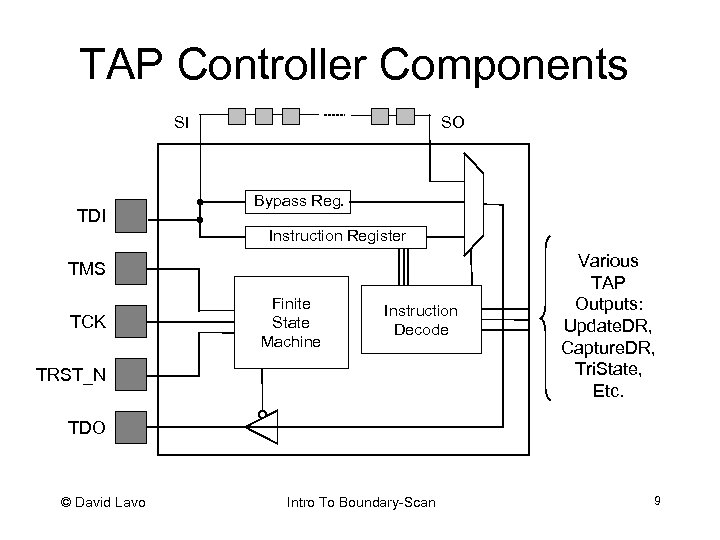

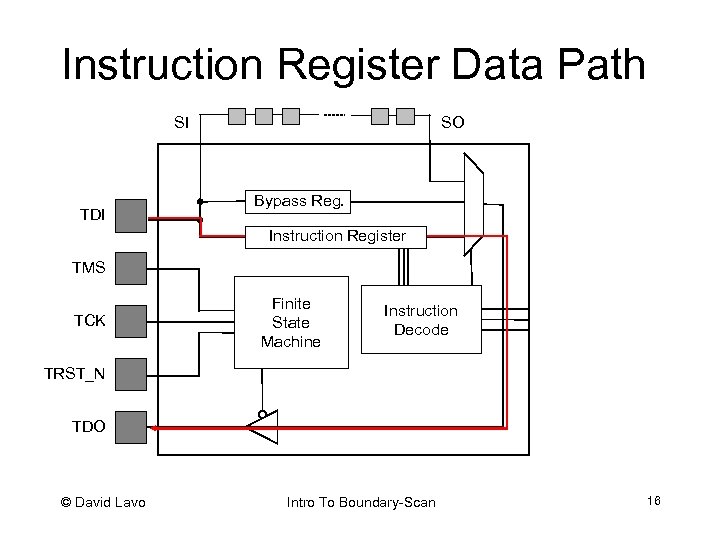

TAP Controller Components SO SI TDI Bypass Reg. Instruction Register TMS TCK Finite State Machine Instruction Decode TRST_N Various TAP Outputs: Update. DR, Capture. DR, Tri. State, Etc. TDO © David Lavo Intro To Boundary-Scan 9

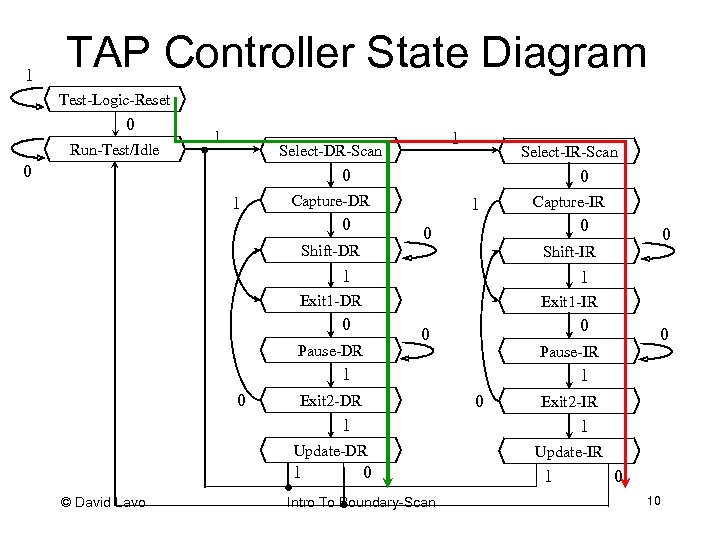

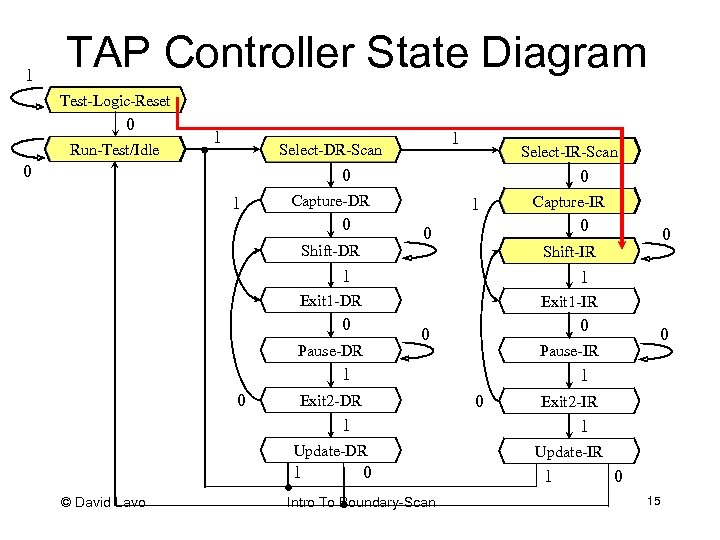

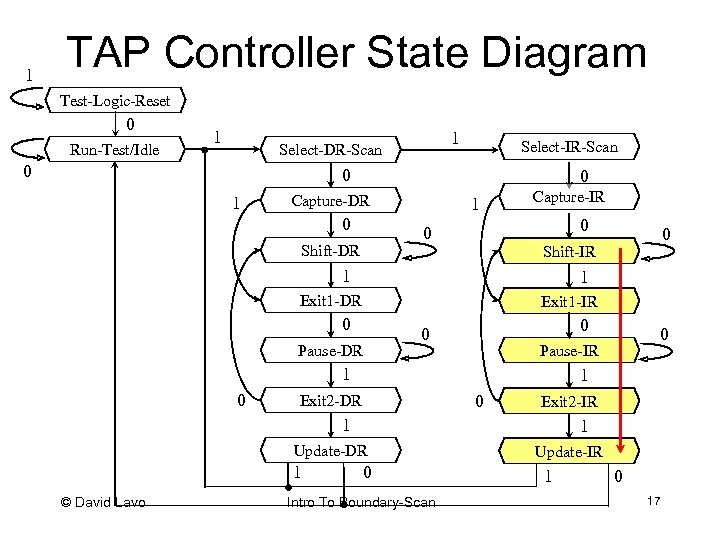

1 TAP Controller State Diagram Test-Logic-Reset 0 Run-Test/Idle 1 1 Select-DR-Scan 0 Select-IR-Scan 0 1 0 Capture-DR 0 1 0 0 Shift-DR Capture-IR Shift-IR 1 1 Exit 1 -DR Exit 1 -IR 0 Pause-DR 0 0 1 0 Exit 2 -DR Exit 2 -IR 1 1 Update-DR 1 © David Lavo 0 Pause-IR 1 0 0 0 Intro To Boundary-Scan Update-IR 1 0 10

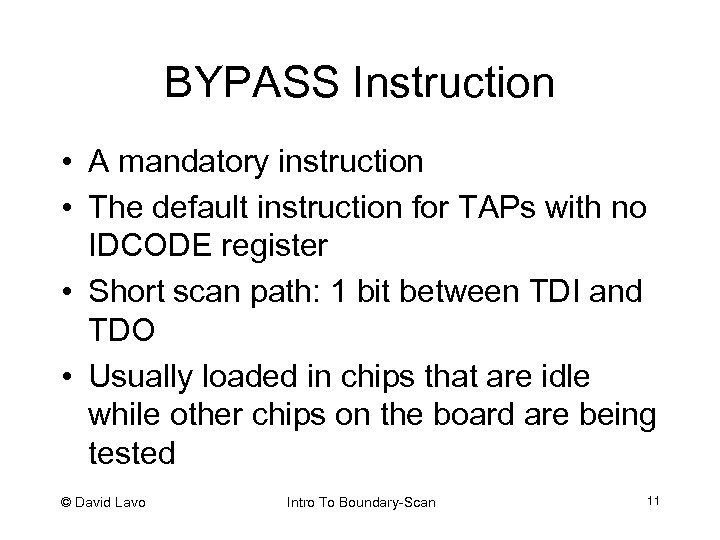

BYPASS Instruction • A mandatory instruction • The default instruction for TAPs with no IDCODE register • Short scan path: 1 bit between TDI and TDO • Usually loaded in chips that are idle while other chips on the board are being tested © David Lavo Intro To Boundary-Scan 11

BYPASS Data Path SO SI TDI Bypass Reg. Instruction Register TMS TCK Finite State Machine Instruction Decode TRST_N TDO © David Lavo Intro To Boundary-Scan 12

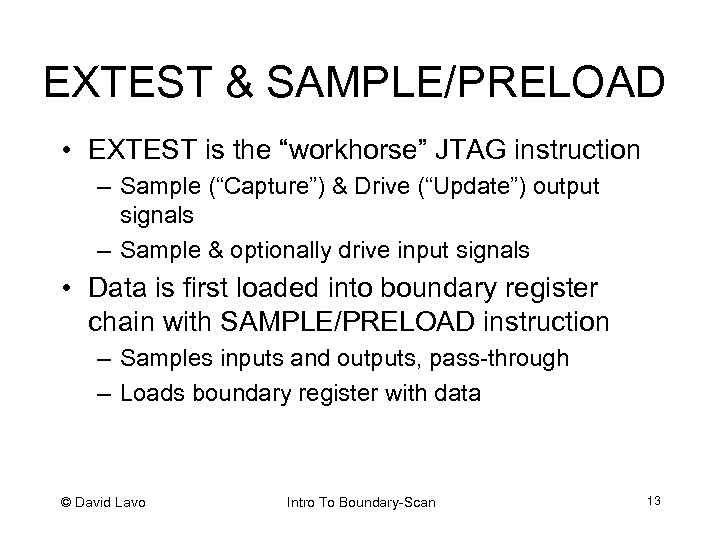

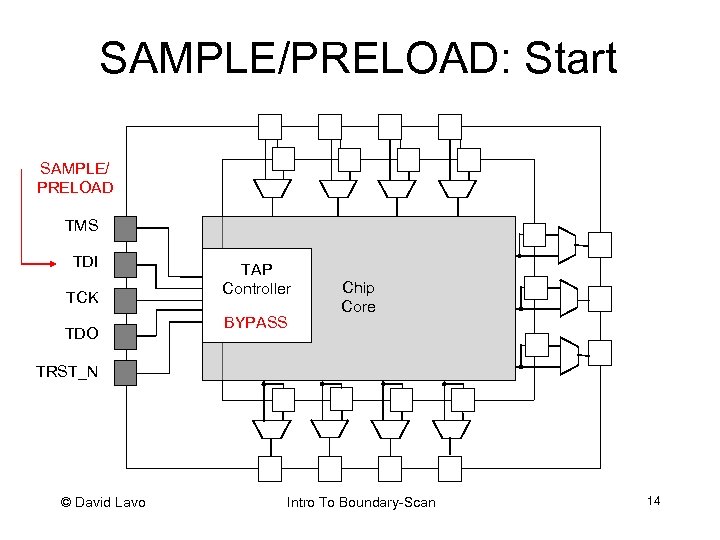

EXTEST & SAMPLE/PRELOAD • EXTEST is the “workhorse” JTAG instruction – Sample (“Capture”) & Drive (“Update”) output signals – Sample & optionally drive input signals • Data is first loaded into boundary register chain with SAMPLE/PRELOAD instruction – Samples inputs and outputs, pass-through – Loads boundary register with data © David Lavo Intro To Boundary-Scan 13

SAMPLE/PRELOAD: Start SAMPLE/ PRELOAD TMS TDI TCK TDO TAP Controller BYPASS Chip Core TRST_N © David Lavo Intro To Boundary-Scan 14

1 TAP Controller State Diagram Test-Logic-Reset 0 Run-Test/Idle 1 1 Select-DR-Scan 0 Select-IR-Scan 0 1 0 Capture-DR 0 1 0 0 Shift-DR Capture-IR Shift-IR 1 1 Exit 1 -DR Exit 1 -IR 0 Pause-DR 0 0 1 0 Exit 2 -DR Exit 2 -IR 1 1 Update-DR 1 © David Lavo 0 Pause-IR 1 0 0 0 Intro To Boundary-Scan Update-IR 1 0 15

Instruction Register Data Path SO SI TDI Bypass Reg. Instruction Register TMS TCK Finite State Machine Instruction Decode TRST_N TDO © David Lavo Intro To Boundary-Scan 16

1 TAP Controller State Diagram Test-Logic-Reset 0 Run-Test/Idle 1 1 Select-DR-Scan 0 Select-IR-Scan 0 1 0 Capture-DR 0 1 0 0 Shift-DR Capture-IR Shift-IR 1 1 Exit 1 -DR Exit 1 -IR 0 Pause-DR 0 0 1 0 Exit 2 -DR Exit 2 -IR 1 1 Update-DR 1 © David Lavo 0 Pause-IR 1 0 0 0 Intro To Boundary-Scan Update-IR 1 0 17

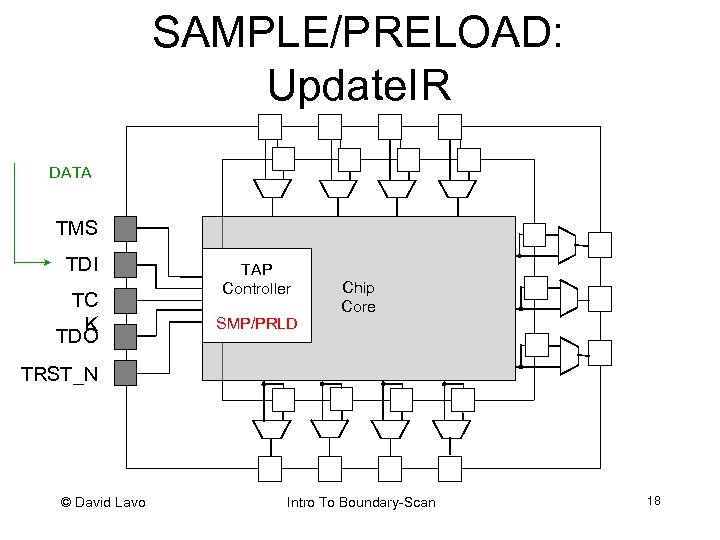

SAMPLE/PRELOAD: Update. IR SAMPLE/ DATA PRELOAD TMS TDI TC K TDO TAP Controller SMP/PRLD BYPASS Chip Core TRST_N © David Lavo Intro To Boundary-Scan 18

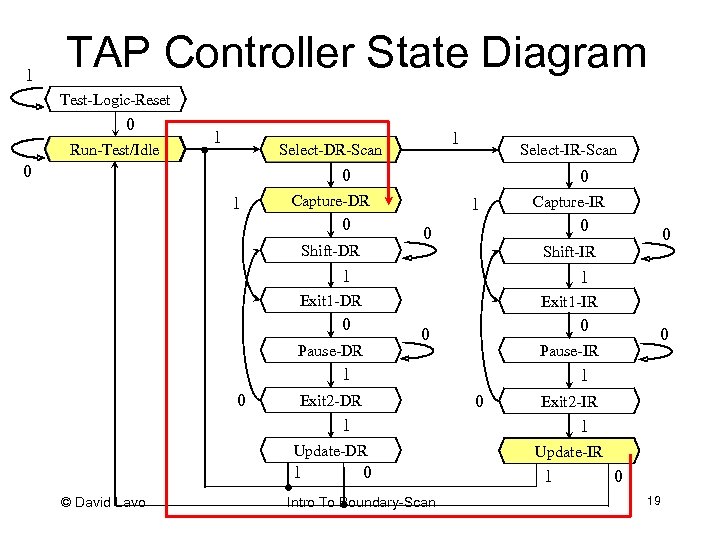

1 TAP Controller State Diagram Test-Logic-Reset 0 Run-Test/Idle 1 1 Select-DR-Scan 0 Select-IR-Scan 0 1 0 Capture-DR 0 1 0 0 Shift-DR Capture-IR Shift-IR 1 1 Exit 1 -DR Exit 1 -IR 0 Pause-DR 0 0 1 0 Exit 2 -DR Exit 2 -IR 1 1 Update-DR 1 © David Lavo 0 Pause-IR 1 0 0 0 Intro To Boundary-Scan Update-IR 1 0 19

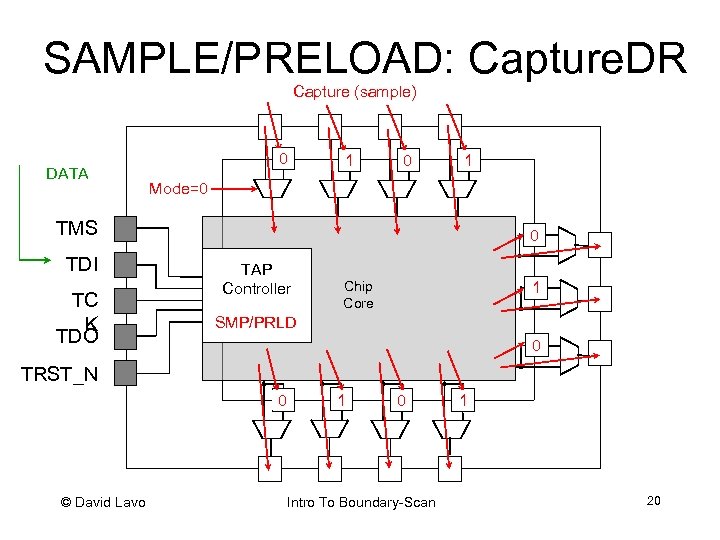

SAMPLE/PRELOAD: Capture. DR Capture (sample) DATA 0 1 Mode=0 TMS TDI TC K TDO 0 TAP Controller Chip Core 1 SMP/PRLD 0 TRST_N 0 © David Lavo 1 0 Intro To Boundary-Scan 1 20

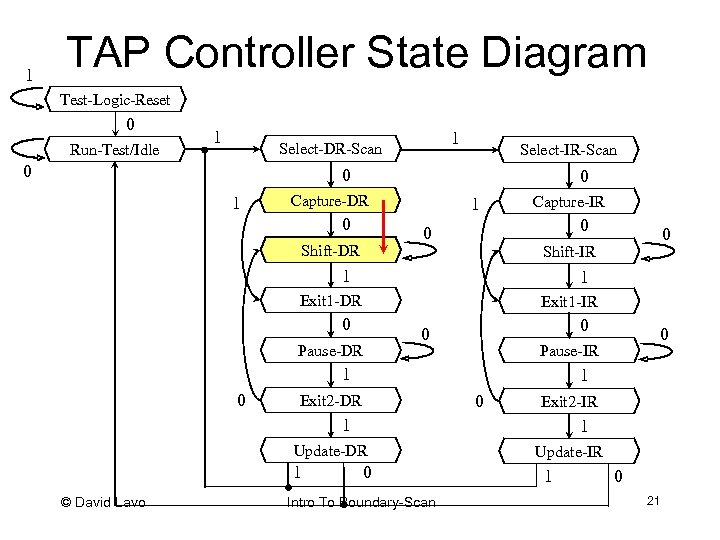

1 TAP Controller State Diagram Test-Logic-Reset 0 Run-Test/Idle 1 1 Select-DR-Scan 0 Select-IR-Scan 0 1 0 Capture-DR 0 1 0 0 Shift-DR Capture-IR Shift-IR 1 1 Exit 1 -DR Exit 1 -IR 0 Pause-DR 0 0 1 0 Exit 2 -DR Exit 2 -IR 1 1 Update-DR 1 © David Lavo 0 Pause-IR 1 0 0 0 Intro To Boundary-Scan Update-IR 1 0 21

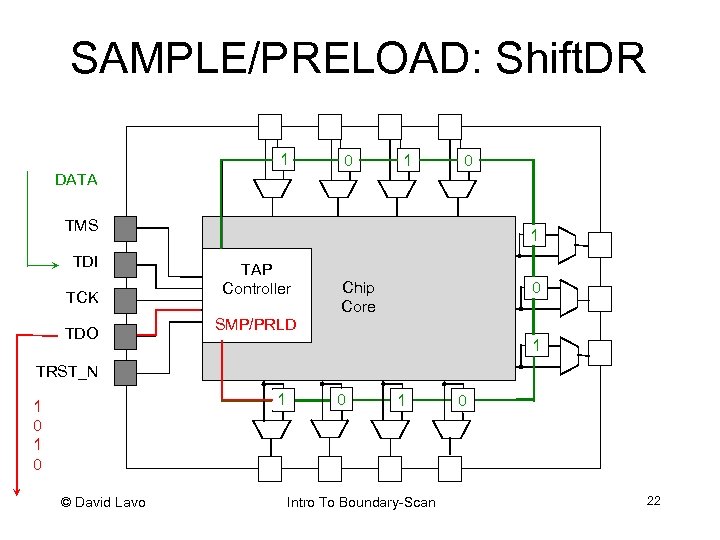

SAMPLE/PRELOAD: Shift. DR 0 1 1 0 DATA TMS TDI TCK TDO 1 0 TAP Controller Chip Core 0 1 SMP/PRLD 1 0 TRST_N 1 0 1 0 © David Lavo 0 1 Intro To Boundary-Scan 1 0 22

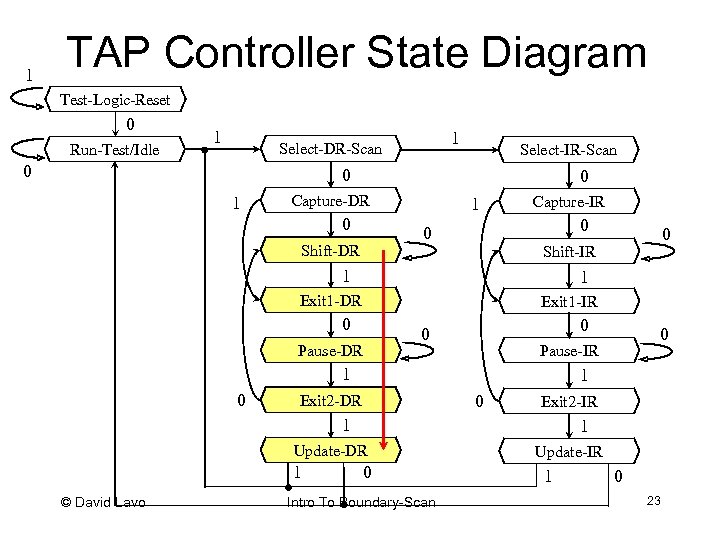

1 TAP Controller State Diagram Test-Logic-Reset 0 Run-Test/Idle 1 1 Select-DR-Scan 0 Select-IR-Scan 0 1 0 Capture-DR 0 1 0 0 Shift-DR Capture-IR Shift-IR 1 1 Exit 1 -DR Exit 1 -IR 0 Pause-DR 0 0 1 0 Exit 2 -DR Exit 2 -IR 1 1 Update-DR 1 © David Lavo 0 Pause-IR 1 0 0 0 Intro To Boundary-Scan Update-IR 1 0 23

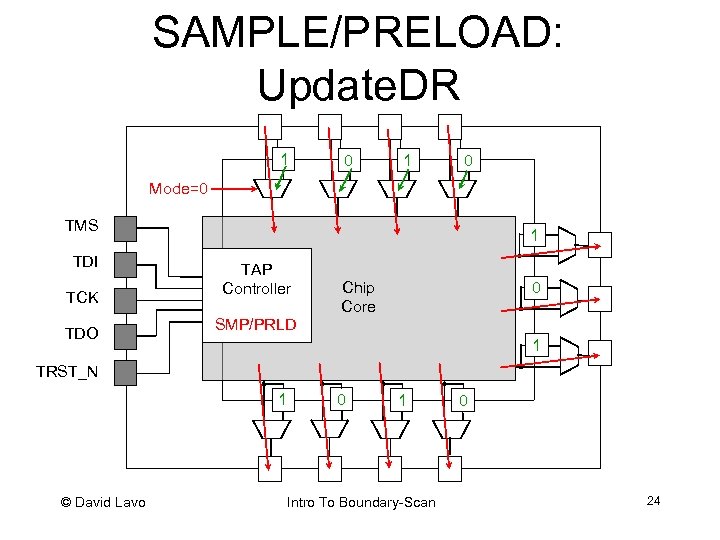

SAMPLE/PRELOAD: Update. DR 1 0 Mode=0 TMS TDI TCK TDO 1 TAP Controller Chip Core 0 SMP/PRLD 1 TRST_N 1 © David Lavo 0 1 Intro To Boundary-Scan 0 24

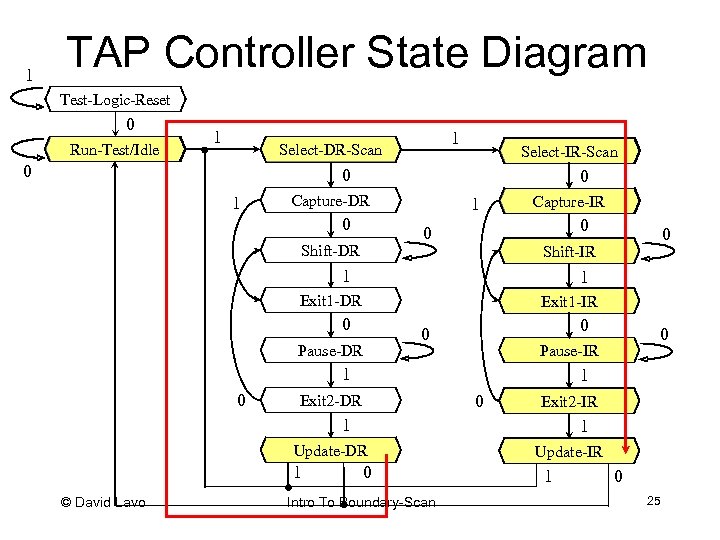

1 TAP Controller State Diagram Test-Logic-Reset 0 Run-Test/Idle 1 1 Select-DR-Scan 0 Select-IR-Scan 0 1 0 Capture-DR 0 1 0 0 Shift-DR Capture-IR Shift-IR 1 1 Exit 1 -DR Exit 1 -IR 0 Pause-DR 0 0 1 0 Exit 2 -DR Exit 2 -IR 1 1 Update-DR 1 © David Lavo 0 Pause-IR 1 0 0 0 Intro To Boundary-Scan Update-IR 1 0 25

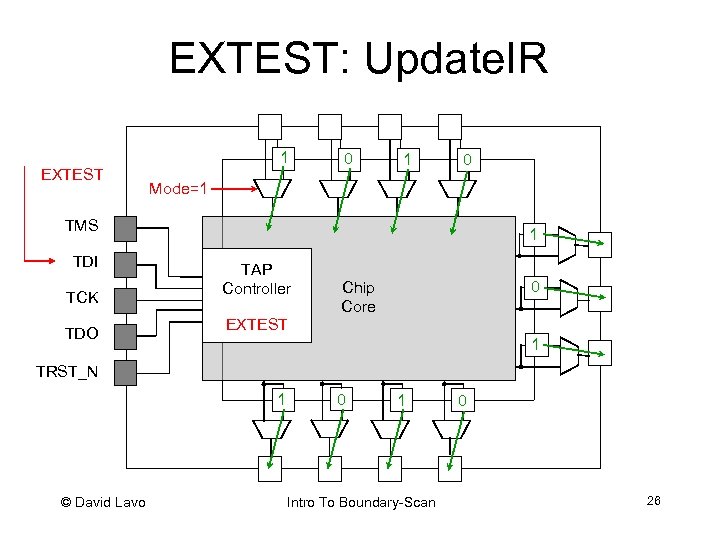

EXTEST: Update. IR EXTEST 1 0 Mode=1 TMS TDI TCK TDO 1 TAP Controller 0 Chip Core EXTEST 1 TRST_N 1 © David Lavo 0 1 Intro To Boundary-Scan 0 26

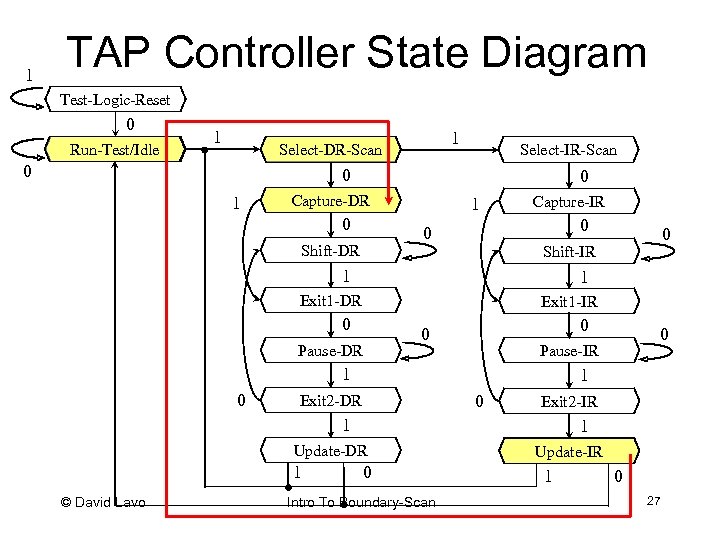

1 TAP Controller State Diagram Test-Logic-Reset 0 Run-Test/Idle 1 1 Select-DR-Scan 0 Select-IR-Scan 0 1 0 Capture-DR 0 1 0 0 Shift-DR Capture-IR Shift-IR 1 1 Exit 1 -DR Exit 1 -IR 0 Pause-DR 0 0 1 0 Exit 2 -DR Exit 2 -IR 1 1 Update-DR 1 © David Lavo 0 Pause-IR 1 0 0 0 Intro To Boundary-Scan Update-IR 1 0 27

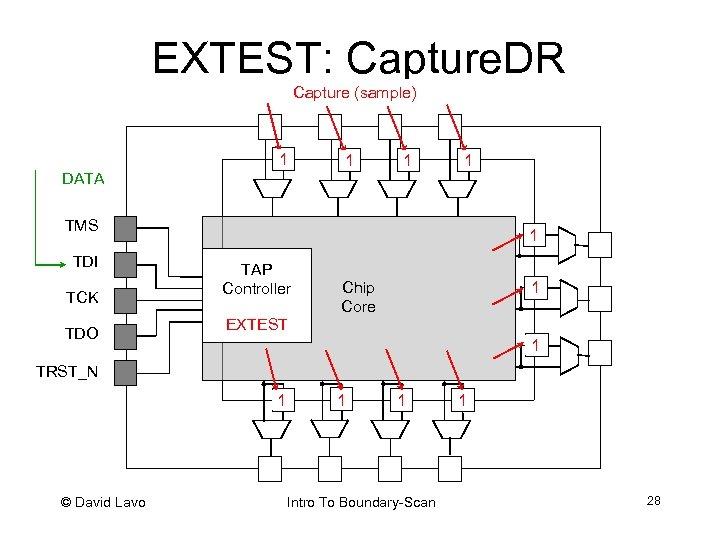

EXTEST: Capture. DR Capture (sample) 1 DATA 0 1 1 0 1 TMS TDI TCK TDO 1 TAP Controller 0 1 Chip Core EXTEST 1 TRST_N 1 © David Lavo 0 1 1 Intro To Boundary-Scan 1 0 28

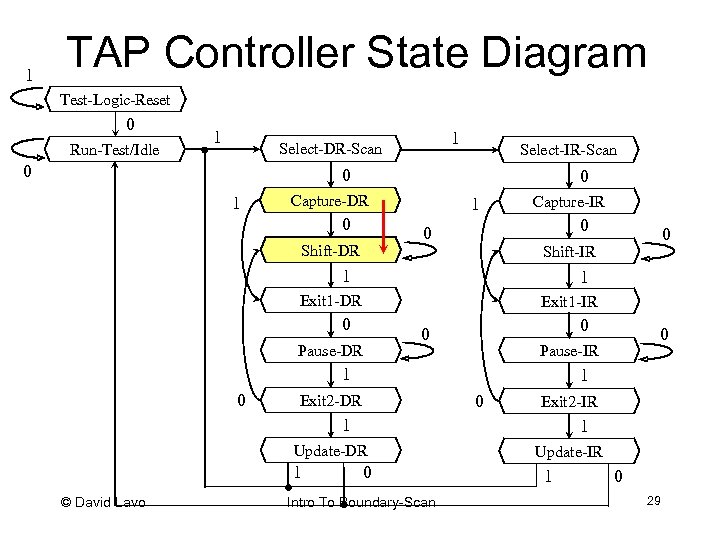

1 TAP Controller State Diagram Test-Logic-Reset 0 Run-Test/Idle 1 1 Select-DR-Scan 0 Select-IR-Scan 0 1 0 Capture-DR 0 1 0 0 Shift-DR Capture-IR Shift-IR 1 1 Exit 1 -DR Exit 1 -IR 0 Pause-DR 0 0 1 0 Exit 2 -DR Exit 2 -IR 1 1 Update-DR 1 © David Lavo 0 Pause-IR 1 0 0 0 Intro To Boundary-Scan Update-IR 1 0 29

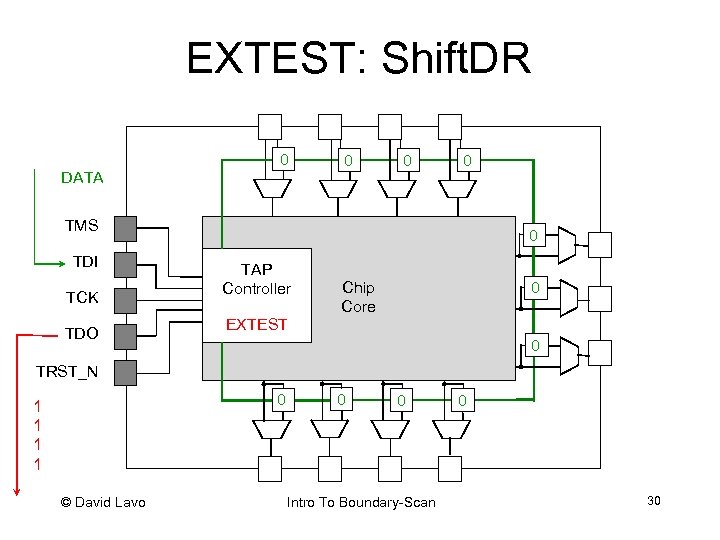

EXTEST: Shift. DR 0 1 DATA 0 1 0 1 TMS TDI TCK TDO 0 1 TAP Controller Chip Core 0 1 EXTEST 0 1 TRST_N 0 1 1 1 © David Lavo 0 1 Intro To Boundary-Scan 0 1 30

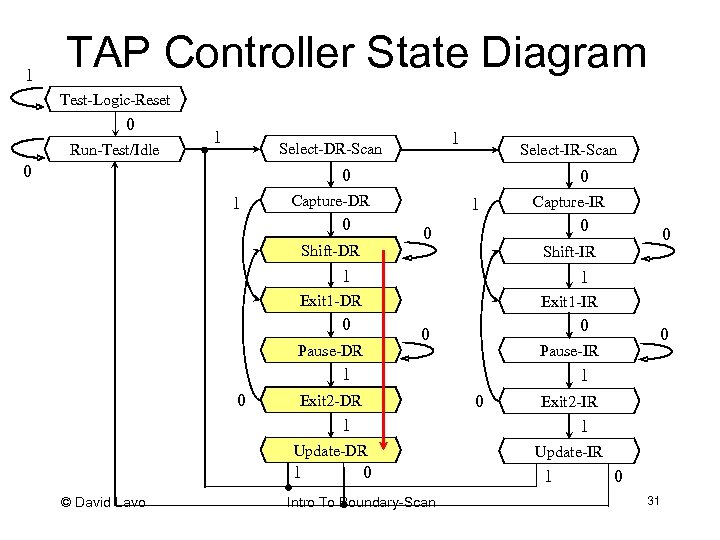

1 TAP Controller State Diagram Test-Logic-Reset 0 Run-Test/Idle 1 1 Select-DR-Scan 0 Select-IR-Scan 0 1 0 Capture-DR 0 1 0 0 Shift-DR Capture-IR Shift-IR 1 1 Exit 1 -DR Exit 1 -IR 0 Pause-DR 0 0 1 0 Exit 2 -DR Exit 2 -IR 1 1 Update-DR 1 © David Lavo 0 Pause-IR 1 0 0 0 Intro To Boundary-Scan Update-IR 1 0 31

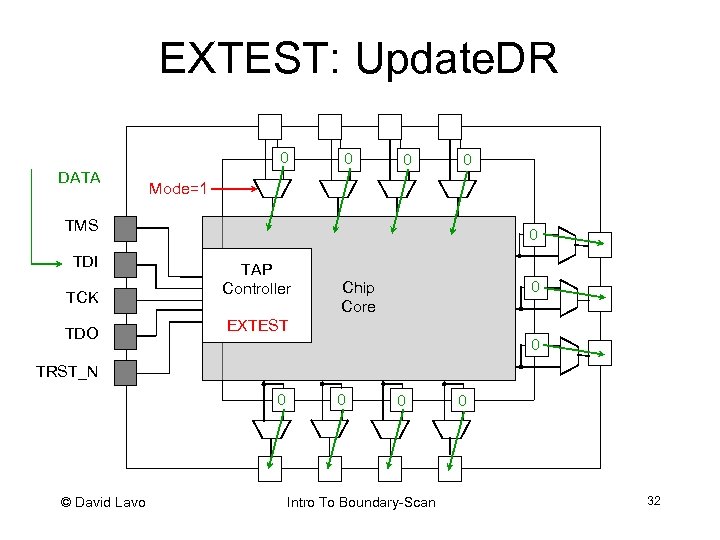

EXTEST: Update. DR 0 DATA 0 0 0 Mode=1 TMS TDI TCK TDO 0 TAP Controller 0 Chip Core EXTEST 0 TRST_N 0 © David Lavo 0 0 Intro To Boundary-Scan 0 32

Outline • • • What is 1149. 1? 1149. 1 Basics Documentation & Resources 1149. 1 for the Designer Extended Uses for the TAP Controller © David Lavo Intro To Boundary-Scan 33

Boundary-Scan Documentation • IEEE Standard: – IEEE Std 1149. 1 -1990 & 1149. 1 a-1993: “IEEE Standard Test Access Port and Boundary-Scan Architecture” – IEEE Std 1149. 1 b-1994: “Supplement to IEEE Std 1149. 1 -1990 …. ” (BDSL) – IEEE Std 1149. 1 -2001 • “The Boundary-Scan Handbook”, Second Edition (1998), by Ken Parker © David Lavo Intro To Boundary-Scan 34

Outline • • • What is 1149. 1? 1149. 1 Basics Documentation & Resources 1149. 1 for the Designer Extended Uses for the TAP Controller © David Lavo Intro To Boundary-Scan 35

Why JTAG is Cool • Adds a lot of test functionality with a small amount of effort – Board test – Pad/parametric test – Enhanced debug and diagnosis – Control of TAP-based tests (BIST, clocks) • Functionally simple • Ultra low performance: 5 to 10 MHz! © David Lavo Intro To Boundary-Scan 36

Lots of Uses Besides Board Test • On-chip access to BIST, programmable logic & EEPROMs, system and circuit test • System configuration & maintenance: © David Lavo Intro To Boundary-Scan 37

Why JTAG is a Pain • Messes with chip timing! • Complicates placement and routing • Obtuse rules, motivations, language and documentation • Requires some manual data entry or massaging • No automated debugging tools © David Lavo Intro To Boundary-Scan 38

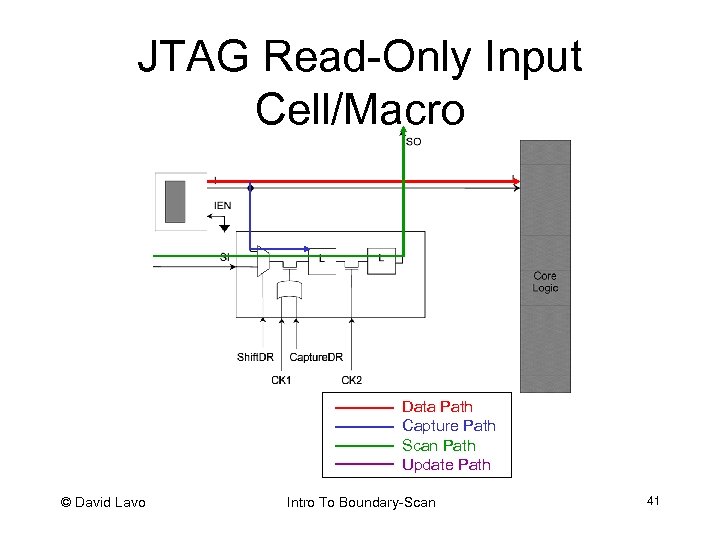

1149. 1 Timing Impact • JTAG adds a mux, and sometimes a gate, into the data path – Insert JTAG early in design process! • The impact can be reduced to just a load by using a “read-only” cell – Intended only for clocks and other sensitive inputs – Some test capability is lost © David Lavo Intro To Boundary-Scan 39

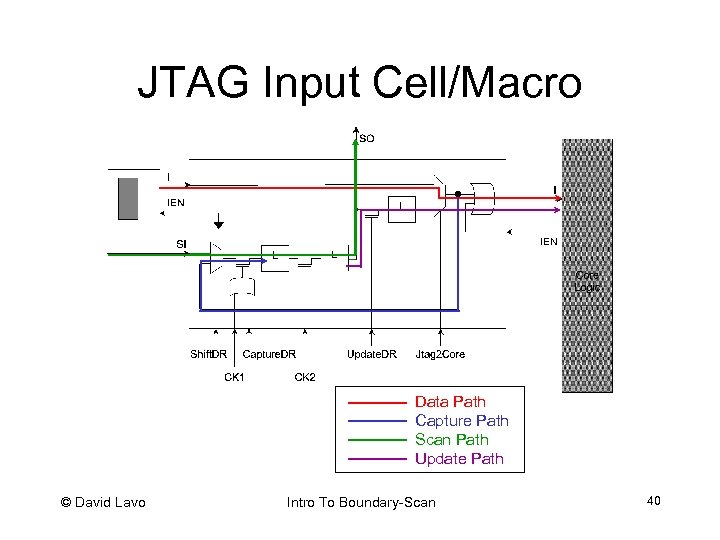

JTAG Input Cell/Macro Data Path Capture Path Scan Path Update Path © David Lavo Intro To Boundary-Scan 40

JTAG Read-Only Input Cell/Macro Data Path Capture Path Scan Path Update Path © David Lavo Intro To Boundary-Scan 41

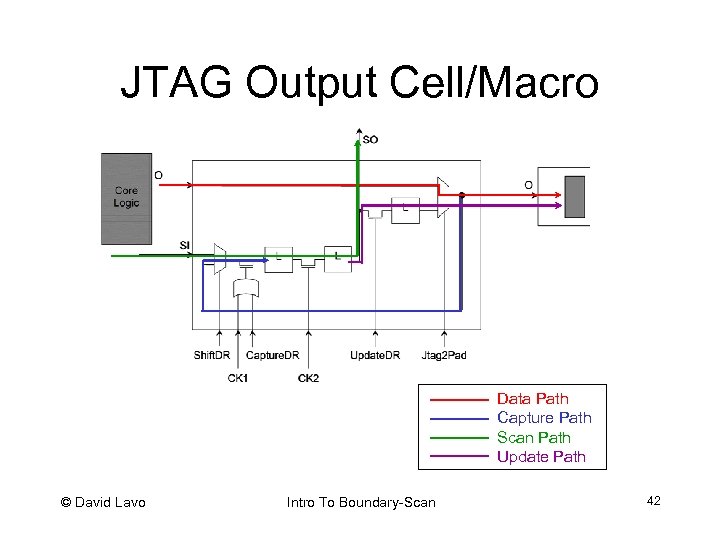

JTAG Output Cell/Macro Data Path Capture Path Scan Path Update Path © David Lavo Intro To Boundary-Scan 42

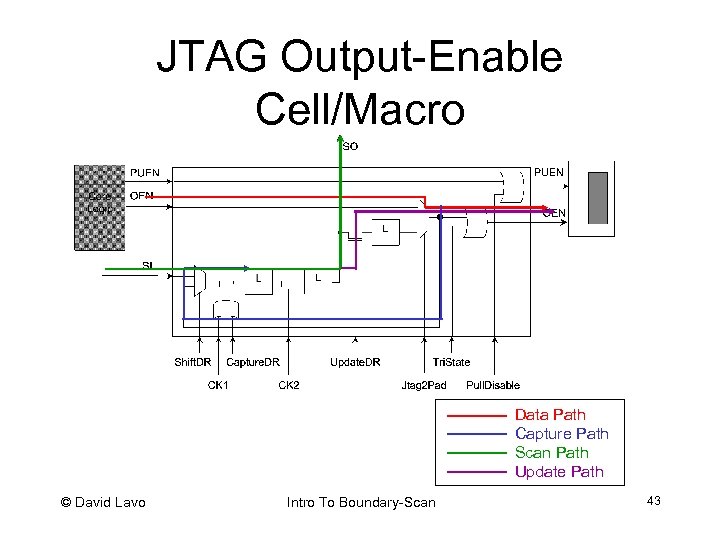

JTAG Output-Enable Cell/Macro Data Path Capture Path Scan Path Update Path © David Lavo Intro To Boundary-Scan 43

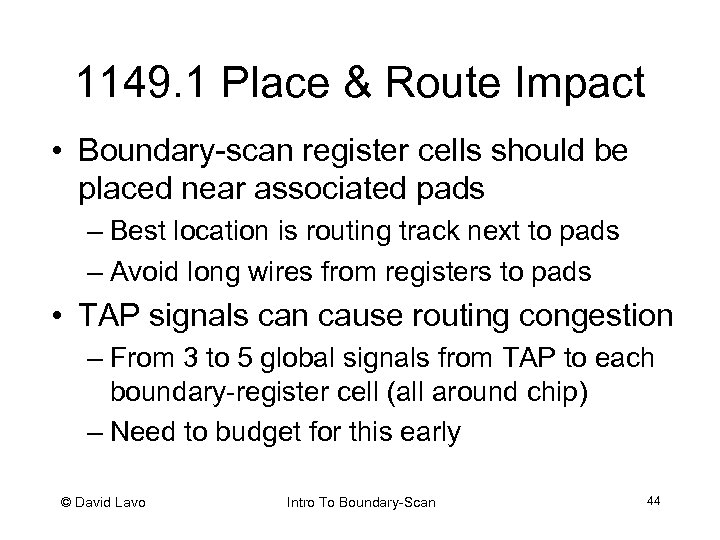

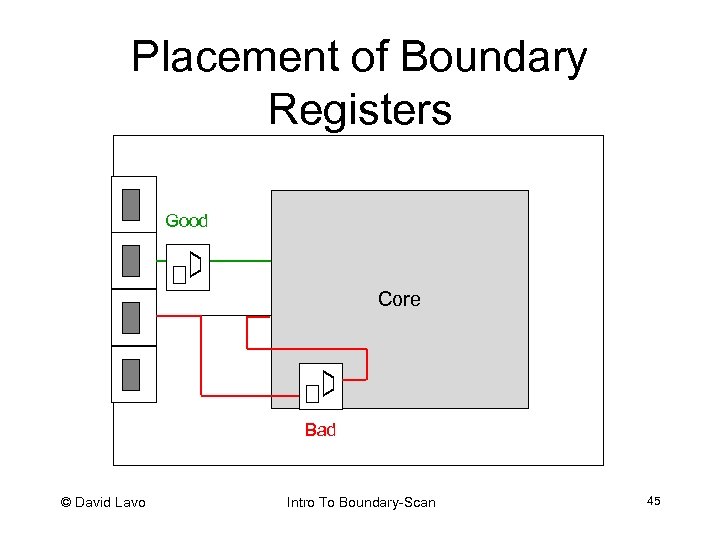

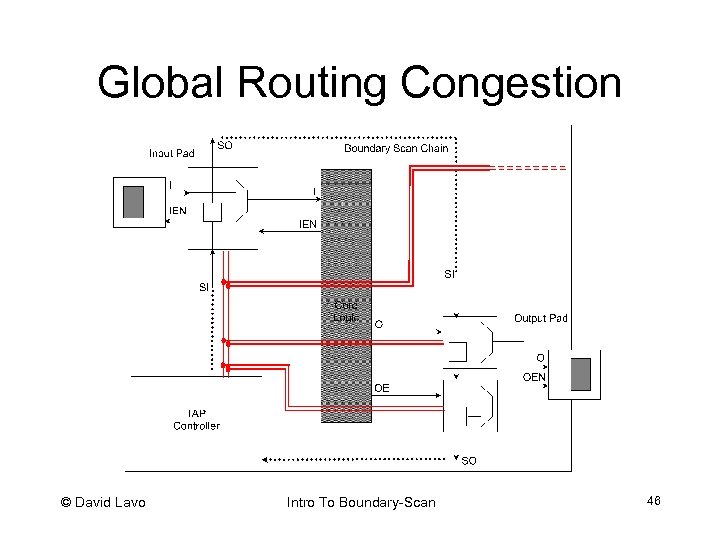

1149. 1 Place & Route Impact • Boundary-scan register cells should be placed near associated pads – Best location is routing track next to pads – Avoid long wires from registers to pads • TAP signals can cause routing congestion – From 3 to 5 global signals from TAP to each boundary-register cell (all around chip) – Need to budget for this early © David Lavo Intro To Boundary-Scan 44

Placement of Boundary Registers Good Core Bad © David Lavo Intro To Boundary-Scan 45

Global Routing Congestion © David Lavo Intro To Boundary-Scan 46

Outline • • • What is 1149. 1? 1149. 1 Basics Documentation & Resources 1149. 1 for the Designer Extended Uses for the TAP Controller © David Lavo Intro To Boundary-Scan 47

Beyond Board-Test: Extending the TAP Controller • The TAP Controller runs the show for boundary-scan and other TAP-based tests • Some TAP-based test functions have become increasingly complex & specialized – Test signal control – BIST control and capture – Scan shifting • Most functions are based on TAP registers © David Lavo Intro To Boundary-Scan 48

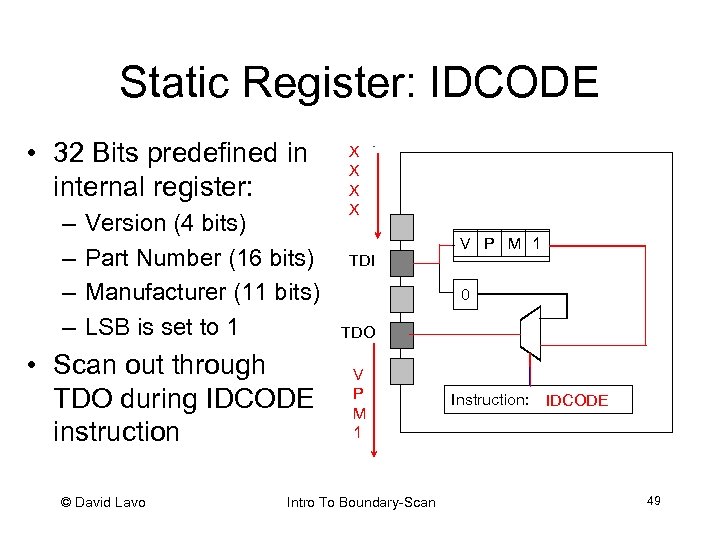

Static Register: IDCODE • 32 Bits predefined in internal register: – – Version (4 bits) Part Number (16 bits) Manufacturer (11 bits) LSB is set to 1 • Scan out through TDO during IDCODE instruction © David Lavo 1 X 0 X TDI V P M 1 0 TDO 1 V 0 P 1 M 0 1 0 Intro To Boundary-Scan Instruction: BYPASS IDCODE 49

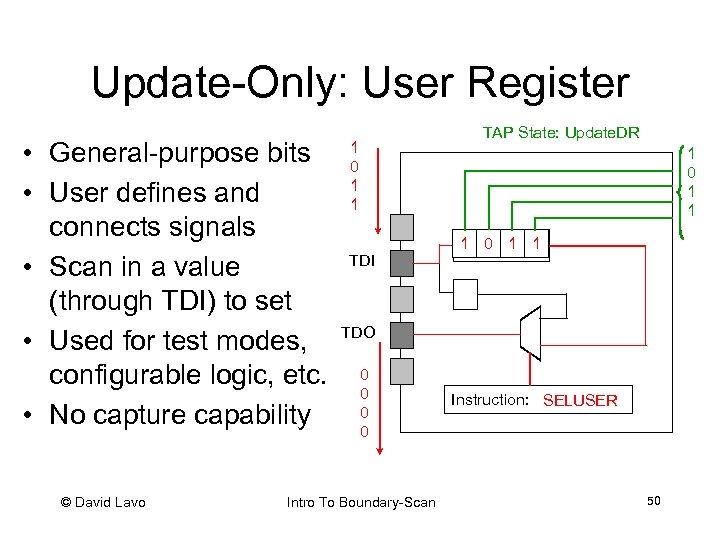

Update-Only: User Register • General-purpose bits • User defines and connects signals • Scan in a value (through TDI) to set • Used for test modes, configurable logic, etc. • No capture capability © David Lavo TAP State: Update. DR 1 0 1 0 0 0 1 TDI 0 0 0 1 1 TDO 0 0 Intro To Boundary-Scan Instruction: SELUSER 50

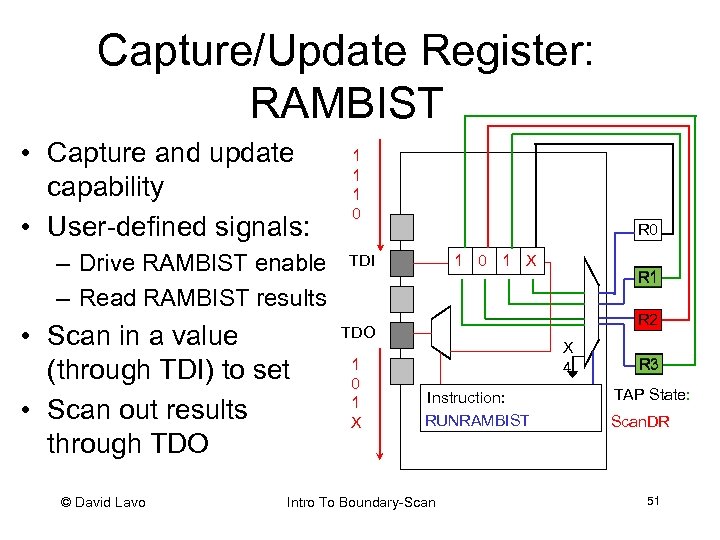

Capture/Update Register: RAMBIST • Capture and update capability • User-defined signals: – Drive RAMBIST enable – Read RAMBIST results • Scan in a value (through TDI) to set • Scan out results through TDO © David Lavo 1 1 1 0 R 0 TDI 1 0 1 X 1 1 0 R 2 TDO 1 0 1 X R 1 X 4 Instruction: SELRAMBIST RUNRAMBIST Intro To Boundary-Scan R 3 TAP State: Scan. DR Update. DR Run. Test Capture. DR Scan. DR 51

95e9643cf0a3cd152aea8b69571779cf.ppt