4561ffe892f5f6baa5d2cd2a367e6faa.ppt

- Количество слайдов: 21

Interrupt Driven I/O • References Text: Tanenbaum ch. 1. 4. 3, ch. 5. 1. 5 Receiver Interrupt Program Example: $pcex/typewr. c

Interrupts • What is an interrupt? • What does an interrupt do to the “flow of control” • Interrupts used to overlap computation & I/O – • Examples would be console I/O, printer output, and disk accesses Normally handled by the OS. Thus under UNIX and NT, rarely coded by ordinary programmers. – In embedded systems and real-time systems, part of the normal programming work. 2

Interrupts (Cont’d) • Why interrupts over polling? Because polling – – – • Ties up the CPU in one activity Uses cycles that could be used more effectively Code can’t be any faster than the tightest polling loop Bottom line: an interrupt is an asynchronous subroutine call (triggered by a hardware event) that saves both the return address and the system status 3

When an Interrupt Occurs • Finish the current instruction • Save minimal state information on stack • Transfer to the interrupt handler, also known as the interrupt service routine (ISR) But there is more to it than this…How do we know which device interrupted? • And what happens if two (or more) devices request an interrupt at the same time? 4

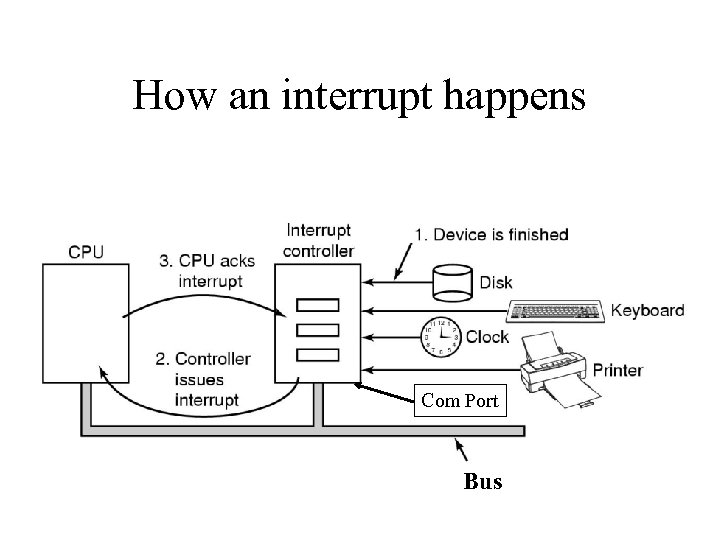

How an interrupt happens Com Port Bus

x 86 Interrupts • Interrupt signals go from device to the PIC and to CPU • All 3 signals are on the bus • Program the PIC and device using IN or OUT instructions on certain I/O port address, e. g. PIC : 0 x 20 and 0 x 21 COM 2: 0 x 2 f 8, 0 x 2 f 9 …

x 86 Interrupts (cont’d) • UART receives a character and signals an interrupt on a bus line. • Interrupt Controller detects the signal. If no pending interrupts are pending, it services the interrupt immediately. • If another one is in progress or a higher priority one is pending, the device is ignored. It continues to assert the interrupt signal until it is serviced. • To handle the interrupt, the controller puts an interrupt vector number (e. g 0 x 23 for COM 2) on the data bus and asserts a signal (INTR)to interrupt the CPU.

x 86 Interrupts (cont’d) • CPU stops what it is doing and starts doing something else. • CPU uses the interrupt vector number to index the IDT (interrupt descriptor table) and find the interrupt vector (i. e. address of the interrupt service routine) • CPU runs the service routine which includes writing a certain value(EOI) to the interrupt controller’s I/O port to ack the interrupt

Saving the Context • The hardware saves certain info before the service procedure. • Info saved depends on the CPU. Saving the Program counter is the minimum. Some saves internal registers. • Most of the CPUs save info on the stack.

Programmable Interrupt Controller (PIC) • Programmable means it has multiple possible behaviors selectable by software (via its own I/O ports) • Devices send IRQ signals to interrupt controller • Interrupt controller prioritizes signals, sending highest to CPU 10

Interrupt Controller Details • Each device has an IRQ number based on its wiring to the PIC – Ex. COM 2 uses IRQ 3, timer 0 uses IRQ 0 • PIC: the 8259 A chip – Supports eight interrupt request (IRQ) lines – Two chips used in PC, called “master” and “slave” – Priority: highest to lowest order is IRQ 0 -1, IRQ 8 -15, IRQ 3 -7 – Asserts INTR to CPU, responds to resulting INTA# with an 8 -bit interrupt type code (“nn”) on the data bus. 11

Interrupt Controller Programming • PIC is accessible at port addresses 0 x 20 and 0 x 21 (for master), using “initialization command words” (ICWs) and “operational command words” (OCWs) • ICWs used to set such things as: – How much to add to the IRQ to produce nn (8 used for DOS, 0 x 20 for Linux, 0 x 50 for Windows) – We trust the (Linux) bootup code to handle this setup • OCWs used for: – EOI command: Reset interrupt in PIC after accepted by ISR (outb of 0 x 20 to port 0 x 20, for master) – Get/Set Interrupt Mask Register (port 0 x 21 for master) • Ex: 0111 1110 = 0 x 7 e enables IRQs 0 and 7, disables 2 -6 12

Interrupt Process • Requesting device generates a signal on IRQn • PIC checks its interrupt mask before putting out a logic high on INTR line • Between instructions, and if IF=1, the CPU sees INTR and initiates its interrupt cycle. • The interrupt handler (ISR) executes • Requesting device is usually accessed in the ISR and is thus notified of the completion of the event – Ex: UART receiver detects inb for received char 13

CPU’s interrupt cycle • CPU detects INTR between instructions with IF=1 • CPU sends back a low on INTA# • PIC responds by setting INTR low and puts out 8 bit interrupt code, nn, on data lines • CPU reads nn and executes int nn instruction: – – Machine state saved on stack (cs: eip and eflags) IF set to zero Access IDT[nn] to obtain ISR address loaded in eip • Causing the interrupt handler to execute next 14

Interrupt Handler Details – ISR must • Save all registers used • Issue EOI command (end-of-interrupt) to PIC • Service the device, i. e. , do whatever processing is needed for the event the device was signaling – Ex. Read the received character, for UART receiver int’s • Restore registers • Finish with iret instruction. 15

UART Interrupts • The UART is a real I/O device, more typical of interrupt sources than timer 0 • The UART has four ways to interrupt, we’ll study just receiver interrupts. • No interrupts are enabled until we command the UART to enable them, via register 1, the IER (i. e port 0 x 3 f 8+1 or port 0 x 2 f 8+1) 16

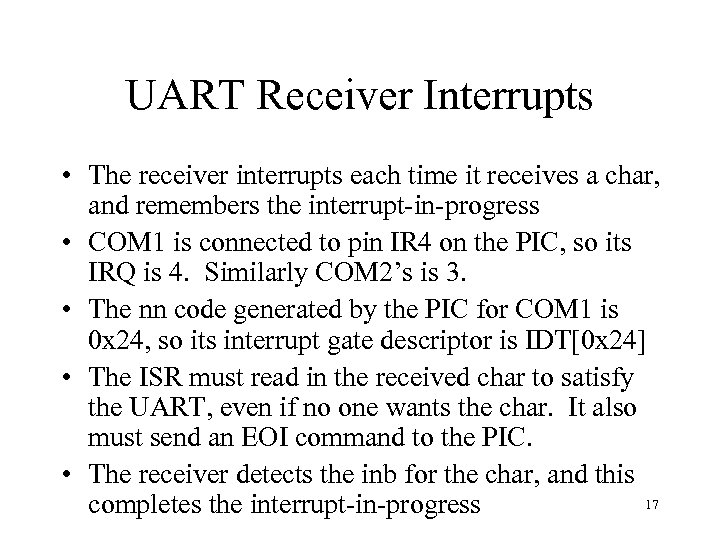

UART Receiver Interrupts • The receiver interrupts each time it receives a char, and remembers the interrupt-in-progress • COM 1 is connected to pin IR 4 on the PIC, so its IRQ is 4. Similarly COM 2’s is 3. • The nn code generated by the PIC for COM 1 is 0 x 24, so its interrupt gate descriptor is IDT[0 x 24] • The ISR must read in the received char to satisfy the UART, even if no one wants the char. It also must send an EOI command to the PIC. • The receiver detects the inb for the char, and this 17 completes the interrupt-in-progress

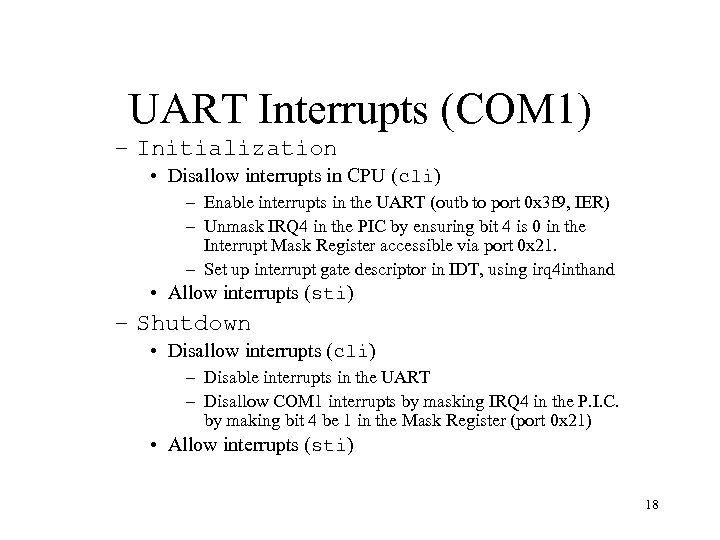

UART Interrupts (COM 1) – Initialization • Disallow interrupts in CPU (cli) – Enable interrupts in the UART (outb to port 0 x 3 f 9, IER) – Unmask IRQ 4 in the PIC by ensuring bit 4 is 0 in the Interrupt Mask Register accessible via port 0 x 21. – Set up interrupt gate descriptor in IDT, using irq 4 inthand • Allow interrupts (sti) – Shutdown • Disallow interrupts (cli) – Disable interrupts in the UART – Disallow COM 1 interrupts by masking IRQ 4 in the P. I. C. by making bit 4 be 1 in the Mask Register (port 0 x 21) • Allow interrupts (sti) 18

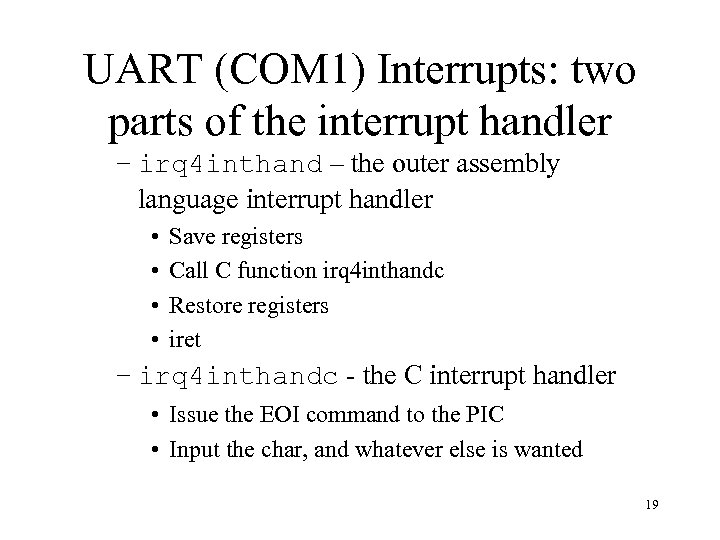

UART (COM 1) Interrupts: two parts of the interrupt handler – irq 4 inthand – the outer assembly language interrupt handler • • Save registers Call C function irq 4 inthandc Restore registers iret – irq 4 inthandc - the C interrupt handler • Issue the EOI command to the PIC • Input the char, and whatever else is wanted 19

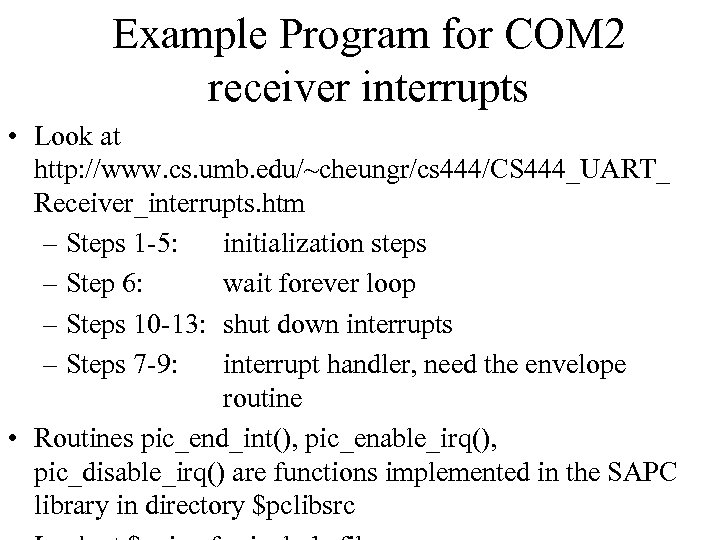

Example Program for COM 2 receiver interrupts • Look at http: //www. cs. umb. edu/~cheungr/cs 444/CS 444_UART_ Receiver_interrupts. htm – Steps 1 -5: initialization steps – Step 6: wait forever loop – Steps 10 -13: shut down interrupts – Steps 7 -9: interrupt handler, need the envelope routine • Routines pic_end_int(), pic_enable_irq(), pic_disable_irq() are functions implemented in the SAPC library in directory $pclibsrc

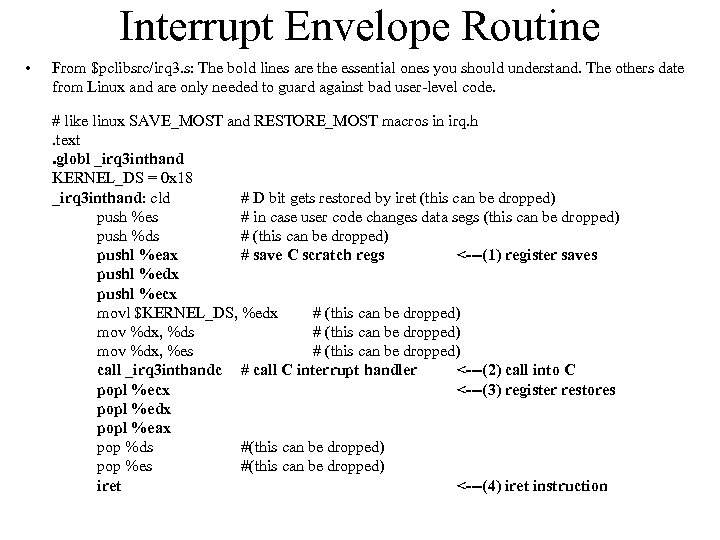

Interrupt Envelope Routine • From $pclibsrc/irq 3. s: The bold lines are the essential ones you should understand. The others date from Linux and are only needed to guard against bad user-level code. # like linux SAVE_MOST and RESTORE_MOST macros in irq. h. text. globl _irq 3 inthand KERNEL_DS = 0 x 18 _irq 3 inthand: cld # D bit gets restored by iret (this can be dropped) push %es # in case user code changes data segs (this can be dropped) push %ds # (this can be dropped) pushl %eax # save C scratch regs <---(1) register saves pushl %edx pushl %ecx movl $KERNEL_DS, %edx # (this can be dropped) mov %dx, %ds # (this can be dropped) mov %dx, %es # (this can be dropped) call _irq 3 inthandc # call C interrupt handler <---(2) call into C popl %ecx <---(3) register restores popl %edx popl %eax pop %ds #(this can be dropped) pop %es #(this can be dropped) iret <---(4) iret instruction

4561ffe892f5f6baa5d2cd2a367e6faa.ppt