49f806bef763f29b841db46415f17e23.ppt

- Количество слайдов: 25

Interpolation-Sequence Based Model Checking Yakir Vizel 1, 2 and Orna Grumberg 1 1. 2. Computer Science Department, The Technion, Haifa, Israel. Architecture, System Level and Validation Solutions, Intel Development Center, Haifa, Israel Formal Methods in Computer Aided Design, Austin, Texas 2009 1

Outline Introduction Model checking Forward Reachability Analysis Bounded Model Checking Interpolation-Sequence Based Model Checking Experimental Results Formal Methods in Computer Aided Design, Austin, Texas 2009 2

Introduction Formal Methods in Computer Aided Design, Austin, Texas 2009 3

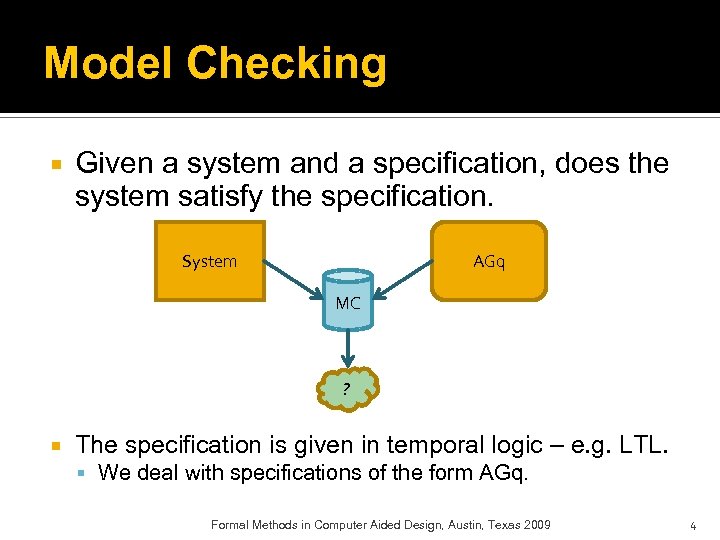

Model Checking Given a system and a specification, does the system satisfy the specification. AGq System MC ? The specification is given in temporal logic – e. g. LTL. We deal with specifications of the form AGq. Formal Methods in Computer Aided Design, Austin, Texas 2009 4

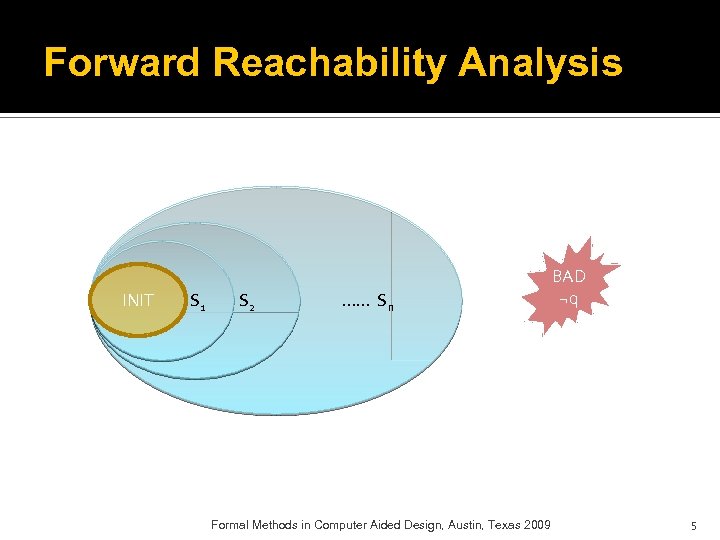

Forward Reachability Analysis INIT S 1 S 2 …… Sn Formal Methods in Computer Aided Design, Austin, Texas 2009 BAD ¬q 5

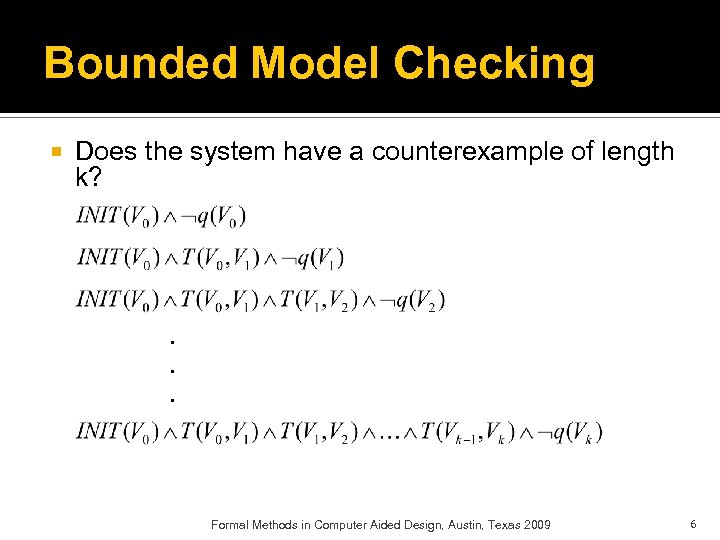

Bounded Model Checking Does the system have a counterexample of length k? . . . Formal Methods in Computer Aided Design, Austin, Texas 2009 6

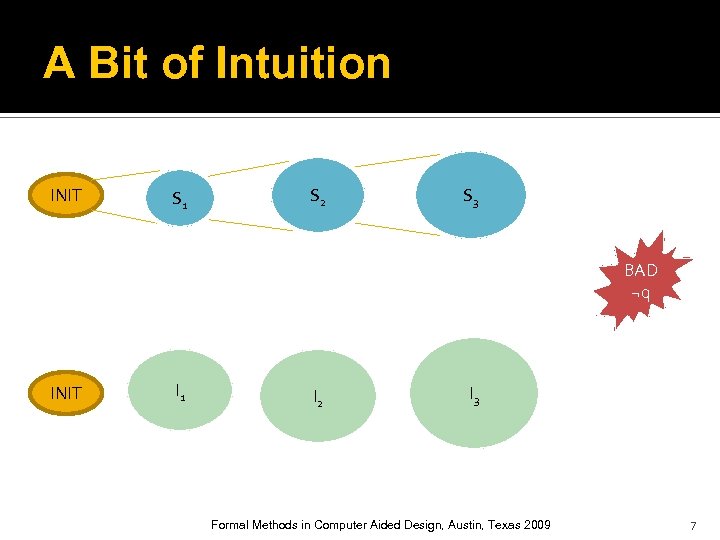

A Bit of Intuition INIT S 1 S 2 S 3 BAD ¬q INIT I 1 I 2 I 3 Formal Methods in Computer Aided Design, Austin, Texas 2009 7

Interpolation Formal Methods in Computer Aided Design, Austin, Texas 2009 8

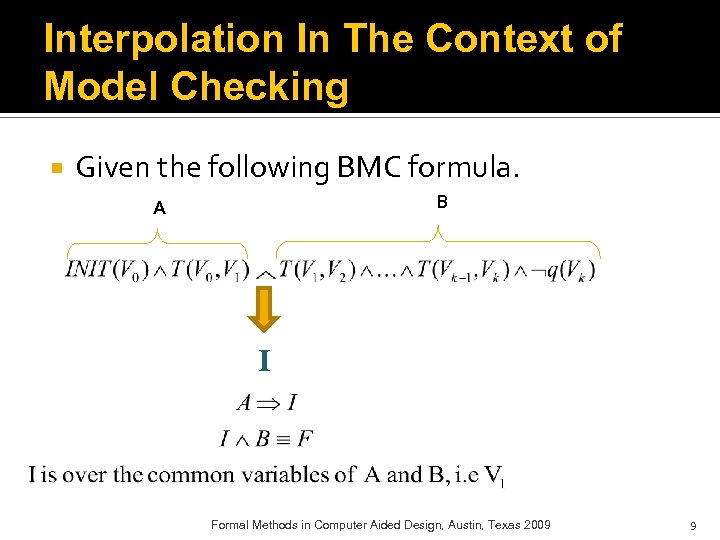

Interpolation In The Context of Model Checking Given the following BMC formula. B A I Formal Methods in Computer Aided Design, Austin, Texas 2009 9

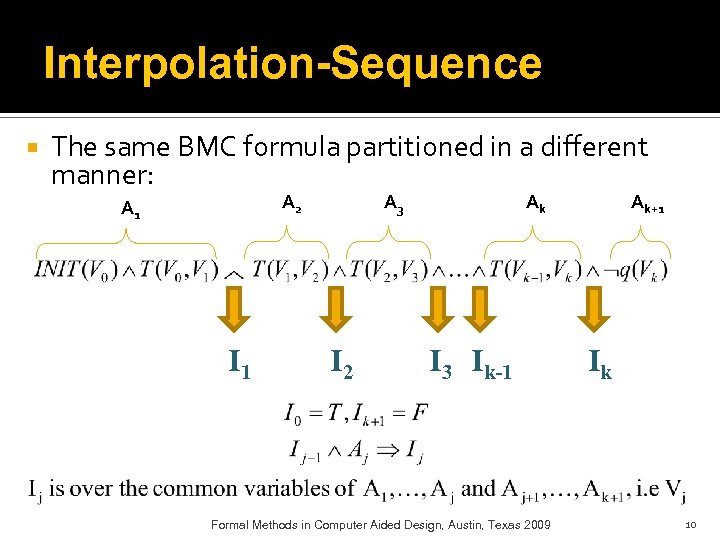

Interpolation-Sequence The same BMC formula partitioned in a different manner: A 2 A 1 I 1 A 3 I 2 Ak I 3 Ik-1 Formal Methods in Computer Aided Design, Austin, Texas 2009 Ak+1 Ik 10

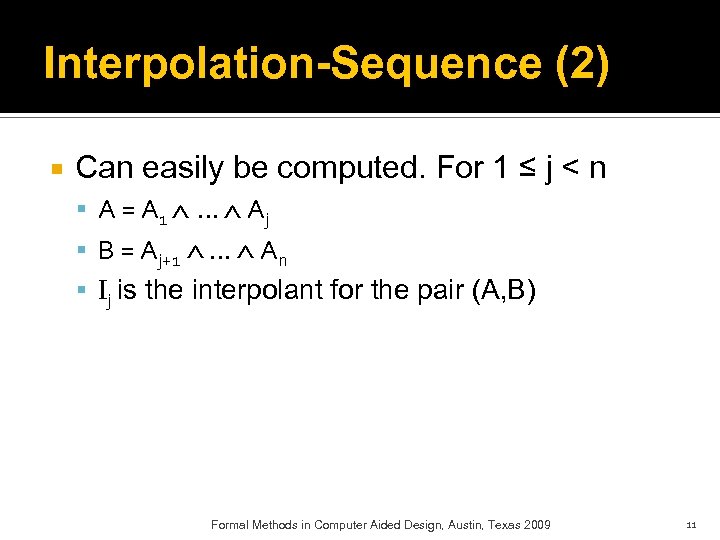

Interpolation-Sequence (2) Can easily be computed. For 1 ≤ j < n A = A 1 Ù … Ù Aj B = Aj+1 Ù … Ù An Ij is the interpolant for the pair (A, B) Formal Methods in Computer Aided Design, Austin, Texas 2009 11

Interpolation-Sequence Based Model Checking Formal Methods in Computer Aided Design, Austin, Texas 2009 12

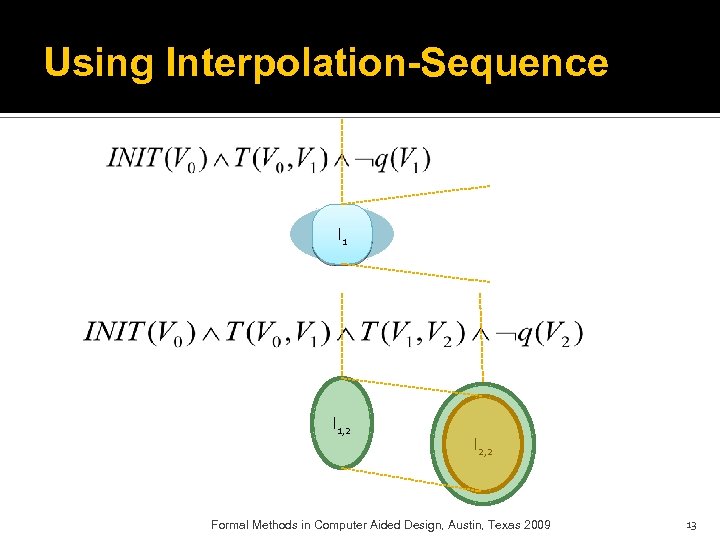

Using Interpolation-Sequence II 1 1, 1 I 1, 2 I 2, 2 Formal Methods in Computer Aided Design, Austin, Texas 2009 13

Combining Interpolation. Sequence and BMC A way to do reachability analysis using a SAT solver. Uses the original BMC loop and adds an inclusion check for full verification. Similar sets to those computed by Forward Reachability Analysis but overapproximated. Formal Methods in Computer Aided Design, Austin, Texas 2009 14

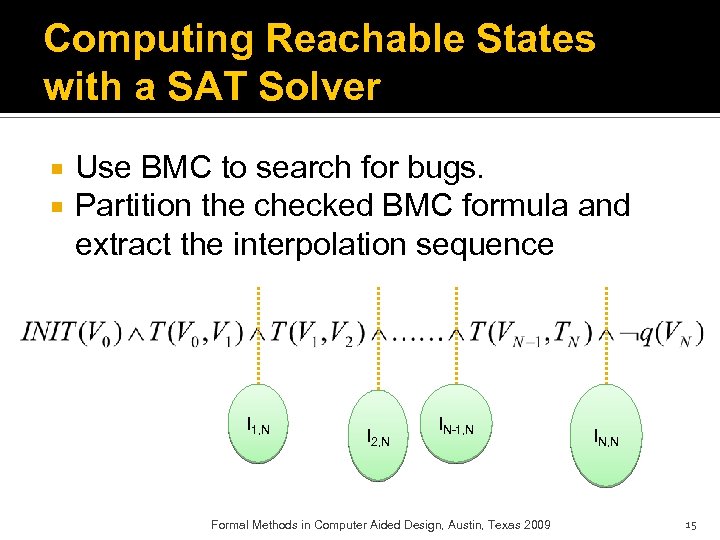

Computing Reachable States with a SAT Solver Use BMC to search for bugs. Partition the checked BMC formula and extract the interpolation sequence I 1, N I 2, N IN-1, N Formal Methods in Computer Aided Design, Austin, Texas 2009 IN, N 15

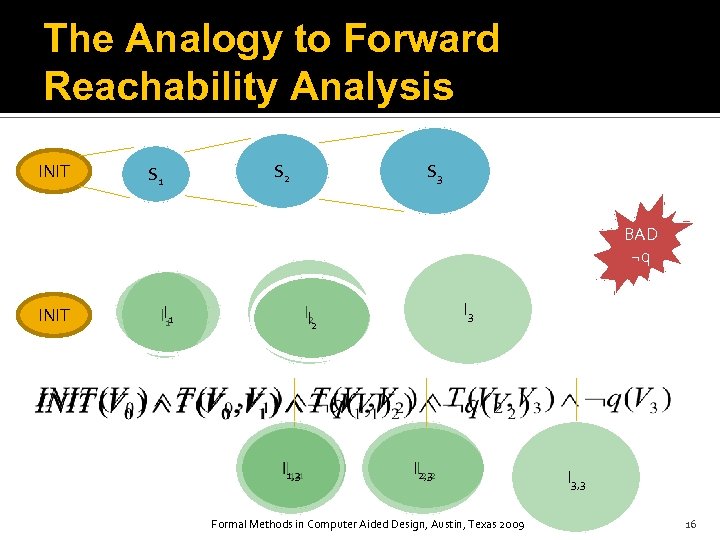

The Analogy to Forward Reachability Analysis INIT S 1 S 3 S 2 BAD ¬q INIT II 11 I 3 II 2 2 II 1, 2 1, 3 1, 1 II 2, 3 2, 2 Formal Methods in Computer Aided Design, Austin, Texas 2009 I 3, 3 16

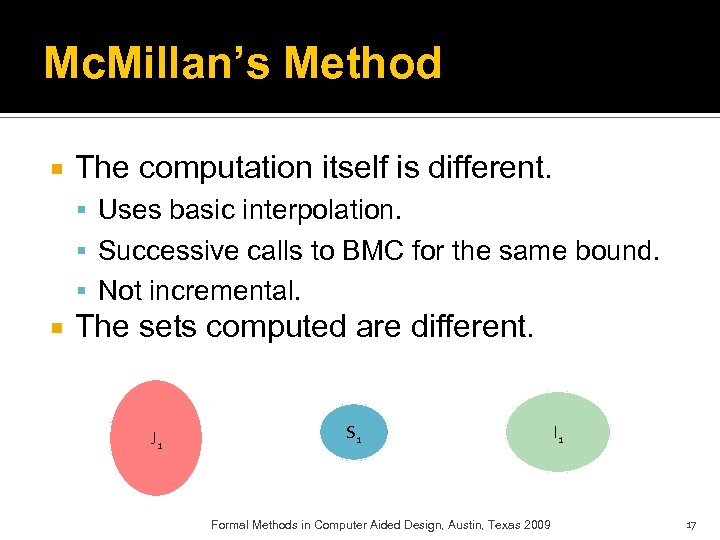

Mc. Millan’s Method The computation itself is different. Uses basic interpolation. Successive calls to BMC for the same bound. Not incremental. The sets computed are different. J 1 S 1 Formal Methods in Computer Aided Design, Austin, Texas 2009 I 1 17

Experimental Results Formal Methods in Computer Aided Design, Austin, Texas 2009 18

Experimental Results Experiments were conducted on two future CPU designs from Intel (two different architectures/tocks) Formal Methods in Computer Aided Design, Austin, Texas 2009 19

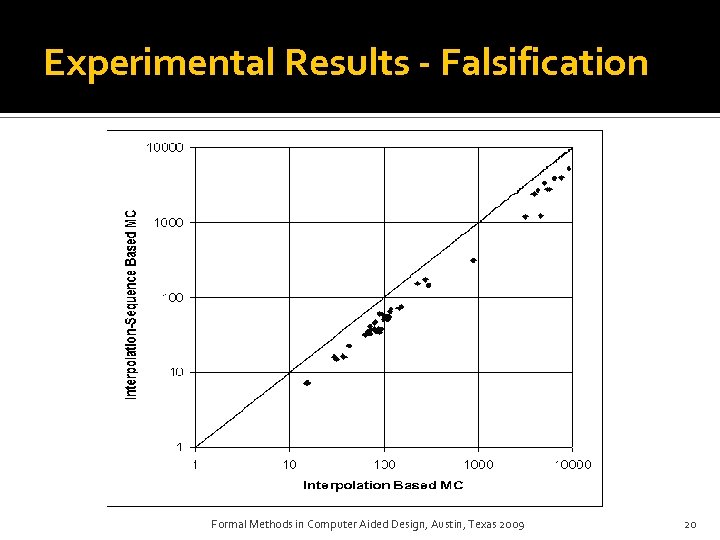

Experimental Results - Falsification Formal Methods in Computer Aided Design, Austin, Texas 2009 20

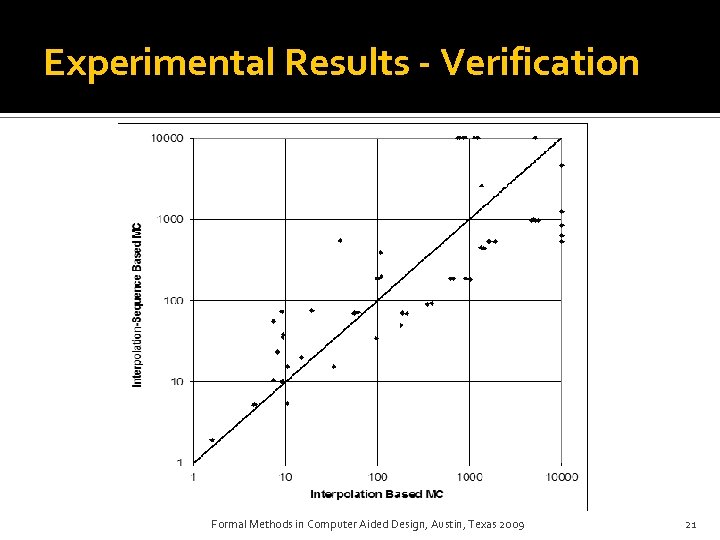

Experimental Results - Verification Formal Methods in Computer Aided Design, Austin, Texas 2009 21

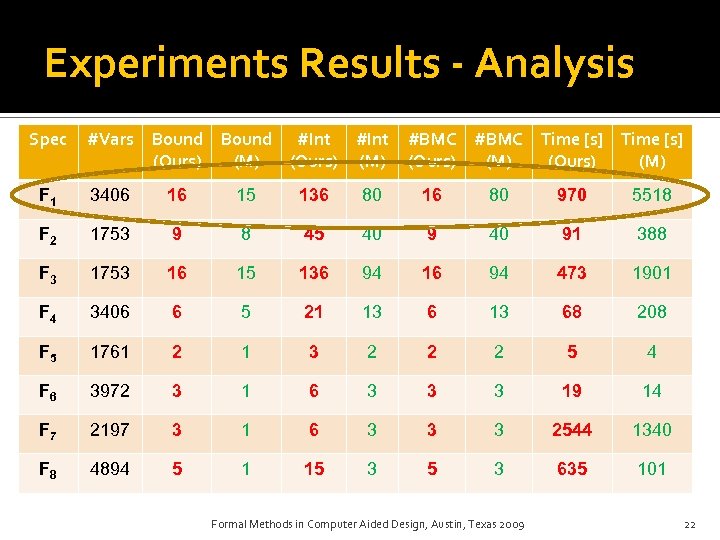

Experiments Results - Analysis Spec #Vars Bound (Ours) Bound #Int (M) (Ours) (M) #BMC (Ours) #BMC (M) Time [s] (Ours) Time [s] (M) F 1 3406 16 15 136 80 16 80 970 5518 F 2 1753 9 8 45 40 91 388 F 3 1753 16 15 136 94 16 94 473 1901 F 4 3406 6 5 21 13 68 208 F 5 1761 2 1 3 2 2 2 5 4 F 6 3972 3 1 6 3 3 3 19 14 F 7 2197 3 1 6 3 3 3 2544 1340 F 8 4894 5 1 15 3 635 101 Formal Methods in Computer Aided Design, Austin, Texas 2009 22

Analysis False properties is always faster. True properties – results vary. Heavier properties favor ISB where the easier favor IB. Some properties cannot be verified by one method but can be verified by the other and vise-versa. Formal Methods in Computer Aided Design, Austin, Texas 2009 23

Conclusions A new SAT-based method for unbounded model checking. BMC is used for falsification. Simulating forward reachability analysis for verification. Method was successfully applied to industrial sized systems. Formal Methods in Computer Aided Design, Austin, Texas 2009 24

Questions? Thank You! Formal Methods in Computer Aided Design, Austin, Texas 2009 25

49f806bef763f29b841db46415f17e23.ppt