f6191506278549d79561664ecf4a43c9.ppt

- Количество слайдов: 18

Integrated Management of Power Aware Computing & Communication Technologies PI Meeting Nader Bagherzadeh, Pai H. Chou, Fadi Kurdahi University of California, Irvine, ECE Dept. DARPA Contract F 33615 -00 -1 -1719 April 18 -20, 2001 San Diego, CA 1

Integrated Management of Power Aware Computing & Communication Technologies PI Meeting Nader Bagherzadeh, Pai H. Chou, Fadi Kurdahi University of California, Irvine, ECE Dept. DARPA Contract F 33615 -00 -1 -1719 April 18 -20, 2001 San Diego, CA 1

Outline n Introduction o Status n overview, Application Accomplishments to date o Scheduling o Component power models and simulators o Architecture configuration: Mode Selection n Metrics n Review of program milestones and goals o Fulfilled: prototype of scheduling/planning tool o Upcoming: integration with COPPER project, dynamic scheduling n Future planned evaluation n Development platforms, tools, metrics n Transition plan. 2

Outline n Introduction o Status n overview, Application Accomplishments to date o Scheduling o Component power models and simulators o Architecture configuration: Mode Selection n Metrics n Review of program milestones and goals o Fulfilled: prototype of scheduling/planning tool o Upcoming: integration with COPPER project, dynamic scheduling n Future planned evaluation n Development platforms, tools, metrics n Transition plan. 2

![Applications n Space o Mars Pathfinder o X-2000 architecture n [new] NASA Deep Impact Applications n Space o Mars Pathfinder o X-2000 architecture n [new] NASA Deep Impact](https://present5.com/presentation/f6191506278549d79561664ecf4a43c9/image-3.jpg) Applications n Space o Mars Pathfinder o X-2000 architecture n [new] NASA Deep Impact o JPL-led effort, with Power. PC 750 testbed (measures power) o Mission planning, software architecture level n ATR o Needs algorithm-level parallelization and arch. (DSP, FPGA) first o System-level pipeline scheduling n UCAV o thermal battery scheduling 3

Applications n Space o Mars Pathfinder o X-2000 architecture n [new] NASA Deep Impact o JPL-led effort, with Power. PC 750 testbed (measures power) o Mission planning, software architecture level n ATR o Needs algorithm-level parallelization and arch. (DSP, FPGA) first o System-level pipeline scheduling n UCAV o thermal battery scheduling 3

Personnel & teaming plans n UC Irvine Bagherzadeh o Pai Chou o Fadi Kurdahi o Jinfeng Liu o Dexin Li o Duan Tran - Design tools o Nader n USC Gaudiot o Seong-Won Lee students - Component power optimization o Jean-Luc n JPL student - Applications and benchmarking o Nazeeh Aranki o Nikzad “Benny” Toomarian 4

Personnel & teaming plans n UC Irvine Bagherzadeh o Pai Chou o Fadi Kurdahi o Jinfeng Liu o Dexin Li o Duan Tran - Design tools o Nader n USC Gaudiot o Seong-Won Lee students - Component power optimization o Jean-Luc n JPL student - Applications and benchmarking o Nazeeh Aranki o Nikzad “Benny” Toomarian 4

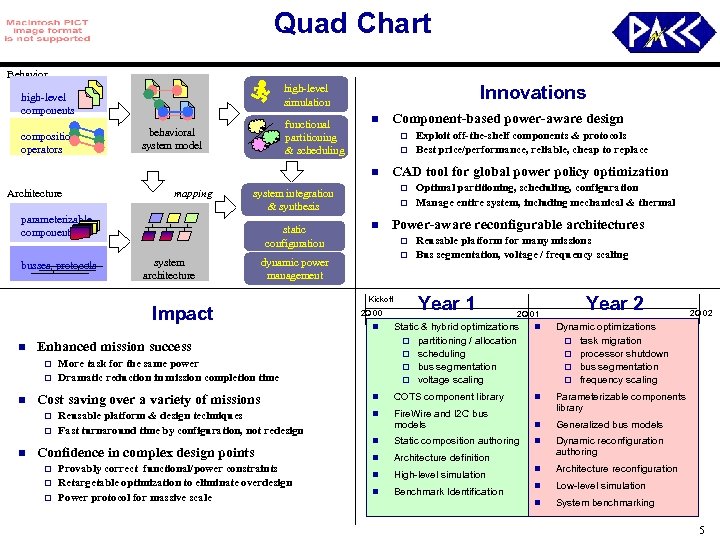

Quad Chart Behavior composition operators Innovations high-level simulation high-level components functional partitioning & scheduling behavioral system model n o o n Architecture mapping static configuration system architecture o Kickoff o Reusable platform & design techniques Fast turnaround time by configuration, not redesign Confidence in complex design points o o o Provably correct functional/power constraints Retargetable optimization to eliminate overdesign Power protocol for massive scale Reusable platform for many missions Bus segmentation, voltage / frequency scaling Year 1 2 Q 01 Year 2 n Static & hybrid optimizations o partitioning / allocation o scheduling o bus segmentation o voltage scaling n n COTS component library n n Fire. Wire and I 2 C bus models Parameterizable components library n Generalized bus models n Static composition authoring n n Architecture definition Dynamic reconfiguration authoring n High-level simulation n Architecture reconfiguration n Benchmark Identification n Low-level simulation n 2 Q 02 Dynamic optimizations o task migration o processor shutdown o bus segmentation o frequency scaling System benchmarking More task for the same power Dramatic reduction in mission completion time Cost saving over a variety of missions o n o 2 Q 00 Optimal partitioning, scheduling, configuration Manage entire system, including mechanical & thermal Power-aware reconfigurable architectures o Enhanced mission success o n o dynamic power management Impact n o n Exploit off-the-shelf components & protocols Best price/performance, reliable, cheap to replace CAD tool for global power policy optimization system integration & synthesis parameterizable components busses, protocols Component-based power-aware design 5

Quad Chart Behavior composition operators Innovations high-level simulation high-level components functional partitioning & scheduling behavioral system model n o o n Architecture mapping static configuration system architecture o Kickoff o Reusable platform & design techniques Fast turnaround time by configuration, not redesign Confidence in complex design points o o o Provably correct functional/power constraints Retargetable optimization to eliminate overdesign Power protocol for massive scale Reusable platform for many missions Bus segmentation, voltage / frequency scaling Year 1 2 Q 01 Year 2 n Static & hybrid optimizations o partitioning / allocation o scheduling o bus segmentation o voltage scaling n n COTS component library n n Fire. Wire and I 2 C bus models Parameterizable components library n Generalized bus models n Static composition authoring n n Architecture definition Dynamic reconfiguration authoring n High-level simulation n Architecture reconfiguration n Benchmark Identification n Low-level simulation n 2 Q 02 Dynamic optimizations o task migration o processor shutdown o bus segmentation o frequency scaling System benchmarking More task for the same power Dramatic reduction in mission completion time Cost saving over a variety of missions o n o 2 Q 00 Optimal partitioning, scheduling, configuration Manage entire system, including mechanical & thermal Power-aware reconfigurable architectures o Enhanced mission success o n o dynamic power management Impact n o n Exploit off-the-shelf components & protocols Best price/performance, reliable, cheap to replace CAD tool for global power policy optimization system integration & synthesis parameterizable components busses, protocols Component-based power-aware design 5

Program Overview n Power-aware system-level design o Amdahl's law applies to power as well as performance o Enhance mission success (time, task) o Rapid customization for different missions n Design tool o Exploration & evaluation o Optimization& specialization o Technique integration n System architecture o Statically configurable o Dynamically adaptive o Use COTS parts & protocols 6

Program Overview n Power-aware system-level design o Amdahl's law applies to power as well as performance o Enhance mission success (time, task) o Rapid customization for different missions n Design tool o Exploration & evaluation o Optimization& specialization o Technique integration n System architecture o Statically configurable o Dynamically adaptive o Use COTS parts & protocols 6

Accomplishments to date n Power-aware scheduling -- DEMO o Multiple processors, mechanical, thermal o Min / Max power and timing constraints o Power-aware Gantt chart user interface o Pipelining at system-level n Architectural optimization o Bus topology optimization, segmentation o Mode selection for power & timing n Component power models and simulators o Performance simulator o Parameterized energy model n Interface to COPPER project 7

Accomplishments to date n Power-aware scheduling -- DEMO o Multiple processors, mechanical, thermal o Min / Max power and timing constraints o Power-aware Gantt chart user interface o Pipelining at system-level n Architectural optimization o Bus topology optimization, segmentation o Mode selection for power & timing n Component power models and simulators o Performance simulator o Parameterized energy model n Interface to COPPER project 7

![Power-Aware Scheduling n New constraint-based application model [paper at Codes'01] o Min/Max l l Power-Aware Scheduling n New constraint-based application model [paper at Codes'01] o Min/Max l l](https://present5.com/presentation/f6191506278549d79561664ecf4a43c9/image-8.jpg) Power-Aware Scheduling n New constraint-based application model [paper at Codes'01] o Min/Max l l l Precedence, subsumes dataflow, general timing, shared resource Dependency across iteration boundaries – loop pipelining Execution delay of tasks – enables frequency/voltage scaling o Power l l n Timing constraints Max power – total power budget Min power – controls power jitter or force utilization of free source System-level, multi-scenario scheduling [paper at DAC'01] o 25% Faster while saving 31% energy cost o Exploits "free" power (solar, nuclear min-output) n System-level loop pipelining [working papers] o Borrow time and power across iteration boundaries o Aggressive design space exploration by new constraint classification o Achieves 49% speedup and 24% energy reduction 8

Power-Aware Scheduling n New constraint-based application model [paper at Codes'01] o Min/Max l l l Precedence, subsumes dataflow, general timing, shared resource Dependency across iteration boundaries – loop pipelining Execution delay of tasks – enables frequency/voltage scaling o Power l l n Timing constraints Max power – total power budget Min power – controls power jitter or force utilization of free source System-level, multi-scenario scheduling [paper at DAC'01] o 25% Faster while saving 31% energy cost o Exploits "free" power (solar, nuclear min-output) n System-level loop pipelining [working papers] o Borrow time and power across iteration boundaries o Aggressive design space exploration by new constraint classification o Achieves 49% speedup and 24% energy reduction 8

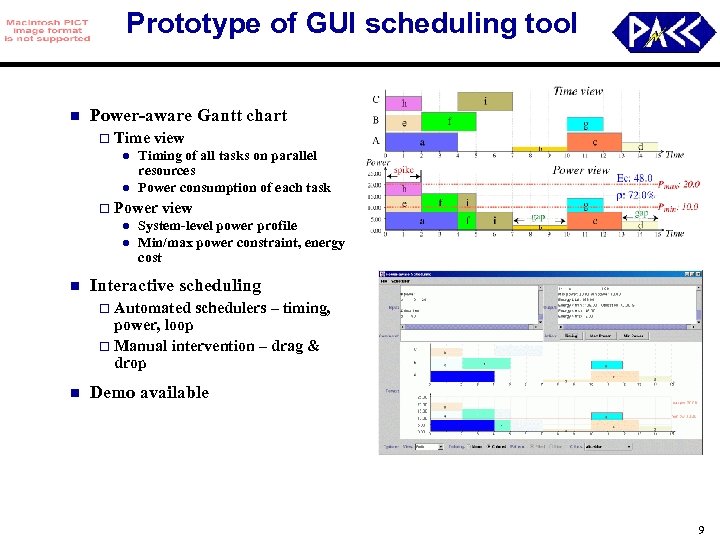

Prototype of GUI scheduling tool n Power-aware Gantt chart o Time view l l o Power view l l n Timing of all tasks on parallel resources Power consumption of each task System-level power profile Min/max power constraint, energy cost Interactive scheduling Automated schedulers – timing, power, loop o Manual intervention – drag & drop o n Demo available 9

Prototype of GUI scheduling tool n Power-aware Gantt chart o Time view l l o Power view l l n Timing of all tasks on parallel resources Power consumption of each task System-level power profile Min/max power constraint, energy cost Interactive scheduling Automated schedulers – timing, power, loop o Manual intervention – drag & drop o n Demo available 9

Architectural Configuration n Mode selection o Power consumption level (doze, nap, sleep, etc. ) o Low power design techniques l l l Clock scaling, voltage scaling Memory/cache configurations, bus encoding Communication protocols, compression, algorithm transformations o Optimize feasible solutions for energy/timing costs o Power, Real time, Inter-resource modes constraints o Constraints between functionality modes and resources modes Functionality mode and resource modes n Bus topology optimization o Static clustering and bus partitioning o Dynamic reclustering with shutdown 10

Architectural Configuration n Mode selection o Power consumption level (doze, nap, sleep, etc. ) o Low power design techniques l l l Clock scaling, voltage scaling Memory/cache configurations, bus encoding Communication protocols, compression, algorithm transformations o Optimize feasible solutions for energy/timing costs o Power, Real time, Inter-resource modes constraints o Constraints between functionality modes and resources modes Functionality mode and resource modes n Bus topology optimization o Static clustering and bus partitioning o Dynamic reclustering with shutdown 10

Component power model n Performance simulator-drive power estimation o Independent performance simulator and power estimation modules o Modular, can be replaced with other model, extensible n Performance simulator o for SMT, up to 8 threads, emulates single thread superscalar CPU o Executes Alpha EV 6 binaries, emulates Alpha 21264 n Power estimation model o Parameterizable power model for HW modules in microarchitecture o Moving average model for power profile o Inputs microarchitectural params, # accesses (activity factor) 11

Component power model n Performance simulator-drive power estimation o Independent performance simulator and power estimation modules o Modular, can be replaced with other model, extensible n Performance simulator o for SMT, up to 8 threads, emulates single thread superscalar CPU o Executes Alpha EV 6 binaries, emulates Alpha 21264 n Power estimation model o Parameterizable power model for HW modules in microarchitecture o Moving average model for power profile o Inputs microarchitectural params, # accesses (activity factor) 11

Metrics n Source-aware energy model o Takes “free energy” into account o Cost for not using free energy n Profile-aware o Total energy dependent on consumers’ power profile o Smoothness of power draw n Scenario-aware o Cost function tracks external factors (e. g. temperature, solar level) o Stage in mission n Timing/performance o Makespan (length of an iteration) o Dynamic planning cost 12

Metrics n Source-aware energy model o Takes “free energy” into account o Cost for not using free energy n Profile-aware o Total energy dependent on consumers’ power profile o Smoothness of power draw n Scenario-aware o Cost function tracks external factors (e. g. temperature, solar level) o Stage in mission n Timing/performance o Makespan (length of an iteration) o Dynamic planning cost 12

Review of Milestones & Goals n Accomplished o UI prototype o Power-aware scheduling [3 papers] l l Multi-scenario System-level pipelining o Mode l selection encompass power mgmt (voltage/freq scaling) o Processor n power & simulation models Upcoming o Dynamic l l optimization Scheduling Architectural reconfiguration o Library of parameterizable bus models o Tool integration l l IMPACCT tools and library between IMPACCT and COPPER 13

Review of Milestones & Goals n Accomplished o UI prototype o Power-aware scheduling [3 papers] l l Multi-scenario System-level pipelining o Mode l selection encompass power mgmt (voltage/freq scaling) o Processor n power & simulation models Upcoming o Dynamic l l optimization Scheduling Architectural reconfiguration o Library of parameterizable bus models o Tool integration l l IMPACCT tools and library between IMPACCT and COPPER 13

Future planned evaluation n Deep Impact from JPL o Mission planning and scheduling example o Image compression (wavelet) algorithm o Architectural mapping n JPL Testbed o PPC 750 board to measure actual power o PPC 750 to simulate instrumentation in real-time o advanced board with real instrumentation n Validation through COPPER o Scheduler output fed to COPPER for compilation o Compare estimated power with refined version 14

Future planned evaluation n Deep Impact from JPL o Mission planning and scheduling example o Image compression (wavelet) algorithm o Architectural mapping n JPL Testbed o PPC 750 board to measure actual power o PPC 750 to simulate instrumentation in real-time o advanced board with real instrumentation n Validation through COPPER o Scheduler output fed to COPPER for compilation o Compare estimated power with refined version 14

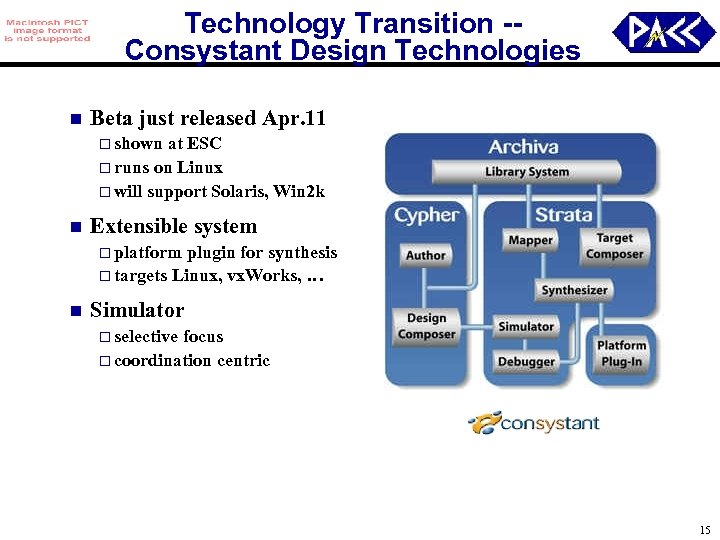

Technology Transition -Consystant Design Technologies n Beta just released Apr. 11 o shown at ESC o runs on Linux o will support Solaris, Win 2 k n Extensible system o platform plugin for synthesis o targets Linux, vx. Works, … n Simulator o selective focus o coordination centric 15

Technology Transition -Consystant Design Technologies n Beta just released Apr. 11 o shown at ESC o runs on Linux o will support Solaris, Win 2 k n Extensible system o platform plugin for synthesis o targets Linux, vx. Works, … n Simulator o selective focus o coordination centric 15

Development plans n Scripting and web-based tool o Jython (Java + Python) for GUI prototype o Core scheduler l l Modular, detachable from GUI Option to run on separate server or same process as UI o CGI scripts for arch. configuration (unix/web based) o Latest version distributed thru Web. CVS n Interface with commercial CAD backend o Detailed power estimation tools o Functional simulation with proprietary models n Rationale o Open source, runs on any platform o All publicly available development tools o Trivial to install, no compilation, encourage modification 16

Development plans n Scripting and web-based tool o Jython (Java + Python) for GUI prototype o Core scheduler l l Modular, detachable from GUI Option to run on separate server or same process as UI o CGI scripts for arch. configuration (unix/web based) o Latest version distributed thru Web. CVS n Interface with commercial CAD backend o Detailed power estimation tools o Functional simulation with proprietary models n Rationale o Open source, runs on any platform o All publicly available development tools o Trivial to install, no compilation, encourage modification 16

http: //www. ece. uci. edu/impacct/ 17

http: //www. ece. uci. edu/impacct/ 17

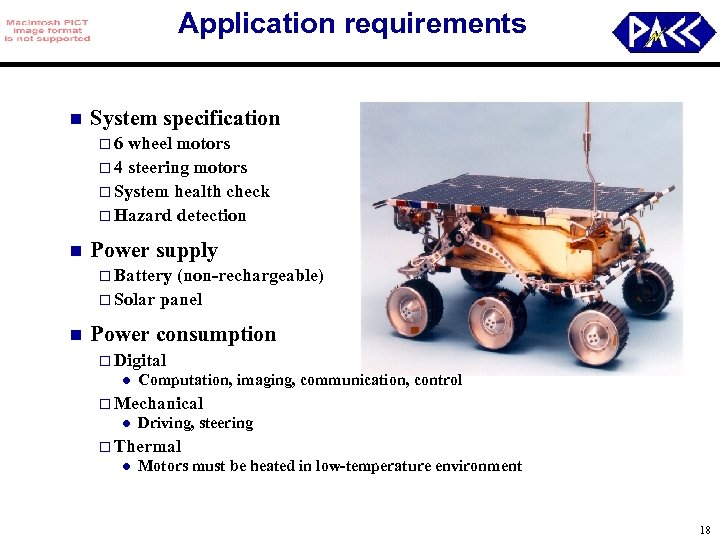

Application requirements n System specification o 6 wheel motors o 4 steering motors o System health check o Hazard detection n Power supply o Battery (non-rechargeable) o Solar panel n Power consumption o Digital l Computation, imaging, communication, control o Mechanical l Driving, steering o Thermal l Motors must be heated in low-temperature environment 18

Application requirements n System specification o 6 wheel motors o 4 steering motors o System health check o Hazard detection n Power supply o Battery (non-rechargeable) o Solar panel n Power consumption o Digital l Computation, imaging, communication, control o Mechanical l Driving, steering o Thermal l Motors must be heated in low-temperature environment 18