abfe3cec947f292f2c62fa0eefe429d9.ppt

- Количество слайдов: 25

Integrated Management of Power Aware Computing & Communication Technologies PI Meeting Nader Bagherzadeh, Pai H. Chou, Fadi Kurdahi University of California, Irvine, ECE Dept. DARPA Contract F 33615 -00 -1 -1719 November 1 -3, 2000 1

Integrated Management of Power Aware Computing & Communication Technologies PI Meeting Nader Bagherzadeh, Pai H. Chou, Fadi Kurdahi University of California, Irvine, ECE Dept. DARPA Contract F 33615 -00 -1 -1719 November 1 -3, 2000 1

Outline n Introduction o Concepts and goals o Program overview o Application n Accomplishments to date o Architecture configuration o Scheduling n Development platforms and tools n Metrics n Anticipated transitions 2

Outline n Introduction o Concepts and goals o Program overview o Application n Accomplishments to date o Architecture configuration o Scheduling n Development platforms and tools n Metrics n Anticipated transitions 2

Personnel & teaming plans n UC Irvine Bagherzadeh o Pai Chou o Fadi Kurdahi o Dexin Li o Jinfeng Liu o Duan Tran - Design tools o Nader n USC students - Component power optimization o Jean-Luc Gaudiot o Seong-Won Lee n JPL - Applications and benchmarking o Nazeeh Aranki o Nikzad “Benny” Toomarian 3

Personnel & teaming plans n UC Irvine Bagherzadeh o Pai Chou o Fadi Kurdahi o Dexin Li o Jinfeng Liu o Duan Tran - Design tools o Nader n USC students - Component power optimization o Jean-Luc Gaudiot o Seong-Won Lee n JPL - Applications and benchmarking o Nazeeh Aranki o Nikzad “Benny” Toomarian 3

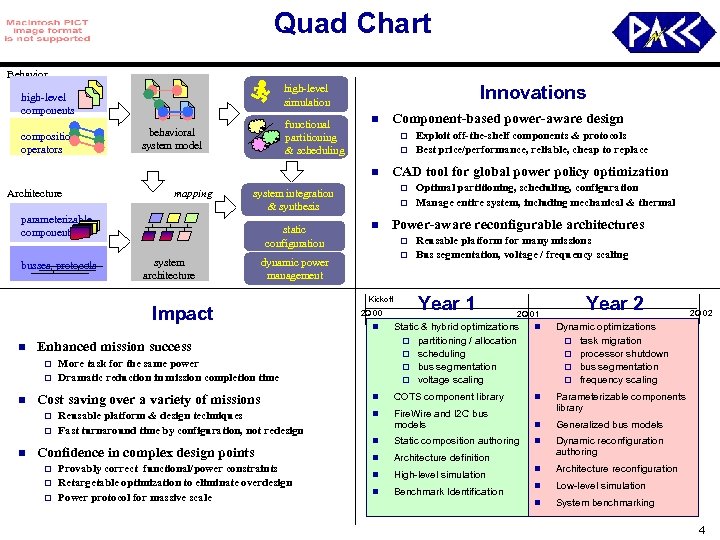

Quad Chart Behavior composition operators Innovations high-level simulation high-level components functional partitioning & scheduling behavioral system model n o o n Architecture mapping static configuration system architecture o Kickoff o Reusable platform & design techniques Fast turnaround time by configuration, not redesign Confidence in complex design points o o o Provably correct functional/power constraints Retargetable optimization to eliminate overdesign Power protocol for massive scale Reusable platform for many missions Bus segmentation, voltage / frequency scaling Year 1 2 Q 01 Year 2 n Static & hybrid optimizations o partitioning / allocation o scheduling o bus segmentation o voltage scaling n n COTS component library n n Fire. Wire and I 2 C bus models Parameterizable components library n Generalized bus models n Static composition authoring n n Architecture definition Dynamic reconfiguration authoring n High-level simulation n Architecture reconfiguration n Benchmark Identification n Low-level simulation n 2 Q 02 Dynamic optimizations o task migration o processor shutdown o bus segmentation o frequency scaling System benchmarking More task for the same power Dramatic reduction in mission completion time Cost saving over a variety of missions o n o 2 Q 00 Optimal partitioning, scheduling, configuration Manage entire system, including mechanical & thermal Power-aware reconfigurable architectures o Enhanced mission success o n o dynamic power management Impact n o n Exploit off-the-shelf components & protocols Best price/performance, reliable, cheap to replace CAD tool for global power policy optimization system integration & synthesis parameterizable components busses, protocols Component-based power-aware design 4

Quad Chart Behavior composition operators Innovations high-level simulation high-level components functional partitioning & scheduling behavioral system model n o o n Architecture mapping static configuration system architecture o Kickoff o Reusable platform & design techniques Fast turnaround time by configuration, not redesign Confidence in complex design points o o o Provably correct functional/power constraints Retargetable optimization to eliminate overdesign Power protocol for massive scale Reusable platform for many missions Bus segmentation, voltage / frequency scaling Year 1 2 Q 01 Year 2 n Static & hybrid optimizations o partitioning / allocation o scheduling o bus segmentation o voltage scaling n n COTS component library n n Fire. Wire and I 2 C bus models Parameterizable components library n Generalized bus models n Static composition authoring n n Architecture definition Dynamic reconfiguration authoring n High-level simulation n Architecture reconfiguration n Benchmark Identification n Low-level simulation n 2 Q 02 Dynamic optimizations o task migration o processor shutdown o bus segmentation o frequency scaling System benchmarking More task for the same power Dramatic reduction in mission completion time Cost saving over a variety of missions o n o 2 Q 00 Optimal partitioning, scheduling, configuration Manage entire system, including mechanical & thermal Power-aware reconfigurable architectures o Enhanced mission success o n o dynamic power management Impact n o n Exploit off-the-shelf components & protocols Best price/performance, reliable, cheap to replace CAD tool for global power policy optimization system integration & synthesis parameterizable components busses, protocols Component-based power-aware design 4

Program Goals n Power-aware system-level design o Enhance mission success (time, task) o Rapid customization for different missions n Design tool o Exploration & evaluation o Optimization& specialization o Technique integration n System architecture o Statically configurable o Dynamically adaptive o Use COTS parts & protocols 5

Program Goals n Power-aware system-level design o Enhance mission success (time, task) o Rapid customization for different missions n Design tool o Exploration & evaluation o Optimization& specialization o Technique integration n System architecture o Statically configurable o Dynamically adaptive o Use COTS parts & protocols 5

Technical approach n High-level specification o Separate behavior from architecture o Explicit constraints (timing, power) o Library characterization n System synthesis tool o Source-aware power usage scheduling o Bus topology transformation and communication scheduling n Configurable architecture o Task migration & selective shutdown o Bus segmentation and voltage scaling n Domain knowledge o Encompass mechanical / thermal power o Aware of power supply model 6

Technical approach n High-level specification o Separate behavior from architecture o Explicit constraints (timing, power) o Library characterization n System synthesis tool o Source-aware power usage scheduling o Bus topology transformation and communication scheduling n Configurable architecture o Task migration & selective shutdown o Bus segmentation and voltage scaling n Domain knowledge o Encompass mechanical / thermal power o Aware of power supply model 6

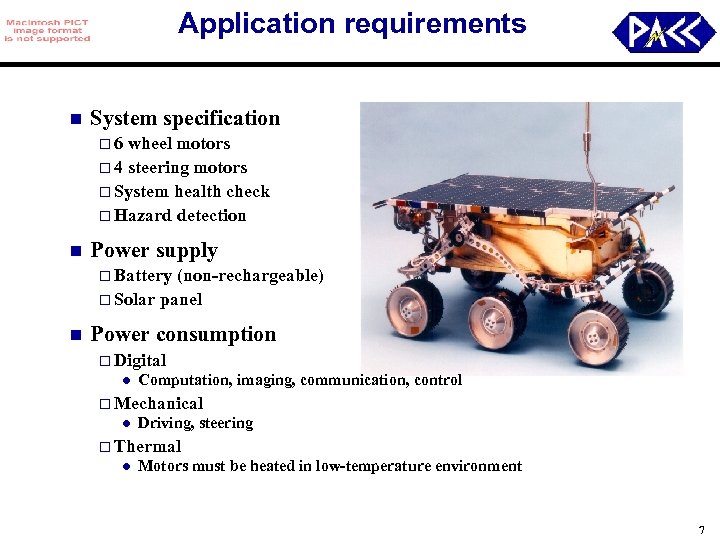

Application requirements n System specification o 6 wheel motors o 4 steering motors o System health check o Hazard detection n Power supply o Battery (non-rechargeable) o Solar panel n Power consumption o Digital l Computation, imaging, communication, control o Mechanical l Driving, steering o Thermal l Motors must be heated in low-temperature environment 7

Application requirements n System specification o 6 wheel motors o 4 steering motors o System health check o Hazard detection n Power supply o Battery (non-rechargeable) o Solar panel n Power consumption o Digital l Computation, imaging, communication, control o Mechanical l Driving, steering o Thermal l Motors must be heated in low-temperature environment 7

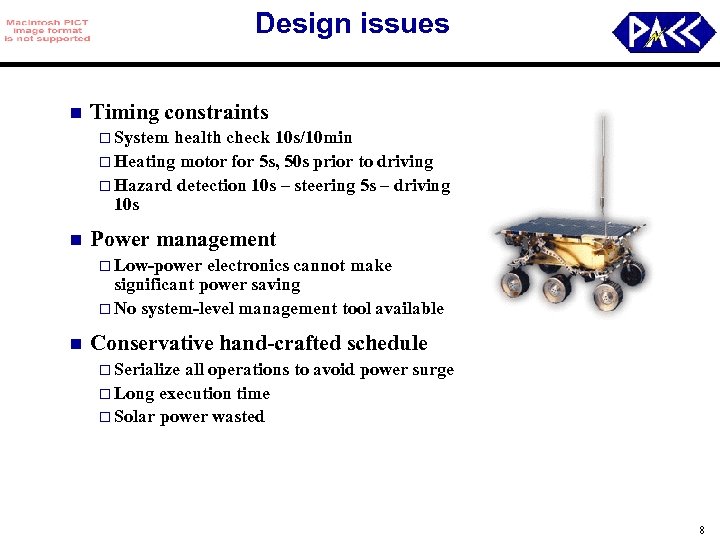

Design issues n Timing constraints o System health check 10 s/10 min o Heating motor for 5 s, 50 s prior to driving o Hazard detection 10 s – steering 5 s – driving 10 s n Power management o Low-power electronics cannot make significant power saving o No system-level management tool available n Conservative hand-crafted schedule o Serialize all operations to avoid power surge o Long execution time o Solar power wasted 8

Design issues n Timing constraints o System health check 10 s/10 min o Heating motor for 5 s, 50 s prior to driving o Hazard detection 10 s – steering 5 s – driving 10 s n Power management o Low-power electronics cannot make significant power saving o No system-level management tool available n Conservative hand-crafted schedule o Serialize all operations to avoid power surge o Long execution time o Solar power wasted 8

Power-aware vs low-power n Low power o Minimize power consumption only o Minimal application specific knowledge, limited reconfiguration space o Conservative n Power aware: Make best use of available power o Use MAX solar power while it's available o Increase parallelism, perform more tasks, reduce mission time o Both MIN and MAX power constraints o Application-specific knowledge l l Multiple mission requirement Adapt to run-time power supply, operating environment 9

Power-aware vs low-power n Low power o Minimize power consumption only o Minimal application specific knowledge, limited reconfiguration space o Conservative n Power aware: Make best use of available power o Use MAX solar power while it's available o Increase parallelism, perform more tasks, reduce mission time o Both MIN and MAX power constraints o Application-specific knowledge l l Multiple mission requirement Adapt to run-time power supply, operating environment 9

What's needed? n Reconfigurable system architecture o NASA X-2000 o Statically configurable for different missions o Reconfiguration for dynamic power management o Support state-of-the-art power management policies n System-level design tool o Support design space exploration o Take full advantage of COTS components o Optimize mission-specific system configuration o Synthesize system-level power manager o Support simulation for early validation 10

What's needed? n Reconfigurable system architecture o NASA X-2000 o Statically configurable for different missions o Reconfiguration for dynamic power management o Support state-of-the-art power management policies n System-level design tool o Support design space exploration o Take full advantage of COTS components o Optimize mission-specific system configuration o Synthesize system-level power manager o Support simulation for early validation 10

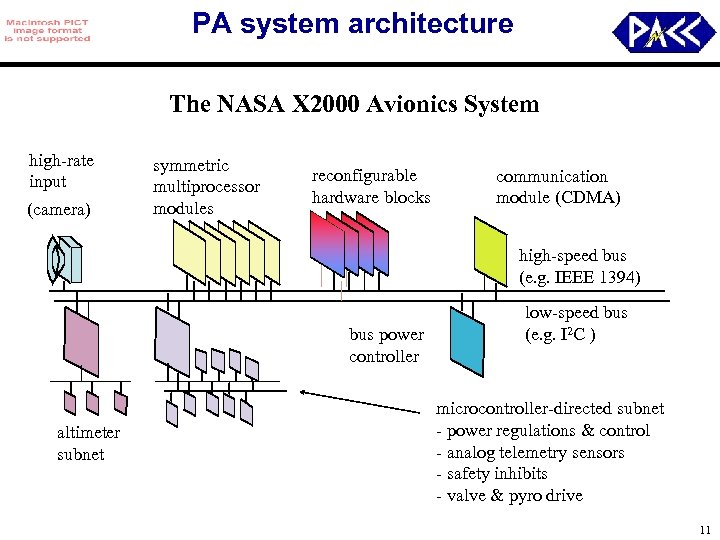

PA system architecture The NASA X 2000 Avionics System high-rate input (camera) symmetric multiprocessor modules reconfigurable hardware blocks communication module (CDMA) high-speed bus (e. g. IEEE 1394) bus power controller altimeter subnet low-speed bus (e. g. I 2 C ) microcontroller-directed subnet - power regulations & control - analog telemetry sensors - safety inhibits - valve & pyro drive 11

PA system architecture The NASA X 2000 Avionics System high-rate input (camera) symmetric multiprocessor modules reconfigurable hardware blocks communication module (CDMA) high-speed bus (e. g. IEEE 1394) bus power controller altimeter subnet low-speed bus (e. g. I 2 C ) microcontroller-directed subnet - power regulations & control - analog telemetry sensors - safety inhibits - valve & pyro drive 11

Design tool n Library o Components and bus protocols o Provides power estimation o Defines configuration space n Authoring o Behavioral description, architecture description o Mapping from behavior to architecture n Synthesis o Scheduling, partitioning o Bus segmentation, voltage scaling o Synthesis of power manager with task scheduler n Simulation o High-level: explore design space o Detailed-level: power/performance for a given design point 12

Design tool n Library o Components and bus protocols o Provides power estimation o Defines configuration space n Authoring o Behavioral description, architecture description o Mapping from behavior to architecture n Synthesis o Scheduling, partitioning o Bus segmentation, voltage scaling o Synthesis of power manager with task scheduler n Simulation o High-level: explore design space o Detailed-level: power/performance for a given design point 12

Accomplishments to date n Power-aware scheduling o Multiple processors, mechanical, thermal o Min / Max power and timing constraints o Power-aware Gantt chart user interface n Architectural optimization o Bus topology optimization o Bus segmentation o Power-mode-change optimization 13

Accomplishments to date n Power-aware scheduling o Multiple processors, mechanical, thermal o Min / Max power and timing constraints o Power-aware Gantt chart user interface n Architectural optimization o Bus topology optimization o Bus segmentation o Power-mode-change optimization 13

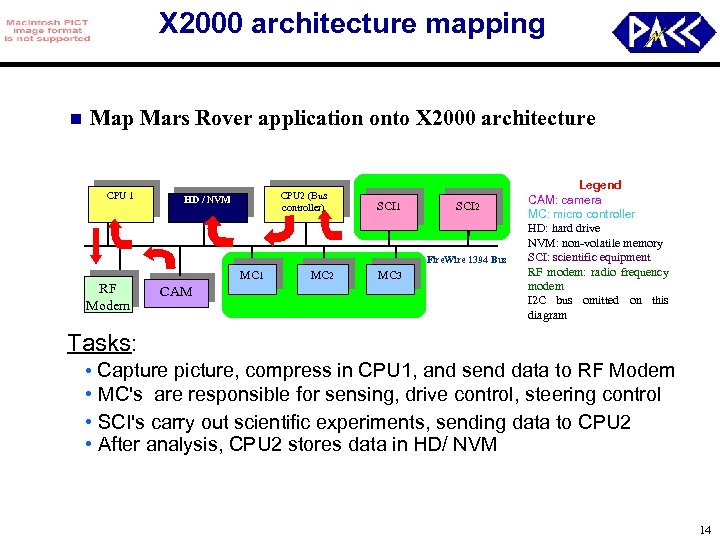

X 2000 architecture mapping n Map Mars Rover application onto X 2000 architecture CPU 1 CPU 2 (Bus controller) HD / NVM SCI 1 SCI 2 SCI Fire. Wire 1394 Bus RF Modem MC 1 CAM MC 2 MC 3 Legend CAM: camera MC: micro controller HD: hard drive NVM: non-volatile memory SCI: scientific equipment RF modem: radio frequency modem I 2 C bus omitted on this diagram Tasks: • Capture picture, compress in CPU 1, and send data to RF Modem • MC's are responsible for sensing, drive control, steering control • SCI's carry out scientific experiments, sending data to CPU 2 • After analysis, CPU 2 stores data in HD/ NVM 14

X 2000 architecture mapping n Map Mars Rover application onto X 2000 architecture CPU 1 CPU 2 (Bus controller) HD / NVM SCI 1 SCI 2 SCI Fire. Wire 1394 Bus RF Modem MC 1 CAM MC 2 MC 3 Legend CAM: camera MC: micro controller HD: hard drive NVM: non-volatile memory SCI: scientific equipment RF modem: radio frequency modem I 2 C bus omitted on this diagram Tasks: • Capture picture, compress in CPU 1, and send data to RF Modem • MC's are responsible for sensing, drive control, steering control • SCI's carry out scientific experiments, sending data to CPU 2 • After analysis, CPU 2 stores data in HD/ NVM 14

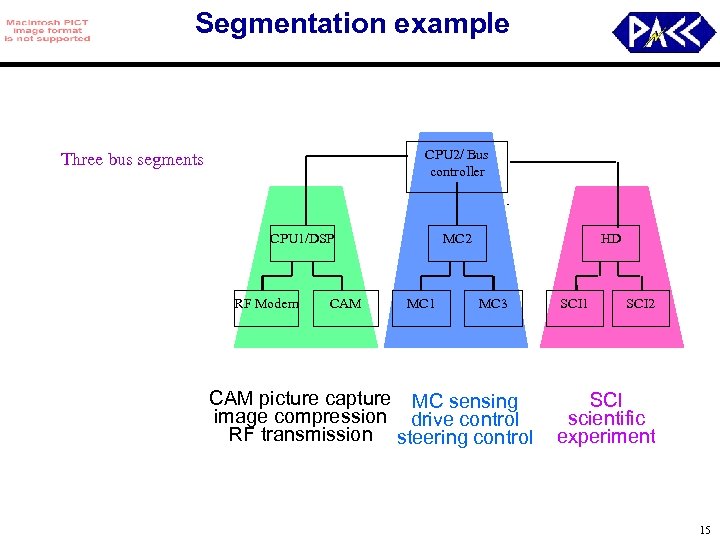

Segmentation example CPU 2/ Bus controller Three bus segments CPU 1/DSP RF Modem CAM MC 2 MC 1 HD MC 3 CAM picture capture MC sensing image compression drive control RF transmission steering control SCI 1 SCI 2 SCI scientific experiment 15

Segmentation example CPU 2/ Bus controller Three bus segments CPU 1/DSP RF Modem CAM MC 2 MC 1 HD MC 3 CAM picture capture MC sensing image compression drive control RF transmission steering control SCI 1 SCI 2 SCI scientific experiment 15

Summary of architecture optimization n Towards loose coupling o Reduced bus contention o Increased parallel bandwidth o Enabling voltage/frequency scaling n Application-driven clustering o Communication bandwidth requirements between processes o Knowledge from high-level behavioral model n Static optimization 2. 4 x energy reduction o Bus segmentation o Cluster shutdown n Dynamic reclustering 1. 9 x energy reduction 16

Summary of architecture optimization n Towards loose coupling o Reduced bus contention o Increased parallel bandwidth o Enabling voltage/frequency scaling n Application-driven clustering o Communication bandwidth requirements between processes o Knowledge from high-level behavioral model n Static optimization 2. 4 x energy reduction o Bus segmentation o Cluster shutdown n Dynamic reclustering 1. 9 x energy reduction 16

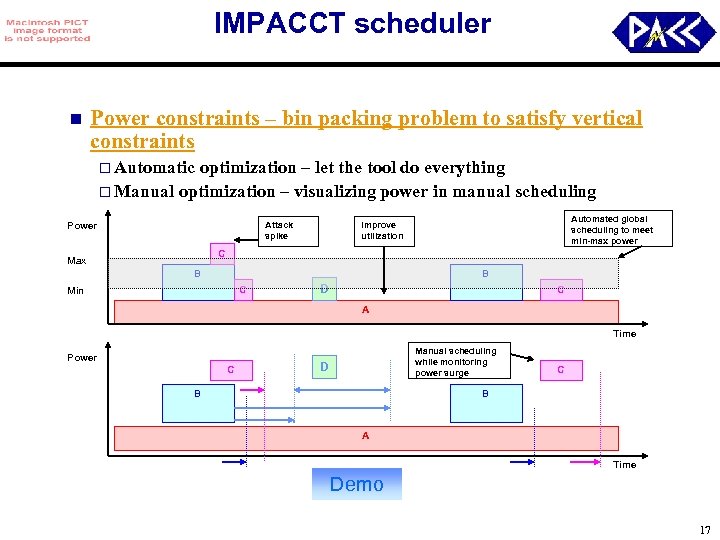

IMPACCT scheduler n Power constraints – bin packing problem to satisfy vertical constraints o Automatic optimization – let the tool do everything o Manual optimization – visualizing power in manual scheduling Attack spike Power Automated global scheduling to meet min-max power Improve utilization C Max B B C Min D C A Time Power C Manual scheduling while monitoring power surge D B C B A Time Demo 17

IMPACCT scheduler n Power constraints – bin packing problem to satisfy vertical constraints o Automatic optimization – let the tool do everything o Manual optimization – visualizing power in manual scheduling Attack spike Power Automated global scheduling to meet min-max power Improve utilization C Max B B C Min D C A Time Power C Manual scheduling while monitoring power surge D B C B A Time Demo 17

Example – Mars Rover n Power constraints o Different solar power supply over time o Different power consumption over temperature/time 18

Example – Mars Rover n Power constraints o Different solar power supply over time o Different power consumption over temperature/time 18

Application-level evaluation n Mission description o Target n location – 48 (distance-) steps away from current location Power condition o 14. 9 W solar power for first 10 minutes, 12 W for next 10 minutes, 9 W thereafter n Metrics o Execution time o Total energy drawn from battery 19

Application-level evaluation n Mission description o Target n location – 48 (distance-) steps away from current location Power condition o 14. 9 W solar power for first 10 minutes, 12 W for next 10 minutes, 9 W thereafter n Metrics o Execution time o Total energy drawn from battery 19

Application-level evaluation n Power-awareness o Execution speed scales with power condition adaptively n Smart schedule o Maximize best case o Avoid worst case n Tradeoff o Power vs. performance o Energy renewability n Application-specific o Application-level knowledge o Working mode parameters of components 20

Application-level evaluation n Power-awareness o Execution speed scales with power condition adaptively n Smart schedule o Maximize best case o Avoid worst case n Tradeoff o Power vs. performance o Energy renewability n Application-specific o Application-level knowledge o Working mode parameters of components 20

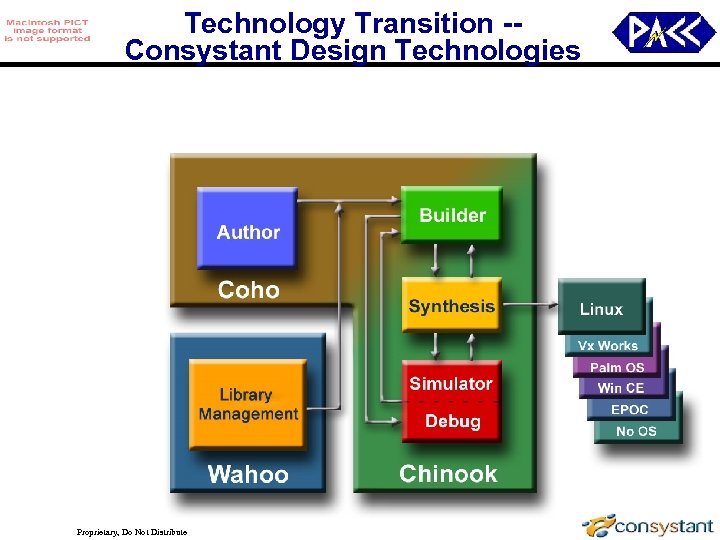

Technology Transition -Consystant Design Technologies Proprietary, Do Not Distribute 21

Technology Transition -Consystant Design Technologies Proprietary, Do Not Distribute 21

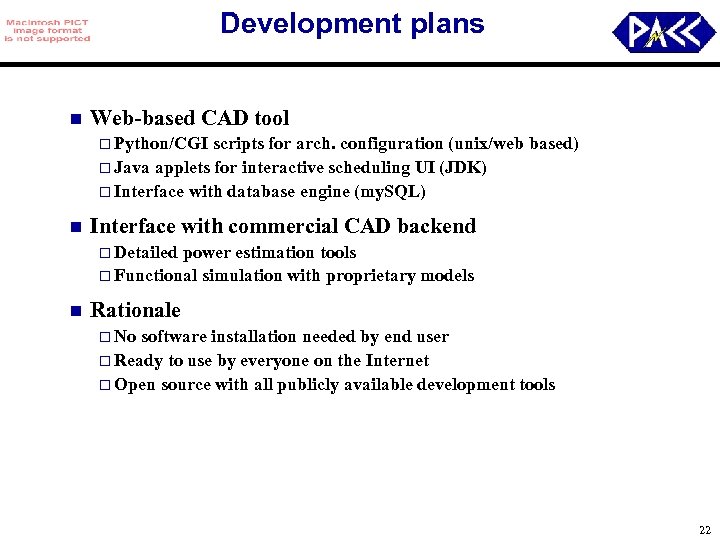

Development plans n Web-based CAD tool o Python/CGI scripts for arch. configuration (unix/web based) o Java applets for interactive scheduling UI (JDK) o Interface with database engine (my. SQL) n Interface with commercial CAD backend o Detailed power estimation tools o Functional simulation with proprietary models n Rationale o No software installation needed by end user o Ready to use by everyone on the Internet o Open source with all publicly available development tools 22

Development plans n Web-based CAD tool o Python/CGI scripts for arch. configuration (unix/web based) o Java applets for interactive scheduling UI (JDK) o Interface with database engine (my. SQL) n Interface with commercial CAD backend o Detailed power estimation tools o Functional simulation with proprietary models n Rationale o No software installation needed by end user o Ready to use by everyone on the Internet o Open source with all publicly available development tools 22

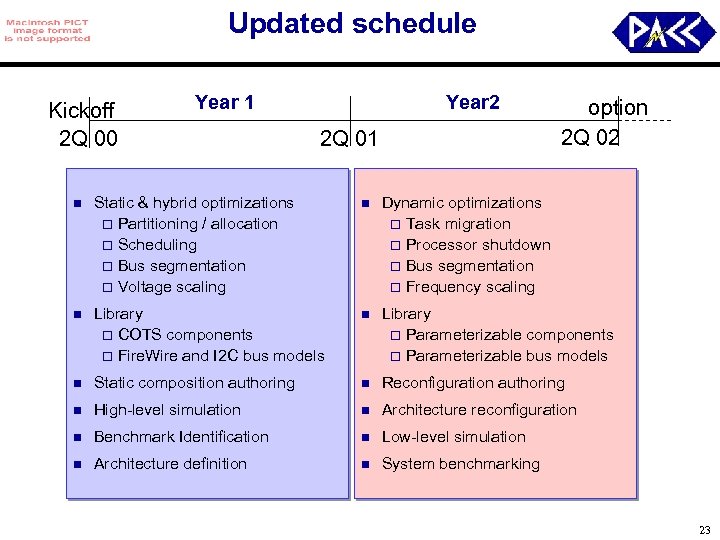

Updated schedule Kickoff 2 Q 00 Year 1 Year 2 2 Q 01 option 2 Q 02 n Static & hybrid optimizations o Partitioning / allocation o Scheduling o Bus segmentation o Voltage scaling n Dynamic optimizations o Task migration o Processor shutdown o Bus segmentation o Frequency scaling n Library o COTS components o Fire. Wire and I 2 C bus models n Library o Parameterizable components o Parameterizable bus models n Static composition authoring n Reconfiguration authoring n High-level simulation n Architecture reconfiguration n Benchmark Identification n Low-level simulation n Architecture definition n System benchmarking 23

Updated schedule Kickoff 2 Q 00 Year 1 Year 2 2 Q 01 option 2 Q 02 n Static & hybrid optimizations o Partitioning / allocation o Scheduling o Bus segmentation o Voltage scaling n Dynamic optimizations o Task migration o Processor shutdown o Bus segmentation o Frequency scaling n Library o COTS components o Fire. Wire and I 2 C bus models n Library o Parameterizable components o Parameterizable bus models n Static composition authoring n Reconfiguration authoring n High-level simulation n Architecture reconfiguration n Benchmark Identification n Low-level simulation n Architecture definition n System benchmarking 23

http: //www. ece. uci. edu/impacct/ 24

http: //www. ece. uci. edu/impacct/ 24

The need for a system-level CAD tool n Avoid pitfalls with manual design o Overdesign (too conservative) o Hardwired assumptions in implementation (hard to change/adapt) o System integration (bottleneck in projects) n Scalable methodology o Specification: l l l separation of concerns Behavior vs. architecture Policy vs. mechanism Constraint vs. implementation o Exploration l l Framework for technique integration Rapid feedback o Manage l l complexity Knowledge base for component/bus details Consistent knowledge propagation through design stages 25

The need for a system-level CAD tool n Avoid pitfalls with manual design o Overdesign (too conservative) o Hardwired assumptions in implementation (hard to change/adapt) o System integration (bottleneck in projects) n Scalable methodology o Specification: l l l separation of concerns Behavior vs. architecture Policy vs. mechanism Constraint vs. implementation o Exploration l l Framework for technique integration Rapid feedback o Manage l l complexity Knowledge base for component/bus details Consistent knowledge propagation through design stages 25