ac1c8404ea5047119e08c905696ffe64.ppt

- Количество слайдов: 80

Input-Output Organization Sumith Gamage 1

Input-Output Organization Sumith Gamage 1

Overview • • Peripheral Devices Input-Output Interface Asynchronous Data Transfer Modes of Transfer Priority Interrupts Direct Memory Access Input-Output Processor Serial Communication 2

Overview • • Peripheral Devices Input-Output Interface Asynchronous Data Transfer Modes of Transfer Priority Interrupts Direct Memory Access Input-Output Processor Serial Communication 2

Peripheral Devices 3

Peripheral Devices 3

Peripheral Devices • Efficient communication between CPU & outside • Gets inputs external sources – Keyboard, mouse, touch screen, barcode reader, modem, NIC, Mic, disk, tape • Send outputs – Monitor, NIC, Printer, Modem, Speaker, disk, tape • Peripheral devices extremely slow to CPU – Large amount of data prepares in advance to transfer to CPU – The result of programs transfer to high-speed disk and then to the peripheral like printers 4

Peripheral Devices • Efficient communication between CPU & outside • Gets inputs external sources – Keyboard, mouse, touch screen, barcode reader, modem, NIC, Mic, disk, tape • Send outputs – Monitor, NIC, Printer, Modem, Speaker, disk, tape • Peripheral devices extremely slow to CPU – Large amount of data prepares in advance to transfer to CPU – The result of programs transfer to high-speed disk and then to the peripheral like printers 4

Peripheral • On-line devices – Devices under direct computer control – Read/write information to memory on CPU command • Peripheral – – – Devices attached to the computer Electromechanical/electromagnetic Monitor/Keyboard Printer Magnetic tape Magnetic disk 5

Peripheral • On-line devices – Devices under direct computer control – Read/write information to memory on CPU command • Peripheral – – – Devices attached to the computer Electromechanical/electromagnetic Monitor/Keyboard Printer Magnetic tape Magnetic disk 5

ASCII Alphanumeric Characters • American Standard Code for Information Interchange • 128 characters – 94 printable • 26 Uppercase, 26 Lowercase, 10 numeric, 32 special (%, *) – 34 non-printable (control) • Abbreviated names – Format characters (BS - backspace, CR - carriage return) – Information separators (RS - record separators, FS - file separators) – Communication controls (STX - start of text, ETX - end of text) 6

ASCII Alphanumeric Characters • American Standard Code for Information Interchange • 128 characters – 94 printable • 26 Uppercase, 26 Lowercase, 10 numeric, 32 special (%, *) – 34 non-printable (control) • Abbreviated names – Format characters (BS - backspace, CR - carriage return) – Information separators (RS - record separators, FS - file separators) – Communication controls (STX - start of text, ETX - end of text) 6

ASCII Alphanumeric Characters • Computer uses 8 bits for a character • Additional bit? – As the parity for character – For other special characters (Italic, Greek) 7

ASCII Alphanumeric Characters • Computer uses 8 bits for a character • Additional bit? – As the parity for character – For other special characters (Italic, Greek) 7

Input-Output Interface • Transfer information between internal storage and external peripherals • Resolves the difference between CPU and peripherals – – Signal value changes Transfer rate mapping Data code format mapping Control operating modes (not to disturb each other) • Interfaces supervise and synchronize transfers • Lies between processor bus and peripheral device (or its controller) 8

Input-Output Interface • Transfer information between internal storage and external peripherals • Resolves the difference between CPU and peripherals – – Signal value changes Transfer rate mapping Data code format mapping Control operating modes (not to disturb each other) • Interfaces supervise and synchronize transfers • Lies between processor bus and peripheral device (or its controller) 8

O/I Bus and Interface Modules • I/O bus consists of – Data lines – Control lines – Address lines • Each peripheral is associated with its interface unit – – Decode address and control received Interrupts for the device Provide signals for device Synchronize and supervise data flow 9

O/I Bus and Interface Modules • I/O bus consists of – Data lines – Control lines – Address lines • Each peripheral is associated with its interface unit – – Decode address and control received Interrupts for the device Provide signals for device Synchronize and supervise data flow 9

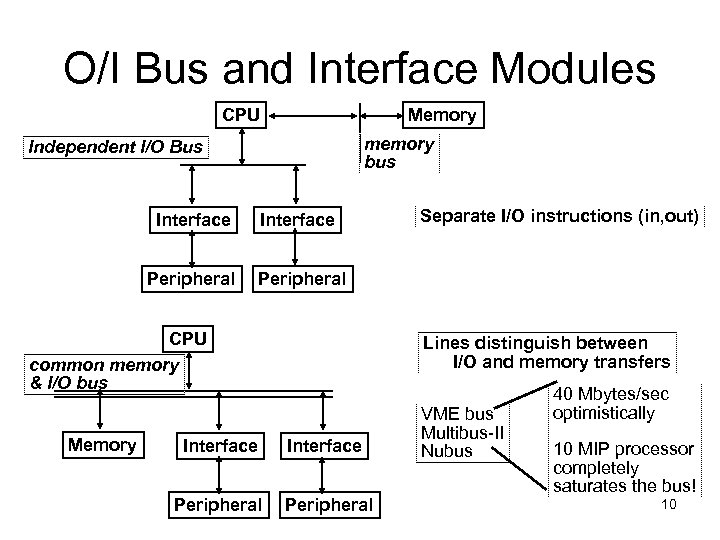

O/I Bus and Interface Modules CPU Memory memory bus Independent I/O Bus Interface Peripheral CPU common memory & I/O bus Memory Separate I/O instructions (in, out) Lines distinguish between I/O and memory transfers Interface Peripheral VME bus Multibus-II Nubus 40 Mbytes/sec optimistically 10 MIP processor completely saturates the bus! 10

O/I Bus and Interface Modules CPU Memory memory bus Independent I/O Bus Interface Peripheral CPU common memory & I/O bus Memory Separate I/O instructions (in, out) Lines distinguish between I/O and memory transfers Interface Peripheral VME bus Multibus-II Nubus 40 Mbytes/sec optimistically 10 MIP processor completely saturates the bus! 10

Input-Output Interface 11

Input-Output Interface 11

I/O Bus and Interface Modules • Each interface has own address • Processor places address on address lines • Corresponding peripheral responds while others are deactivated • Same time processor provides function code on control lines • Interface executes function on peripheral • 4 main command types – Control commands, status, output data, input data 12

I/O Bus and Interface Modules • Each interface has own address • Processor places address on address lines • Corresponding peripheral responds while others are deactivated • Same time processor provides function code on control lines • Interface executes function on peripheral • 4 main command types – Control commands, status, output data, input data 12

I/O vs. Memory Bus • 3 ways to communicate with I/O and memory – Use two separate buses • Uses separate I/O processor • Memory communicate with both IOP and CPU via memory bus • IOP has separate set of data, address and control lines with peripheral interfaces – Use common bus but separate control lines – Common bus and control lines 13

I/O vs. Memory Bus • 3 ways to communicate with I/O and memory – Use two separate buses • Uses separate I/O processor • Memory communicate with both IOP and CPU via memory bus • IOP has separate set of data, address and control lines with peripheral interfaces – Use common bus but separate control lines – Common bus and control lines 13

Isolated vs. Memory-Mapped I/O • Uses common bus for data transfer • Isolated I/O – – Uses separate Memory or I/O R/W lines Separate I/O instruction set Own address spaces for memory and I/O Complex but high flexible • Memory mapped I/O – – – Uses same address space with memory Only one set of R/W signals Interface registers considered as a part of memory system Reduces memory address space available Same instruction set 14

Isolated vs. Memory-Mapped I/O • Uses common bus for data transfer • Isolated I/O – – Uses separate Memory or I/O R/W lines Separate I/O instruction set Own address spaces for memory and I/O Complex but high flexible • Memory mapped I/O – – – Uses same address space with memory Only one set of R/W signals Interface registers considered as a part of memory system Reduces memory address space available Same instruction set 14

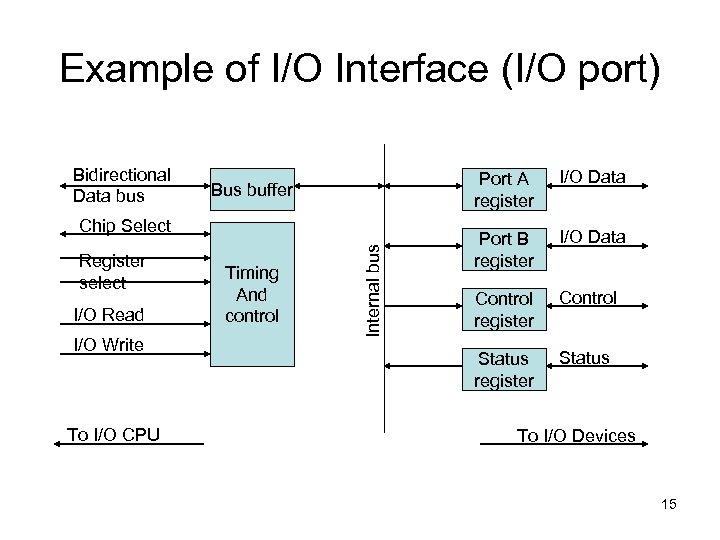

Example of I/O Interface (I/O port) Bidirectional Data bus Port A register Bus buffer Register select I/O Read I/O Write To I/O CPU Timing And control Internal bus Chip Select I/O Data Port B register I/O Data Control register Control Status register Status To I/O Devices 15

Example of I/O Interface (I/O port) Bidirectional Data bus Port A register Bus buffer Register select I/O Read I/O Write To I/O CPU Timing And control Internal bus Chip Select I/O Data Port B register I/O Data Control register Control Status register Status To I/O Devices 15

Example of I/O Interface (I/O port) • Interface communicate with CPU though data bus • CS and RS determine interface address • Set of 4 registers directly communicate with the device • I/O data can transfer port A or B • Interface can use bidirectional lines when it is connected to – Input only (Character reader) – Output only (Printer) – Both (but not at the same time) (Hard disk) 16

Example of I/O Interface (I/O port) • Interface communicate with CPU though data bus • CS and RS determine interface address • Set of 4 registers directly communicate with the device • I/O data can transfer port A or B • Interface can use bidirectional lines when it is connected to – Input only (Character reader) – Output only (Printer) – Both (but not at the same time) (Hard disk) 16

Example of I/O Interface (I/O port) • Issue commands – write command word to control register • Receive status – reading from status register • Data transfer – via port A and B registers • Function code of I/O bus not used CS RS 1 RS 0 Register selected 0 X X None: data bus in high impedance 1 0 0 Port A register 1 0 1 Port B register 1 1 0 Control register 1 1 1 Status register 17

Example of I/O Interface (I/O port) • Issue commands – write command word to control register • Receive status – reading from status register • Data transfer – via port A and B registers • Function code of I/O bus not used CS RS 1 RS 0 Register selected 0 X X None: data bus in high impedance 1 0 0 Port A register 1 0 1 Port B register 1 1 0 Control register 1 1 1 Status register 17

Asynchronous Data Transfer 18

Asynchronous Data Transfer 18

Asynchronous Data Transfer • Internal operations in a computer are synchronize with internal clock pulse generator – Applied to all registers – All data transfer among registers happen at the same time with the occurrence of the clock pulse • But the CPU and I/O interfaces are independent – They run on their own clocks – If I/O shares common clock with CPU two units said to be synchronize. – Otherwise asynchronous 19

Asynchronous Data Transfer • Internal operations in a computer are synchronize with internal clock pulse generator – Applied to all registers – All data transfer among registers happen at the same time with the occurrence of the clock pulse • But the CPU and I/O interfaces are independent – They run on their own clocks – If I/O shares common clock with CPU two units said to be synchronize. – Otherwise asynchronous 19

Asynchronous Data Transfer • Asynchronous data transfer – Requires control signals to indicate time at which transmission occurs • Main methods of indicate data transfer time – Strobe - Giving a signal by one unit to indicate transfer time – Handshaking - Transfer on agreement • Data transfer with a control signal indicating the presence of data • Data receiver sends an acknowledge receipt of data • Timing diagrams are commonly used to show the relationship between control signals • Sequence of control signals depends whether transfer initiated by source or destination 20

Asynchronous Data Transfer • Asynchronous data transfer – Requires control signals to indicate time at which transmission occurs • Main methods of indicate data transfer time – Strobe - Giving a signal by one unit to indicate transfer time – Handshaking - Transfer on agreement • Data transfer with a control signal indicating the presence of data • Data receiver sends an acknowledge receipt of data • Timing diagrams are commonly used to show the relationship between control signals • Sequence of control signals depends whether transfer initiated by source or destination 20

Strobe Control • Uses a control line to time each transfer • Strobe is activated either by source or destination • Strobe says when there is valid data on data bus • Generally strobes activated by clock signals • CPU is always in control of the transfer (i. e. strobe is always from CPU) • This method is mainly applicable in memory R/W operations. • Most of I/O operations use handshaking 21

Strobe Control • Uses a control line to time each transfer • Strobe is activated either by source or destination • Strobe says when there is valid data on data bus • Generally strobes activated by clock signals • CPU is always in control of the transfer (i. e. strobe is always from CPU) • This method is mainly applicable in memory R/W operations. • Most of I/O operations use handshaking 21

Source initiated data transfer • • Source places data on the bus Have a brief delay to settle data on the bus Source activate the strobe pulse Then destination reads data to internal register (Often uses falling edge) • Source removes data after brief delay (Not necessary) Source Unit Data bus Strobe Destination Unit Valid Data Strobe 22

Source initiated data transfer • • Source places data on the bus Have a brief delay to settle data on the bus Source activate the strobe pulse Then destination reads data to internal register (Often uses falling edge) • Source removes data after brief delay (Not necessary) Source Unit Data bus Strobe Destination Unit Valid Data Strobe 22

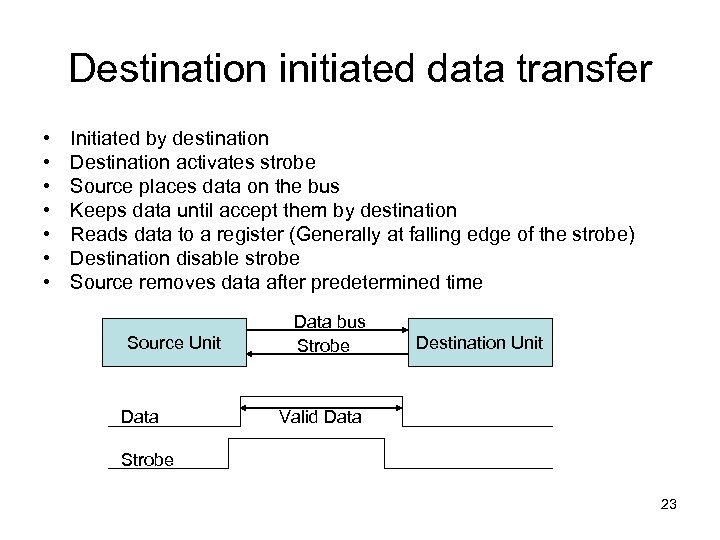

Destination initiated data transfer • • Initiated by destination Destination activates strobe Source places data on the bus Keeps data until accept them by destination Reads data to a register (Generally at falling edge of the strobe) Destination disable strobe Source removes data after predetermined time Source Unit Data bus Strobe Destination Unit Valid Data Strobe 23

Destination initiated data transfer • • Initiated by destination Destination activates strobe Source places data on the bus Keeps data until accept them by destination Reads data to a register (Generally at falling edge of the strobe) Destination disable strobe Source removes data after predetermined time Source Unit Data bus Strobe Destination Unit Valid Data Strobe 23

Handshaking • Strobe disadvantage – In source initiation - Source doesn’t know whether destination got the data – In destination initiation – Destination doesn’t know whether source has placed the data on the bus • Handshaking introduce a reply method to solve this problem 24

Handshaking • Strobe disadvantage – In source initiation - Source doesn’t know whether destination got the data – In destination initiation – Destination doesn’t know whether source has placed the data on the bus • Handshaking introduce a reply method to solve this problem 24

Two wired handshaking • 1 st control line – Same direction as the data flow – Use by the source – Indicates whether it has valid data • 2 nd control line – From destination to source – Uses by the destination – Indicates whether it can accept data • Sequence of control used depends on the unit initiate transfer • In a fault at one end timeout uses to detect the error 25

Two wired handshaking • 1 st control line – Same direction as the data flow – Use by the source – Indicates whether it has valid data • 2 nd control line – From destination to source – Uses by the destination – Indicates whether it can accept data • Sequence of control used depends on the unit initiate transfer • In a fault at one end timeout uses to detect the error 25

Source Initiated Transfer Source Unit Data bus Data valid Data accepted Destination Unit Block Diagram Data bus Timing Diagram Data valid Data accepted Place data on bus Enable data valid Disable data valid Invalidate data on bus Accept data from bus Enable data accept Initial stage Disable data accepted Ready to accept data Sequence of events 26

Source Initiated Transfer Source Unit Data bus Data valid Data accepted Destination Unit Block Diagram Data bus Timing Diagram Data valid Data accepted Place data on bus Enable data valid Disable data valid Invalidate data on bus Accept data from bus Enable data accept Initial stage Disable data accepted Ready to accept data Sequence of events 26

Destination Initiated Transfer Source Unit Data bus Data valid Ready for data Destination Unit Block Diagram Ready for data Timing Diagram Data valid Data bus Ready to accept data Enable ready for data Place data on bus Enable data valid Initial stage Disable data valid Invalidate data on bus Accept data from bus Disable ready for data Sequence of events 27

Destination Initiated Transfer Source Unit Data bus Data valid Ready for data Destination Unit Block Diagram Ready for data Timing Diagram Data valid Data bus Ready to accept data Enable ready for data Place data on bus Enable data valid Initial stage Disable data valid Invalidate data on bus Accept data from bus Disable ready for data Sequence of events 27

Asynchronous Serial Transfer • Parallel transmission – – – Each bit of message has its own path Total message transmitted at the same time N bit message requires N conduction paths Faster/expensive Short distance transmission • Serial transmission – Each bit in message sent in sequence one at a time – Uses only one pair of conductors (or one conductor with a common ground – Slower/cheaper – Uses for long distance transmission 28

Asynchronous Serial Transfer • Parallel transmission – – – Each bit of message has its own path Total message transmitted at the same time N bit message requires N conduction paths Faster/expensive Short distance transmission • Serial transmission – Each bit in message sent in sequence one at a time – Uses only one pair of conductors (or one conductor with a common ground – Slower/cheaper – Uses for long distance transmission 28

Asynchronous Serial Transfer • Synchronous – Uses common clock frequency – Transmits bits continuously – For long distance transmission • Use separate clocks with same frequency • Keep clocks in step via synchronization signals send periodically – Periodic synchronization signals should transfer even no data to transmit • Asynchronous – – – Transmits only when data available to transmit Otherwise keeps in idle Uses start and stop bits at the both ends of the character code Transmission line rests at state 1 while idle Start bit is always 0 Stop bit can be 1 or more 1 s 29

Asynchronous Serial Transfer • Synchronous – Uses common clock frequency – Transmits bits continuously – For long distance transmission • Use separate clocks with same frequency • Keep clocks in step via synchronization signals send periodically – Periodic synchronization signals should transfer even no data to transmit • Asynchronous – – – Transmits only when data available to transmit Otherwise keeps in idle Uses start and stop bits at the both ends of the character code Transmission line rests at state 1 while idle Start bit is always 0 Stop bit can be 1 or more 1 s 29

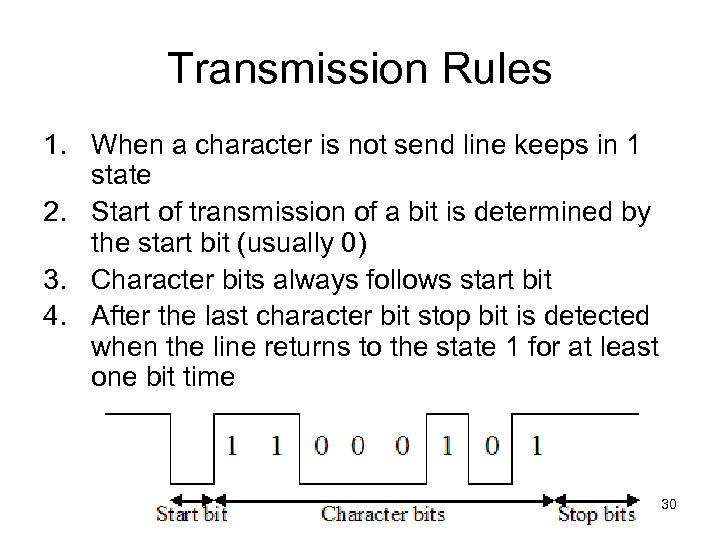

Transmission Rules 1. When a character is not send line keeps in 1 state 2. Start of transmission of a bit is determined by the start bit (usually 0) 3. Character bits always follows start bit 4. After the last character bit stop bit is detected when the line returns to the state 1 for at least one bit time 30

Transmission Rules 1. When a character is not send line keeps in 1 state 2. Start of transmission of a bit is determined by the start bit (usually 0) 3. Character bits always follows start bit 4. After the last character bit stop bit is detected when the line returns to the state 1 for at least one bit time 30

How it works • Using transmission rules receiver detects start bit when line goes 1 to 0 • Receiver knows – Bit transmission rate – Number of bits in character • After a character transmission line keeps at state 1 for at least one or two bits for resynchronization at both transmitter and receiver • Ex: Transmission rate 10 characters/sec (at 1 start bit, 8 info bits and 2 stop bits) (1+8+2)*10 bit/s 110 bit/s • i. e. baud rate 110 baud 31

How it works • Using transmission rules receiver detects start bit when line goes 1 to 0 • Receiver knows – Bit transmission rate – Number of bits in character • After a character transmission line keeps at state 1 for at least one or two bits for resynchronization at both transmitter and receiver • Ex: Transmission rate 10 characters/sec (at 1 start bit, 8 info bits and 2 stop bits) (1+8+2)*10 bit/s 110 bit/s • i. e. baud rate 110 baud 31

Definitions • Baud rate – Rate at which serial information is transmitted and equivalent to the data transfer in bits per second • UART – Universal Asynchronous Receiver -Transmitter (Asynchronous Communication Interface) – An interface which accept 8 bit character code from a computer and forward corresponding 11 bit serial code to the device or does the function other way around 32

Definitions • Baud rate – Rate at which serial information is transmitted and equivalent to the data transfer in bits per second • UART – Universal Asynchronous Receiver -Transmitter (Asynchronous Communication Interface) – An interface which accept 8 bit character code from a computer and forward corresponding 11 bit serial code to the device or does the function other way around 32

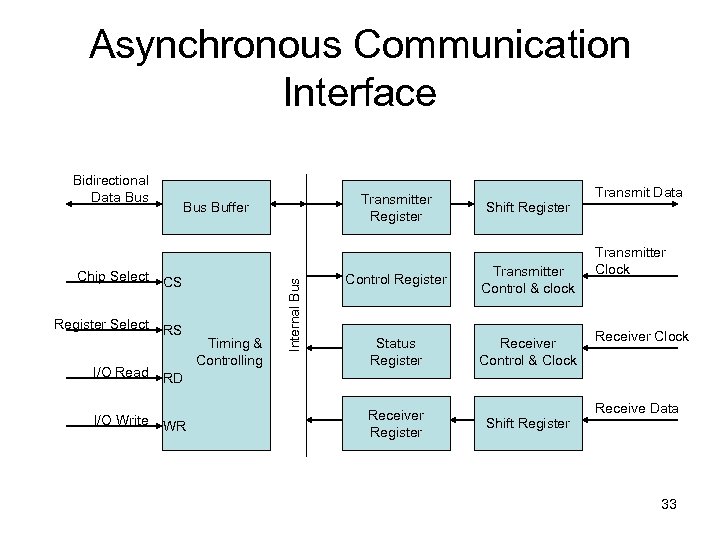

Asynchronous Communication Interface Bidirectional Data Bus CS Register Select RS I/O Write Timing & Controlling Internal Bus Buffer Chip Select I/O Read Transmitter Register Shift Register Control Register Transmitter Control & clock Status Register Receiver Control & Clock Transmit Data Transmitter Clock Receiver Clock RD WR Receiver Register Shift Register Receive Data 33

Asynchronous Communication Interface Bidirectional Data Bus CS Register Select RS I/O Write Timing & Controlling Internal Bus Buffer Chip Select I/O Read Transmitter Register Shift Register Control Register Transmitter Control & clock Status Register Receiver Control & Clock Transmit Data Transmitter Clock Receiver Clock RD WR Receiver Register Shift Register Receive Data 33

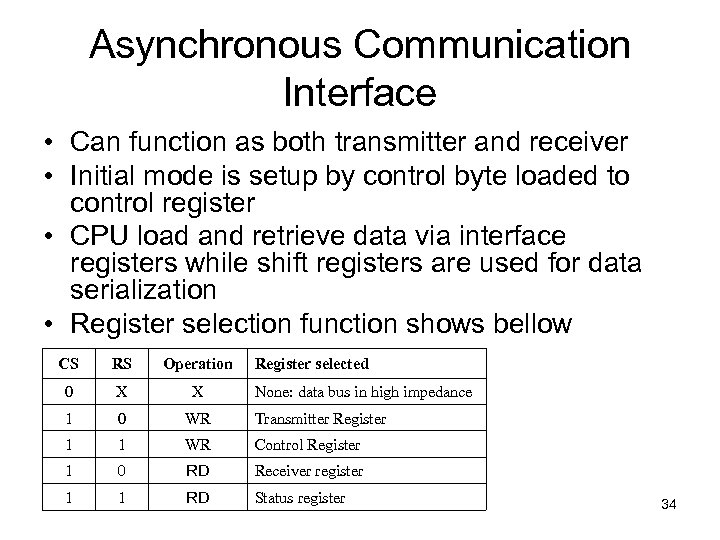

Asynchronous Communication Interface • Can function as both transmitter and receiver • Initial mode is setup by control byte loaded to control register • CPU load and retrieve data via interface registers while shift registers are used for data serialization • Register selection function shows bellow CS RS Operation Register selected 0 X X 1 0 WR Transmitter Register 1 1 WR Control Register 1 0 RD Receiver register 1 1 RD Status register None: data bus in high impedance 34

Asynchronous Communication Interface • Can function as both transmitter and receiver • Initial mode is setup by control byte loaded to control register • CPU load and retrieve data via interface registers while shift registers are used for data serialization • Register selection function shows bellow CS RS Operation Register selected 0 X X 1 0 WR Transmitter Register 1 1 WR Control Register 1 0 RD Receiver register 1 1 RD Status register None: data bus in high impedance 34

Operation • Start by CPU by sending a byte to control register specifying – – – Mode of operation Baud rate to use Bits in each character No of stops bits should append Whether to use parity check • Status register – 2 bit Flags • Transmit register is empty • Receiver register is full 35

Operation • Start by CPU by sending a byte to control register specifying – – – Mode of operation Baud rate to use Bits in each character No of stops bits should append Whether to use parity check • Status register – 2 bit Flags • Transmit register is empty • Receiver register is full 35

Operation • Transmitter – CPU reads status register – Check flag to know whether transmit register is empty – If empty CPU transfer character to transmit register & interface marks register full – Set 1 st bit of shift register to 0, transfer character there and append appropriate no of stop bits – Mark transmit register empty – Character is transmitted bit at a time in specified baud rate – CPU can load another character after checking flag – This is a double buffered interface, since new character can be loaded as soon as previous one start transmission • Receiver ? 36

Operation • Transmitter – CPU reads status register – Check flag to know whether transmit register is empty – If empty CPU transfer character to transmit register & interface marks register full – Set 1 st bit of shift register to 0, transfer character there and append appropriate no of stop bits – Mark transmit register empty – Character is transmitted bit at a time in specified baud rate – CPU can load another character after checking flag – This is a double buffered interface, since new character can be loaded as soon as previous one start transmission • Receiver ? 36

Operation • Receiver – Receive data input line is in state 1 when line is idle – Receiver controller monitors input line for occurrence of a 0 – Once start bit detected incoming bits of character are shifted to register at prescribed baud rate – Then it checks for parity and stop bits – Character without start and stop bits transfer in parallel to the receiver register – Flag in status register set to indicate receiver register is full – CPU checks flag and if data available read data and clears receiver register full flag • Possible receiving error – Parity error – Failure in parity bit checking – Framing error – Invalid stop bits – Overrun error – Write next character before read previous by CPU 37

Operation • Receiver – Receive data input line is in state 1 when line is idle – Receiver controller monitors input line for occurrence of a 0 – Once start bit detected incoming bits of character are shifted to register at prescribed baud rate – Then it checks for parity and stop bits – Character without start and stop bits transfer in parallel to the receiver register – Flag in status register set to indicate receiver register is full – CPU checks flag and if data available read data and clears receiver register full flag • Possible receiving error – Parity error – Failure in parity bit checking – Framing error – Invalid stop bits – Overrun error – Write next character before read previous by CPU 37

Modes of Transfer 38

Modes of Transfer 38

Modes of Transfer • CPU merely execute instruction and accept data temporally from I/O devices • Ultimate source and destination is memory – Receiving data from input devices stores in memory – Sending data to output devices from memory • I/O handling modes – Programmed I/O – Interrupt-initiated I/O – Direct Memory Access (DMA) 39

Modes of Transfer • CPU merely execute instruction and accept data temporally from I/O devices • Ultimate source and destination is memory – Receiving data from input devices stores in memory – Sending data to output devices from memory • I/O handling modes – Programmed I/O – Interrupt-initiated I/O – Direct Memory Access (DMA) 39

Programmed I/O • I/O instructions are executed according to a program in CPU • I/O instruction transfers from and to CPU registers • A memory load instruction used to load it memory • Another instruction used to verify data and count the number of words transferred • Constant I/O monitoring is required by CPU • CPU stays in a program loop until I/O unit indicate data ready • This waste CPU time 40

Programmed I/O • I/O instructions are executed according to a program in CPU • I/O instruction transfers from and to CPU registers • A memory load instruction used to load it memory • Another instruction used to verify data and count the number of words transferred • Constant I/O monitoring is required by CPU • CPU stays in a program loop until I/O unit indicate data ready • This waste CPU time 40

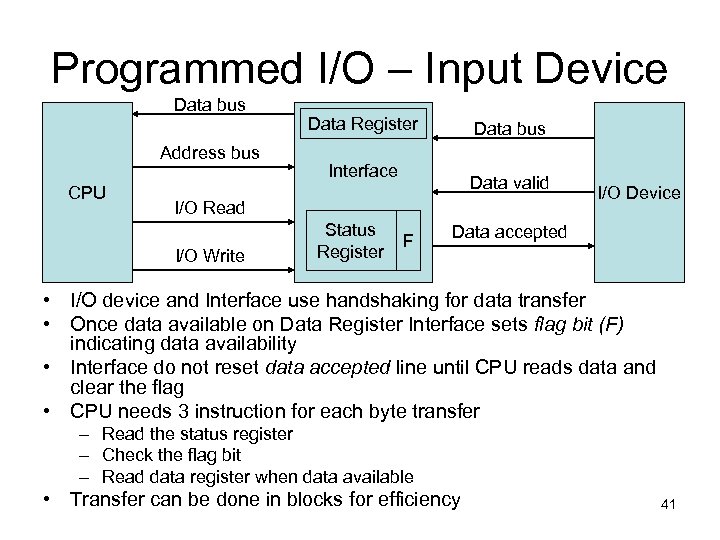

Programmed I/O – Input Device Data bus Address bus CPU Data Register Data bus Interface Data valid I/O Read I/O Write Status Register F I/O Device Data accepted • I/O device and Interface use handshaking for data transfer • Once data available on Data Register Interface sets flag bit (F) indicating data availability • Interface do not reset data accepted line until CPU reads data and clear the flag • CPU needs 3 instruction for each byte transfer – Read the status register – Check the flag bit – Read data register when data available • Transfer can be done in blocks for efficiency 41

Programmed I/O – Input Device Data bus Address bus CPU Data Register Data bus Interface Data valid I/O Read I/O Write Status Register F I/O Device Data accepted • I/O device and Interface use handshaking for data transfer • Once data available on Data Register Interface sets flag bit (F) indicating data availability • Interface do not reset data accepted line until CPU reads data and clear the flag • CPU needs 3 instruction for each byte transfer – Read the status register – Check the flag bit – Read data register when data available • Transfer can be done in blocks for efficiency 41

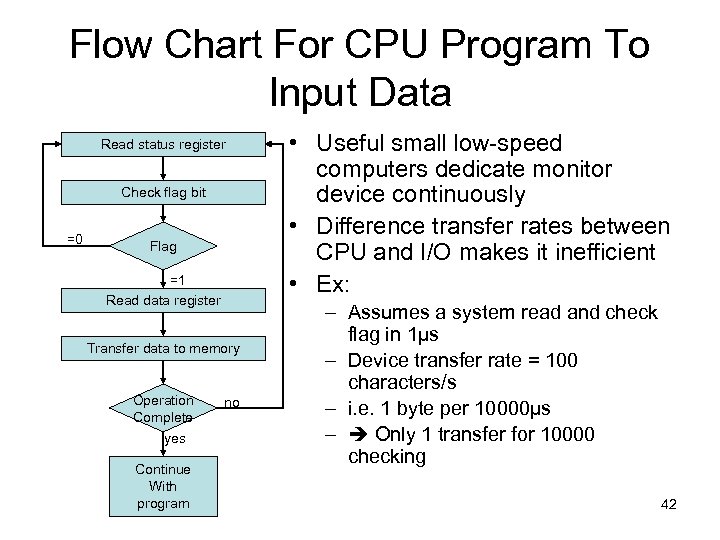

Flow Chart For CPU Program To Input Data Read status register Check flag bit =0 Flag =1 Read data register Transfer data to memory Operation Complete yes Continue With program no • Useful small low-speed computers dedicate monitor device continuously • Difference transfer rates between CPU and I/O makes it inefficient • Ex: – Assumes a system read and check flag in 1µs – Device transfer rate = 100 characters/s – i. e. 1 byte per 10000µs – Only 1 transfer for 10000 checking 42

Flow Chart For CPU Program To Input Data Read status register Check flag bit =0 Flag =1 Read data register Transfer data to memory Operation Complete yes Continue With program no • Useful small low-speed computers dedicate monitor device continuously • Difference transfer rates between CPU and I/O makes it inefficient • Ex: – Assumes a system read and check flag in 1µs – Device transfer rate = 100 characters/s – i. e. 1 byte per 10000µs – Only 1 transfer for 10000 checking 42

Interrupt Initiated I/O • Instead of continues monitoring at CPU interface inform when data ready • Uses interrupts • CPU deviated from current program and take care of data transfer – Save return address from program counter to stack – Then control branches to service routing • Non vectored interrupts • Vectored interrupts • After completing I/O transfer it returns back to previous program 43

Interrupt Initiated I/O • Instead of continues monitoring at CPU interface inform when data ready • Uses interrupts • CPU deviated from current program and take care of data transfer – Save return address from program counter to stack – Then control branches to service routing • Non vectored interrupts • Vectored interrupts • After completing I/O transfer it returns back to previous program 43

Software Consideration • In addition to h/w computer should have s/w routings to control interface and transfer data • Ex: Control commands – activate peripheral, check data state, stop tape, print character, issue interrupt • I/O control software is fairly complex • Standard I/O routing provided by the manufacturer and included with OS • I/O routings available as OS procedures; do not need to go to assembly level details 44

Software Consideration • In addition to h/w computer should have s/w routings to control interface and transfer data • Ex: Control commands – activate peripheral, check data state, stop tape, print character, issue interrupt • I/O control software is fairly complex • Standard I/O routing provided by the manufacturer and included with OS • I/O routings available as OS procedures; do not need to go to assembly level details 44

Priority Interrupts 45

Priority Interrupts 45

Priority Interrupts • Generally I/O data transfer is initiated by CPU • But device must be ready first • Device readiness for data transfer can be identify by the interrupt signal • How CPU responds to the interrupt request – Push return address to the memory stack – Branch to the interrupt service routing • Priority Interrupt system – Deals with simultaneous interrupts and determine which one to serve first (critical situation / fast I/O) – Determine in which conditions allow interrupting while executing another interrupt service routing 46

Priority Interrupts • Generally I/O data transfer is initiated by CPU • But device must be ready first • Device readiness for data transfer can be identify by the interrupt signal • How CPU responds to the interrupt request – Push return address to the memory stack – Branch to the interrupt service routing • Priority Interrupt system – Deals with simultaneous interrupts and determine which one to serve first (critical situation / fast I/O) – Determine in which conditions allow interrupting while executing another interrupt service routing 46

Polling (Software) • • Priority identification mechanism in software For all interrupts has a common branch address Then polls the interrupt devices in sequence The order at which it polls determine the priority – – Higher priority device is tested first. If its interrupt signal is on serves the device Then test for the next device Proceed on until last device • Disadvantage: When there are multiple interrupts polling time might exceed time available to service the I/O device • Solution: Hardware priority interrupts unit 47

Polling (Software) • • Priority identification mechanism in software For all interrupts has a common branch address Then polls the interrupt devices in sequence The order at which it polls determine the priority – – Higher priority device is tested first. If its interrupt signal is on serves the device Then test for the next device Proceed on until last device • Disadvantage: When there are multiple interrupts polling time might exceed time available to service the I/O device • Solution: Hardware priority interrupts unit 47

Hardware Priority Interrupt Units • • Accepts interrupts from many sources Determine which one has higher priority Issue interrupt accordingly to the CPU Further each interrupt source has its own interrupt vector to access its own service routing directly • No polling required • 2 major establishments of hardware priority function – Serial Connection (Daisy-chain) – Parallel Connection 48

Hardware Priority Interrupt Units • • Accepts interrupts from many sources Determine which one has higher priority Issue interrupt accordingly to the CPU Further each interrupt source has its own interrupt vector to access its own service routing directly • No polling required • 2 major establishments of hardware priority function – Serial Connection (Daisy-chain) – Parallel Connection 48

Daisy Chain Priority data bus PI VAD Device 1 P 0 PI VAD Device 2 P 0 PI Interrupt request Interrupt acknowledge • • • VAD Device 3 P 0 To Next Device INT CPU INTACK Serial connection of all interrupt devices Higher priority one places first Interrupt request line is common (wired logic) CPU responds interrupt via Interrupt Acknowledge line If Device 1 has pending interrupt disable P 1 and place its own Interrupt vector. Otherwise pass it to the next device via P 0 49

Daisy Chain Priority data bus PI VAD Device 1 P 0 PI VAD Device 2 P 0 PI Interrupt request Interrupt acknowledge • • • VAD Device 3 P 0 To Next Device INT CPU INTACK Serial connection of all interrupt devices Higher priority one places first Interrupt request line is common (wired logic) CPU responds interrupt via Interrupt Acknowledge line If Device 1 has pending interrupt disable P 1 and place its own Interrupt vector. Otherwise pass it to the next device via P 0 49

Parallel Priority Interrupt Register Disk I 0 Printer I 1 Reader I 2 Keyboard I 3 Priority Encoder IEN IST VAD To CPU Y X 0 0 0 Enable Interrupt to CPU Mask Register INTACK from CPU 50

Parallel Priority Interrupt Register Disk I 0 Printer I 1 Reader I 2 Keyboard I 3 Priority Encoder IEN IST VAD To CPU Y X 0 0 0 Enable Interrupt to CPU Mask Register INTACK from CPU 50

Parallel Priority Interrupt • Uses a register to set interrupt bits by each device • Uses Mask Register change the sequence of servicing • Priority encoder generates Interrupt Vector • CPU interrupt is generated only when Interrupt. ENable and Interrupt. STate are set • IEN can be set by the program • With the INTACK from CPU VAD is put on to the bus 51

Parallel Priority Interrupt • Uses a register to set interrupt bits by each device • Uses Mask Register change the sequence of servicing • Priority encoder generates Interrupt Vector • CPU interrupt is generated only when Interrupt. ENable and Interrupt. STate are set • IEN can be set by the program • With the INTACK from CPU VAD is put on to the bus 51

Priority Encoder • Implements the priority function Inputs Outputs I 0 I 1 I 2 I 3 x y I Boolean S function T 1 x x x 0 0 1 x x 0 1 1 0 0 1 x 1 0 0 0 0 1 1 x = I 0 ’ I 1 ’ x = I 0 ’ I 1 + I 0 ’ 1 I 2 ’ (IST) = I 0 + I 1 + 1 I 2 + I 3 0 52

Priority Encoder • Implements the priority function Inputs Outputs I 0 I 1 I 2 I 3 x y I Boolean S function T 1 x x x 0 0 1 x x 0 1 1 0 0 1 x 1 0 0 0 0 1 1 x = I 0 ’ I 1 ’ x = I 0 ’ I 1 + I 0 ’ 1 I 2 ’ (IST) = I 0 + I 1 + 1 I 2 + I 3 0 52

Interrupt Cycle • IEN uses by the program to enable or disable interrupts while running • At the end of each instruction cycle CPU checks IEN and if enabled checks IST • Sequence of micro operations follows as receive an interrupt: – – – SP – 1 M[SP] PC INTACK 1 PC VAD IEN 0 Go to fetch next instruction 53

Interrupt Cycle • IEN uses by the program to enable or disable interrupts while running • At the end of each instruction cycle CPU checks IEN and if enabled checks IST • Sequence of micro operations follows as receive an interrupt: – – – SP – 1 M[SP] PC INTACK 1 PC VAD IEN 0 Go to fetch next instruction 53

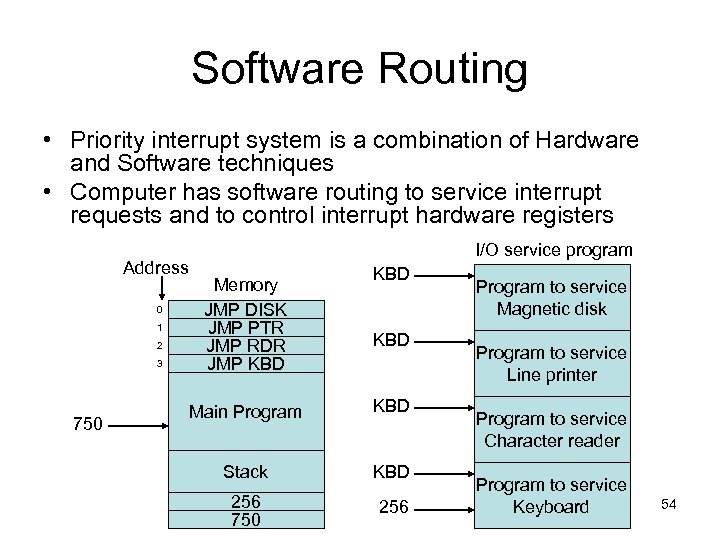

Software Routing • Priority interrupt system is a combination of Hardware and Software techniques • Computer has software routing to service interrupt requests and to control interrupt hardware registers Address 0 1 2 3 750 I/O service program Memory JMP DISK JMP PTR JMP RDR JMP KBD KBD Main Program KBD Stack KBD 256 750 256 Program to service Magnetic disk Program to service Line printer Program to service Character reader Program to service Keyboard 54

Software Routing • Priority interrupt system is a combination of Hardware and Software techniques • Computer has software routing to service interrupt requests and to control interrupt hardware registers Address 0 1 2 3 750 I/O service program Memory JMP DISK JMP PTR JMP RDR JMP KBD KBD Main Program KBD Stack KBD 256 750 256 Program to service Magnetic disk Program to service Line printer Program to service Character reader Program to service Keyboard 54

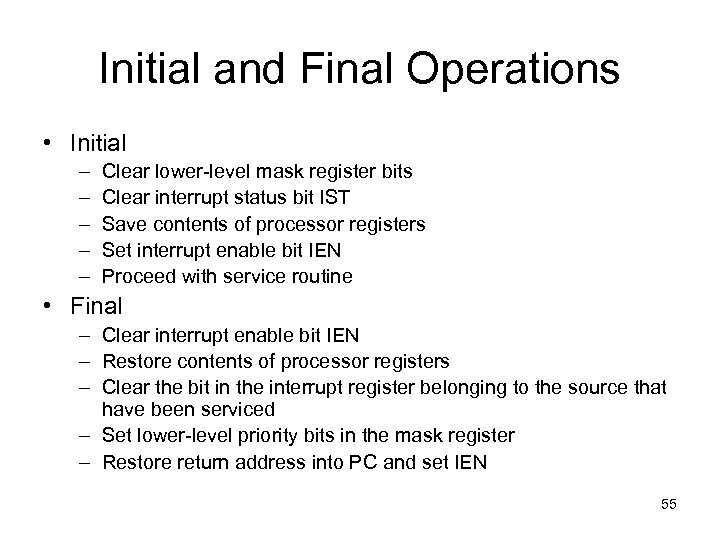

Initial and Final Operations • Initial – – – Clear lower-level mask register bits Clear interrupt status bit IST Save contents of processor registers Set interrupt enable bit IEN Proceed with service routine • Final – Clear interrupt enable bit IEN – Restore contents of processor registers – Clear the bit in the interrupt register belonging to the source that have been serviced – Set lower-level priority bits in the mask register – Restore return address into PC and set IEN 55

Initial and Final Operations • Initial – – – Clear lower-level mask register bits Clear interrupt status bit IST Save contents of processor registers Set interrupt enable bit IEN Proceed with service routine • Final – Clear interrupt enable bit IEN – Restore contents of processor registers – Clear the bit in the interrupt register belonging to the source that have been serviced – Set lower-level priority bits in the mask register – Restore return address into PC and set IEN 55

DMA (Direct Memory Access) 56

DMA (Direct Memory Access) 56

Direct Memory Access - DMA • CPU limits the data transfer speed for fast I/O devices • DMA removes CPU and allow peripherals to handle memory bus • During the transfer CPU does not have the control over the bus • CPU idling the bus can be done through the control signals “Bus Request” & “Bus Grant” – DMA controller enables BR, – then CPU finishes current operation and puts its address and data buses in high impedance – CPU sets BG line – DMA transfers data and resets BR for the CPU to use the memory bus • DMA data transfer can either happen as – Burst transfer or – Cycle stealing 57

Direct Memory Access - DMA • CPU limits the data transfer speed for fast I/O devices • DMA removes CPU and allow peripherals to handle memory bus • During the transfer CPU does not have the control over the bus • CPU idling the bus can be done through the control signals “Bus Request” & “Bus Grant” – DMA controller enables BR, – then CPU finishes current operation and puts its address and data buses in high impedance – CPU sets BG line – DMA transfers data and resets BR for the CPU to use the memory bus • DMA data transfer can either happen as – Burst transfer or – Cycle stealing 57

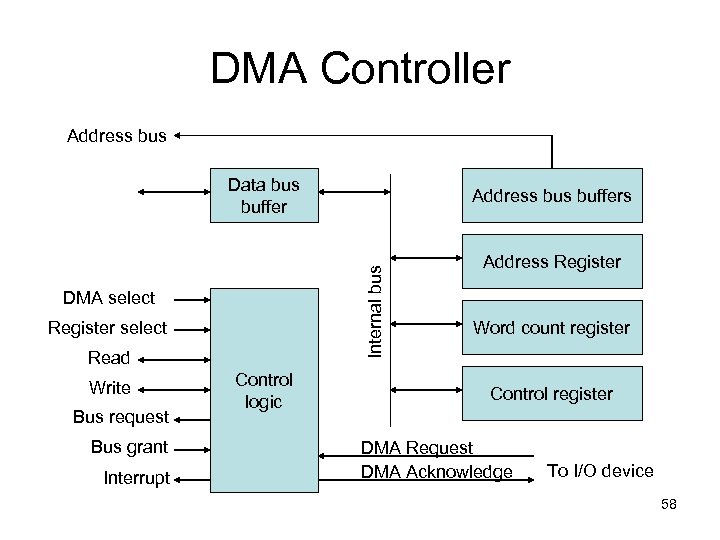

DMA Controller Address bus Data bus buffer Internal bus DMA select Register select Read Write Bus request Bus grant Interrupt Address buffers Control logic Address Register Word count register Control register DMA Request DMA Acknowledge To I/O device 58

DMA Controller Address bus Data bus buffer Internal bus DMA select Register select Read Write Bus request Bus grant Interrupt Address buffers Control logic Address Register Word count register Control register DMA Request DMA Acknowledge To I/O device 58

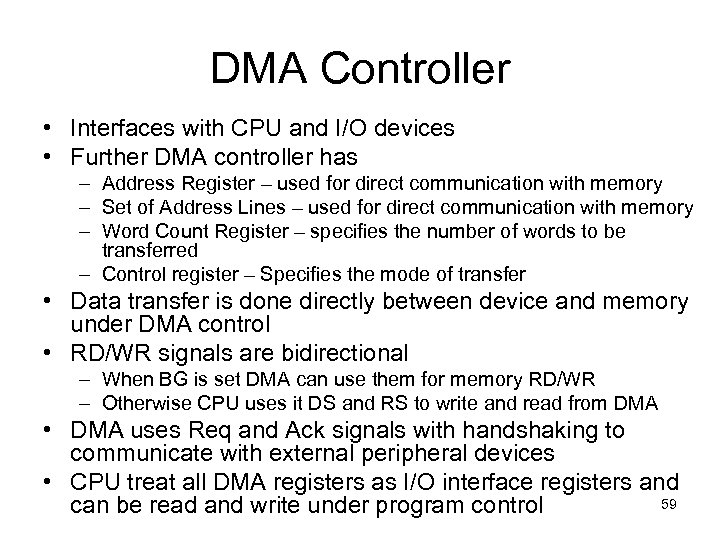

DMA Controller • Interfaces with CPU and I/O devices • Further DMA controller has – Address Register – used for direct communication with memory – Set of Address Lines – used for direct communication with memory – Word Count Register – specifies the number of words to be transferred – Control register – Specifies the mode of transfer • Data transfer is done directly between device and memory under DMA control • RD/WR signals are bidirectional – When BG is set DMA can use them for memory RD/WR – Otherwise CPU uses it DS and RS to write and read from DMA • DMA uses Req and Ack signals with handshaking to communicate with external peripheral devices • CPU treat all DMA registers as I/O interface registers and 59 can be read and write under program control

DMA Controller • Interfaces with CPU and I/O devices • Further DMA controller has – Address Register – used for direct communication with memory – Set of Address Lines – used for direct communication with memory – Word Count Register – specifies the number of words to be transferred – Control register – Specifies the mode of transfer • Data transfer is done directly between device and memory under DMA control • RD/WR signals are bidirectional – When BG is set DMA can use them for memory RD/WR – Otherwise CPU uses it DS and RS to write and read from DMA • DMA uses Req and Ack signals with handshaking to communicate with external peripheral devices • CPU treat all DMA registers as I/O interface registers and 59 can be read and write under program control

DMA Controller • DMA is initialized by CPU • Then DMA continues transfer an entire block of data between memory and peripheral • CPU sends following information on DMA initialization – – Starting address for memory read or write Word count the number of words to be transferred Control to specify mode of transfer Control to start transfer • CPU communicates with DMA after transfer initialization only if – It receives an interrupt – It wants to know how many words have been transferred 60

DMA Controller • DMA is initialized by CPU • Then DMA continues transfer an entire block of data between memory and peripheral • CPU sends following information on DMA initialization – – Starting address for memory read or write Word count the number of words to be transferred Control to specify mode of transfer Control to start transfer • CPU communicates with DMA after transfer initialization only if – It receives an interrupt – It wants to know how many words have been transferred 60

DMA Transfer • CPU communicates with DMA through address and data bus as with any other interface unit • DMA has its own address by which DS & RS activates • CPU initialize DMA through data bus • DMA can start data transfer between memory and peripheral device as it gets the control command 61

DMA Transfer • CPU communicates with DMA through address and data bus as with any other interface unit • DMA has its own address by which DS & RS activates • CPU initialize DMA through data bus • DMA can start data transfer between memory and peripheral device as it gets the control command 61

DMA Transfer Interrupt Random-access Memory (RAM) CPU BG BR RD WR Address Data RD Read Control WR Address Data Write Control Address bus Data Bus Address select RD DS RS BR WR Address Direct memory Access (DMA) controller BG Interrupt Data DMA Acknowledge DMA Request I/O Peripheral device 62

DMA Transfer Interrupt Random-access Memory (RAM) CPU BG BR RD WR Address Data RD Read Control WR Address Data Write Control Address bus Data Bus Address select RD DS RS BR WR Address Direct memory Access (DMA) controller BG Interrupt Data DMA Acknowledge DMA Request I/O Peripheral device 62

DMA Transfer - Sequence • Peripheral device sends DMA request • DMA controller activates BR • CPU finishes current bus cycle and grant the bus by activating BG • DMA puts current address to the address bus and activate RD or WR accordingly • And acknowledges peripheral • Then peripheral puts data to (or reads data from) the bus • Thus peripheral directly read or write memory • For each word transferred DMA increment address and decrement word count register 63

DMA Transfer - Sequence • Peripheral device sends DMA request • DMA controller activates BR • CPU finishes current bus cycle and grant the bus by activating BG • DMA puts current address to the address bus and activate RD or WR accordingly • And acknowledges peripheral • Then peripheral puts data to (or reads data from) the bus • Thus peripheral directly read or write memory • For each word transferred DMA increment address and decrement word count register 63

DMA Transfer – Sequence (Cont. ) • If word count is not zero DMA checks request line coming from peripheral – If active (fast devices) initiate the second transfer immediately – Otherwise disable BR • If word count is zero – DMA stop transfer, disable BR and inform CPU the termination of data transfer • Zero value in word count indicates successful data transfer • DMA can have even more than one channel • DMA commonly used in devices like magnetic disks and screen display 64

DMA Transfer – Sequence (Cont. ) • If word count is not zero DMA checks request line coming from peripheral – If active (fast devices) initiate the second transfer immediately – Otherwise disable BR • If word count is zero – DMA stop transfer, disable BR and inform CPU the termination of data transfer • Zero value in word count indicates successful data transfer • DMA can have even more than one channel • DMA commonly used in devices like magnetic disks and screen display 64

I/O Processor (IOP) 65

I/O Processor (IOP) 65

I/O Processing • Instead of each interface communicating with the CPU • One or more external processors assigned to communicate directly with I/O devices • IOP has both direct memory access and I/O communication capabilities • IOP releases the CPU from the housekeeping the chores involved in I/O transfer • Processors handling serial communication with remote terminal are called Data Communication Processors (DCP) • IOP is similar to CPU except its handles only I/O processing • Unlike DMA controller totally setup by the CPU, IOP can fetch and executes its own instructions • Additionally IOP can perform other tasks like arithmetic, 66 logic, branching and code translation

I/O Processing • Instead of each interface communicating with the CPU • One or more external processors assigned to communicate directly with I/O devices • IOP has both direct memory access and I/O communication capabilities • IOP releases the CPU from the housekeeping the chores involved in I/O transfer • Processors handling serial communication with remote terminal are called Data Communication Processors (DCP) • IOP is similar to CPU except its handles only I/O processing • Unlike DMA controller totally setup by the CPU, IOP can fetch and executes its own instructions • Additionally IOP can perform other tasks like arithmetic, 66 logic, branching and code translation

Computer with I/O Processor Memory unit Memory bus Central processing unit (CPU) Peripheral devices PD Input-output Processor (IOP) PD PD PD I/O bus 67

Computer with I/O Processor Memory unit Memory bus Central processing unit (CPU) Peripheral devices PD Input-output Processor (IOP) PD PD PD I/O bus 67

Responsibilities of IOP • Memory at the centre can communicate with both processors via DMA • CPU responsible for data processing and computational tasks • IOP transfers data between peripheral devices and memory • CPU is usually assigned the task of initiating the I/O program, there after IOP operates independently • IOP take care of data format difference and structure mapping between memory and various I/O devices • Communication between CPU and IOP is similar to programmed I/O • Communication between Memory and IOP is done as DMA • IOP can be independent or slave processors depending on the sophistication of the system • Instructions for IOP generally refers as commands 68

Responsibilities of IOP • Memory at the centre can communicate with both processors via DMA • CPU responsible for data processing and computational tasks • IOP transfers data between peripheral devices and memory • CPU is usually assigned the task of initiating the I/O program, there after IOP operates independently • IOP take care of data format difference and structure mapping between memory and various I/O devices • Communication between CPU and IOP is similar to programmed I/O • Communication between Memory and IOP is done as DMA • IOP can be independent or slave processors depending on the sophistication of the system • Instructions for IOP generally refers as commands 68

CPU-IOP Communication Transfer status word To memory location If status OK… send Start I/O instruction To IOP Access memory for IOP program CPU continues with Another program Conduct I/O transfers Using DMA; prepare Status report Request IOP status I/O transfer completed; Interrupt CPU Check status word For correct transfer Transfer status word To memory location IOP Operations CPU Operations Send instruction To test IOP path 69 Continue

CPU-IOP Communication Transfer status word To memory location If status OK… send Start I/O instruction To IOP Access memory for IOP program CPU continues with Another program Conduct I/O transfers Using DMA; prepare Status report Request IOP status I/O transfer completed; Interrupt CPU Check status word For correct transfer Transfer status word To memory location IOP Operations CPU Operations Send instruction To test IOP path 69 Continue

Serial Communication 70

Serial Communication 70

Data Communication Processor • DCP distribute and collect data from remote terminals • Specialized I/O processor for communicating with data communication network • Network can have any device like printers, interactive display devices, digital sensors, remote computers • Can serve many uses at a time using time-sharing • Main difference with IOP is DCP uses single pair of wires while IOP uses a common bus with control lines 71

Data Communication Processor • DCP distribute and collect data from remote terminals • Specialized I/O processor for communicating with data communication network • Network can have any device like printers, interactive display devices, digital sensors, remote computers • Can serve many uses at a time using time-sharing • Main difference with IOP is DCP uses single pair of wires while IOP uses a common bus with control lines 71

Connection Methods • Commonly connected via telephone or other public communication network • Telephone network was originally designed for voice communication and commuter uses modem for modulating and demodulating signals • Communication line may connected to synchronous or asynchronous interface depending on remote terminal • Synchronous transmission – doesn’t required start and stop bits – more efficient in transmission – uses by high speed devices (modems) • Modem uses frequency synchronization – i. e. extract clock signals from the communication line at both ends – Modems transfers and receives data with the clock signals to keep the synchronization at both ends – Transmitter and receiver clocks are adjusted continuously according incoming bit stream • Asynchronous transmission – sends each character and block separately with start and stop bits – No need of continuous messages for synchronization 72

Connection Methods • Commonly connected via telephone or other public communication network • Telephone network was originally designed for voice communication and commuter uses modem for modulating and demodulating signals • Communication line may connected to synchronous or asynchronous interface depending on remote terminal • Synchronous transmission – doesn’t required start and stop bits – more efficient in transmission – uses by high speed devices (modems) • Modem uses frequency synchronization – i. e. extract clock signals from the communication line at both ends – Modems transfers and receives data with the clock signals to keep the synchronization at both ends – Transmitter and receiver clocks are adjusted continuously according incoming bit stream • Asynchronous transmission – sends each character and block separately with start and stop bits – No need of continuous messages for synchronization 72

Error Detection • • Error detection is the one of functions in DCP Using parity bits – checks at each character echo character – prints to the terminal LRC – Longitudinal Redundancy Check – LRC is one more characters with the party over the entire block – sends following each block • CRC – Cyclic Redundancy Check – A polynomial code – Obtained by passing through a feedback register – Suitable for detecting burst errors 73

Error Detection • • Error detection is the one of functions in DCP Using parity bits – checks at each character echo character – prints to the terminal LRC – Longitudinal Redundancy Check – LRC is one more characters with the party over the entire block – sends following each block • CRC – Cyclic Redundancy Check – A polynomial code – Obtained by passing through a feedback register – Suitable for detecting burst errors 73

Transmission Modes • Simplex – Line carry information in one direction only – Receiver can not feedback or acknowledge – Rarely used in data communication • Half-duplex – – – Used a single pair of wires Transmit data only one direction at a time In modems one act as the transmitter and other the receiver When transmission completed reverse the role Switching time is called turnaround time • Full-duplex – 2 pair of wires – Even single pair can do full duplex transmission using frequency spectrum 74

Transmission Modes • Simplex – Line carry information in one direction only – Receiver can not feedback or acknowledge – Rarely used in data communication • Half-duplex – – – Used a single pair of wires Transmit data only one direction at a time In modems one act as the transmitter and other the receiver When transmission completed reverse the role Switching time is called turnaround time • Full-duplex – 2 pair of wires – Even single pair can do full duplex transmission using frequency spectrum 74

Protocols • Data links – communication lines, modems and other equipments used between two or more stations • Protocol – set of rules followed by interconnected computers and terminals – – – Establish connection Identify sender and receiver Ensure error free transmission Handle all control functions Categorized according to the framing techniques • Character oriented – based on binary code of characters • Bit oriented – do not use characters in control fields 75

Protocols • Data links – communication lines, modems and other equipments used between two or more stations • Protocol – set of rules followed by interconnected computers and terminals – – – Establish connection Identify sender and receiver Ensure error free transmission Handle all control functions Categorized according to the framing techniques • Character oriented – based on binary code of characters • Bit oriented – do not use characters in control fields 75

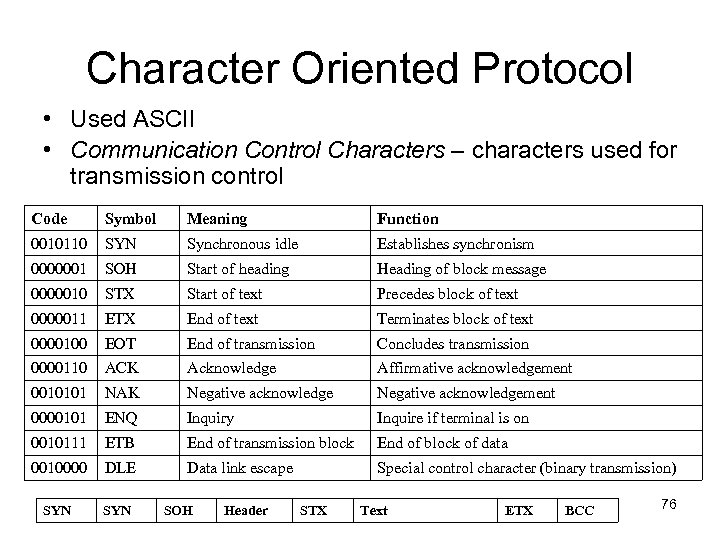

Character Oriented Protocol • Used ASCII • Communication Control Characters – characters used for transmission control Code Symbol Meaning Function 0010110 SYN Synchronous idle Establishes synchronism 0000001 SOH Start of heading Heading of block message 0000010 STX Start of text Precedes block of text 0000011 ETX End of text Terminates block of text 0000100 EOT End of transmission Concludes transmission 0000110 ACK Acknowledge Affirmative acknowledgement 0010101 NAK Negative acknowledgement 0000101 ENQ Inquiry Inquire if terminal is on 0010111 ETB End of transmission block End of block of data 0010000 DLE Data link escape Special control character (binary transmission) SYN SOH Header STX Text ETX BCC 76

Character Oriented Protocol • Used ASCII • Communication Control Characters – characters used for transmission control Code Symbol Meaning Function 0010110 SYN Synchronous idle Establishes synchronism 0000001 SOH Start of heading Heading of block message 0000010 STX Start of text Precedes block of text 0000011 ETX End of text Terminates block of text 0000100 EOT End of transmission Concludes transmission 0000110 ACK Acknowledge Affirmative acknowledgement 0010101 NAK Negative acknowledgement 0000101 ENQ Inquiry Inquire if terminal is on 0010111 ETB End of transmission block End of block of data 0010000 DLE Data link escape Special control character (binary transmission) SYN SOH Header STX Text ETX BCC 76

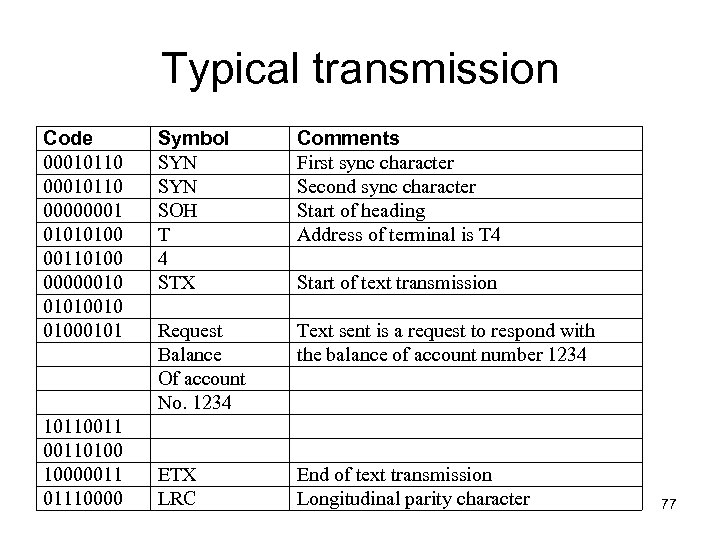

Typical transmission Code 00010110 00000001 01010100 00110100 00000010 01010010 01000101 101100110100 10000011 01110000 Symbol SYN SOH T 4 STX Comments First sync character Second sync character Start of heading Address of terminal is T 4 Request Balance Of account No. 1234 Text sent is a request to respond with the balance of account number 1234 ETX LRC End of text transmission Longitudinal parity character Start of text transmission 77

Typical transmission Code 00010110 00000001 01010100 00110100 00000010 01010010 01000101 101100110100 10000011 01110000 Symbol SYN SOH T 4 STX Comments First sync character Second sync character Start of heading Address of terminal is T 4 Request Balance Of account No. 1234 Text sent is a request to respond with the balance of account number 1234 ETX LRC End of text transmission Longitudinal parity character Start of text transmission 77

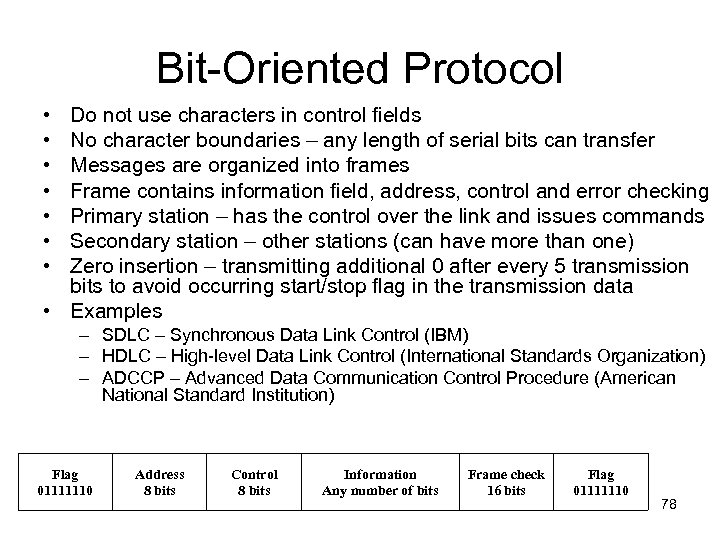

Bit-Oriented Protocol • • Do not use characters in control fields No character boundaries – any length of serial bits can transfer Messages are organized into frames Frame contains information field, address, control and error checking Primary station – has the control over the link and issues commands Secondary station – other stations (can have more than one) Zero insertion – transmitting additional 0 after every 5 transmission bits to avoid occurring start/stop flag in the transmission data • Examples – SDLC – Synchronous Data Link Control (IBM) – HDLC – High-level Data Link Control (International Standards Organization) – ADCCP – Advanced Data Communication Control Procedure (American National Standard Institution) Flag 01111110 Address 8 bits Control 8 bits Information Any number of bits Frame check 16 bits Flag 01111110 78

Bit-Oriented Protocol • • Do not use characters in control fields No character boundaries – any length of serial bits can transfer Messages are organized into frames Frame contains information field, address, control and error checking Primary station – has the control over the link and issues commands Secondary station – other stations (can have more than one) Zero insertion – transmitting additional 0 after every 5 transmission bits to avoid occurring start/stop flag in the transmission data • Examples – SDLC – Synchronous Data Link Control (IBM) – HDLC – High-level Data Link Control (International Standards Organization) – ADCCP – Advanced Data Communication Control Procedure (American National Standard Institution) Flag 01111110 Address 8 bits Control 8 bits Information Any number of bits Frame check 16 bits Flag 01111110 78

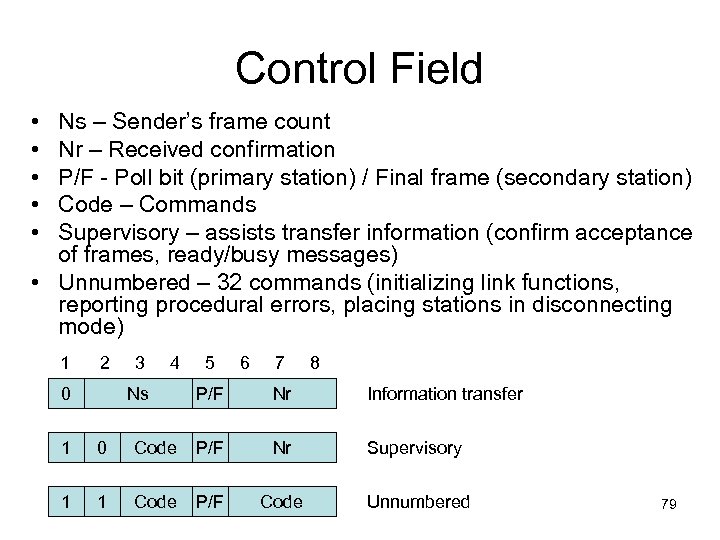

Control Field • • • Ns – Sender’s frame count Nr – Received confirmation P/F - Poll bit (primary station) / Final frame (secondary station) Code – Commands Supervisory – assists transfer information (confirm acceptance of frames, ready/busy messages) • Unnumbered – 32 commands (initializing link functions, reporting procedural errors, placing stations in disconnecting mode) 1 2 0 3 4 Ns 5 6 7 8 P/F Nr Information transfer 1 0 Code P/F Nr Supervisory 1 1 Code P/F Code Unnumbered 79

Control Field • • • Ns – Sender’s frame count Nr – Received confirmation P/F - Poll bit (primary station) / Final frame (secondary station) Code – Commands Supervisory – assists transfer information (confirm acceptance of frames, ready/busy messages) • Unnumbered – 32 commands (initializing link functions, reporting procedural errors, placing stations in disconnecting mode) 1 2 0 3 4 Ns 5 6 7 8 P/F Nr Information transfer 1 0 Code P/F Nr Supervisory 1 1 Code P/F Code Unnumbered 79

Thank you! Q/A 80

Thank you! Q/A 80