530b35d76bff7f1bb0771d95583d2b52.ppt

- Количество слайдов: 25

Input-Output Organization 1 INPUT-OUTPUT ORGANIZATION • Peripheral Devices • Input-Output Interface • Asynchronous Data Transfer • Modes of Transfer • Priority Interrupt • Direct Memory Access • Input-Output Processor • Serial Communication Computer Organization Computer Architectures Lab

Input-Output Organization 1 INPUT-OUTPUT ORGANIZATION • Peripheral Devices • Input-Output Interface • Asynchronous Data Transfer • Modes of Transfer • Priority Interrupt • Direct Memory Access • Input-Output Processor • Serial Communication Computer Organization Computer Architectures Lab

Input-Output Organization 2 Peripheral Devices PERIPHERAL DEVICES Input Devices Output Devices • Keyboard • Optical input devices - Card Reader - Paper Tape Reader - Bar code reader - Digitizer - Optical Mark Reader • Magnetic Input Devices - Magnetic Stripe Reader • Screen Input Devices - Touch Screen - Light Pen - Mouse • Analog Input Devices • Card Puncher, Paper Tape Puncher • CRT • Printer (Impact, Ink Jet, Laser, Dot Matrix) • Plotter • Analog • Voice Computer Organization Computer Architectures Lab

Input-Output Organization 2 Peripheral Devices PERIPHERAL DEVICES Input Devices Output Devices • Keyboard • Optical input devices - Card Reader - Paper Tape Reader - Bar code reader - Digitizer - Optical Mark Reader • Magnetic Input Devices - Magnetic Stripe Reader • Screen Input Devices - Touch Screen - Light Pen - Mouse • Analog Input Devices • Card Puncher, Paper Tape Puncher • CRT • Printer (Impact, Ink Jet, Laser, Dot Matrix) • Plotter • Analog • Voice Computer Organization Computer Architectures Lab

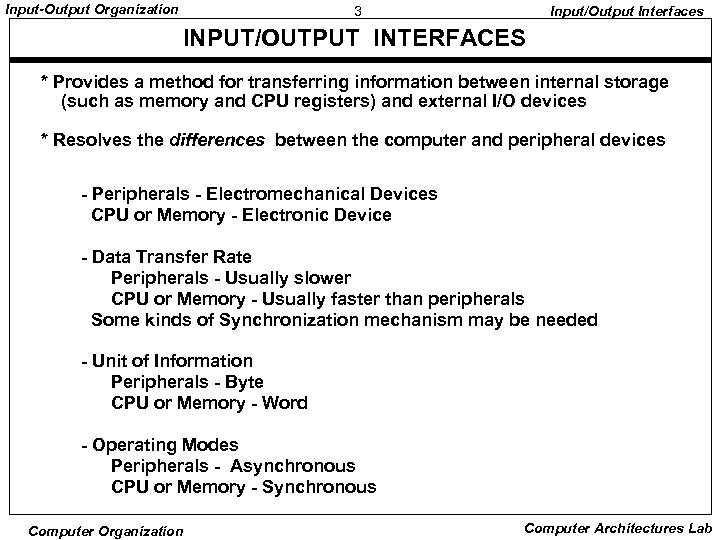

Input-Output Organization 3 Input/Output Interfaces INPUT/OUTPUT INTERFACES * Provides a method for transferring information between internal storage (such as memory and CPU registers) and external I/O devices * Resolves the differences between the computer and peripheral devices - Peripherals - Electromechanical Devices CPU or Memory - Electronic Device - Data Transfer Rate Peripherals - Usually slower CPU or Memory - Usually faster than peripherals Some kinds of Synchronization mechanism may be needed - Unit of Information Peripherals - Byte CPU or Memory - Word - Operating Modes Peripherals - Asynchronous CPU or Memory - Synchronous Computer Organization Computer Architectures Lab

Input-Output Organization 3 Input/Output Interfaces INPUT/OUTPUT INTERFACES * Provides a method for transferring information between internal storage (such as memory and CPU registers) and external I/O devices * Resolves the differences between the computer and peripheral devices - Peripherals - Electromechanical Devices CPU or Memory - Electronic Device - Data Transfer Rate Peripherals - Usually slower CPU or Memory - Usually faster than peripherals Some kinds of Synchronization mechanism may be needed - Unit of Information Peripherals - Byte CPU or Memory - Word - Operating Modes Peripherals - Asynchronous CPU or Memory - Synchronous Computer Organization Computer Architectures Lab

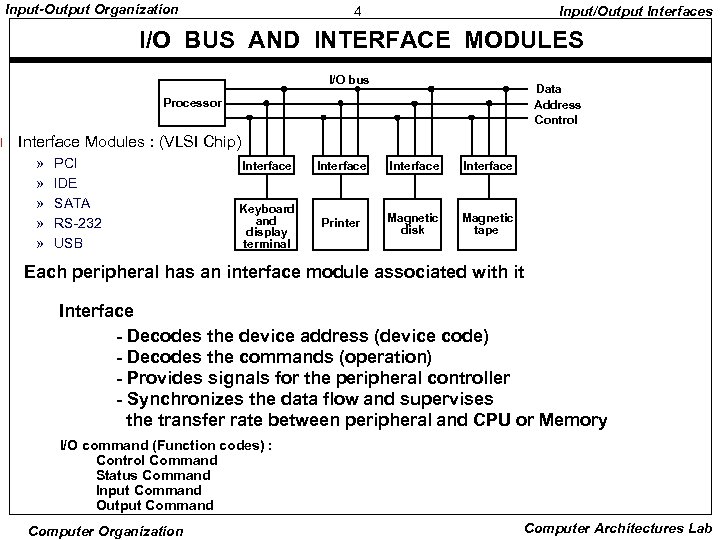

Input-Output Organization 4 Input/Output Interfaces I/O BUS AND INTERFACE MODULES I/O bus Data Address Control Processor l Interface Modules : (VLSI Chip) » » » PCI IDE SATA RS-232 USB Interface Keyboard and display terminal Printer Magnetic disk Magnetic tape Each peripheral has an interface module associated with it Interface - Decodes the device address (device code) - Decodes the commands (operation) - Provides signals for the peripheral controller - Synchronizes the data flow and supervises the transfer rate between peripheral and CPU or Memory I/O command (Function codes) : Control Command Status Command Input Command Output Command Computer Organization Computer Architectures Lab

Input-Output Organization 4 Input/Output Interfaces I/O BUS AND INTERFACE MODULES I/O bus Data Address Control Processor l Interface Modules : (VLSI Chip) » » » PCI IDE SATA RS-232 USB Interface Keyboard and display terminal Printer Magnetic disk Magnetic tape Each peripheral has an interface module associated with it Interface - Decodes the device address (device code) - Decodes the commands (operation) - Provides signals for the peripheral controller - Synchronizes the data flow and supervises the transfer rate between peripheral and CPU or Memory I/O command (Function codes) : Control Command Status Command Input Command Output Command Computer Organization Computer Architectures Lab

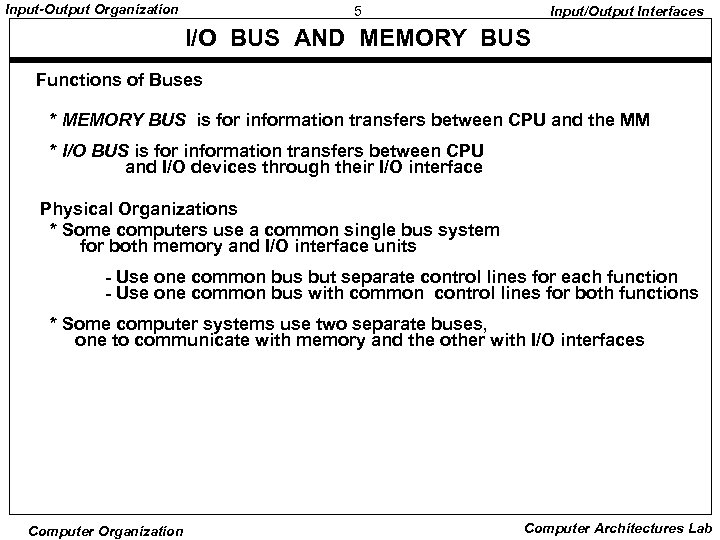

Input-Output Organization 5 Input/Output Interfaces I/O BUS AND MEMORY BUS Functions of Buses * MEMORY BUS is for information transfers between CPU and the MM * I/O BUS is for information transfers between CPU and I/O devices through their I/O interface Physical Organizations * Some computers use a common single bus system for both memory and I/O interface units - Use one common bus but separate control lines for each function - Use one common bus with common control lines for both functions * Some computer systems use two separate buses, one to communicate with memory and the other with I/O interfaces Computer Organization Computer Architectures Lab

Input-Output Organization 5 Input/Output Interfaces I/O BUS AND MEMORY BUS Functions of Buses * MEMORY BUS is for information transfers between CPU and the MM * I/O BUS is for information transfers between CPU and I/O devices through their I/O interface Physical Organizations * Some computers use a common single bus system for both memory and I/O interface units - Use one common bus but separate control lines for each function - Use one common bus with common control lines for both functions * Some computer systems use two separate buses, one to communicate with memory and the other with I/O interfaces Computer Organization Computer Architectures Lab

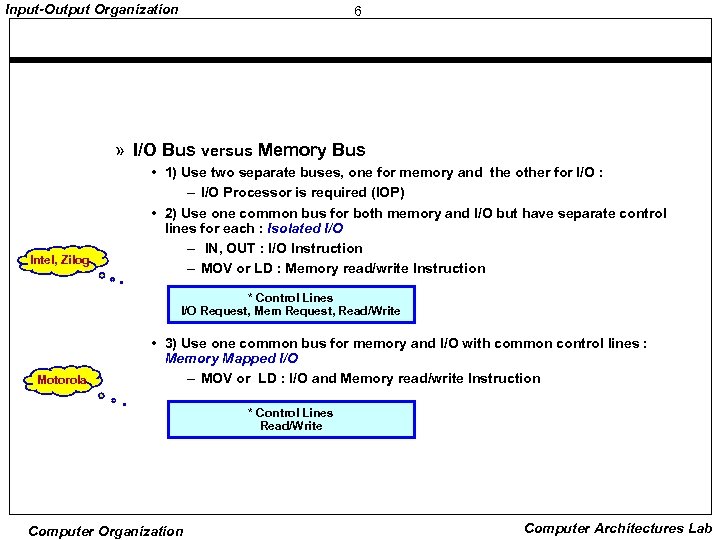

Input-Output Organization 6 » I/O Bus versus Memory Bus Intel, Zilog • 1) Use two separate buses, one for memory and the other for I/O : – I/O Processor is required (IOP) • 2) Use one common bus for both memory and I/O but have separate control lines for each : Isolated I/O – IN, OUT : I/O Instruction – MOV or LD : Memory read/write Instruction * Control Lines I/O Request, Mem Request, Read/Write Motorola • 3) Use one common bus for memory and I/O with common control lines : Memory Mapped I/O – MOV or LD : I/O and Memory read/write Instruction * Control Lines Read/Write Computer Organization Computer Architectures Lab

Input-Output Organization 6 » I/O Bus versus Memory Bus Intel, Zilog • 1) Use two separate buses, one for memory and the other for I/O : – I/O Processor is required (IOP) • 2) Use one common bus for both memory and I/O but have separate control lines for each : Isolated I/O – IN, OUT : I/O Instruction – MOV or LD : Memory read/write Instruction * Control Lines I/O Request, Mem Request, Read/Write Motorola • 3) Use one common bus for memory and I/O with common control lines : Memory Mapped I/O – MOV or LD : I/O and Memory read/write Instruction * Control Lines Read/Write Computer Organization Computer Architectures Lab

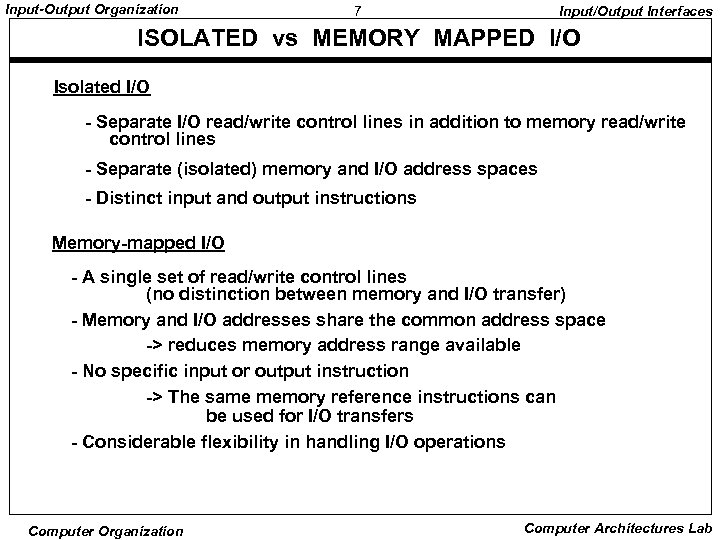

Input-Output Organization 7 Input/Output Interfaces ISOLATED vs MEMORY MAPPED I/O Isolated I/O - Separate I/O read/write control lines in addition to memory read/write control lines - Separate (isolated) memory and I/O address spaces - Distinct input and output instructions Memory-mapped I/O - A single set of read/write control lines (no distinction between memory and I/O transfer) - Memory and I/O addresses share the common address space -> reduces memory address range available - No specific input or output instruction -> The same memory reference instructions can be used for I/O transfers - Considerable flexibility in handling I/O operations Computer Organization Computer Architectures Lab

Input-Output Organization 7 Input/Output Interfaces ISOLATED vs MEMORY MAPPED I/O Isolated I/O - Separate I/O read/write control lines in addition to memory read/write control lines - Separate (isolated) memory and I/O address spaces - Distinct input and output instructions Memory-mapped I/O - A single set of read/write control lines (no distinction between memory and I/O transfer) - Memory and I/O addresses share the common address space -> reduces memory address range available - No specific input or output instruction -> The same memory reference instructions can be used for I/O transfers - Considerable flexibility in handling I/O operations Computer Organization Computer Architectures Lab

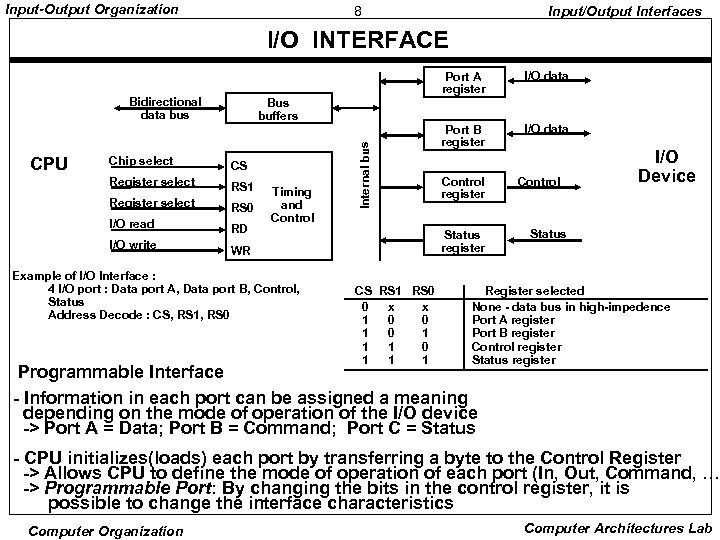

Input-Output Organization 8 Input/Output Interfaces I/O INTERFACE Port A register Bidirectional data bus Port B register I/O data Bus buffers Chip select CS Register select RS 1 Register select RS 0 I/O read RD I/O write Internal bus CPU I/O data WR Timing and Control Example of I/O Interface : 4 I/O port : Data port A, Data port B, Control, Status Address Decode : CS, RS 1, RS 0 Control register Status register CS RS 1 RS 0 0 x x 1 0 0 1 1 1 Control I/O Device Status Register selected None - data bus in high-impedence Port A register Port B register Control register Status register Programmable Interface - Information in each port can be assigned a meaning depending on the mode of operation of the I/O device -> Port A = Data; Port B = Command; Port C = Status - CPU initializes(loads) each port by transferring a byte to the Control Register -> Allows CPU to define the mode of operation of each port (In, Out, Command, … -> Programmable Port: By changing the bits in the control register, it is possible to change the interface characteristics Computer Organization Computer Architectures Lab

Input-Output Organization 8 Input/Output Interfaces I/O INTERFACE Port A register Bidirectional data bus Port B register I/O data Bus buffers Chip select CS Register select RS 1 Register select RS 0 I/O read RD I/O write Internal bus CPU I/O data WR Timing and Control Example of I/O Interface : 4 I/O port : Data port A, Data port B, Control, Status Address Decode : CS, RS 1, RS 0 Control register Status register CS RS 1 RS 0 0 x x 1 0 0 1 1 1 Control I/O Device Status Register selected None - data bus in high-impedence Port A register Port B register Control register Status register Programmable Interface - Information in each port can be assigned a meaning depending on the mode of operation of the I/O device -> Port A = Data; Port B = Command; Port C = Status - CPU initializes(loads) each port by transferring a byte to the Control Register -> Allows CPU to define the mode of operation of each port (In, Out, Command, … -> Programmable Port: By changing the bits in the control register, it is possible to change the interface characteristics Computer Organization Computer Architectures Lab

Input-Output Organization 9 Asynchronous Data Transfer ASYNCHRONOUS DATA TRANSFER Synchronous and Asynchronous Operations Synchronous - All devices derive the timing information from common clock line Asynchronous - No common clock Asynchronous Data Transfer Asynchronous data transfer between two independent units requires that control signals be transmitted between the communicating units to indicate the time at which data is being transmitted Two Asynchronous Data Transfer Methods Strobe pulse - A strobe pulse is supplied by one unit to indicate the other unit when the transfer has to occur Handshaking - A control signal is accompanied with each data being transmitted to indicate the presence of data - The receiving unit responds with another control signal to acknowledge receipt of the data Computer Organization Computer Architectures Lab

Input-Output Organization 9 Asynchronous Data Transfer ASYNCHRONOUS DATA TRANSFER Synchronous and Asynchronous Operations Synchronous - All devices derive the timing information from common clock line Asynchronous - No common clock Asynchronous Data Transfer Asynchronous data transfer between two independent units requires that control signals be transmitted between the communicating units to indicate the time at which data is being transmitted Two Asynchronous Data Transfer Methods Strobe pulse - A strobe pulse is supplied by one unit to indicate the other unit when the transfer has to occur Handshaking - A control signal is accompanied with each data being transmitted to indicate the presence of data - The receiving unit responds with another control signal to acknowledge receipt of the data Computer Organization Computer Architectures Lab

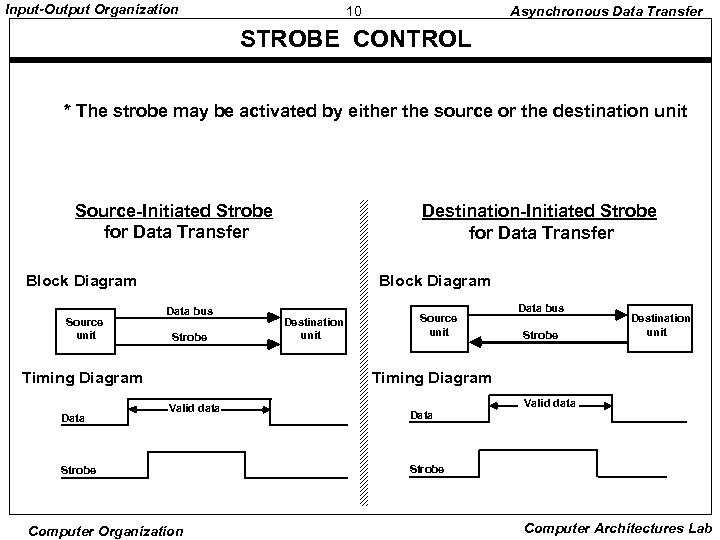

Input-Output Organization 10 Asynchronous Data Transfer STROBE CONTROL * The strobe may be activated by either the source or the destination unit Source-Initiated Strobe for Data Transfer Destination-Initiated Strobe for Data Transfer Block Diagram Source unit Block Diagram Data bus Strobe Timing Diagram Data Destination unit Source unit Data bus Strobe Destination unit Timing Diagram Valid data Strobe Computer Organization Data Valid data Strobe Computer Architectures Lab

Input-Output Organization 10 Asynchronous Data Transfer STROBE CONTROL * The strobe may be activated by either the source or the destination unit Source-Initiated Strobe for Data Transfer Destination-Initiated Strobe for Data Transfer Block Diagram Source unit Block Diagram Data bus Strobe Timing Diagram Data Destination unit Source unit Data bus Strobe Destination unit Timing Diagram Valid data Strobe Computer Organization Data Valid data Strobe Computer Architectures Lab

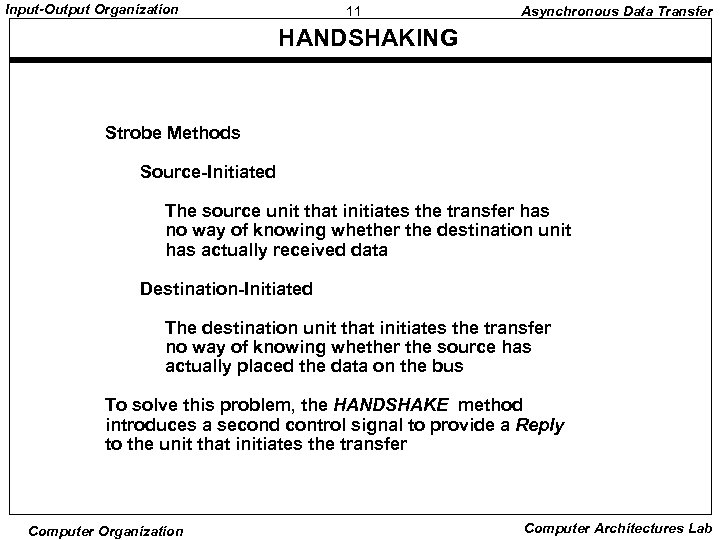

Input-Output Organization 11 Asynchronous Data Transfer HANDSHAKING Strobe Methods Source-Initiated The source unit that initiates the transfer has no way of knowing whether the destination unit has actually received data Destination-Initiated The destination unit that initiates the transfer no way of knowing whether the source has actually placed the data on the bus To solve this problem, the HANDSHAKE method introduces a second control signal to provide a Reply to the unit that initiates the transfer Computer Organization Computer Architectures Lab

Input-Output Organization 11 Asynchronous Data Transfer HANDSHAKING Strobe Methods Source-Initiated The source unit that initiates the transfer has no way of knowing whether the destination unit has actually received data Destination-Initiated The destination unit that initiates the transfer no way of knowing whether the source has actually placed the data on the bus To solve this problem, the HANDSHAKE method introduces a second control signal to provide a Reply to the unit that initiates the transfer Computer Organization Computer Architectures Lab

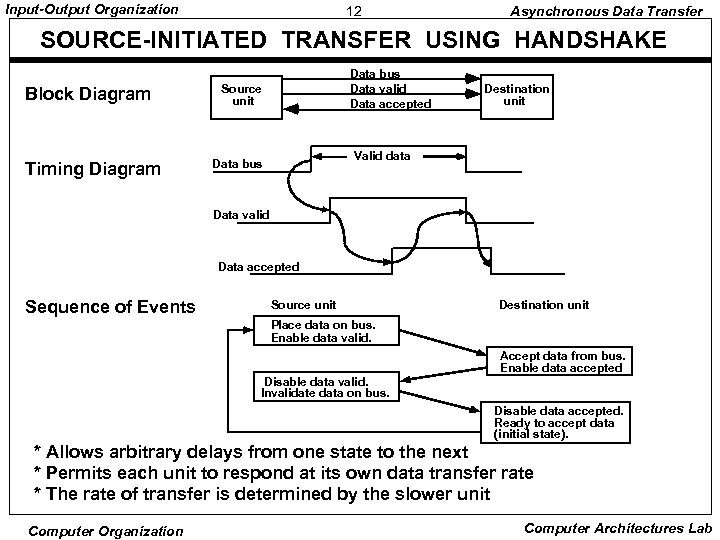

Input-Output Organization 12 Asynchronous Data Transfer SOURCE-INITIATED TRANSFER USING HANDSHAKE Block Diagram Timing Diagram Data bus Data valid Data accepted Source unit Destination unit Valid data Data bus Data valid Data accepted Sequence of Events Source unit Destination unit Place data on bus. Enable data valid. Accept data from bus. Enable data accepted Disable data valid. Invalidate data on bus. Disable data accepted. Ready to accept data (initial state). * Allows arbitrary delays from one state to the next * Permits each unit to respond at its own data transfer rate * The rate of transfer is determined by the slower unit Computer Organization Computer Architectures Lab

Input-Output Organization 12 Asynchronous Data Transfer SOURCE-INITIATED TRANSFER USING HANDSHAKE Block Diagram Timing Diagram Data bus Data valid Data accepted Source unit Destination unit Valid data Data bus Data valid Data accepted Sequence of Events Source unit Destination unit Place data on bus. Enable data valid. Accept data from bus. Enable data accepted Disable data valid. Invalidate data on bus. Disable data accepted. Ready to accept data (initial state). * Allows arbitrary delays from one state to the next * Permits each unit to respond at its own data transfer rate * The rate of transfer is determined by the slower unit Computer Organization Computer Architectures Lab

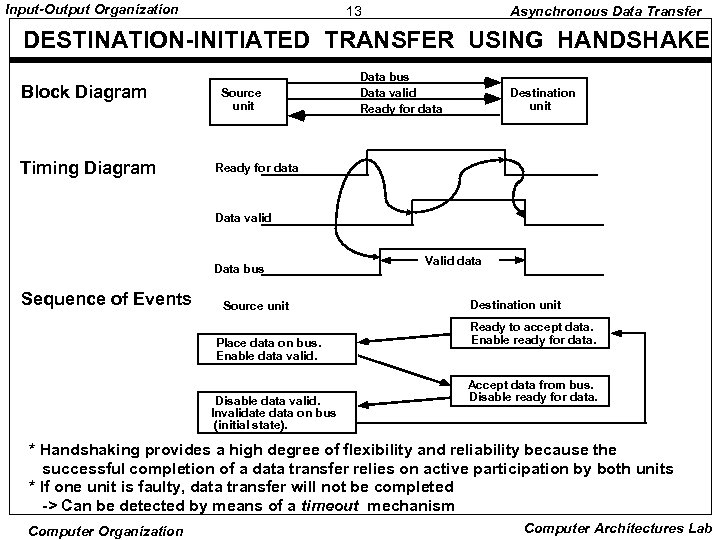

Input-Output Organization 13 Asynchronous Data Transfer DESTINATION-INITIATED TRANSFER USING HANDSHAKE Block Diagram Timing Diagram Source unit Data bus Data valid Ready for data Destination unit Ready for data Data valid Data bus Sequence of Events Source unit Place data on bus. Enable data valid. Disable data valid. Invalidate data on bus (initial state). Valid data Destination unit Ready to accept data. Enable ready for data. Accept data from bus. Disable ready for data. * Handshaking provides a high degree of flexibility and reliability because the successful completion of a data transfer relies on active participation by both units * If one unit is faulty, data transfer will not be completed -> Can be detected by means of a timeout mechanism Computer Organization Computer Architectures Lab

Input-Output Organization 13 Asynchronous Data Transfer DESTINATION-INITIATED TRANSFER USING HANDSHAKE Block Diagram Timing Diagram Source unit Data bus Data valid Ready for data Destination unit Ready for data Data valid Data bus Sequence of Events Source unit Place data on bus. Enable data valid. Disable data valid. Invalidate data on bus (initial state). Valid data Destination unit Ready to accept data. Enable ready for data. Accept data from bus. Disable ready for data. * Handshaking provides a high degree of flexibility and reliability because the successful completion of a data transfer relies on active participation by both units * If one unit is faulty, data transfer will not be completed -> Can be detected by means of a timeout mechanism Computer Organization Computer Architectures Lab

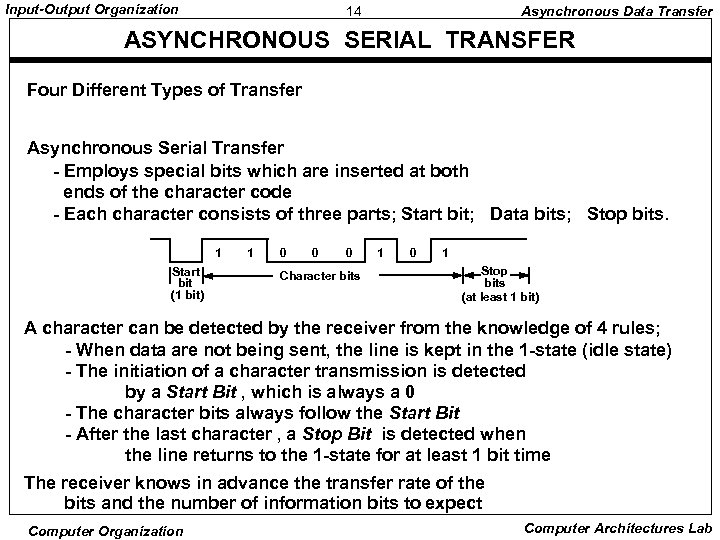

Input-Output Organization 14 Asynchronous Data Transfer ASYNCHRONOUS SERIAL TRANSFER Four Different Types of Transfer Asynchronous Serial Transfer - Employs special bits which are inserted at both ends of the character code - Each character consists of three parts; Start bit; Data bits; Stop bits. 1 Start bit (1 bit) 1 0 0 0 Character bits 1 0 1 Stop bits (at least 1 bit) A character can be detected by the receiver from the knowledge of 4 rules; - When data are not being sent, the line is kept in the 1 -state (idle state) - The initiation of a character transmission is detected by a Start Bit , which is always a 0 - The character bits always follow the Start Bit - After the last character , a Stop Bit is detected when the line returns to the 1 -state for at least 1 bit time The receiver knows in advance the transfer rate of the bits and the number of information bits to expect Computer Organization Computer Architectures Lab

Input-Output Organization 14 Asynchronous Data Transfer ASYNCHRONOUS SERIAL TRANSFER Four Different Types of Transfer Asynchronous Serial Transfer - Employs special bits which are inserted at both ends of the character code - Each character consists of three parts; Start bit; Data bits; Stop bits. 1 Start bit (1 bit) 1 0 0 0 Character bits 1 0 1 Stop bits (at least 1 bit) A character can be detected by the receiver from the knowledge of 4 rules; - When data are not being sent, the line is kept in the 1 -state (idle state) - The initiation of a character transmission is detected by a Start Bit , which is always a 0 - The character bits always follow the Start Bit - After the last character , a Stop Bit is detected when the line returns to the 1 -state for at least 1 bit time The receiver knows in advance the transfer rate of the bits and the number of information bits to expect Computer Organization Computer Architectures Lab

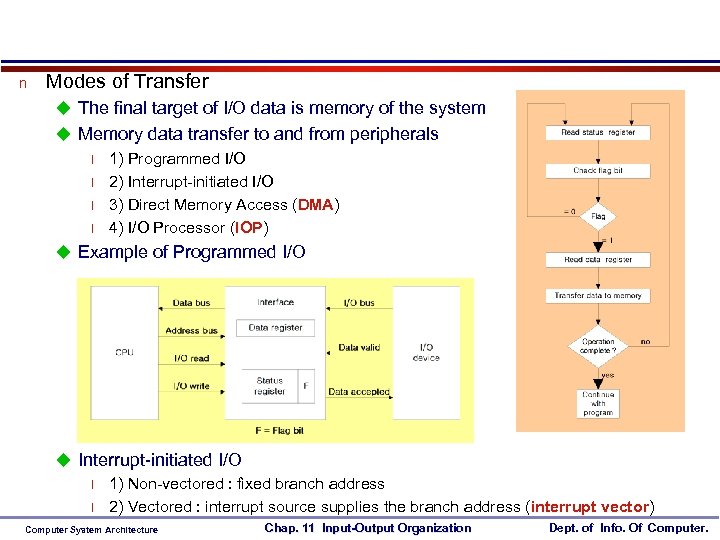

n Modes of Transfer u The final target of I/O data is memory of the system u Memory data transfer to and from peripherals l 1) Programmed I/O l 2) Interrupt-initiated I/O l 3) Direct Memory Access (DMA) l 4) I/O Processor (IOP) u Example of Programmed I/O u Interrupt-initiated I/O l 1) Non-vectored : fixed branch address l 2) Vectored : interrupt source supplies the branch address (interrupt vector) Computer System Architecture Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

n Modes of Transfer u The final target of I/O data is memory of the system u Memory data transfer to and from peripherals l 1) Programmed I/O l 2) Interrupt-initiated I/O l 3) Direct Memory Access (DMA) l 4) I/O Processor (IOP) u Example of Programmed I/O u Interrupt-initiated I/O l 1) Non-vectored : fixed branch address l 2) Vectored : interrupt source supplies the branch address (interrupt vector) Computer System Architecture Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

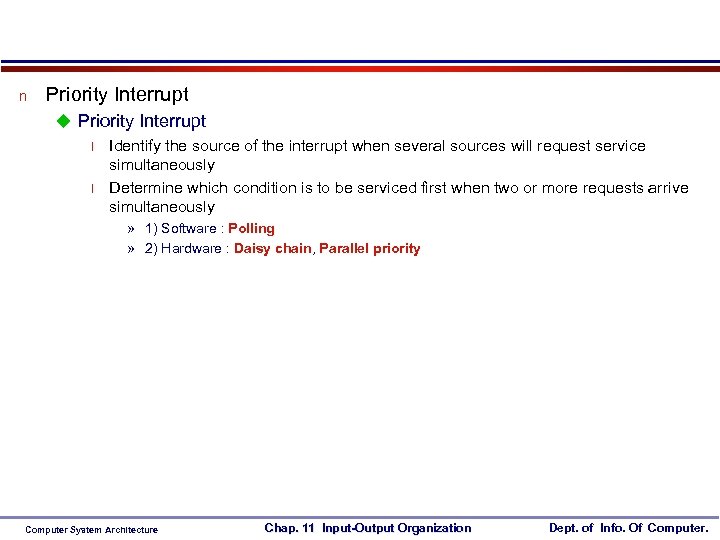

n Priority Interrupt u Priority Interrupt l Identify the source of the interrupt when several sources will request service simultaneously l Determine which condition is to be serviced first when two or more requests arrive simultaneously » 1) Software : Polling » 2) Hardware : Daisy chain, Parallel priority Computer System Architecture Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

n Priority Interrupt u Priority Interrupt l Identify the source of the interrupt when several sources will request service simultaneously l Determine which condition is to be serviced first when two or more requests arrive simultaneously » 1) Software : Polling » 2) Hardware : Daisy chain, Parallel priority Computer System Architecture Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

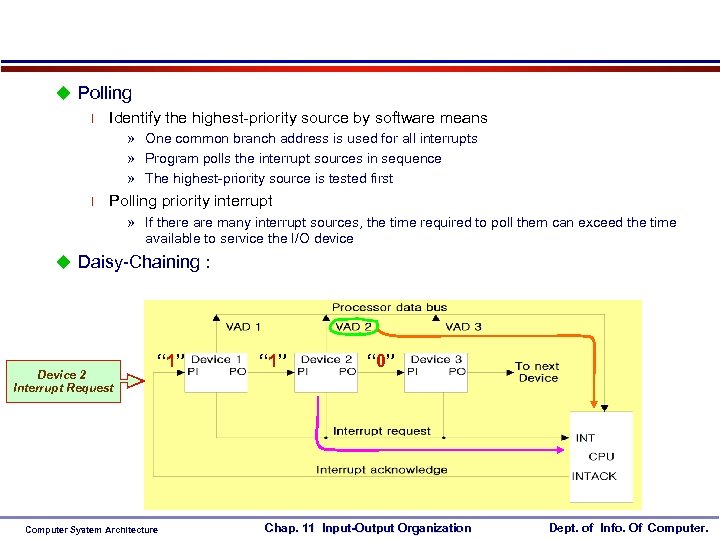

u Polling l Identify the highest-priority source by software means » One common branch address is used for all interrupts » Program polls the interrupt sources in sequence » The highest-priority source is tested first l Polling priority interrupt » If there are many interrupt sources, the time required to poll them can exceed the time available to service the I/O device u Daisy-Chaining : Device 2 Interrupt Request “ 1” Computer System Architecture “ 1” “ 0” Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

u Polling l Identify the highest-priority source by software means » One common branch address is used for all interrupts » Program polls the interrupt sources in sequence » The highest-priority source is tested first l Polling priority interrupt » If there are many interrupt sources, the time required to poll them can exceed the time available to service the I/O device u Daisy-Chaining : Device 2 Interrupt Request “ 1” Computer System Architecture “ 1” “ 0” Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

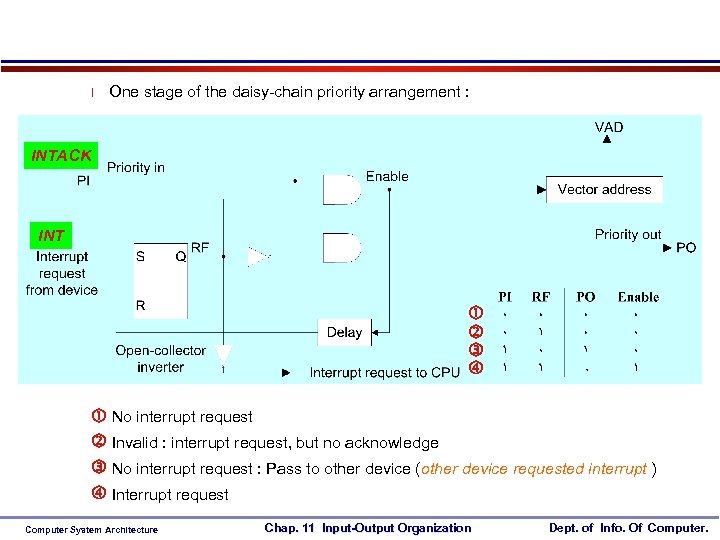

l One stage of the daisy-chain priority arrangement : INTACK INT No interrupt request Invalid : interrupt request, but no acknowledge No interrupt request : Pass to other device (other device requested interrupt ) Interrupt request Computer System Architecture Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

l One stage of the daisy-chain priority arrangement : INTACK INT No interrupt request Invalid : interrupt request, but no acknowledge No interrupt request : Pass to other device (other device requested interrupt ) Interrupt request Computer System Architecture Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

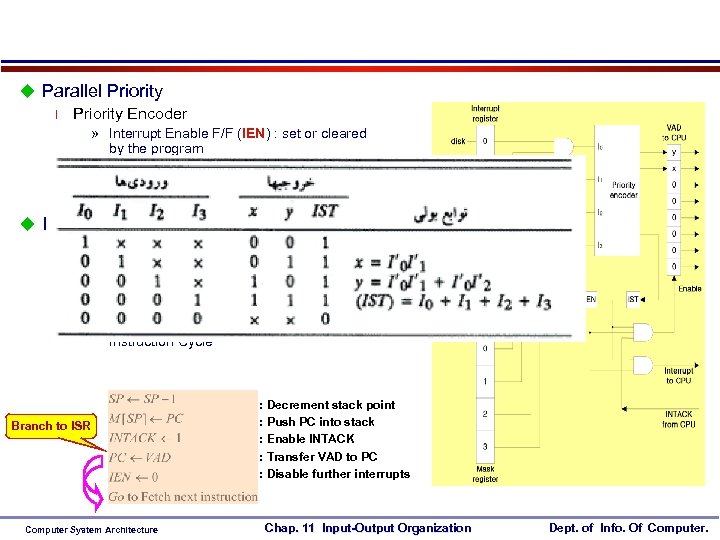

u Parallel Priority Encoder » Interrupt Enable F/F (IEN) : set or cleared by the program » Interrupt Status F/F (IST) : set or cleared by the encoder output l Priority Encoder Truth Table u Interrupt Cycle l At the end of each instruction cycle, CPU checks IEN and IST l if both IEN and IST equal to “ 1” l CPU goes to an Instruction Cycle » Sequence of microoperation during Instruction Cycle Branch to ISR Computer System Architecture : Decrement stack point : Push PC into stack : Enable INTACK : Transfer VAD to PC : Disable further interrupts Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

u Parallel Priority Encoder » Interrupt Enable F/F (IEN) : set or cleared by the program » Interrupt Status F/F (IST) : set or cleared by the encoder output l Priority Encoder Truth Table u Interrupt Cycle l At the end of each instruction cycle, CPU checks IEN and IST l if both IEN and IST equal to “ 1” l CPU goes to an Instruction Cycle » Sequence of microoperation during Instruction Cycle Branch to ISR Computer System Architecture : Decrement stack point : Push PC into stack : Enable INTACK : Transfer VAD to PC : Disable further interrupts Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

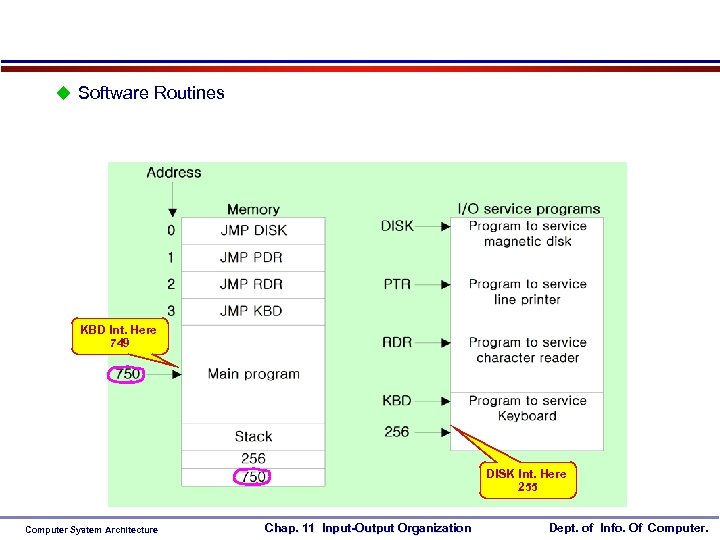

u Software Routines KBD Int. Here 749 DISK Int. Here 255 Computer System Architecture Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

u Software Routines KBD Int. Here 749 DISK Int. Here 255 Computer System Architecture Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

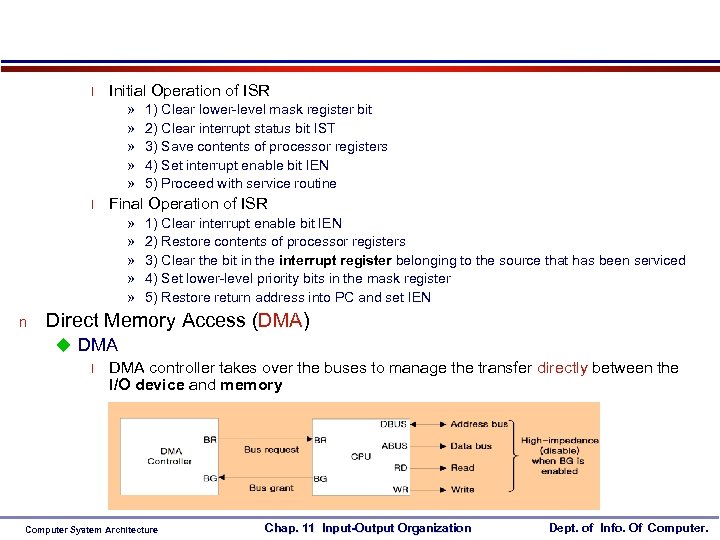

l Initial Operation of ISR » » » l Final Operation of ISR » » » n 1) Clear lower-level mask register bit 2) Clear interrupt status bit IST 3) Save contents of processor registers 4) Set interrupt enable bit IEN 5) Proceed with service routine 1) Clear interrupt enable bit IEN 2) Restore contents of processor registers 3) Clear the bit in the interrupt register belonging to the source that has been serviced 4) Set lower-level priority bits in the mask register 5) Restore return address into PC and set IEN Direct Memory Access (DMA) u DMA l DMA controller takes over the buses to manage the transfer directly between the I/O device and memory Computer System Architecture Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

l Initial Operation of ISR » » » l Final Operation of ISR » » » n 1) Clear lower-level mask register bit 2) Clear interrupt status bit IST 3) Save contents of processor registers 4) Set interrupt enable bit IEN 5) Proceed with service routine 1) Clear interrupt enable bit IEN 2) Restore contents of processor registers 3) Clear the bit in the interrupt register belonging to the source that has been serviced 4) Set lower-level priority bits in the mask register 5) Restore return address into PC and set IEN Direct Memory Access (DMA) u DMA l DMA controller takes over the buses to manage the transfer directly between the I/O device and memory Computer System Architecture Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

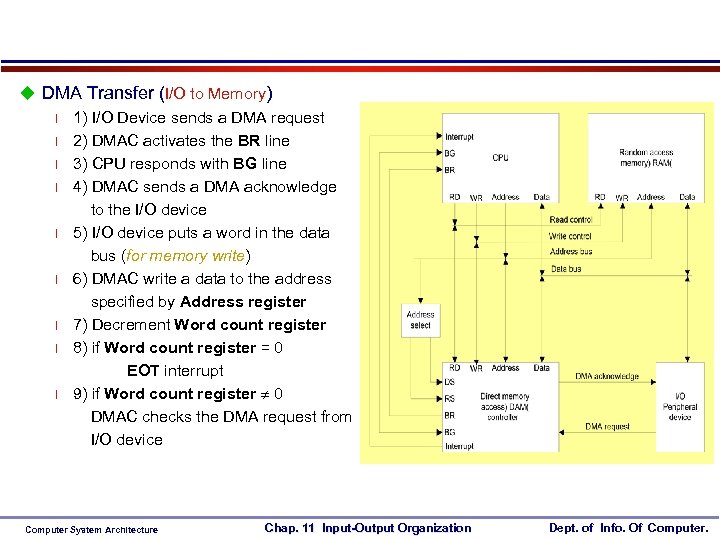

u DMA Transfer (I/O to Memory) l 1) I/O Device sends a DMA request l 2) DMAC activates the BR line l 3) CPU responds with BG line l 4) DMAC sends a DMA acknowledge to the I/O device l 5) I/O device puts a word in the data bus (for memory write) l 6) DMAC write a data to the address specified by Address register l 7) Decrement Word count register l 8) if Word count register = 0 EOT interrupt l 9) if Word count register 0 DMAC checks the DMA request from I/O device Computer System Architecture Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

u DMA Transfer (I/O to Memory) l 1) I/O Device sends a DMA request l 2) DMAC activates the BR line l 3) CPU responds with BG line l 4) DMAC sends a DMA acknowledge to the I/O device l 5) I/O device puts a word in the data bus (for memory write) l 6) DMAC write a data to the address specified by Address register l 7) Decrement Word count register l 8) if Word count register = 0 EOT interrupt l 9) if Word count register 0 DMAC checks the DMA request from I/O device Computer System Architecture Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

u Transfer Modes l 1) Burst transfer : l 2) Cycle stealing transfer : u DMA Controller ( Intel 8237 DMAC ) l DMA Initialization Process » 1) Set Address register : n memory address for read/write » 2) Set Word count register : n the number of words to transfer » 3) Set transfer mode : n n n read/write, burst/cycle stealing, I/O to I/O, I/O to Memory, …. . » 4) DMA transfer start » 5) EOT (End of Transfer) n Interrupt Computer System Architecture Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

u Transfer Modes l 1) Burst transfer : l 2) Cycle stealing transfer : u DMA Controller ( Intel 8237 DMAC ) l DMA Initialization Process » 1) Set Address register : n memory address for read/write » 2) Set Word count register : n the number of words to transfer » 3) Set transfer mode : n n n read/write, burst/cycle stealing, I/O to I/O, I/O to Memory, …. . » 4) DMA transfer start » 5) EOT (End of Transfer) n Interrupt Computer System Architecture Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

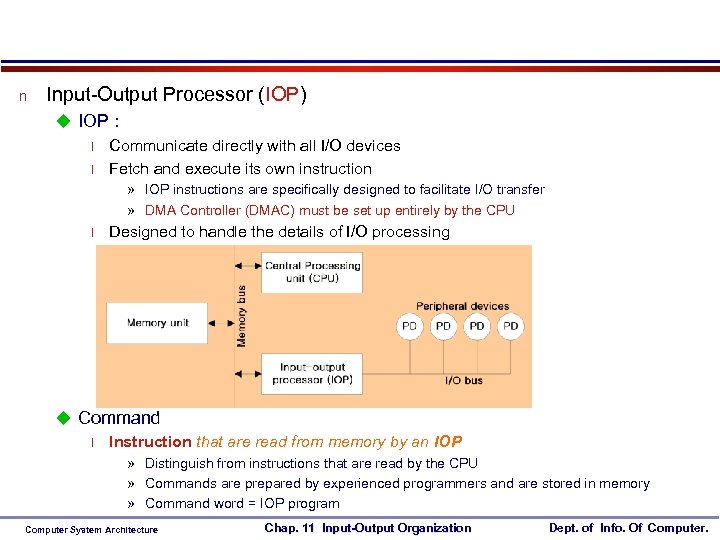

n Input-Output Processor (IOP) u IOP : l Communicate directly with all I/O devices l Fetch and execute its own instruction » IOP instructions are specifically designed to facilitate I/O transfer » DMA Controller (DMAC) must be set up entirely by the CPU l Designed to handle the details of I/O processing u Command l Instruction that are read from memory by an IOP » Distinguish from instructions that are read by the CPU » Commands are prepared by experienced programmers and are stored in memory » Command word = IOP program Computer System Architecture Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

n Input-Output Processor (IOP) u IOP : l Communicate directly with all I/O devices l Fetch and execute its own instruction » IOP instructions are specifically designed to facilitate I/O transfer » DMA Controller (DMAC) must be set up entirely by the CPU l Designed to handle the details of I/O processing u Command l Instruction that are read from memory by an IOP » Distinguish from instructions that are read by the CPU » Commands are prepared by experienced programmers and are stored in memory » Command word = IOP program Computer System Architecture Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

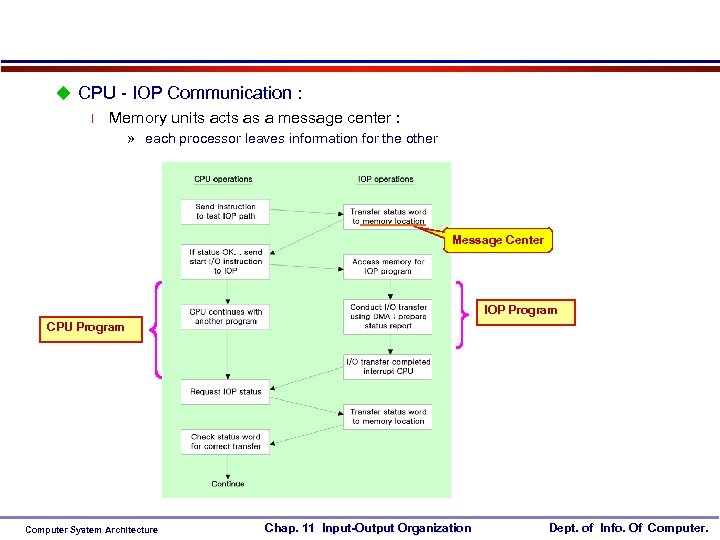

u CPU - IOP Communication : l Memory units acts as a message center : » each processor leaves information for the other Message Center IOP Program CPU Program Computer System Architecture Chap. 11 Input-Output Organization Dept. of Info. Of Computer.

u CPU - IOP Communication : l Memory units acts as a message center : » each processor leaves information for the other Message Center IOP Program CPU Program Computer System Architecture Chap. 11 Input-Output Organization Dept. of Info. Of Computer.