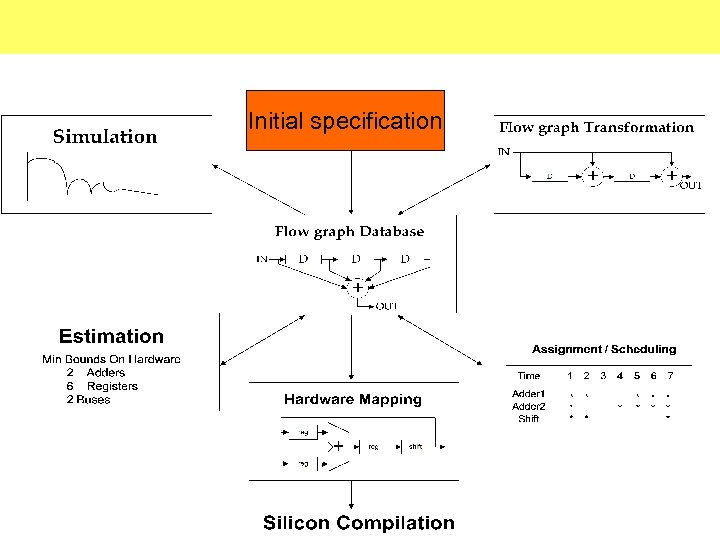

Initial specification

Initial specification

Why Synthesis? Why not Synthesis?

Why Synthesis? Why not Synthesis?

From Behavioral specification at ‘System Level’ (Algorithms) To Structural implementation at ‘Register Transfer Level’ of Data path (ALU’s, REG’s, MUX’s) and Controller

From Behavioral specification at ‘System Level’ (Algorithms) To Structural implementation at ‘Register Transfer Level’ of Data path (ALU’s, REG’s, MUX’s) and Controller

In Camposano Our Abstraction levels

In Camposano Our Abstraction levels

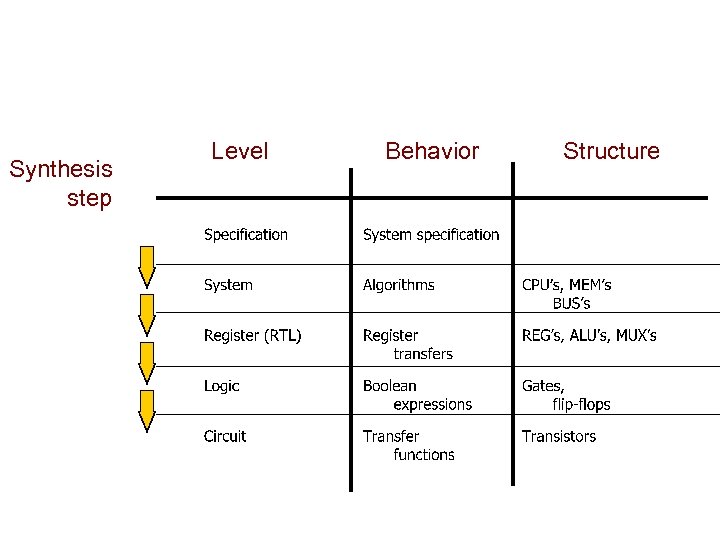

Synthesis step Level Behavior Structure

Synthesis step Level Behavior Structure

What are possible levels of synthesis? What are possible styles? How to automate big tasks?

What are possible levels of synthesis? What are possible styles? How to automate big tasks?

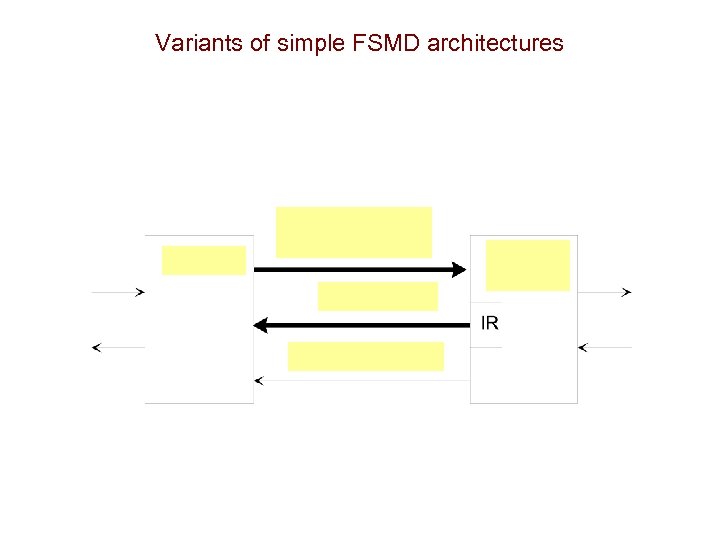

Variants of simple FSMD architectures

Variants of simple FSMD architectures

Variants of simple FSMD architectures

Variants of simple FSMD architectures

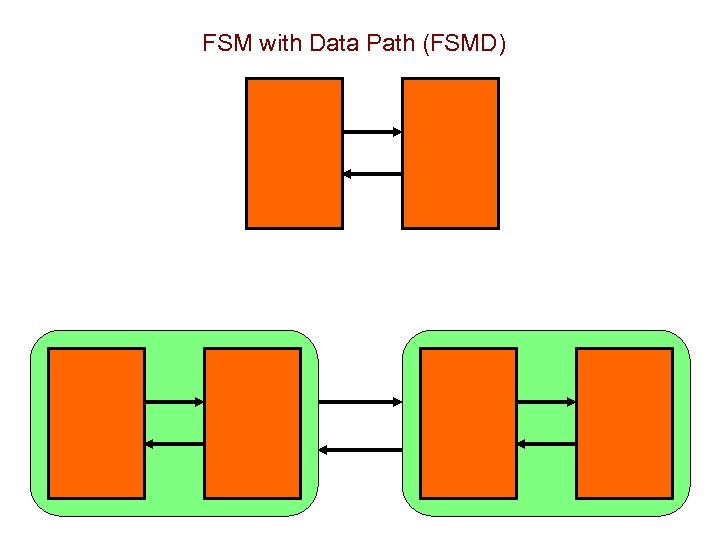

FSM with Data Path (FSMD)

FSM with Data Path (FSMD)

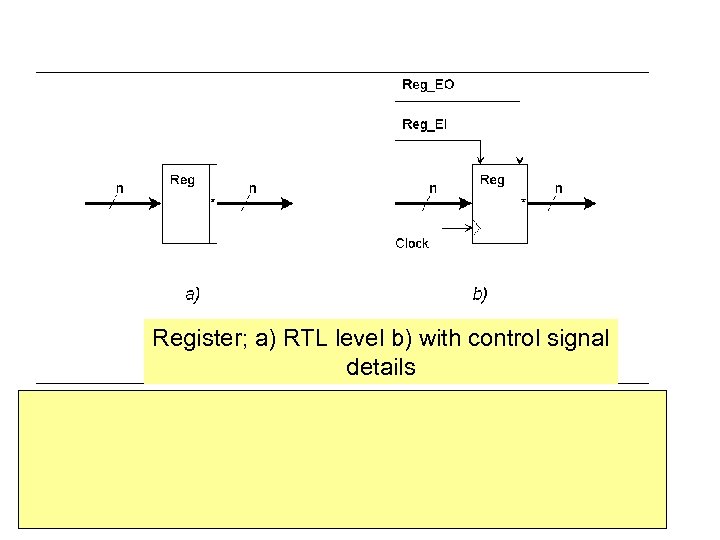

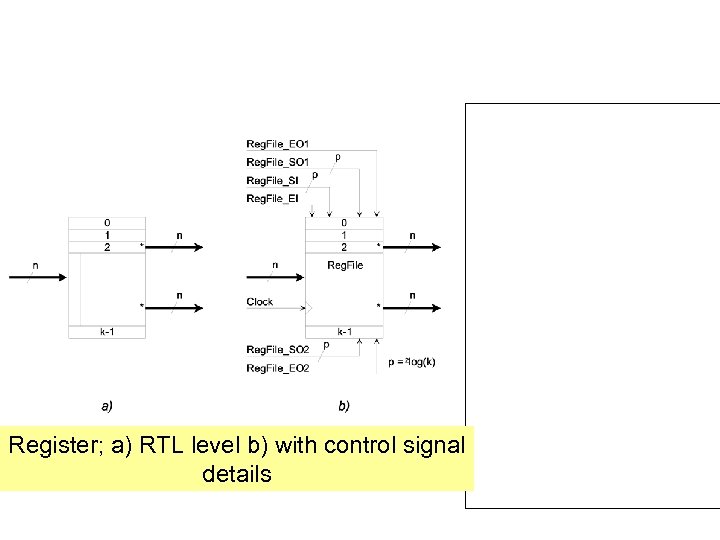

Register; a) RTL level b) with control signal details

Register; a) RTL level b) with control signal details

Register; a) RTL level b) with control signal details

Register; a) RTL level b) with control signal details

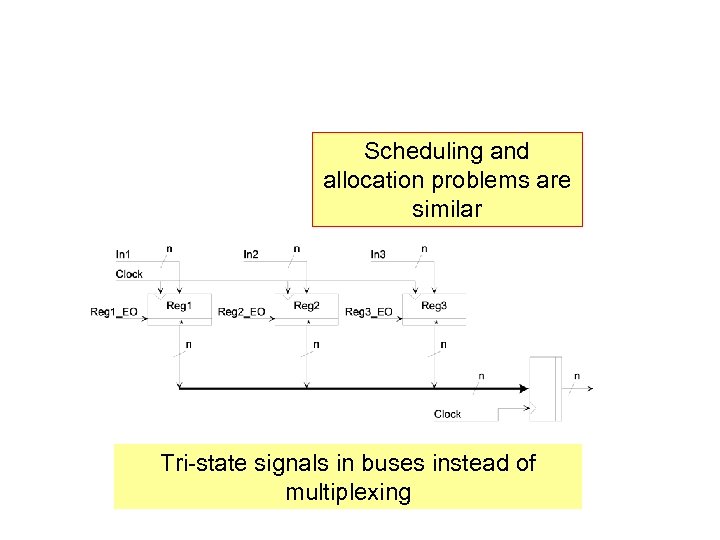

Scheduling and allocation problems are similar Tri-state signals in buses instead of multiplexing

Scheduling and allocation problems are similar Tri-state signals in buses instead of multiplexing

Semantics of variables

Semantics of variables

Semantics of variables

Semantics of variables

Example

Example

Timing semantics

Timing semantics

Synthesis policy for VHDL and Verilog

Synthesis policy for VHDL and Verilog

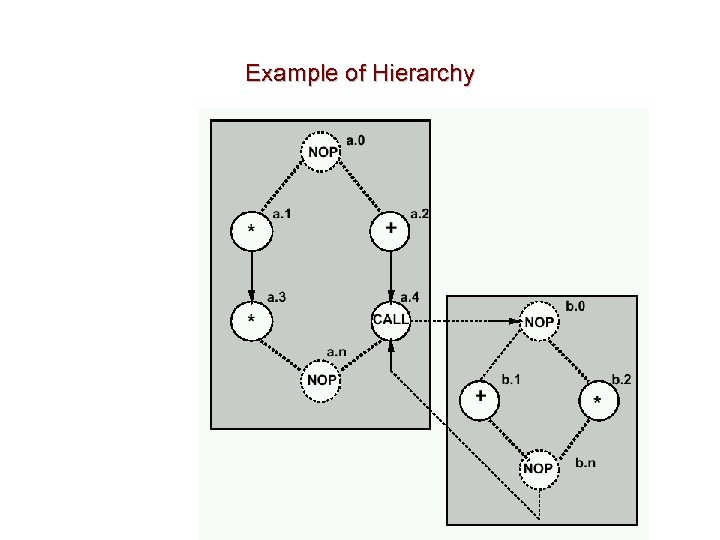

Example of Hierarchy

Example of Hierarchy

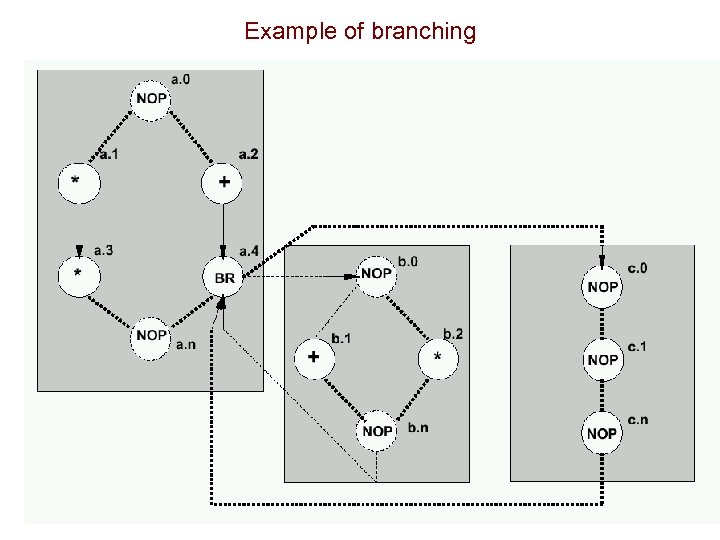

Example of branching

Example of branching

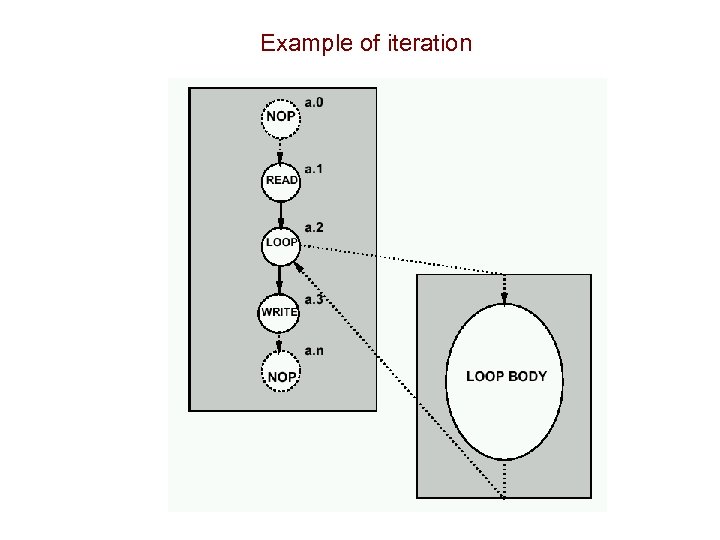

Example of iteration

Example of iteration

Example of iteration

Example of iteration

Control 1 Control of

Control 1 Control of

Control 2

Control 2

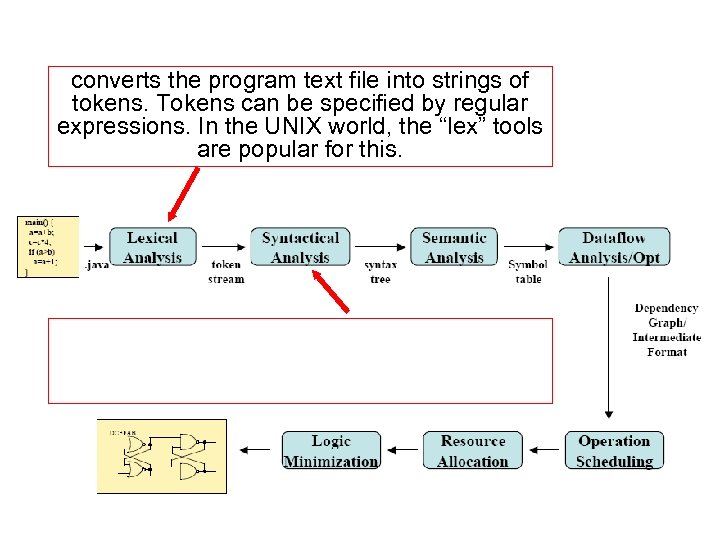

converts the program text file into strings of tokens. Tokens can be specified by regular expressions. In the UNIX world, the “lex” tools are popular for this.

converts the program text file into strings of tokens. Tokens can be specified by regular expressions. In the UNIX world, the “lex” tools are popular for this.

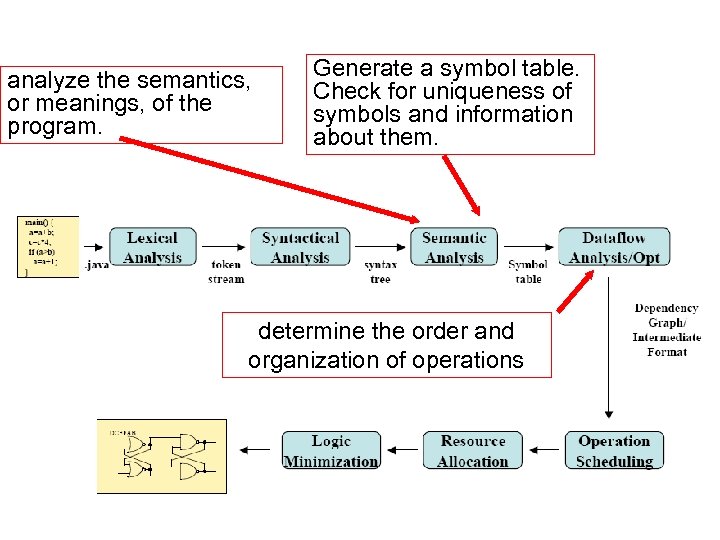

analyze the semantics, or meanings, of the program. Generate a symbol table. Check for uniqueness of symbols and information about them. determine the order and organization of operations

analyze the semantics, or meanings, of the program. Generate a symbol table. Check for uniqueness of symbols and information about them. determine the order and organization of operations