Информатика7.pptx

- Количество слайдов: 42

Информатика Лекция 7

Информатика Лекция 7

УМНОЖЕНИЕ ЦЕЛЫХ ЧИСЕЛ Умножение двоичных чисел состоит в последовательном умножении множимого на отдельные разряды множителя с суммированием результатов умножения. Результат умножения множимого на один разряд множителя принято называть частным произведением. 2

УМНОЖЕНИЕ ЦЕЛЫХ ЧИСЕЛ Умножение двоичных чисел состоит в последовательном умножении множимого на отдельные разряды множителя с суммированием результатов умножения. Результат умножения множимого на один разряд множителя принято называть частным произведением. 2

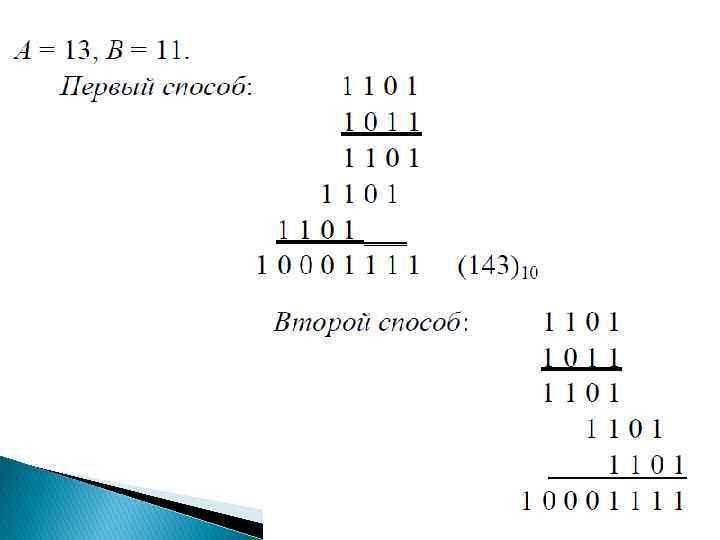

3

3

Особенности операции умножения целых чисел необходимо учитывать следующее: • каждое частное произведение либо совпадает с множимым, либо равно нулю; • формируемые частные произведения должны быть определенным образом сдвинуты друг относительно друга для их последующего суммирования; • частное произведение можно формировать, начиная как от младших, так и от старших разрядов множителя; • в общем случае для результата умножения требуется количество цифр, равное сумме количества цифр операндов. Если операнды имеют одинаковое количество цифр, то для суммы потребуется 2 n разрядов. 4

Особенности операции умножения целых чисел необходимо учитывать следующее: • каждое частное произведение либо совпадает с множимым, либо равно нулю; • формируемые частные произведения должны быть определенным образом сдвинуты друг относительно друга для их последующего суммирования; • частное произведение можно формировать, начиная как от младших, так и от старших разрядов множителя; • в общем случае для результата умножения требуется количество цифр, равное сумме количества цифр операндов. Если операнды имеют одинаковое количество цифр, то для суммы потребуется 2 n разрядов. 4

Особенности реализации операций умножения 1. В операционном устройстве для умножения двоичных чисел должен использоваться многоразрядный двоичный сумматор. Умножение реализуется в виде последовательного многошагового процесса, на каждом шаге которого проводится умножение на один разряд множителя. Для фиксации суммы частных произведений необходимо использовать 2 n-разрядный регистр при n-разрядных операндах. Перед началом операции этот регистр необходимо обнулить; 2. На каждом шаге умножения анализируется определенный разряд множителя. Если он равен 1, то на этом шаге проводится сложение суммы частных произведений с множимым. Если разряд равен 0, то сложение не проводится; 5

Особенности реализации операций умножения 1. В операционном устройстве для умножения двоичных чисел должен использоваться многоразрядный двоичный сумматор. Умножение реализуется в виде последовательного многошагового процесса, на каждом шаге которого проводится умножение на один разряд множителя. Для фиксации суммы частных произведений необходимо использовать 2 n-разрядный регистр при n-разрядных операндах. Перед началом операции этот регистр необходимо обнулить; 2. На каждом шаге умножения анализируется определенный разряд множителя. Если он равен 1, то на этом шаге проводится сложение суммы частных произведений с множимым. Если разряд равен 0, то сложение не проводится; 5

Особенности реализации операций умножения 3. Каждый шаг умножения должен сопровождаться сдвигом суммы частных произведений (СЧП) относительно неподвижного множимого, или на оборот: сдвиг множимого относительно неподвижной СЧП; 4. Умножение можно начинать как с младших, так и со старших разрядов множителя; 6

Особенности реализации операций умножения 3. Каждый шаг умножения должен сопровождаться сдвигом суммы частных произведений (СЧП) относительно неподвижного множимого, или на оборот: сдвиг множимого относительно неподвижной СЧП; 4. Умножение можно начинать как с младших, так и со старших разрядов множителя; 6

Особенности реализации операций умножения 5. В целях упрощения схемы умножения регистр множителя реализуется как сдвигающий, это дает возможность анализировать только один разряд регистра. При выполнении умножения, начиная от младших разрядов, схема анализа привязывается к младшему разряду регистра множителя, регистр при этом сдвигается вправо; При реализации умножения, начиная от старших разрядов, схема анализа привязывается к старшему разряду множителя, реализуется сдвиг влево. 6. Для фиксации момента завершения операции в операционном устройстве умножения должен быть использован суммирующий или вычитающий счетчик, который считает количество разрядов множителя; 7

Особенности реализации операций умножения 5. В целях упрощения схемы умножения регистр множителя реализуется как сдвигающий, это дает возможность анализировать только один разряд регистра. При выполнении умножения, начиная от младших разрядов, схема анализа привязывается к младшему разряду регистра множителя, регистр при этом сдвигается вправо; При реализации умножения, начиная от старших разрядов, схема анализа привязывается к старшему разряду множителя, реализуется сдвиг влево. 6. Для фиксации момента завершения операции в операционном устройстве умножения должен быть использован суммирующий или вычитающий счетчик, который считает количество разрядов множителя; 7

Способы (схемы) реализации умножения Для учета особенностей реализации операции умножения можно использовать четыре способа (схемы) умножения: 1. начиная от младших разрядов множителя со сдвигом множимого влево; 2. начиная от младших разрядов со сдвигом СЧП вправо; 3. начиная от старших разрядов со сдвигом множимого вправо; 4. начиная от старших разрядов со сдвигом СЧП влево. 8

Способы (схемы) реализации умножения Для учета особенностей реализации операции умножения можно использовать четыре способа (схемы) умножения: 1. начиная от младших разрядов множителя со сдвигом множимого влево; 2. начиная от младших разрядов со сдвигом СЧП вправо; 3. начиная от старших разрядов со сдвигом множимого вправо; 4. начиная от старших разрядов со сдвигом СЧП влево. 8

Анализ схем 1. В схемах умножения со сдвигом множимого для его представления требуется два n-разрядных регистра. 2. Для схем умножения со сдвигом СЧП для представления множимого требуется n-разрядный регистр. 3. В схемах умножения, начиная от старших разрядов со сдвигом множителя вправо, необходимо использовать 2 n-разрядный регистр. 9

Анализ схем 1. В схемах умножения со сдвигом множимого для его представления требуется два n-разрядных регистра. 2. Для схем умножения со сдвигом СЧП для представления множимого требуется n-разрядный регистр. 3. В схемах умножения, начиная от старших разрядов со сдвигом множителя вправо, необходимо использовать 2 n-разрядный регистр. 9

Анализ схем 4. Для схем умножения, начиняя от старших разрядов со сдвигом СЧП влево, требуется 2 n-разрядный регистр для хранения суммы СЧП. 5. Для схем умножения, начиная от младших разрядов со сдвигом СЧП вправо, требуется n-разрядный регистр СЧП. 10

Анализ схем 4. Для схем умножения, начиняя от старших разрядов со сдвигом СЧП влево, требуется 2 n-разрядный регистр для хранения суммы СЧП. 5. Для схем умножения, начиная от младших разрядов со сдвигом СЧП вправо, требуется n-разрядный регистр СЧП. 10

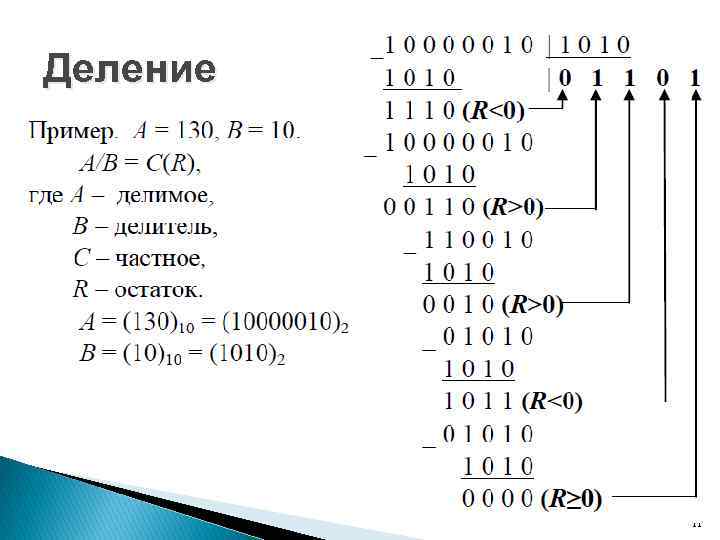

Деление 11

Деление 11

Особенности двоичного деления: 1) Процесс деления сводится к последовательному вычитанию делителя первоначально из делимого, а далее – из получаемых текущих остатков (под текущим остатком будем понимать промежуточный результат вычитания делителя из делимого на первом шаге или очередного остатка на последующих шагах). 2) На начальном шаге делитель совмещается со старшими разрядами делимого, а затем на каждом шаге делитель сдвигается на одну позицию (разряд) вправо относительно неподвижного текущего остатка. На последнем шаге делитель совмещается с младшими разрядами текущего остатка. 12

Особенности двоичного деления: 1) Процесс деления сводится к последовательному вычитанию делителя первоначально из делимого, а далее – из получаемых текущих остатков (под текущим остатком будем понимать промежуточный результат вычитания делителя из делимого на первом шаге или очередного остатка на последующих шагах). 2) На начальном шаге делитель совмещается со старшими разрядами делимого, а затем на каждом шаге делитель сдвигается на одну позицию (разряд) вправо относительно неподвижного текущего остатка. На последнем шаге делитель совмещается с младшими разрядами текущего остатка. 12

Особенности двоичного деления: 3) Цифры частного, вырабатываемые на каждом шаге, определяются знаком текущего остатка. Для остатка большего или равного 0 цифра частного равна 1, для остатка, который меньше 0, цифра частного равна 0. 4) О знаке текущего остатка можно судить по наличию или отсутствию заѐма в старший разряд делимого при вычитании. Если заѐм есть, то результат вычитания (т. е. текущий остаток) отрицателен. Если заѐм отсутствует, то результат вычитания и, соответственно, текущий остаток не отрицателен. 13

Особенности двоичного деления: 3) Цифры частного, вырабатываемые на каждом шаге, определяются знаком текущего остатка. Для остатка большего или равного 0 цифра частного равна 1, для остатка, который меньше 0, цифра частного равна 0. 4) О знаке текущего остатка можно судить по наличию или отсутствию заѐма в старший разряд делимого при вычитании. Если заѐм есть, то результат вычитания (т. е. текущий остаток) отрицателен. Если заѐм отсутствует, то результат вычитания и, соответственно, текущий остаток не отрицателен. 13

Архитектура персонального компьютера Основной принцип построения ЭВМ носит название архитектуры фон Неймана - американского ученого венгерского происхождения Джона фон Неймана, который ее предложил. Принцип программного управления. Принцип программы, сохраняемой в памяти. Принцип произвольного доступа к памяти. 14

Архитектура персонального компьютера Основной принцип построения ЭВМ носит название архитектуры фон Неймана - американского ученого венгерского происхождения Джона фон Неймана, который ее предложил. Принцип программного управления. Принцип программы, сохраняемой в памяти. Принцип произвольного доступа к памяти. 14

Принцип программного управления. Обеспечивает автоматизацию процесса вычислений на ЭВМ. Согласно этому принципу, для решения каждой задачи составляется программа, которая определяет последовательность действий компьютера. Эффективность программного управления будет выше при решении задачи этой же программой много раз (хотя и с разными начальными данными). 15

Принцип программного управления. Обеспечивает автоматизацию процесса вычислений на ЭВМ. Согласно этому принципу, для решения каждой задачи составляется программа, которая определяет последовательность действий компьютера. Эффективность программного управления будет выше при решении задачи этой же программой много раз (хотя и с разными начальными данными). 15

Принцип программы, сохраняемой в памяти. Согласно этому принципу, команды программы подаются, как и данные, в виде чисел и обрабатываются так же, как и числа, а сама программа перед выполнением загружается в оперативную память, что ускоряет процесс ее выполнения. 16

Принцип программы, сохраняемой в памяти. Согласно этому принципу, команды программы подаются, как и данные, в виде чисел и обрабатываются так же, как и числа, а сама программа перед выполнением загружается в оперативную память, что ускоряет процесс ее выполнения. 16

Принцип произвольного доступа к памяти. В соответствии с этим принципом, элементы программ и данных могут записываться в произвольное место оперативной памяти, что позволяет обратиться по любому заданному адресу (к конкретному участку памяти) без просмотра предыдущих. 17

Принцип произвольного доступа к памяти. В соответствии с этим принципом, элементы программ и данных могут записываться в произвольное место оперативной памяти, что позволяет обратиться по любому заданному адресу (к конкретному участку памяти) без просмотра предыдущих. 17

Архитектура компьютера Персональный компьютер типа IBM PC имеет довольно традиционную архитектуру микропроцессорной системы и содержит все обычные функциональные узлы: процессор, постоянную и оперативную память, устройства ввода/вывода, системную шину, источник питания. 18

Архитектура компьютера Персональный компьютер типа IBM PC имеет довольно традиционную архитектуру микропроцессорной системы и содержит все обычные функциональные узлы: процессор, постоянную и оперативную память, устройства ввода/вывода, системную шину, источник питания. 18

Архитектура компьютера 19

Архитектура компьютера 19

Основные узлы компьютера Центральный процессор — это микропроцессор со всеми необходимыми вспомогательными микросхемами, включая внешнюю кэш-память и контроллер системной шины. В большинстве случаев именно центральный процессор осуществляет обмен по системной шине. Оперативная память может занимать почти все адресуемое пространство памяти процессора. Однако чаще всего ее объем гораздо меньше. Оперативная память компьютера выполняется на микросхемах динамической памяти и поэтому требует регенерации. 20

Основные узлы компьютера Центральный процессор — это микропроцессор со всеми необходимыми вспомогательными микросхемами, включая внешнюю кэш-память и контроллер системной шины. В большинстве случаев именно центральный процессор осуществляет обмен по системной шине. Оперативная память может занимать почти все адресуемое пространство памяти процессора. Однако чаще всего ее объем гораздо меньше. Оперативная память компьютера выполняется на микросхемах динамической памяти и поэтому требует регенерации. 20

Основные узлы компьютера Постоянная память (ROM BIOS — Base Input/Output System) имеет небольшой объем, содержит программу начального запуска, описание конфигурации системы, а также драйверы (программы нижнего уровня) для взаимодействия с системными устройствами. Контроллер прерываний преобразует аппаратные прерывания системной магистрали в аппаратные прерывания процессора и задает адреса векторов прерывания. Все режимы функционирования контроллера прерываний задаются программно процессором перед началом работы. 21

Основные узлы компьютера Постоянная память (ROM BIOS — Base Input/Output System) имеет небольшой объем, содержит программу начального запуска, описание конфигурации системы, а также драйверы (программы нижнего уровня) для взаимодействия с системными устройствами. Контроллер прерываний преобразует аппаратные прерывания системной магистрали в аппаратные прерывания процессора и задает адреса векторов прерывания. Все режимы функционирования контроллера прерываний задаются программно процессором перед началом работы. 21

Основные узлы компьютера Контроллер прямого доступа к памяти принимает запрос на ПДП из системной магистрали, передает его процессору, а после предоставления процессором магистрали производит пересылку данных между памятью и устройством ввода/вывода. Все режимы функционирования контроллера ПДП задаются программно процессором перед началом работы. Использование встроенных в компьютер контроллеров прерываний и ПДП позволяет существенно упростить аппаратуру применяемых плат расширения. Контроллер регенерации осуществляет периодическое обновление информации в динамической оперативной памяти путем проведения по шине специальных циклов регенерации. На время циклов регенерации он становится хозяином (задатчиком) шины. 22

Основные узлы компьютера Контроллер прямого доступа к памяти принимает запрос на ПДП из системной магистрали, передает его процессору, а после предоставления процессором магистрали производит пересылку данных между памятью и устройством ввода/вывода. Все режимы функционирования контроллера ПДП задаются программно процессором перед началом работы. Использование встроенных в компьютер контроллеров прерываний и ПДП позволяет существенно упростить аппаратуру применяемых плат расширения. Контроллер регенерации осуществляет периодическое обновление информации в динамической оперативной памяти путем проведения по шине специальных циклов регенерации. На время циклов регенерации он становится хозяином (задатчиком) шины. 22

Основные узлы компьютера Перестановщик байтов данных помогает производить обмен данными между устройствами с разной разрядностью, пересылать целые слова или отдельные байты. Часы реального времени и таймер-счетчик — это устройства для внутреннего контроля времени и даты, а также для программной выдержки временных интервалов, программного задания частоты и т. д. 23

Основные узлы компьютера Перестановщик байтов данных помогает производить обмен данными между устройствами с разной разрядностью, пересылать целые слова или отдельные байты. Часы реального времени и таймер-счетчик — это устройства для внутреннего контроля времени и даты, а также для программной выдержки временных интервалов, программного задания частоты и т. д. 23

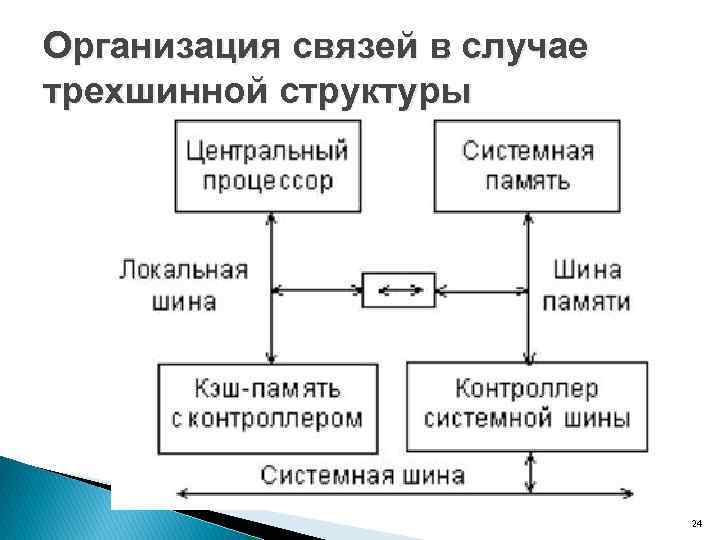

Организация связей в случае трехшинной структуры 24

Организация связей в случае трехшинной структуры 24

Назначение шин к локальной шине подключаются центральный процессор и кэш-память (быстрая буферная память); к шине памяти подключается оперативная и постоянная память компьютера, а также контроллер системной шины; к системной шине (магистрали) подключаются все остальные устройства компьютера. 25

Назначение шин к локальной шине подключаются центральный процессор и кэш-память (быстрая буферная память); к шине памяти подключается оперативная и постоянная память компьютера, а также контроллер системной шины; к системной шине (магистрали) подключаются все остальные устройства компьютера. 25

Системная шина Основной обязанностью системной шины является передача информации между процессором и остальными компонентами компьютера. По этой шине осуществляется не только передача информации, но и адресация устройств, а также обмен специальными служебными сигналами. Таким образом, упрощенно системную шину (магистраль) можно представить как совокупность сигнальных линий, объединенных по их назначению (данные, адреса, управление). Основной характеристикой этих линий является их разрядность - разрядность адресной шины, шины данных. 26

Системная шина Основной обязанностью системной шины является передача информации между процессором и остальными компонентами компьютера. По этой шине осуществляется не только передача информации, но и адресация устройств, а также обмен специальными служебными сигналами. Таким образом, упрощенно системную шину (магистраль) можно представить как совокупность сигнальных линий, объединенных по их назначению (данные, адреса, управление). Основной характеристикой этих линий является их разрядность - разрядность адресной шины, шины данных. 26

Процессор Основа вычислительной машины – процессор; он состоит из компонентов: 1. 2. 3. арифметико-логическое устройство - АЛУ, устройство управления – УУ, регистры для временного хранения информации. 27

Процессор Основа вычислительной машины – процессор; он состоит из компонентов: 1. 2. 3. арифметико-логическое устройство - АЛУ, устройство управления – УУ, регистры для временного хранения информации. 27

Регистры Регистром называется функциональный узел, осуществляющий приём, хранение и передачу информации. Регистры состоят из группы триггеров, и служат для временного хранения двоичных чисел. При выборке из памяти очередной команды она помещается в регистр команд. В процессоре имеется значительное количество регистров, большая часть которых используется самим процессором и недоступна программисту. 28

Регистры Регистром называется функциональный узел, осуществляющий приём, хранение и передачу информации. Регистры состоят из группы триггеров, и служат для временного хранения двоичных чисел. При выборке из памяти очередной команды она помещается в регистр команд. В процессоре имеется значительное количество регистров, большая часть которых используется самим процессором и недоступна программисту. 28

Регистровая КЭШ-память (Cache – тайник) – высокоскоростная память сравнительно большой емкости, являющаяся буфером между ОП и МП и позволяющая увеличить скорость выполнения операций. Регистры КЭШ-памяти недоступны для пользователя. В КЭШ-памяти хранятся данные, которые МП получил и будет использовать в ближайшие такты своей работы. Быстрый доступ к этим данным и позволяет сократить время выполнения очередных команд программы. При выполнении программы данные, считанные из ОП с небольшим опережением, записываются в КЭШ-память. 29

Регистровая КЭШ-память (Cache – тайник) – высокоскоростная память сравнительно большой емкости, являющаяся буфером между ОП и МП и позволяющая увеличить скорость выполнения операций. Регистры КЭШ-памяти недоступны для пользователя. В КЭШ-памяти хранятся данные, которые МП получил и будет использовать в ближайшие такты своей работы. Быстрый доступ к этим данным и позволяет сократить время выполнения очередных команд программы. При выполнении программы данные, считанные из ОП с небольшим опережением, записываются в КЭШ-память. 29

Характеристики процессора Разрядность Тактовая частота Адресное пространство 30

Характеристики процессора Разрядность Тактовая частота Адресное пространство 30

Intel 80386 Первым был Intel 80386, он появился в 1986 году и мог работать на частоте до 40 МГц. Этот процессор относится к третьему поколению Использовался техпроцесс 1500 нм. 31

Intel 80386 Первым был Intel 80386, он появился в 1986 году и мог работать на частоте до 40 МГц. Этот процессор относится к третьему поколению Использовался техпроцесс 1500 нм. 31

80486 Четвертое поколение. Процессор работал на частоте 50 МГц и мог выполнять 40 миллионов команд в секунду. Процессор имел 8 кб кэша первого уровня Для изготовления использовался техпроцесс 1000 нм. 32

80486 Четвертое поколение. Процессор работал на частоте 50 МГц и мог выполнять 40 миллионов команд в секунду. Процессор имел 8 кб кэша первого уровня Для изготовления использовался техпроцесс 1000 нм. 32

Р 5 и Р 6 P 5 или Pentium. Эти процессоры появились в 1993 году, здесь был увеличен кэш до 32 кб, частота до 60 МГц, а техпроцесс уменьшен до 800 нм. В шестом поколении P 6 размер кэша составлял 32 кб, а частота достигла 450 МГц. Тех процесс был уменьшен до 180 нм. 33

Р 5 и Р 6 P 5 или Pentium. Эти процессоры появились в 1993 году, здесь был увеличен кэш до 32 кб, частота до 60 МГц, а техпроцесс уменьшен до 800 нм. В шестом поколении P 6 размер кэша составлял 32 кб, а частота достигла 450 МГц. Тех процесс был уменьшен до 180 нм. 33

Архитектура Net. Burst Использовалось 16 кб кэша первого уровня на каждое ядро, и до 2 Мб кэша второго уровня. Частота выросла до 3 ГГц, а техпроцесс остался на том же уровне — 180 нм. Появились 64 битные процессоры, которые поддерживали адресацию большего количества памяти. Также было внесено множество расширений команд. Добавлена технология Hyper-Threading, которая позволяла создавать два потока из одного ядра, что повышало производительность. 34

Архитектура Net. Burst Использовалось 16 кб кэша первого уровня на каждое ядро, и до 2 Мб кэша второго уровня. Частота выросла до 3 ГГц, а техпроцесс остался на том же уровне — 180 нм. Появились 64 битные процессоры, которые поддерживали адресацию большего количества памяти. Также было внесено множество расширений команд. Добавлена технология Hyper-Threading, которая позволяла создавать два потока из одного ядра, что повышало производительность. 34

Архитектура Intel Core Одной из причин разработки этой архитектуры была невозможность увеличения частоты в Net. Brust, а также ее очень большое тепловыделение. Эта архитектура была рассчитана на разработку многоядерных процессоров, размер кэша первого уровня был увеличен до 64 Кб. Частота осталась на уровне 3 ГГц, но зато была сильно снижена потребляемая мощность, а также техпроцесс, до 60 нм. Не поддерживали Hyper-Threading 35

Архитектура Intel Core Одной из причин разработки этой архитектуры была невозможность увеличения частоты в Net. Brust, а также ее очень большое тепловыделение. Эта архитектура была рассчитана на разработку многоядерных процессоров, размер кэша первого уровня был увеличен до 64 Кб. Частота осталась на уровне 3 ГГц, но зато была сильно снижена потребляемая мощность, а также техпроцесс, до 60 нм. Не поддерживали Hyper-Threading 35

Первое поколение — Nehalem Появилась в 2007 году. Здесь используется 45 нм тех процесс и была добавлена поддержка технологии Hyper-Therading. Процессоры Nehalem имеют размер L 1 кэша 64 Кб, 4 Мб L 2 кэша и 12 Мб кєша L 3. Кэш доступен для всех ядер процессора. Появилась возможность встраивать графический ускоритель в процессор. 36

Первое поколение — Nehalem Появилась в 2007 году. Здесь используется 45 нм тех процесс и была добавлена поддержка технологии Hyper-Therading. Процессоры Nehalem имеют размер L 1 кэша 64 Кб, 4 Мб L 2 кэша и 12 Мб кєша L 3. Кэш доступен для всех ядер процессора. Появилась возможность встраивать графический ускоритель в процессор. 36

Второе поколение — Sandy Bridge появилась в 2011 году для замены Nehalem. Используется техпроцесс 32 нм, используется 64 Кб кэша первого уровня, 256 Кб кэша второго уровня и 8 Мб кэша третьего уровня. Также теперь все устройства выпускаются со встроенным графическим ускорителем. Была увеличена максимальная частота, а также общая производительность. 37

Второе поколение — Sandy Bridge появилась в 2011 году для замены Nehalem. Используется техпроцесс 32 нм, используется 64 Кб кэша первого уровня, 256 Кб кэша второго уровня и 8 Мб кэша третьего уровня. Также теперь все устройства выпускаются со встроенным графическим ускорителем. Была увеличена максимальная частота, а также общая производительность. 37

Третье поколение — Ivy Bridge Процессоры Ivy Bridge работают быстрее чем Sandy Bridge. Для изготовления используется техпроцесс 22 нм. Потребляют на 50% меньше энергии чем предыдущие модели, а также дают повышение на 25 -60% производительности. 38

Третье поколение — Ivy Bridge Процессоры Ivy Bridge работают быстрее чем Sandy Bridge. Для изготовления используется техпроцесс 22 нм. Потребляют на 50% меньше энергии чем предыдущие модели, а также дают повышение на 25 -60% производительности. 38

Четвертое поколение — Haswell Поколение процессора Intel Haswell было разработано в 2012 году. Использовался тот же техпроцесс — 22 нм, изменен дизайн кэша, улучшены механизмы энергопотребления и немного производительность. Основное преимущество Haswell в том, что она может использоваться в портативных устройствах из-за очень низкого энергопотребления. 39

Четвертое поколение — Haswell Поколение процессора Intel Haswell было разработано в 2012 году. Использовался тот же техпроцесс — 22 нм, изменен дизайн кэша, улучшены механизмы энергопотребления и немного производительность. Основное преимущество Haswell в том, что она может использоваться в портативных устройствах из-за очень низкого энергопотребления. 39

Пятое поколение — Broadwell Улучшенная версия архитектуры Haswell, которая использует техпроцесс 14 нм. В архитектуру было внесено несколько улучшений, которые позволили повысить производительность в среднем на 5%. 40

Пятое поколение — Broadwell Улучшенная версия архитектуры Haswell, которая использует техпроцесс 14 нм. В архитектуру было внесено несколько улучшений, которые позволили повысить производительность в среднем на 5%. 40

Шестое поколение — Skylake вышла в 2015 году. Это одно из самых значительных обновлений архитектуры Core. Для установки процессора на материнскую плату используется сокет LGA 1151. Поддерживается память DDR 4, но сохранилась поддержка DDR 3. По традиции была увеличенная производительность, а также снижено энергопотребление. 41

Шестое поколение — Skylake вышла в 2015 году. Это одно из самых значительных обновлений архитектуры Core. Для установки процессора на материнскую плату используется сокет LGA 1151. Поддерживается память DDR 4, но сохранилась поддержка DDR 3. По традиции была увеличенная производительность, а также снижено энергопотребление. 41

Седьмое поколение — Kaby Lake Kaby Lake вышло в 2017 году, первые процессоры появились в середине января. Сохранен техпроцесс 14 нм, а также тот же сокет LGA 1151. Поддерживаются планки памяти DDR 3 L SDRAM и DDR 4 SDRAM, шины PCI Express 3. 0, USB 3. 1. Немного увеличена частота, а также уменьшена плотность расположения транзисторов. Максимальная частота 4, 2 ГГц. 42

Седьмое поколение — Kaby Lake Kaby Lake вышло в 2017 году, первые процессоры появились в середине января. Сохранен техпроцесс 14 нм, а также тот же сокет LGA 1151. Поддерживаются планки памяти DDR 3 L SDRAM и DDR 4 SDRAM, шины PCI Express 3. 0, USB 3. 1. Немного увеличена частота, а также уменьшена плотность расположения транзисторов. Максимальная частота 4, 2 ГГц. 42