Lektsii_Tema_01_Arkhitektura_kompyutera_adresa.ppt

- Количество слайдов: 18

Информационные технологии Тема 1. Архитектура компьютера, адресация, представление данных Шевченко А. В. Тема 1. Архитектура компьютера, адресация, представление данных 1

Информационные технологии Тема 1. Архитектура компьютера, адресация, представление данных Шевченко А. В. Тема 1. Архитектура компьютера, адресация, представление данных 1

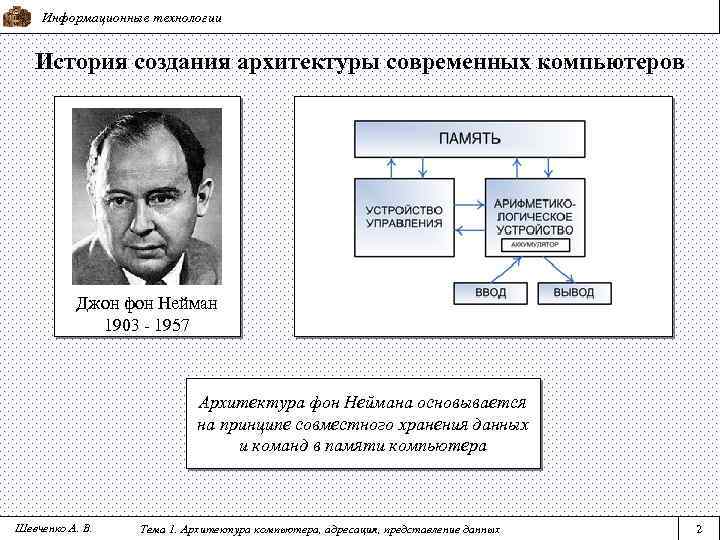

Информационные технологии История создания архитектуры современных компьютеров Джон фон Нейман 1903 - 1957 Архитектура фон Неймана основывается на принципе совместного хранения данных и команд в памяти компьютера Шевченко А. В. Тема 1. Архитектура компьютера, адресация, представление данных 2

Информационные технологии История создания архитектуры современных компьютеров Джон фон Нейман 1903 - 1957 Архитектура фон Неймана основывается на принципе совместного хранения данных и команд в памяти компьютера Шевченко А. В. Тема 1. Архитектура компьютера, адресация, представление данных 2

Информационные технологии Принципы архитектуры фон Неймана • Использование двоичной системы счисления для данных и команд • Программное управление (процессор исполняет команды их памяти) • Однородность памяти (команды и данные хранятся в одной памяти) • Адресуемость памяти (все ячейки имеют адрес и доступны процессору) • Последовательное выполнение команд (одна за другой) • Условный переход (возможность изменения последовательности команд) Шевченко А. В. Тема 1. Архитектура компьютера, адресация, представление данных 3

Информационные технологии Принципы архитектуры фон Неймана • Использование двоичной системы счисления для данных и команд • Программное управление (процессор исполняет команды их памяти) • Однородность памяти (команды и данные хранятся в одной памяти) • Адресуемость памяти (все ячейки имеют адрес и доступны процессору) • Последовательное выполнение команд (одна за другой) • Условный переход (возможность изменения последовательности команд) Шевченко А. В. Тема 1. Архитектура компьютера, адресация, представление данных 3

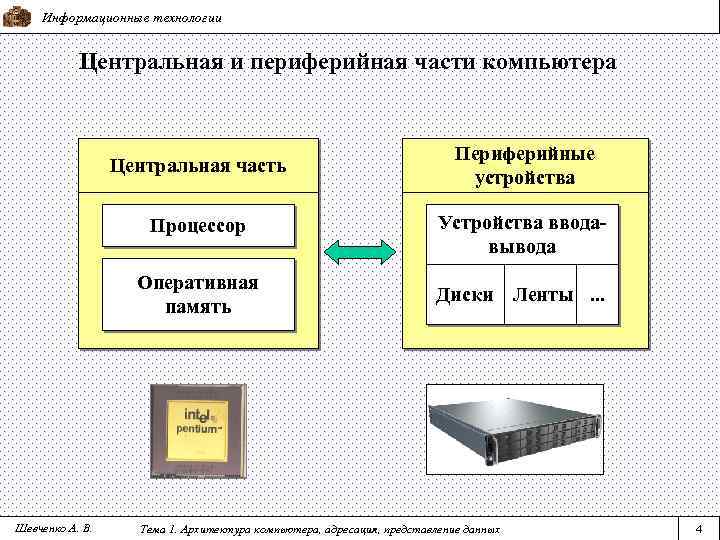

Информационные технологии Центральная и периферийная части компьютера Центральная часть Процессор Устройства вводавывода Оперативная память Шевченко А. В. Периферийные устройства Диски Ленты. . . Тема 1. Архитектура компьютера, адресация, представление данных 4

Информационные технологии Центральная и периферийная части компьютера Центральная часть Процессор Устройства вводавывода Оперативная память Шевченко А. В. Периферийные устройства Диски Ленты. . . Тема 1. Архитектура компьютера, адресация, представление данных 4

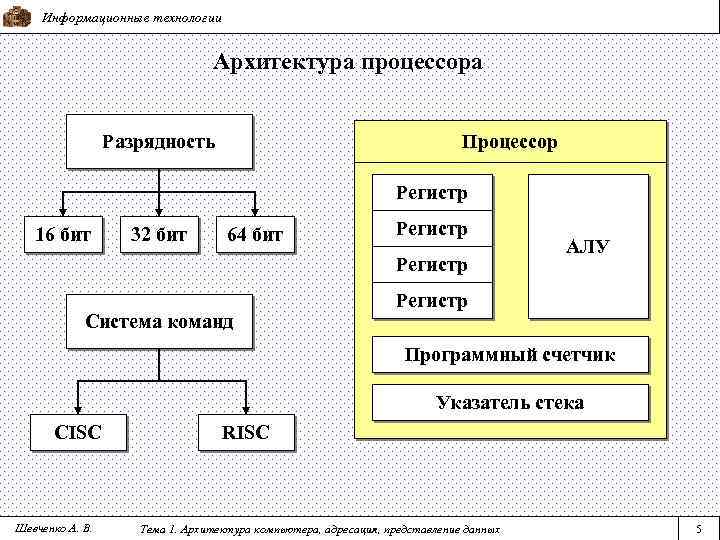

Информационные технологии Архитектура процессора Разрядность Процессор Регистр 16 бит 32 бит 64 бит Регистр Система команд АЛУ Регистр Программный счетчик Указатель стека CISC Шевченко А. В. RISC Тема 1. Архитектура компьютера, адресация, представление данных 5

Информационные технологии Архитектура процессора Разрядность Процессор Регистр 16 бит 32 бит 64 бит Регистр Система команд АЛУ Регистр Программный счетчик Указатель стека CISC Шевченко А. В. RISC Тема 1. Архитектура компьютера, адресация, представление данных 5

Информационные технологии Команды процессора Процессор PDP 11 CLR BNE переход INC инкремент BEQ переход DEC декремент JMP вызов TST тестирование RTS возврат MOV пересылка ROR цикл. сдвиг CMP проверка ROL цикл. сдвиг ADD сложение ASR сдвиг SUB Шевченко А. В. очистка вычитание ASL сдвиг Тема 1. Архитектура компьютера, адресация, представление данных 6

Информационные технологии Команды процессора Процессор PDP 11 CLR BNE переход INC инкремент BEQ переход DEC декремент JMP вызов TST тестирование RTS возврат MOV пересылка ROR цикл. сдвиг CMP проверка ROL цикл. сдвиг ADD сложение ASR сдвиг SUB Шевченко А. В. очистка вычитание ASL сдвиг Тема 1. Архитектура компьютера, адресация, представление данных 6

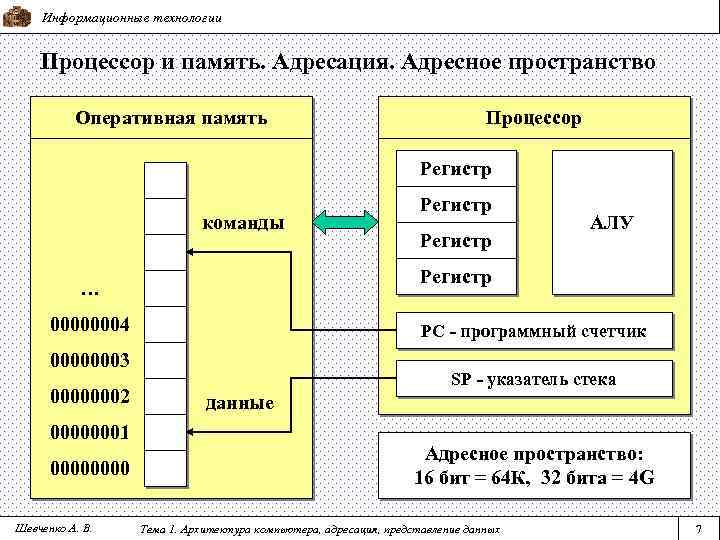

Информационные технологии Процессор и память. Адресация. Адресное пространство Оперативная память Процессор Регистр команды 00000004 PC - программный счетчик 00000003 00000001 0000 Шевченко А. В. Регистр АЛУ Регистр … 00000002 Регистр SP - указатель стека данные Адресное пространство: 16 бит = 64 К, 32 бита = 4 G Тема 1. Архитектура компьютера, адресация, представление данных 7

Информационные технологии Процессор и память. Адресация. Адресное пространство Оперативная память Процессор Регистр команды 00000004 PC - программный счетчик 00000003 00000001 0000 Шевченко А. В. Регистр АЛУ Регистр … 00000002 Регистр SP - указатель стека данные Адресное пространство: 16 бит = 64 К, 32 бита = 4 G Тема 1. Архитектура компьютера, адресация, представление данных 7

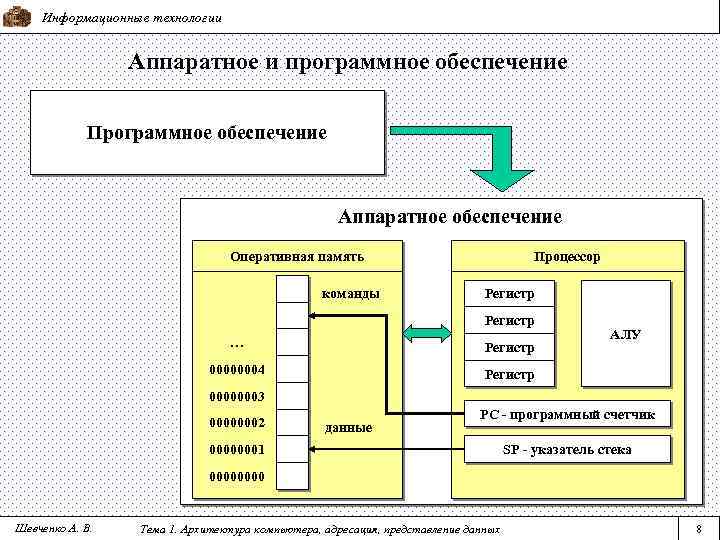

Информационные технологии Аппаратное и программное обеспечение Программное обеспечение Аппаратное обеспечение Оперативная память команды Процессор Регистр … Регистр 00000004 АЛУ Регистр 00000003 00000002 данные PC - программный счетчик 00000001 SP - указатель стека 0000 Шевченко А. В. Тема 1. Архитектура компьютера, адресация, представление данных 8

Информационные технологии Аппаратное и программное обеспечение Программное обеспечение Аппаратное обеспечение Оперативная память команды Процессор Регистр … Регистр 00000004 АЛУ Регистр 00000003 00000002 данные PC - программный счетчик 00000001 SP - указатель стека 0000 Шевченко А. В. Тема 1. Архитектура компьютера, адресация, представление данных 8

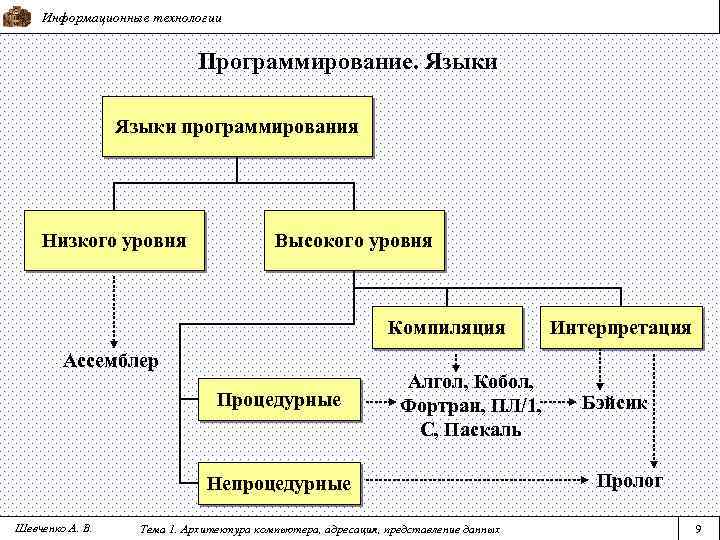

Информационные технологии Программирование. Языки программирования Низкого уровня Высокого уровня Компиляция Ассемблер Процедурные Алгол, Кобол, Фортран, ПЛ/1, С, Паскаль Непроцедурные Шевченко А. В. Тема 1. Архитектура компьютера, адресация, представление данных Интерпретация Бэйсик Пролог 9

Информационные технологии Программирование. Языки программирования Низкого уровня Высокого уровня Компиляция Ассемблер Процедурные Алгол, Кобол, Фортран, ПЛ/1, С, Паскаль Непроцедурные Шевченко А. В. Тема 1. Архитектура компьютера, адресация, представление данных Интерпретация Бэйсик Пролог 9

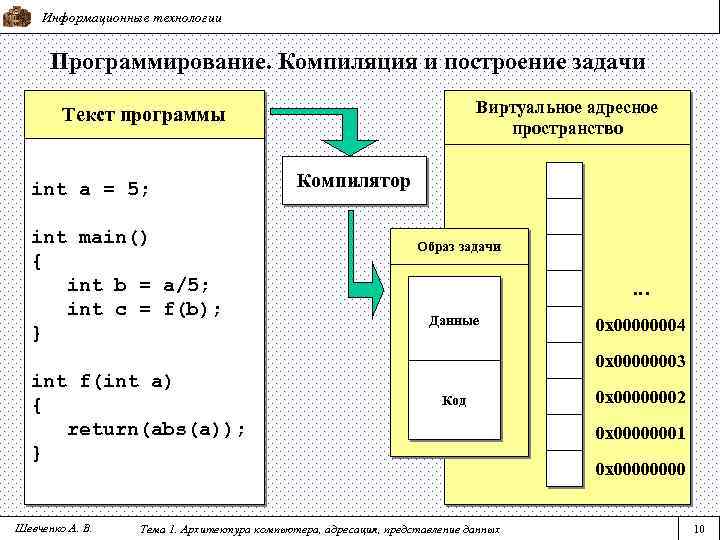

Информационные технологии Программирование. Компиляция и построение задачи Виртуальное адресное пространство Текст программы int a = 5; int main() { int b = a/5; int c = f(b); } int f(int a) { return(abs(a)); } Шевченко А. В. Компилятор Образ задачи … Данные 0 x 00000004 0 x 00000003 Код Тема 1. Архитектура компьютера, адресация, представление данных 0 x 00000002 0 x 00000001 0 x 0000 10

Информационные технологии Программирование. Компиляция и построение задачи Виртуальное адресное пространство Текст программы int a = 5; int main() { int b = a/5; int c = f(b); } int f(int a) { return(abs(a)); } Шевченко А. В. Компилятор Образ задачи … Данные 0 x 00000004 0 x 00000003 Код Тема 1. Архитектура компьютера, адресация, представление данных 0 x 00000002 0 x 00000001 0 x 0000 10

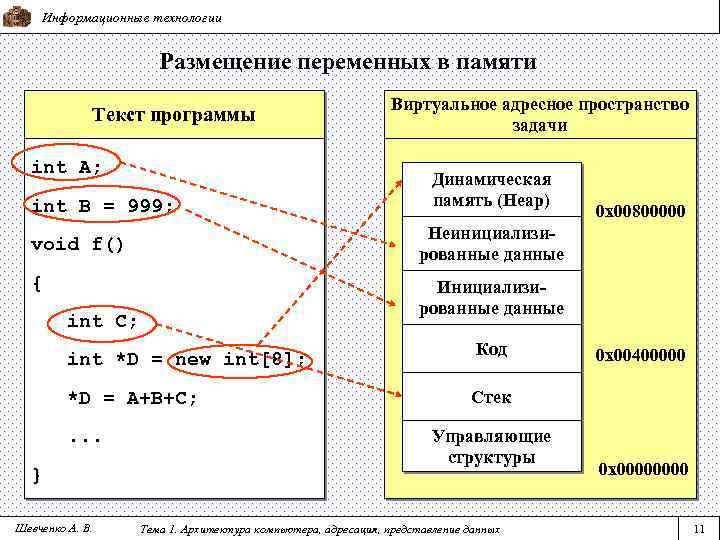

Информационные технологии Размещение переменных в памяти Текст программы int A; int B = 999; { int *D = new int[8]; *D = A+B+C; Шевченко А. В. 0 x 00800000 Инициализированные данные int C; } Динамическая память (Heap) Неинициализированные данные void f() . . . Виртуальное адресное пространство задачи Код 0 x 00400000 Стек Управляющие структуры Тема 1. Архитектура компьютера, адресация, представление данных 0 x 0000 11

Информационные технологии Размещение переменных в памяти Текст программы int A; int B = 999; { int *D = new int[8]; *D = A+B+C; Шевченко А. В. 0 x 00800000 Инициализированные данные int C; } Динамическая память (Heap) Неинициализированные данные void f() . . . Виртуальное адресное пространство задачи Код 0 x 00400000 Стек Управляющие структуры Тема 1. Архитектура компьютера, адресация, представление данных 0 x 0000 11

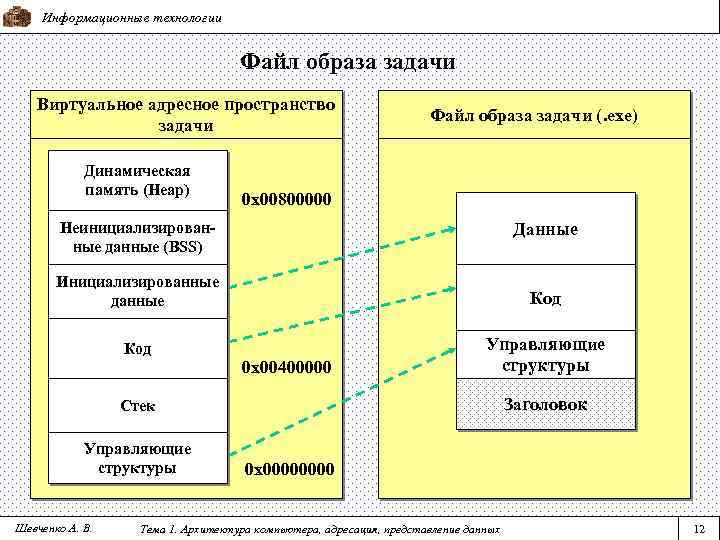

Информационные технологии Файл образа задачи Виртуальное адресное пространство задачи Динамическая память (Heap) Файл образа задачи (. exe) 0 x 00800000 Данные Неинициализированные данные (BSS) Инициализированные данные Код Управляющие структуры 0 x 00400000 Заголовок Стек Управляющие структуры Шевченко А. В. 0 x 0000 Тема 1. Архитектура компьютера, адресация, представление данных 12

Информационные технологии Файл образа задачи Виртуальное адресное пространство задачи Динамическая память (Heap) Файл образа задачи (. exe) 0 x 00800000 Данные Неинициализированные данные (BSS) Инициализированные данные Код Управляющие структуры 0 x 00400000 Заголовок Стек Управляющие структуры Шевченко А. В. 0 x 0000 Тема 1. Архитектура компьютера, адресация, представление данных 12

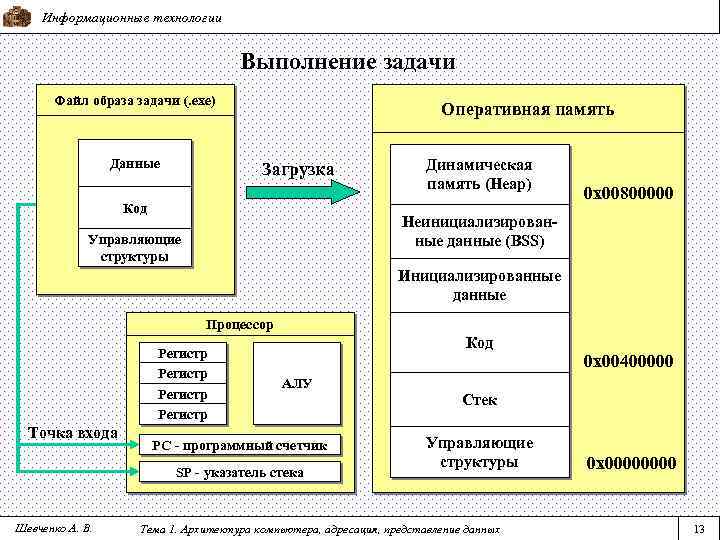

Информационные технологии Выполнение задачи Файл образа задачи (. exe) Данные Оперативная память Загрузка Код Динамическая память (Heap) 0 x 00800000 Неинициализированные данные (BSS) Управляющие структуры Инициализированные данные Процессор Регистр Точка входа Код АЛУ PC - программный счетчик SP - указатель стека Шевченко А. В. 0 x 00400000 Стек Управляющие структуры Тема 1. Архитектура компьютера, адресация, представление данных 0 x 0000 13

Информационные технологии Выполнение задачи Файл образа задачи (. exe) Данные Оперативная память Загрузка Код Динамическая память (Heap) 0 x 00800000 Неинициализированные данные (BSS) Управляющие структуры Инициализированные данные Процессор Регистр Точка входа Код АЛУ PC - программный счетчик SP - указатель стека Шевченко А. В. 0 x 00400000 Стек Управляющие структуры Тема 1. Архитектура компьютера, адресация, представление данных 0 x 0000 13

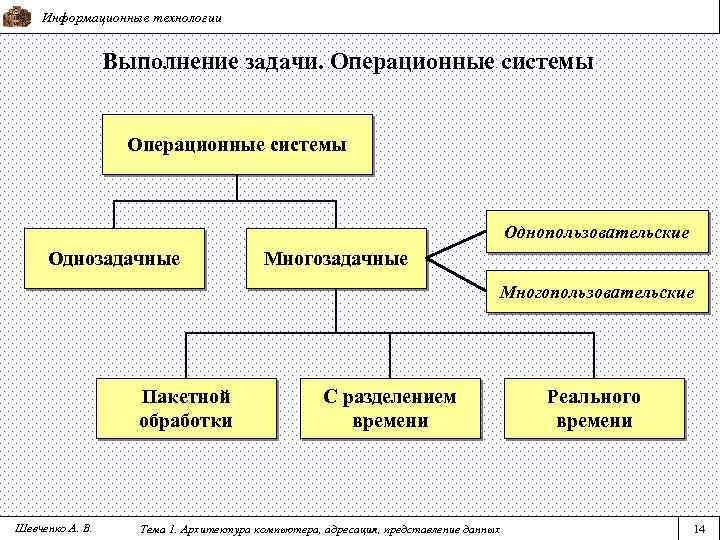

Информационные технологии Выполнение задачи. Операционные системы Однопользовательские Однозадачные Многопользовательские Пакетной обработки Шевченко А. В. С разделением времени Тема 1. Архитектура компьютера, адресация, представление данных Реального времени 14

Информационные технологии Выполнение задачи. Операционные системы Однопользовательские Однозадачные Многопользовательские Пакетной обработки Шевченко А. В. С разделением времени Тема 1. Архитектура компьютера, адресация, представление данных Реального времени 14

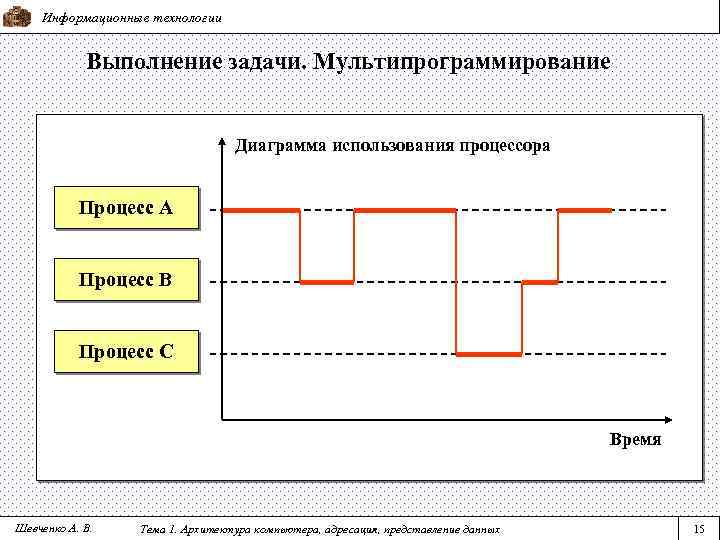

Информационные технологии Выполнение задачи. Мультипрограммирование Диаграмма использования процессора Процесс А Процесс В Процесс С Время Шевченко А. В. Тема 1. Архитектура компьютера, адресация, представление данных 15

Информационные технологии Выполнение задачи. Мультипрограммирование Диаграмма использования процессора Процесс А Процесс В Процесс С Время Шевченко А. В. Тема 1. Архитектура компьютера, адресация, представление данных 15

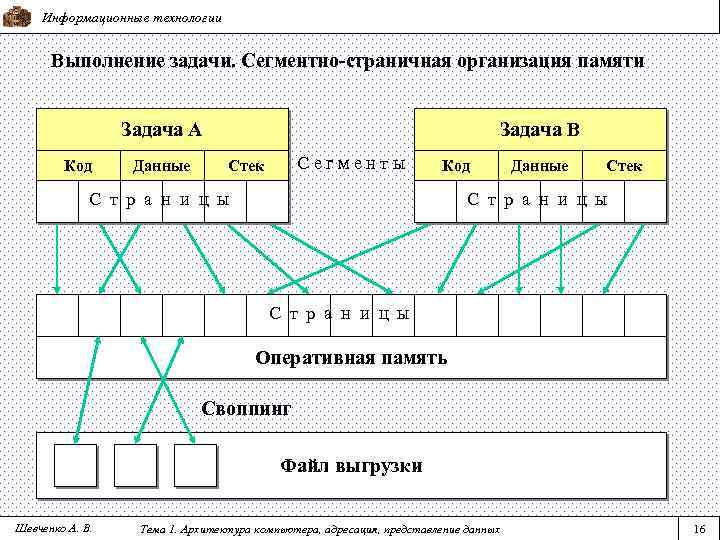

Информационные технологии Выполнение задачи. Сегментно-страничная организация памяти Задача А Код Данные Задача В Сегменты Стек Код С т р а н и ц ы Данные Стек С т р а н и ц ы Оперативная память Своппинг Файл выгрузки Шевченко А. В. Тема 1. Архитектура компьютера, адресация, представление данных 16

Информационные технологии Выполнение задачи. Сегментно-страничная организация памяти Задача А Код Данные Задача В Сегменты Стек Код С т р а н и ц ы Данные Стек С т р а н и ц ы Оперативная память Своппинг Файл выгрузки Шевченко А. В. Тема 1. Архитектура компьютера, адресация, представление данных 16

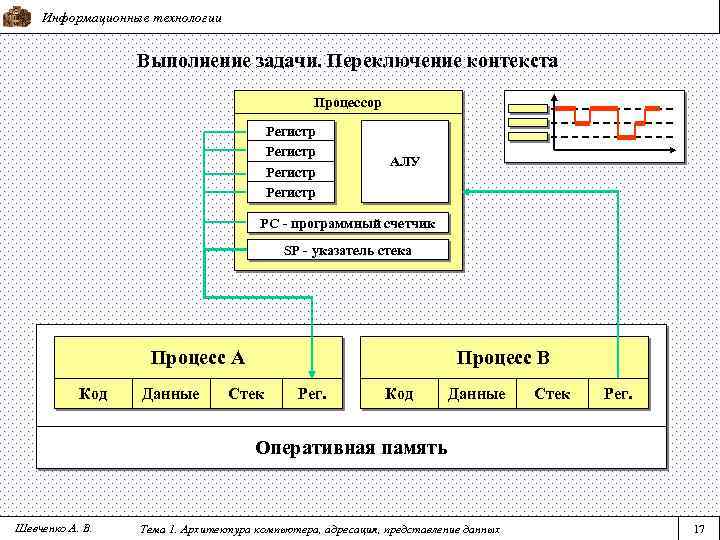

Информационные технологии Выполнение задачи. Переключение контекста Процессор Регистр АЛУ PC - программный счетчик SP - указатель стека Процесс А Код Данные Процесс В Стек Рег. Код Данные Стек Рег. Оперативная память Шевченко А. В. Тема 1. Архитектура компьютера, адресация, представление данных 17

Информационные технологии Выполнение задачи. Переключение контекста Процессор Регистр АЛУ PC - программный счетчик SP - указатель стека Процесс А Код Данные Процесс В Стек Рег. Код Данные Стек Рег. Оперативная память Шевченко А. В. Тема 1. Архитектура компьютера, адресация, представление данных 17

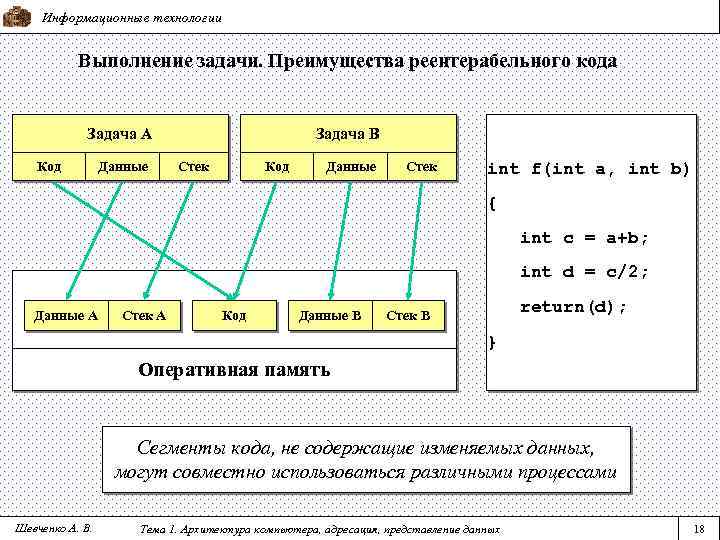

Информационные технологии Выполнение задачи. Преимущества реентерабельного кода Задача А Код Данные Задача В Стек Код Данные Стек int f(int a, int b) { int c = a+b; int d = c/2; Данные А Стек А Код Данные В return(d); Стек В } Оперативная память Сегменты кода, не содержащие изменяемых данных, могут совместно использоваться различными процессами Шевченко А. В. Тема 1. Архитектура компьютера, адресация, представление данных 18

Информационные технологии Выполнение задачи. Преимущества реентерабельного кода Задача А Код Данные Задача В Стек Код Данные Стек int f(int a, int b) { int c = a+b; int d = c/2; Данные А Стек А Код Данные В return(d); Стек В } Оперативная память Сегменты кода, не содержащие изменяемых данных, могут совместно использоваться различными процессами Шевченко А. В. Тема 1. Архитектура компьютера, адресация, представление данных 18