7faa883c6606fcb7c0373c4db21b454f.ppt

- Количество слайдов: 108

In Search of Silicon Consuming Technologies 2003. 10. 31 이 귀로 교수 krlee@ee. kaist. ac. kr Dept. of EECS, KAIST MICROS Research Center http: //micros. kaist. ac. kr 1

In Search of Silicon Consuming Technologies 2003. 10. 31 이 귀로 교수 krlee@ee. kaist. ac. kr Dept. of EECS, KAIST MICROS Research Center http: //micros. kaist. ac. kr 1

약력: ¨ 71 - 76: 서울 공대 전자과 ¨ 78 - 83: 미네소타 대학 전기공학 석박사 - HEMT에 대해 멋모르고 논문을 25편 정도 썼음 ¨ 83 - 86: ㈜ 금성반도체 MOS 기술부장 - 국내 처음으로 CMOS 사업 기획, 공장 건립, 공정개발 및 판매 경험 ¨ 87 -95: KAIST 전기 및 전자공학과 조, 부교수 - Atom 과 Bit 간 방황 ¨ 95 - 현재: 동 대학 정 교수 - 미세정보 시스템 연구센터 (KOSEF ERC) 소장 2

약력: ¨ 71 - 76: 서울 공대 전자과 ¨ 78 - 83: 미네소타 대학 전기공학 석박사 - HEMT에 대해 멋모르고 논문을 25편 정도 썼음 ¨ 83 - 86: ㈜ 금성반도체 MOS 기술부장 - 국내 처음으로 CMOS 사업 기획, 공장 건립, 공정개발 및 판매 경험 ¨ 87 -95: KAIST 전기 및 전자공학과 조, 부교수 - Atom 과 Bit 간 방황 ¨ 95 - 현재: 동 대학 정 교수 - 미세정보 시스템 연구센터 (KOSEF ERC) 소장 2

본인이 좋아하는 (어떤 이는 싫어하는) 격언: ¨ Do not re-invent the wheel. ¨ Whatever being invented was invented before. – 100 년 전 미국 특허청장 ¨ 진통제를 만들어라. 비타민은 좋다는 걸 알면서도 (안 먹 어도 되니까) 안 먹는다. - Ken Rhie ¨ 호기심을 충족하기 위한 연구는 이미 끝났다. 3

본인이 좋아하는 (어떤 이는 싫어하는) 격언: ¨ Do not re-invent the wheel. ¨ Whatever being invented was invented before. – 100 년 전 미국 특허청장 ¨ 진통제를 만들어라. 비타민은 좋다는 걸 알면서도 (안 먹 어도 되니까) 안 먹는다. - Ken Rhie ¨ 호기심을 충족하기 위한 연구는 이미 끝났다. 3

본인이 생각하는 인류의 걸작품 들 Atom의 세계 Bit(미디어)의 세계 ¨ 불 ¨ 시계 ¨ 문자 + 인쇄술 ¨ 화학 ¨ 반도체 + 집적 ¨ 엔진 + 일관 회로 작업 4

본인이 생각하는 인류의 걸작품 들 Atom의 세계 Bit(미디어)의 세계 ¨ 불 ¨ 시계 ¨ 문자 + 인쇄술 ¨ 화학 ¨ 반도체 + 집적 ¨ 엔진 + 일관 회로 작업 4

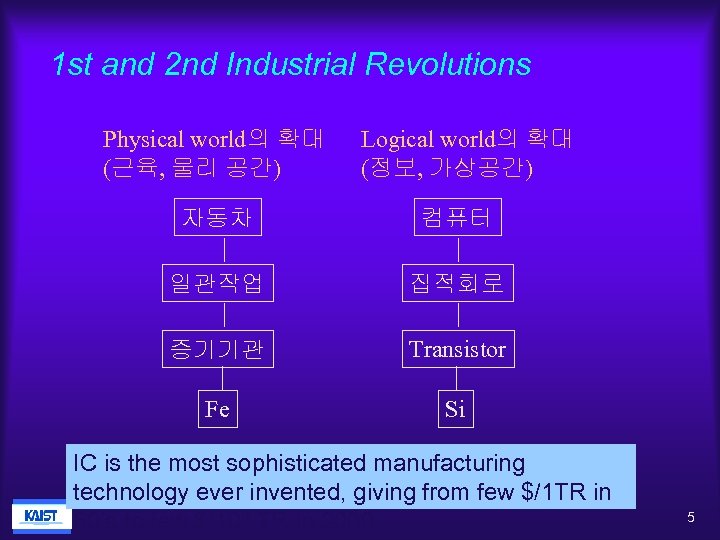

1 st and 2 nd Industrial Revolutions Physical world의 확대 (근육, 물리 공간) Logical world의 확대 (정보, 가상공간) 자동차 컴퓨터 일관작업 집적회로 증기기관 Transistor Fe Si IC is the most sophisticated manufacturing technology ever invented, giving from few $/1 TR in 60’s to few $/109 TR in 2000. 5

1 st and 2 nd Industrial Revolutions Physical world의 확대 (근육, 물리 공간) Logical world의 확대 (정보, 가상공간) 자동차 컴퓨터 일관작업 집적회로 증기기관 Transistor Fe Si IC is the most sophisticated manufacturing technology ever invented, giving from few $/1 TR in 60’s to few $/109 TR in 2000. 5

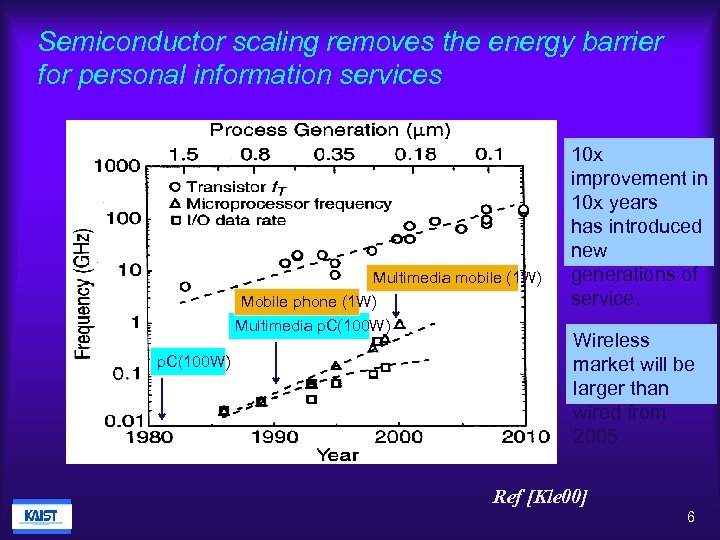

Semiconductor scaling removes the energy barrier for personal information services Multimedia mobile (1 W) Mobile phone (1 W) Multimedia p. C(100 W) 10 x improvement in 10 x years has introduced new generations of service. Wireless market will be larger than wired from 2005. Ref [Kle 00] 6

Semiconductor scaling removes the energy barrier for personal information services Multimedia mobile (1 W) Mobile phone (1 W) Multimedia p. C(100 W) 10 x improvement in 10 x years has introduced new generations of service. Wireless market will be larger than wired from 2005. Ref [Kle 00] 6

Two ways to create new market. ¨ 새로운 기술을 개발한 후 응용을 찾는 방법 – – Bottom-up approach Technology push Claimed to be revolutionary But 비타민 연구에 그치기 쉬움 ¨ 새로운 시장의 요구를 파악하고 필요기술을 개발 – – Top-down approach Market pull Maybe evolutionary But 진통제인 경우가 많음 7

Two ways to create new market. ¨ 새로운 기술을 개발한 후 응용을 찾는 방법 – – Bottom-up approach Technology push Claimed to be revolutionary But 비타민 연구에 그치기 쉬움 ¨ 새로운 시장의 요구를 파악하고 필요기술을 개발 – – Top-down approach Market pull Maybe evolutionary But 진통제인 경우가 많음 7

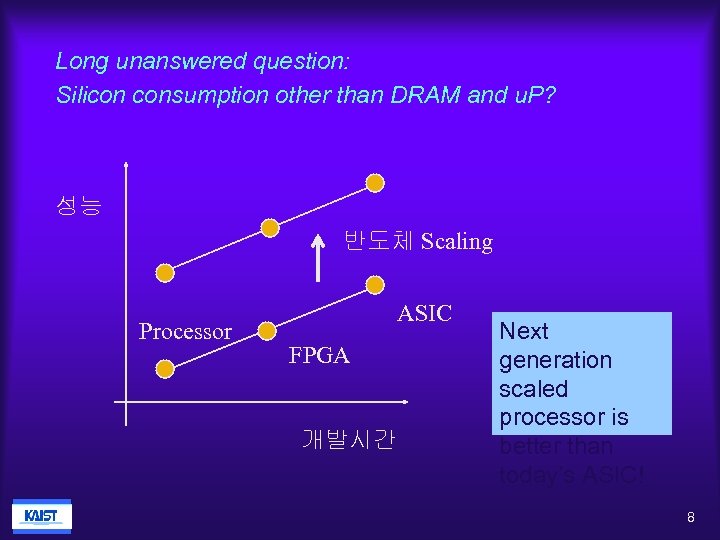

Long unanswered question: Silicon consumption other than DRAM and u. P? 성능 반도체 Scaling Processor ASIC FPGA 개발시간 Next generation scaled processor is better than today’s ASIC! 8

Long unanswered question: Silicon consumption other than DRAM and u. P? 성능 반도체 Scaling Processor ASIC FPGA 개발시간 Next generation scaled processor is better than today’s ASIC! 8

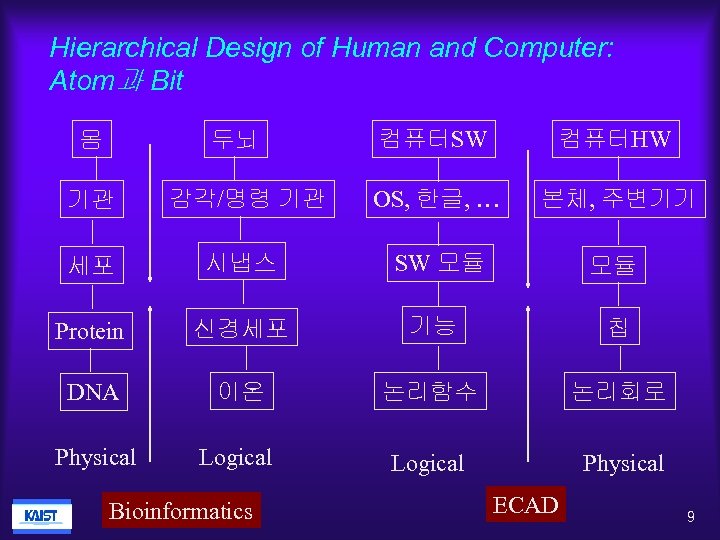

Hierarchical Design of Human and Computer: Atom과 Bit 몸 두뇌 컴퓨터SW 컴퓨터HW 기관 감각/명령 기관 OS, 한글, … 본체, 주변기기 세포 시냅스 SW 모듈 모듈 Protein 신경세포 기능 칩 DNA 이온 논리함수 논리회로 Physical Logical Physical Bioinformatics ECAD 9

Hierarchical Design of Human and Computer: Atom과 Bit 몸 두뇌 컴퓨터SW 컴퓨터HW 기관 감각/명령 기관 OS, 한글, … 본체, 주변기기 세포 시냅스 SW 모듈 모듈 Protein 신경세포 기능 칩 DNA 이온 논리함수 논리회로 Physical Logical Physical Bioinformatics ECAD 9

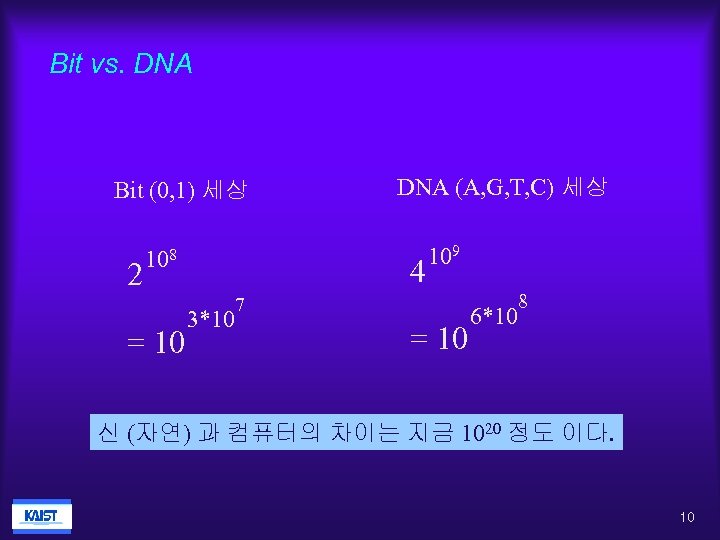

Bit vs. DNA Bit (0, 1) 세상 2 108 DNA (A, G, T, C) 세상 4 109 8 7 = 10 3*10 = 10 6*10 신 (자연) 과 컴퓨터의 차이는 지금 1020 정도 이다. 10

Bit vs. DNA Bit (0, 1) 세상 2 108 DNA (A, G, T, C) 세상 4 109 8 7 = 10 3*10 = 10 6*10 신 (자연) 과 컴퓨터의 차이는 지금 1020 정도 이다. 10

In search of silicon consuming technology -1 Non-Volatile Analog Memory (NVAM) for Artificial Neural Network (ANN) 11

In search of silicon consuming technology -1 Non-Volatile Analog Memory (NVAM) for Artificial Neural Network (ANN) 11

NVAM for ANN ¨ Current computer system is based on von-Neuman ¨ ¨ ¨ architecture composed of u. P and memory. It is sequential and only efficient in computation, terrible in association/recognition. Human logical (nerve and brain) system is highly parallel and very efficient in association/recognition. Artificial neural network draw much attention because it resembles human logical system with self-learning capability. It is composed of neuron and synapse. It is connection oriented and thus efficient realization of synapse is more important than neuron. 12

NVAM for ANN ¨ Current computer system is based on von-Neuman ¨ ¨ ¨ architecture composed of u. P and memory. It is sequential and only efficient in computation, terrible in association/recognition. Human logical (nerve and brain) system is highly parallel and very efficient in association/recognition. Artificial neural network draw much attention because it resembles human logical system with self-learning capability. It is composed of neuron and synapse. It is connection oriented and thus efficient realization of synapse is more important than neuron. 12

¨ An artificial neural network, resembling human brain, provides highly parallel signal processing operation, suitable for various pattern recognition. ¨ In ANN, knowledge is stored within inter-neuron connection strengths known as synaptic weights. ¨ A neural network acquires knowledge through learning in a self-consistent way, whose algorithm is relatively much simpler than others. 13

¨ An artificial neural network, resembling human brain, provides highly parallel signal processing operation, suitable for various pattern recognition. ¨ In ANN, knowledge is stored within inter-neuron connection strengths known as synaptic weights. ¨ A neural network acquires knowledge through learning in a self-consistent way, whose algorithm is relatively much simpler than others. 13

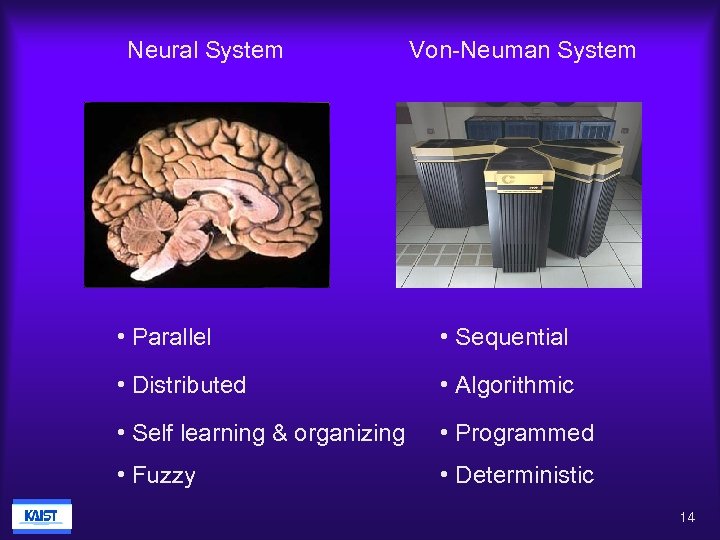

Neural System Von-Neuman System • Parallel • Sequential • Distributed • Algorithmic • Self learning & organizing • Programmed • Fuzzy • Deterministic 14

Neural System Von-Neuman System • Parallel • Sequential • Distributed • Algorithmic • Self learning & organizing • Programmed • Fuzzy • Deterministic 14

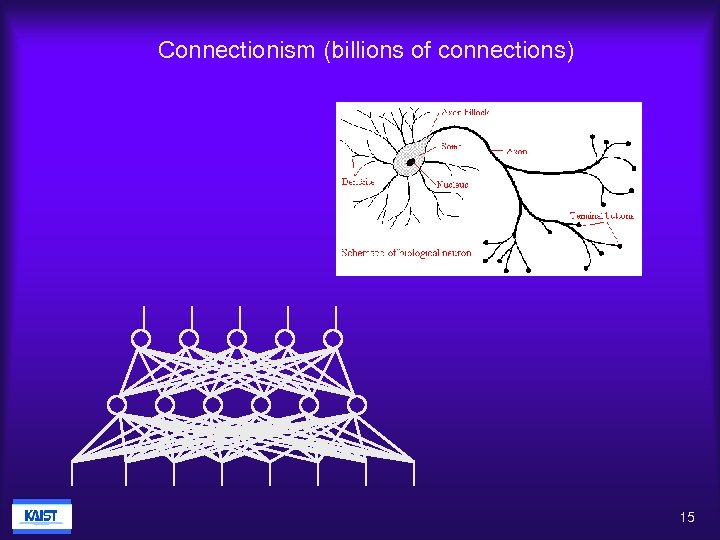

Connectionism (billions of connections) 15

Connectionism (billions of connections) 15

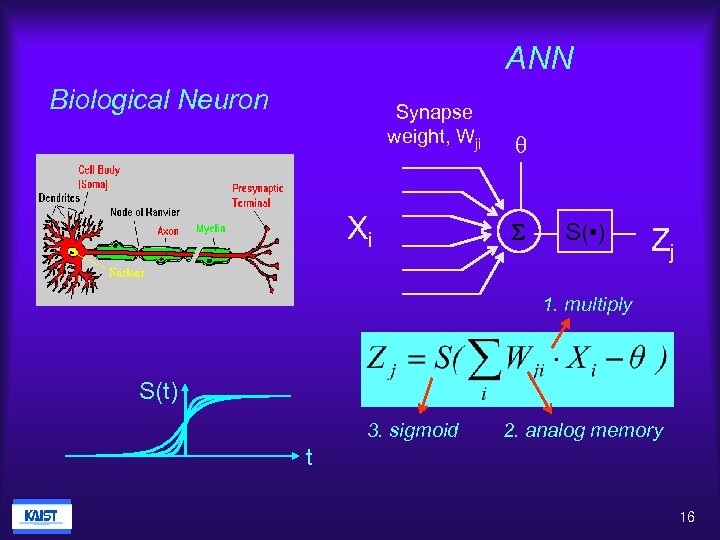

ANN Biological Neuron Synapse weight, Wji Xi q S S( • ) Zj 1. multiply S(t) 3. sigmoid 2. analog memory t 16

ANN Biological Neuron Synapse weight, Wji Xi q S S( • ) Zj 1. multiply S(t) 3. sigmoid 2. analog memory t 16

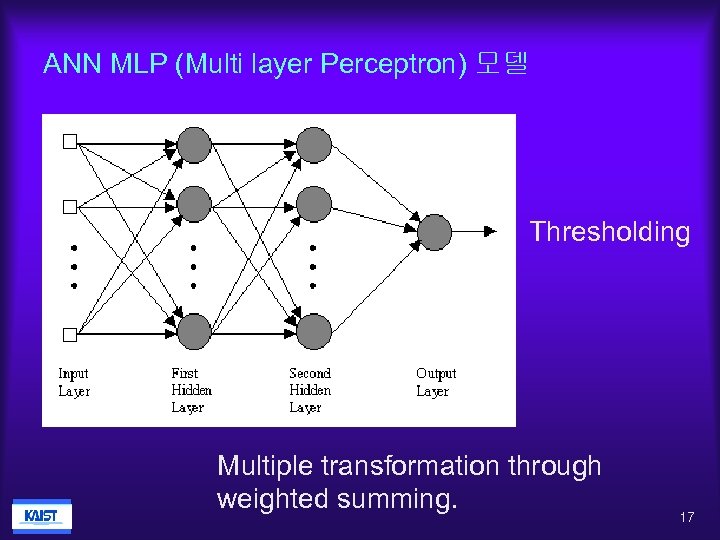

ANN MLP (Multi layer Perceptron) 모델 Thresholding Multiple transformation through weighted summing. 17

ANN MLP (Multi layer Perceptron) 모델 Thresholding Multiple transformation through weighted summing. 17

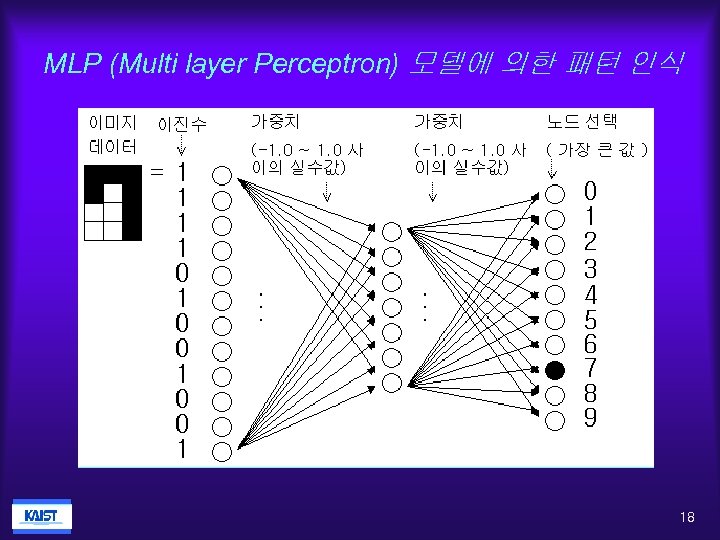

MLP (Multi layer Perceptron) 모델에 의한 패턴 인식 18

MLP (Multi layer Perceptron) 모델에 의한 패턴 인식 18

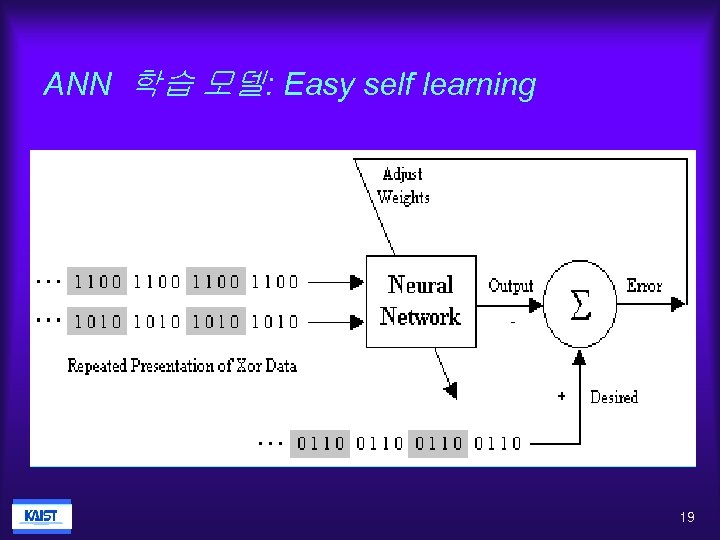

ANN 학습 모델: Easy self learning 19

ANN 학습 모델: Easy self learning 19

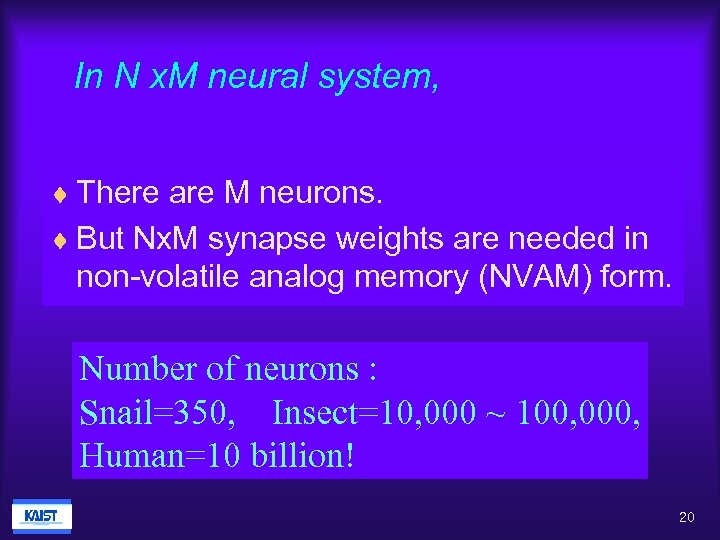

In N x. M neural system, ¨ There are M neurons. ¨ But Nx. M synapse weights are needed in non-volatile analog memory (NVAM) form. Number of neurons : Snail=350, Insect=10, 000 ~ 100, 000, Human=10 billion! 20

In N x. M neural system, ¨ There are M neurons. ¨ But Nx. M synapse weights are needed in non-volatile analog memory (NVAM) form. Number of neurons : Snail=350, Insect=10, 000 ~ 100, 000, Human=10 billion! 20

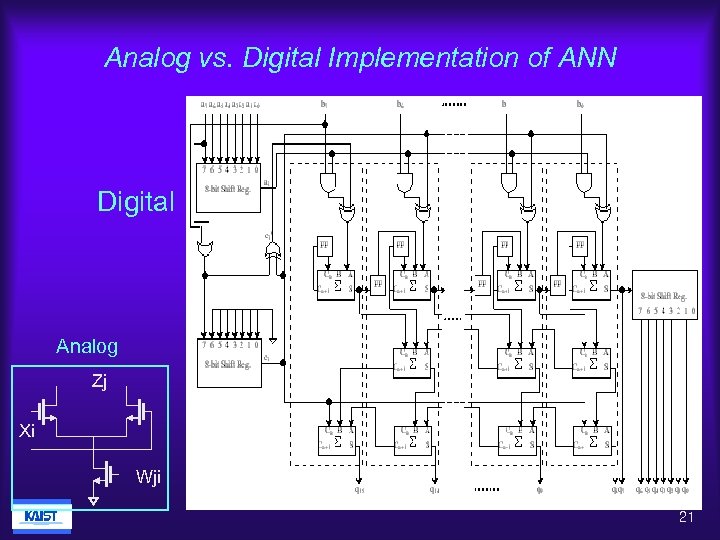

Analog vs. Digital Implementation of ANN Digital Analog Zj Xi Wji 21

Analog vs. Digital Implementation of ANN Digital Analog Zj Xi Wji 21

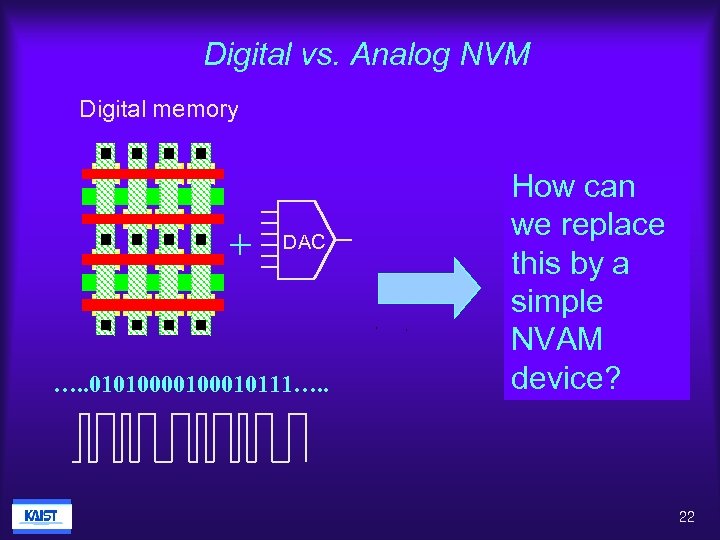

Digital vs. Analog NVM Digital memory + DAC …. . 010100010111…. . How can we replace this by a simple NVAM device? 22

Digital vs. Analog NVM Digital memory + DAC …. . 010100010111…. . How can we replace this by a simple NVAM device? 22

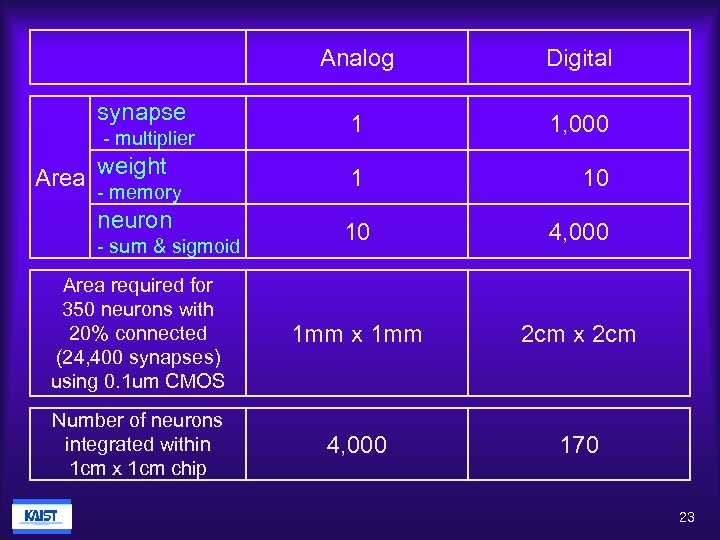

Analog Digital 1 1, 000 Area weight 1 10 neuron 10 4, 000 Area required for 350 neurons with 20% connected (24, 400 synapses) using 0. 1 um CMOS 1 mm x 1 mm 2 cm x 2 cm Number of neurons integrated within 1 cm x 1 cm chip 4, 000 170 synapse - multiplier - memory - sum & sigmoid 23

Analog Digital 1 1, 000 Area weight 1 10 neuron 10 4, 000 Area required for 350 neurons with 20% connected (24, 400 synapses) using 0. 1 um CMOS 1 mm x 1 mm 2 cm x 2 cm Number of neurons integrated within 1 cm x 1 cm chip 4, 000 170 synapse - multiplier - memory - sum & sigmoid 23

Technology options for NVM - Ferroelectric memory - EEPROM using tunneling ……. . 24

Technology options for NVM - Ferroelectric memory - EEPROM using tunneling ……. . 24

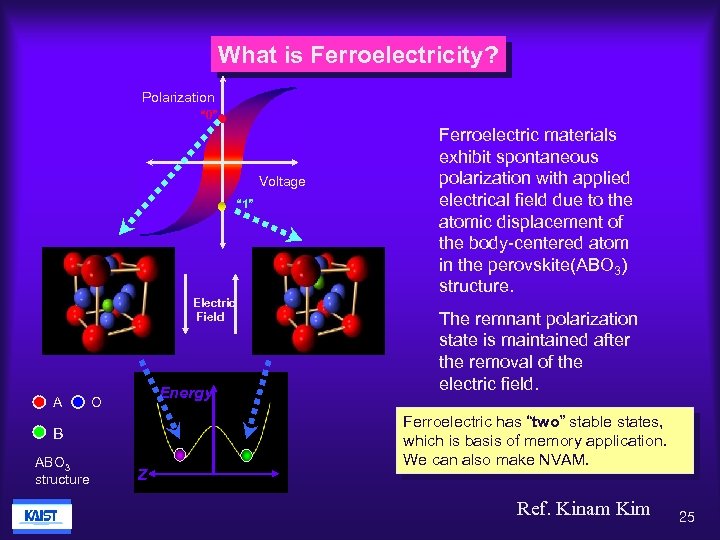

What is Ferroelectricity? Polarization “ 0” Voltage “ 1” Electric Field A Energy O B ABO 3 structure Z Ferroelectric materials exhibit spontaneous polarization with applied electrical field due to the atomic displacement of the body-centered atom in the perovskite(ABO 3) structure. The remnant polarization state is maintained after the removal of the electric field. Ferroelectric has “two” stable states, which is basis of memory application. We can also make NVAM. Ref. Kinam Kim 25

What is Ferroelectricity? Polarization “ 0” Voltage “ 1” Electric Field A Energy O B ABO 3 structure Z Ferroelectric materials exhibit spontaneous polarization with applied electrical field due to the atomic displacement of the body-centered atom in the perovskite(ABO 3) structure. The remnant polarization state is maintained after the removal of the electric field. Ferroelectric has “two” stable states, which is basis of memory application. We can also make NVAM. Ref. Kinam Kim 25

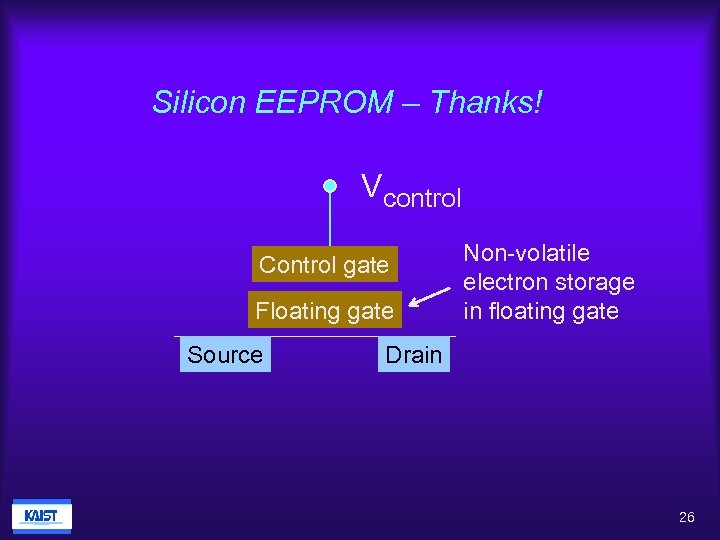

Silicon EEPROM – Thanks! Vcontrol Control gate Floating gate Source Non-volatile electron storage in floating gate Drain 26

Silicon EEPROM – Thanks! Vcontrol Control gate Floating gate Source Non-volatile electron storage in floating gate Drain 26

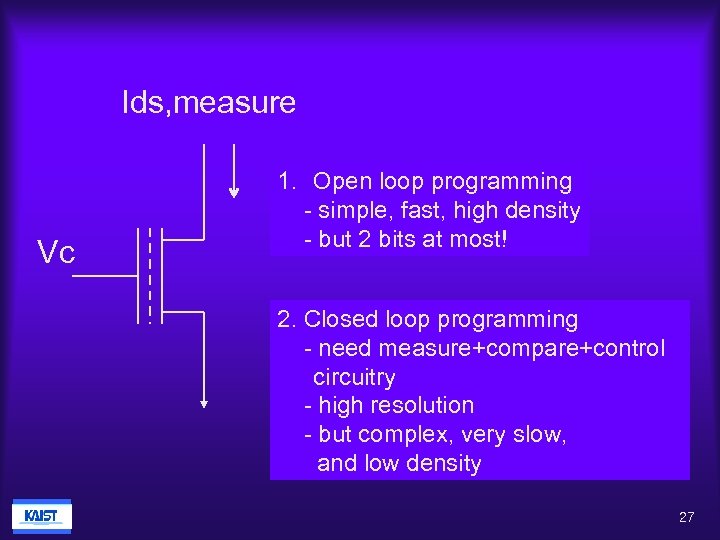

Ids, measure Vc 1. Open loop programming - simple, fast, high density - but 2 bits at most! 2. Closed loop programming - need measure+compare+control circuitry - high resolution - but complex, very slow, and low density 27

Ids, measure Vc 1. Open loop programming - simple, fast, high density - but 2 bits at most! 2. Closed loop programming - need measure+compare+control circuitry - high resolution - but complex, very slow, and low density 27

Homework #1: Vin NVAM Invent a small silicon NVAM device, Vout where Vin can be stored in self-consistent way!!! 28

Homework #1: Vin NVAM Invent a small silicon NVAM device, Vout where Vin can be stored in self-consistent way!!! 28

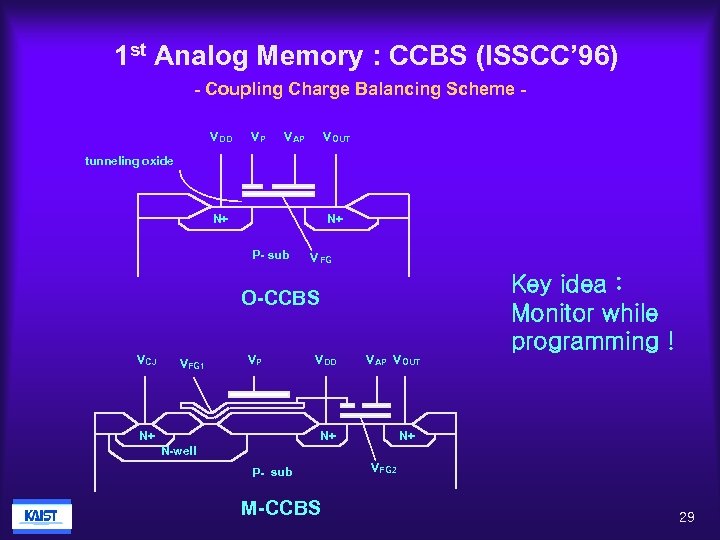

1 st Analog Memory : CCBS (ISSCC’ 96) - Coupling Charge Balancing Scheme V DD VP V AP V OUT tunneling oxide N+ N+ P- sub V FG Key idea : Monitor while programming ! O-CCBS VCJ VFG 1 VP N+ V DD V AP VOUT N+ N+ N-well P- sub M-CCBS VFG 2 29

1 st Analog Memory : CCBS (ISSCC’ 96) - Coupling Charge Balancing Scheme V DD VP V AP V OUT tunneling oxide N+ N+ P- sub V FG Key idea : Monitor while programming ! O-CCBS VCJ VFG 1 VP N+ V DD V AP VOUT N+ N+ N-well P- sub M-CCBS VFG 2 29

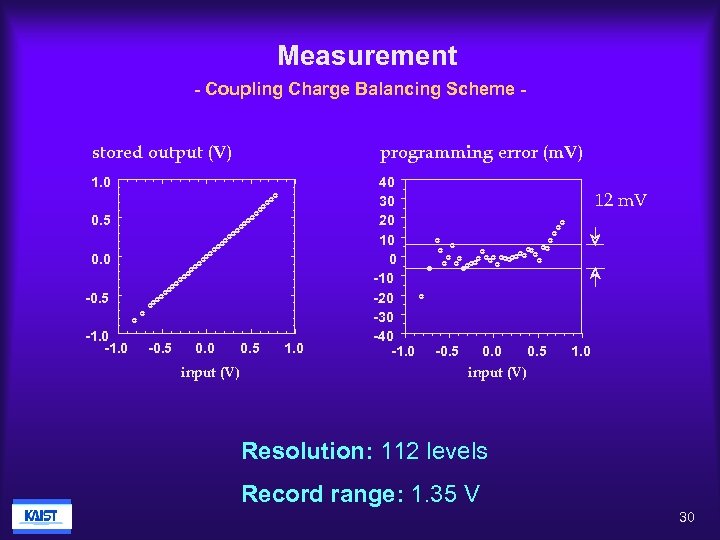

Measurement - Coupling Charge Balancing Scheme stored output (V) programming error (m. V) 1. 0 0. 5 0. 0 -0. 5 -1. 0 -0. 5 0. 0 input (V) 0. 5 1. 0 40 30 20 10 0 -10 -20 -30 -40 -1. 0 12 m. V -0. 5 0. 0 0. 5 input (V) 1. 0 Resolution: 112 levels Record range: 1. 35 V 30

Measurement - Coupling Charge Balancing Scheme stored output (V) programming error (m. V) 1. 0 0. 5 0. 0 -0. 5 -1. 0 -0. 5 0. 0 input (V) 0. 5 1. 0 40 30 20 10 0 -10 -20 -30 -40 -1. 0 12 m. V -0. 5 0. 0 0. 5 input (V) 1. 0 Resolution: 112 levels Record range: 1. 35 V 30

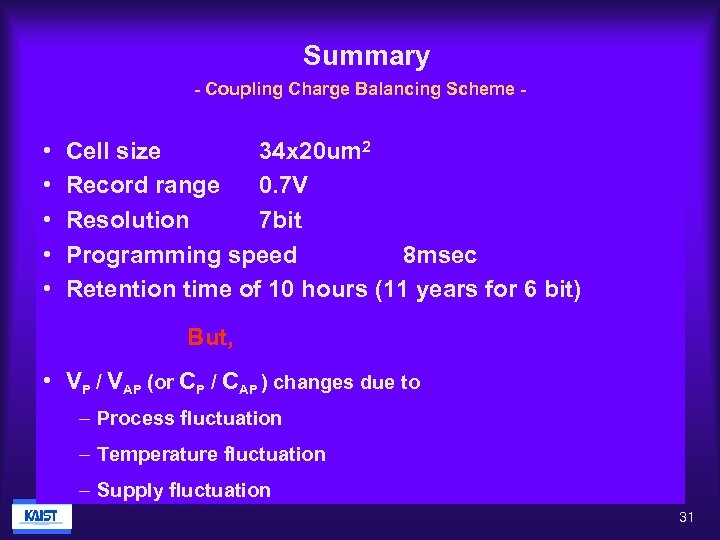

Summary - Coupling Charge Balancing Scheme - • • • Cell size 34 x 20 um 2 Record range 0. 7 V Resolution 7 bit Programming speed 8 msec Retention time of 10 hours (11 years for 6 bit) But, • VP / VAP (or CP / CAP ) changes due to – Process fluctuation – Temperature fluctuation – Supply fluctuation 31

Summary - Coupling Charge Balancing Scheme - • • • Cell size 34 x 20 um 2 Record range 0. 7 V Resolution 7 bit Programming speed 8 msec Retention time of 10 hours (11 years for 6 bit) But, • VP / VAP (or CP / CAP ) changes due to – Process fluctuation – Temperature fluctuation – Supply fluctuation 31

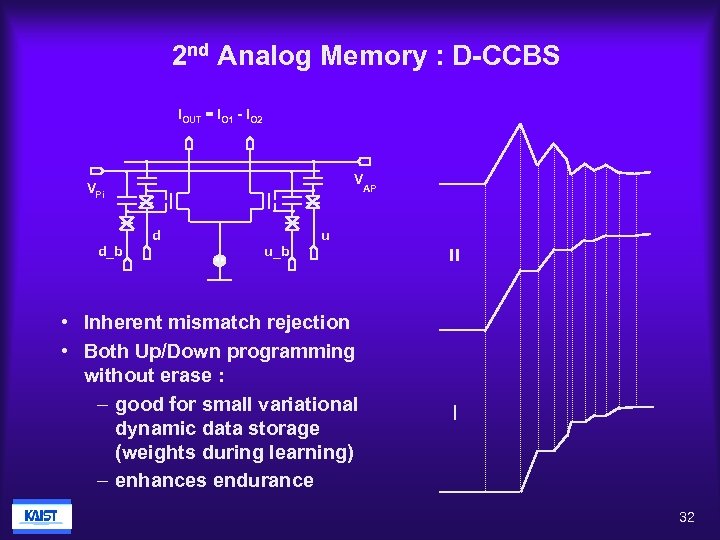

2 nd Analog Memory : D-CCBS IOUT = IO 1 - IO 2 V VPi AP d_b u u_b = d • Inherent mismatch rejection • Both Up/Down programming without erase : – good for small variational dynamic data storage (weights during learning) – enhances endurance 32

2 nd Analog Memory : D-CCBS IOUT = IO 1 - IO 2 V VPi AP d_b u u_b = d • Inherent mismatch rejection • Both Up/Down programming without erase : – good for small variational dynamic data storage (weights during learning) – enhances endurance 32

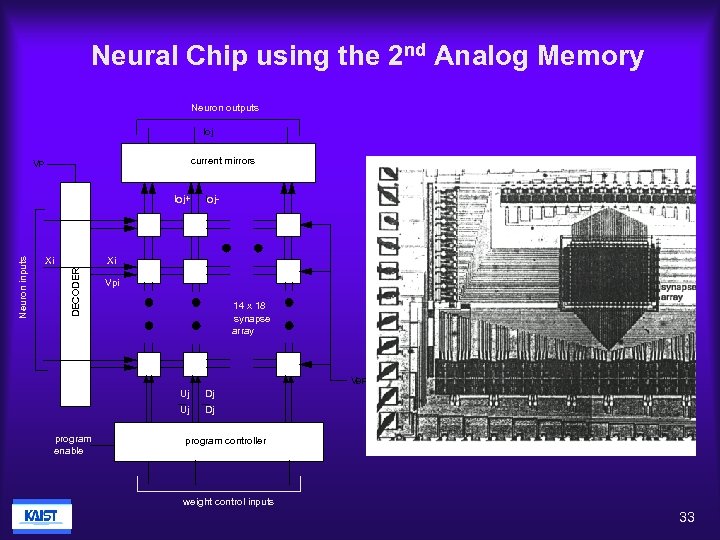

Neural Chip using the 2 nd Analog Memory Neuron outputs Ioj current mirrors VP Xi IO j- Xi DECODER Neuron inputs IO j+ Vpi 14 x 18 synapse array VBP Uj Uj program enable Dj Dj program controller weight control inputs 33

Neural Chip using the 2 nd Analog Memory Neuron outputs Ioj current mirrors VP Xi IO j- Xi DECODER Neuron inputs IO j+ Vpi 14 x 18 synapse array VBP Uj Uj program enable Dj Dj program controller weight control inputs 33

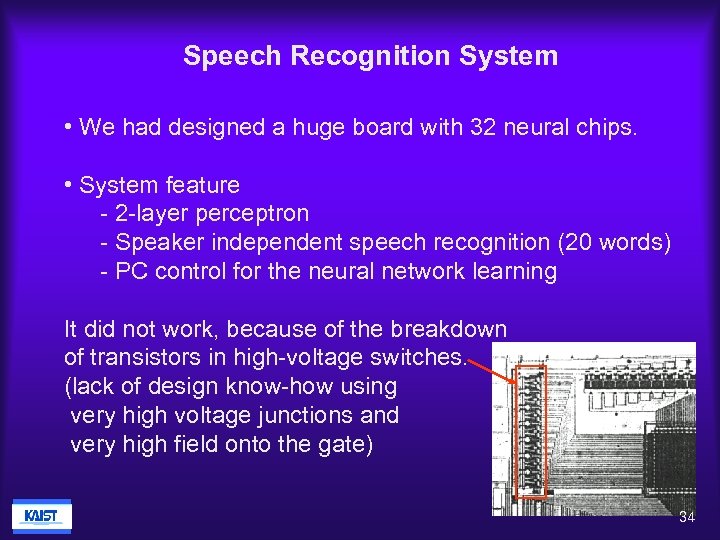

Speech Recognition System • We had designed a huge board with 32 neural chips. • System feature - 2 -layer perceptron - Speaker independent speech recognition (20 words) - PC control for the neural network learning It did not work, because of the breakdown of transistors in high-voltage switches. (lack of design know-how using very high voltage junctions and very high field onto the gate) 34

Speech Recognition System • We had designed a huge board with 32 neural chips. • System feature - 2 -layer perceptron - Speaker independent speech recognition (20 words) - PC control for the neural network learning It did not work, because of the breakdown of transistors in high-voltage switches. (lack of design know-how using very high voltage junctions and very high field onto the gate) 34

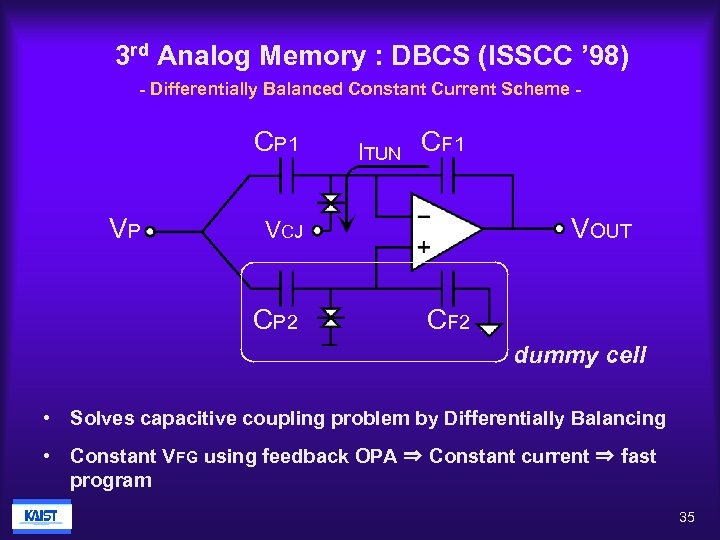

3 rd Analog Memory : DBCS (ISSCC ’ 98) - Differentially Balanced Constant Current Scheme - CP 1 VP ITUN CF 1 VOUT VCJ CP 2 CF 2 dummy cell • Solves capacitive coupling problem by Differentially Balancing • Constant VFG using feedback OPA ⇒ Constant current ⇒ fast program 35

3 rd Analog Memory : DBCS (ISSCC ’ 98) - Differentially Balanced Constant Current Scheme - CP 1 VP ITUN CF 1 VOUT VCJ CP 2 CF 2 dummy cell • Solves capacitive coupling problem by Differentially Balancing • Constant VFG using feedback OPA ⇒ Constant current ⇒ fast program 35

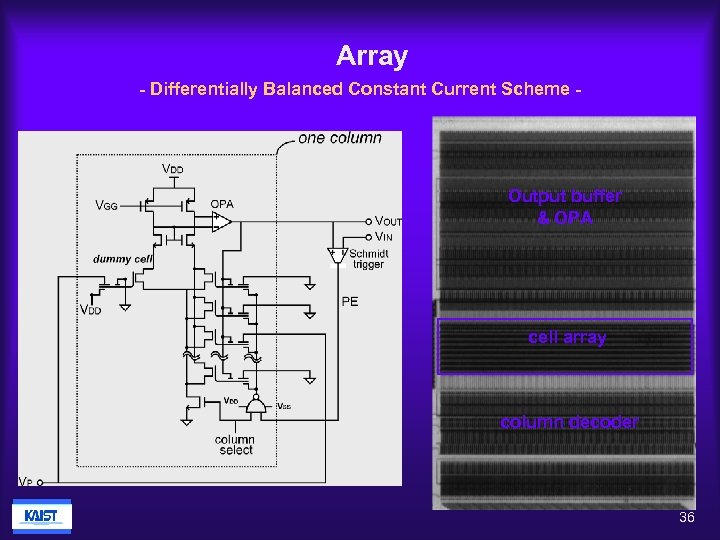

Array - Differentially Balanced Constant Current Scheme - Output buffer & OPA cell array column decoder 36

Array - Differentially Balanced Constant Current Scheme - Output buffer & OPA cell array column decoder 36

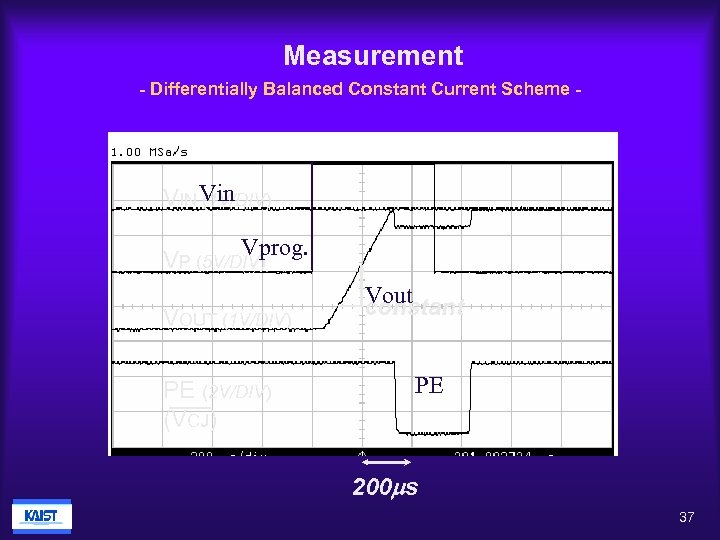

Measurement - Differentially Balanced Constant Current Scheme - VIN Vin (1 V/DIV) Vprog. VP (5 V/DIV) VOUT (1 V/DIV) PE (2 V/DIV) (VCJ) Vout constant PE 200 ms 37

Measurement - Differentially Balanced Constant Current Scheme - VIN Vin (1 V/DIV) Vprog. VP (5 V/DIV) VOUT (1 V/DIV) PE (2 V/DIV) (VCJ) Vout constant PE 200 ms 37

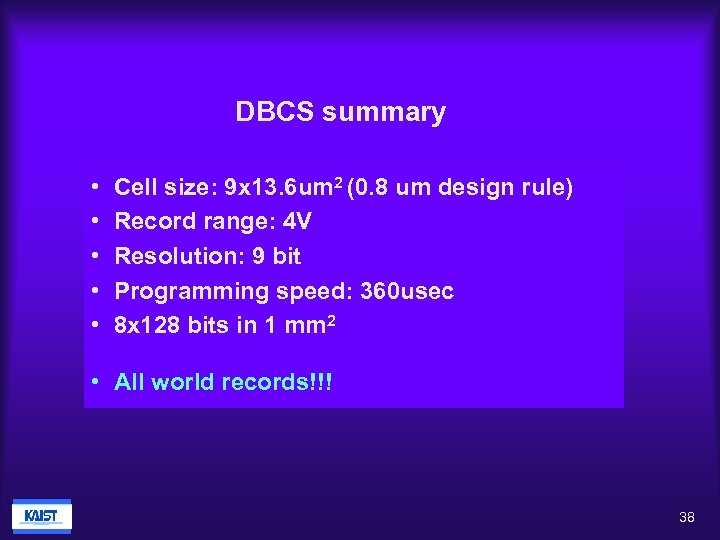

DBCS summary • • • Cell size: 9 x 13. 6 um 2 (0. 8 um design rule) Record range: 4 V Resolution: 9 bit Programming speed: 360 usec 8 x 128 bits in 1 mm 2 • All world records!!! 38

DBCS summary • • • Cell size: 9 x 13. 6 um 2 (0. 8 um design rule) Record range: 4 V Resolution: 9 bit Programming speed: 360 usec 8 x 128 bits in 1 mm 2 • All world records!!! 38

In search of silicon consuming technology – 1: Conclusion ¨ Nonvolatile analog memory is needed for synapse. ¨ Very efficient NVAM were invented using IC technology ¨ ¨ ¨ with world recognition. Tried to develop voice recognition board using VLSI with millions of NVAM’s. Found it is not compatible with current computer system. This research was given up. Concluded it as a typical VITAMIN research. Nowadays this is easily done in scaled DSP, although this is not an efficient architecture. Both physical and logical compatibility and reliability shoul rigorously be proved before having people to try new VITA 39

In search of silicon consuming technology – 1: Conclusion ¨ Nonvolatile analog memory is needed for synapse. ¨ Very efficient NVAM were invented using IC technology ¨ ¨ ¨ with world recognition. Tried to develop voice recognition board using VLSI with millions of NVAM’s. Found it is not compatible with current computer system. This research was given up. Concluded it as a typical VITAMIN research. Nowadays this is easily done in scaled DSP, although this is not an efficient architecture. Both physical and logical compatibility and reliability shoul rigorously be proved before having people to try new VITA 39

Why Digital? 1) Precise signal processing: 6 d. B/bit and ppm accuracy of XO 2) Decision (If then else) 3) Programmability, Configurability 4) Reconfigurability, Learning, Self reproduction 40

Why Digital? 1) Precise signal processing: 6 d. B/bit and ppm accuracy of XO 2) Decision (If then else) 3) Programmability, Configurability 4) Reconfigurability, Learning, Self reproduction 40

Why Software? ¨ Fast configuring of digital signal processing system ¨ Human interfacing algorithm ¨ Sophisticated reconfiguring algorithm and reconfiguration ¨ Learning algorithm 41

Why Software? ¨ Fast configuring of digital signal processing system ¨ Human interfacing algorithm ¨ Sophisticated reconfiguring algorithm and reconfiguration ¨ Learning algorithm 41

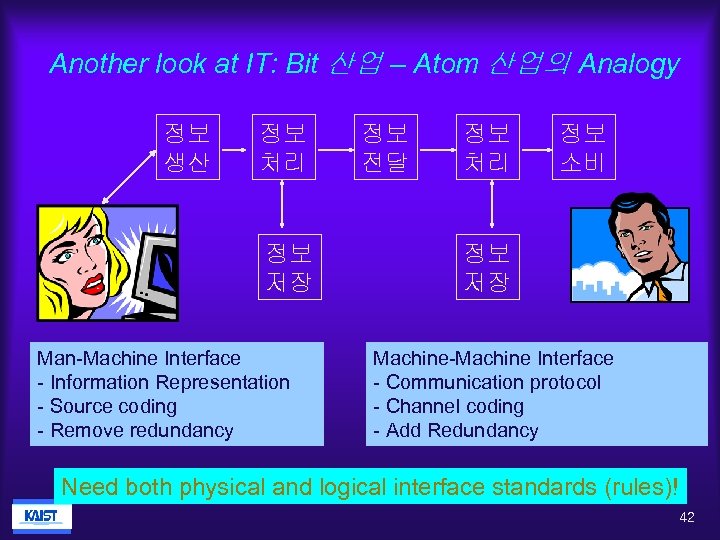

Another look at IT: Bit 산업 – Atom 산업의 Analogy 정보 생산 정보 처리 정보 저장 Man-Machine Interface - Information Representation - Source coding - Remove redundancy 정보 전달 정보 처리 정보 소비 정보 저장 Machine-Machine Interface - Communication protocol - Channel coding - Add Redundancy Need both physical and logical interface standards (rules)! 42

Another look at IT: Bit 산업 – Atom 산업의 Analogy 정보 생산 정보 처리 정보 저장 Man-Machine Interface - Information Representation - Source coding - Remove redundancy 정보 전달 정보 처리 정보 소비 정보 저장 Machine-Machine Interface - Communication protocol - Channel coding - Add Redundancy Need both physical and logical interface standards (rules)! 42

In search of silicon consuming technology – 2: The inception of MICROS ¨ The current logical world is composed of human and ¨ ¨ ¨ computer. The current physical world is composed of human and other creatures. So let us have other creatures to be involved into our logical world. The current macroscopic IT world is composed of computers connected by internet through information super highway. So let us think about silicon microscopic IT world!!! Hope this be the OASIS! 43

In search of silicon consuming technology – 2: The inception of MICROS ¨ The current logical world is composed of human and ¨ ¨ ¨ computer. The current physical world is composed of human and other creatures. So let us have other creatures to be involved into our logical world. The current macroscopic IT world is composed of computers connected by internet through information super highway. So let us think about silicon microscopic IT world!!! Hope this be the OASIS! 43

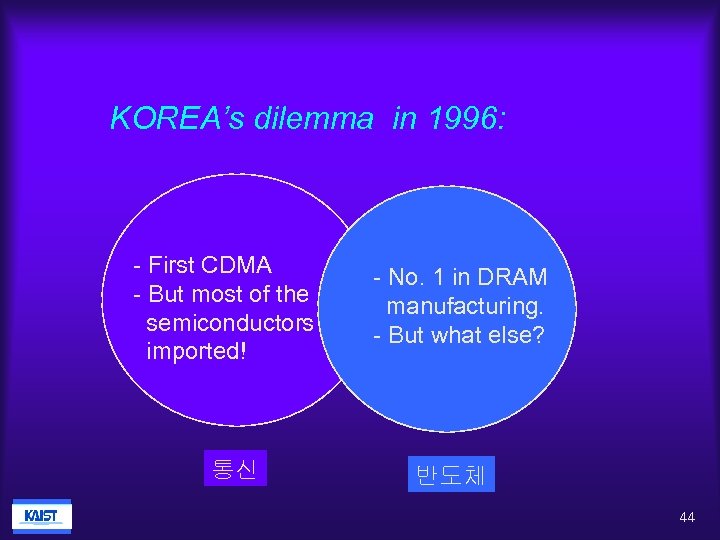

KOREA’s dilemma in 1996: - First CDMA - But most of the semiconductors imported! 통신 - No. 1 in DRAM manufacturing. - But what else? 반도체 44

KOREA’s dilemma in 1996: - First CDMA - But most of the semiconductors imported! 통신 - No. 1 in DRAM manufacturing. - But what else? 반도체 44

Single Chip Radio Vision: MICROS ü MICROS Research Center: Micro Information and Communication Remote Object-oriented System ü Established in 1997 and supported by KOSEF ü To Develop Programmable, Adaptive, Wearable, Coin-sized Wireless Terminal with Extremely Low Power Consumption for Distributed System such as Sensor Networks ¨ MICROS : Micro Information Communication Remote Object- oriented Systems ¨ KOSEF : KOrea Science and Engineering Foundation 45

Single Chip Radio Vision: MICROS ü MICROS Research Center: Micro Information and Communication Remote Object-oriented System ü Established in 1997 and supported by KOSEF ü To Develop Programmable, Adaptive, Wearable, Coin-sized Wireless Terminal with Extremely Low Power Consumption for Distributed System such as Sensor Networks ¨ MICROS : Micro Information Communication Remote Object- oriented Systems ¨ KOSEF : KOrea Science and Engineering Foundation 45

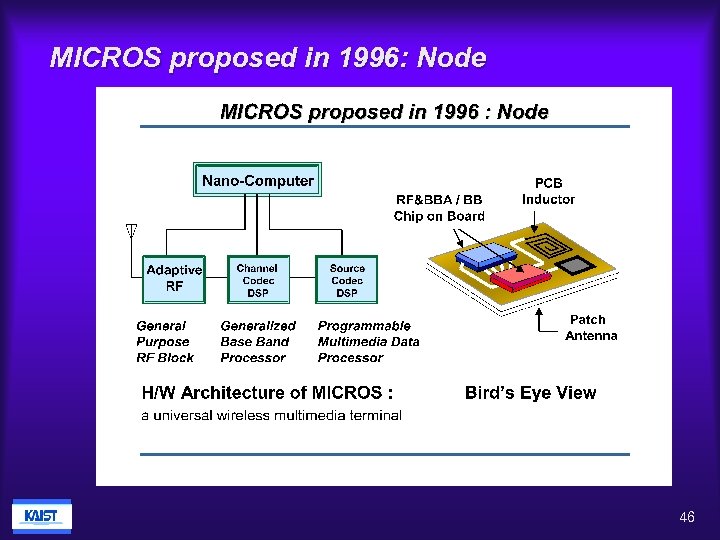

MICROS proposed in 1996: Node 46

MICROS proposed in 1996: Node 46

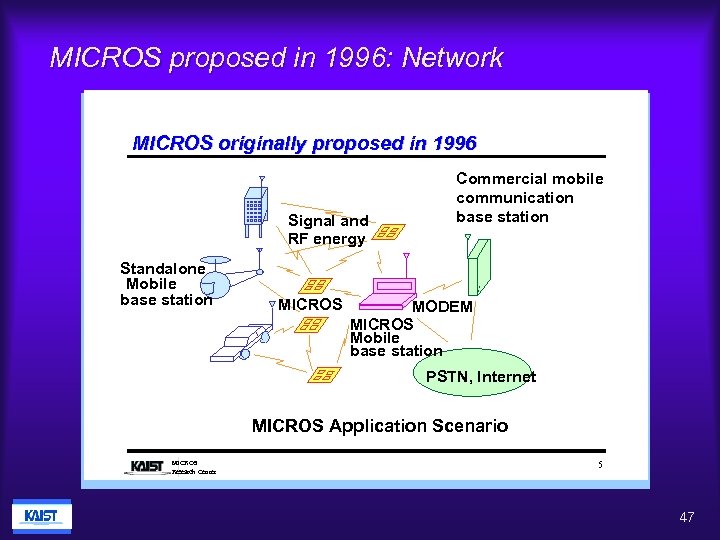

MICROS proposed in 1996: Network MICROS originally proposed in 1996 Signal and RF energy Standalone Mobile base station MICROS Commercial mobile communication base station MODEM MICROS Mobile base station PSTN, Internet MICROS Application Scenario MICROS Research Center 5 47

MICROS proposed in 1996: Network MICROS originally proposed in 1996 Signal and RF energy Standalone Mobile base station MICROS Commercial mobile communication base station MODEM MICROS Mobile base station PSTN, Internet MICROS Application Scenario MICROS Research Center 5 47

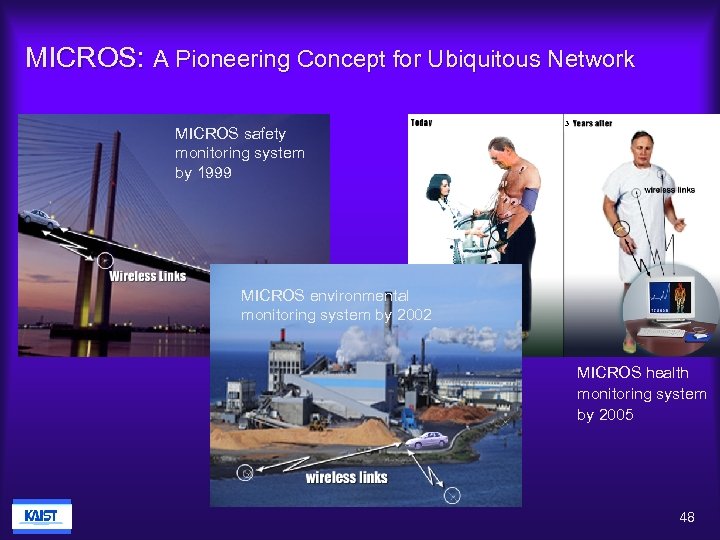

MICROS: A Pioneering Concept for Ubiquitous Network MICROS safety monitoring system by 1999 3 MICROS environmental monitoring system by 2002 MICROS health monitoring system by 2005 48

MICROS: A Pioneering Concept for Ubiquitous Network MICROS safety monitoring system by 1999 3 MICROS environmental monitoring system by 2002 MICROS health monitoring system by 2005 48

1 단계 (1999)현장 평가 결과 요약 ¨ 최종 목표의 타당성 결여 ¨ 선진국의 기술 현황 분석 부족 ¨ 연구 성과의 파급효과가 아직은 크지 않음 ¨ 국제 협력 미진 ¨ 산학 협력 아직 미진 – 산업체의 기술 수요 파악 및 반영 미흡 ¨ 산학 연구 결과의 파급효과 ¨ 단독과제의 목표 지향력이 필요하고 총괄과제와의 관 련성이 커져야 함 49

1 단계 (1999)현장 평가 결과 요약 ¨ 최종 목표의 타당성 결여 ¨ 선진국의 기술 현황 분석 부족 ¨ 연구 성과의 파급효과가 아직은 크지 않음 ¨ 국제 협력 미진 ¨ 산학 협력 아직 미진 – 산업체의 기술 수요 파악 및 반영 미흡 ¨ 산학 연구 결과의 파급효과 ¨ 단독과제의 목표 지향력이 필요하고 총괄과제와의 관 련성이 커져야 함 49

History of WPAN ¨ Bluetooth : Started feasibility study in 1994 inside Ericsson and SIG formed in 1998 ¨ PAN : Proposed in 1995 in MIT ¨ MICROS : Proposed in 1996 in KAIST ¨ Pico Radio : Proposed in 1999 in Berkeley ¨ IEEE 802. 15 Standards : started in 2000 50

History of WPAN ¨ Bluetooth : Started feasibility study in 1994 inside Ericsson and SIG formed in 1998 ¨ PAN : Proposed in 1995 in MIT ¨ MICROS : Proposed in 1996 in KAIST ¨ Pico Radio : Proposed in 1999 in Berkeley ¨ IEEE 802. 15 Standards : started in 2000 50

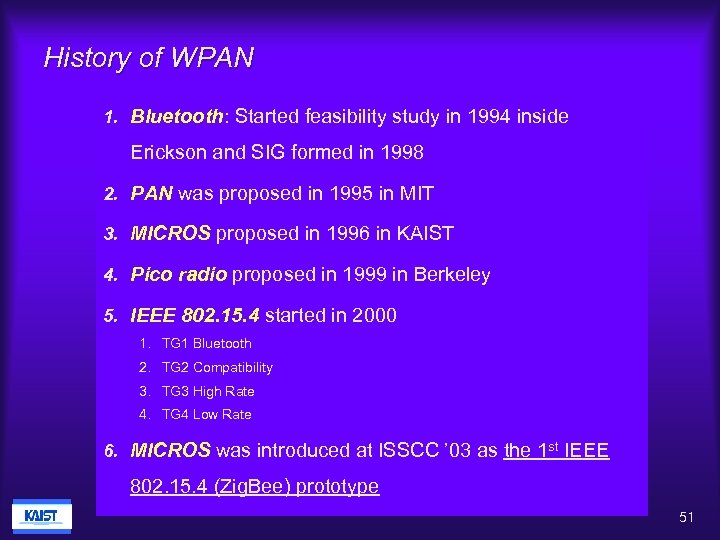

History of WPAN 1. Bluetooth: Started feasibility study in 1994 inside Erickson and SIG formed in 1998 2. PAN was proposed in 1995 in MIT 3. MICROS proposed in 1996 in KAIST 4. Pico radio proposed in 1999 in Berkeley 5. IEEE 802. 15. 4 started in 2000 1. TG 1 Bluetooth 2. TG 2 Compatibility 3. TG 3 High Rate 4. TG 4 Low Rate 6. MICROS was introduced at ISSCC ’ 03 as the 1 st IEEE 802. 15. 4 (Zig. Bee) prototype 51

History of WPAN 1. Bluetooth: Started feasibility study in 1994 inside Erickson and SIG formed in 1998 2. PAN was proposed in 1995 in MIT 3. MICROS proposed in 1996 in KAIST 4. Pico radio proposed in 1999 in Berkeley 5. IEEE 802. 15. 4 started in 2000 1. TG 1 Bluetooth 2. TG 2 Compatibility 3. TG 3 High Rate 4. TG 4 Low Rate 6. MICROS was introduced at ISSCC ’ 03 as the 1 st IEEE 802. 15. 4 (Zig. Bee) prototype 51

IEEE 802. 15: new millennium baby 52

IEEE 802. 15: new millennium baby 52

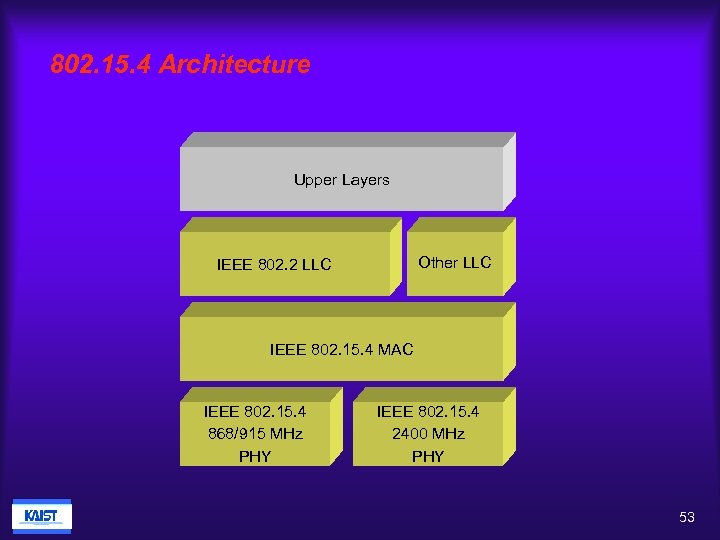

802. 15. 4 Architecture Upper Layers Other LLC IEEE 802. 2 LLC IEEE 802. 15. 4 MAC IEEE 802. 15. 4 868/915 MHz PHY IEEE 802. 15. 4 2400 MHz PHY 53

802. 15. 4 Architecture Upper Layers Other LLC IEEE 802. 2 LLC IEEE 802. 15. 4 MAC IEEE 802. 15. 4 868/915 MHz PHY IEEE 802. 15. 4 2400 MHz PHY 53

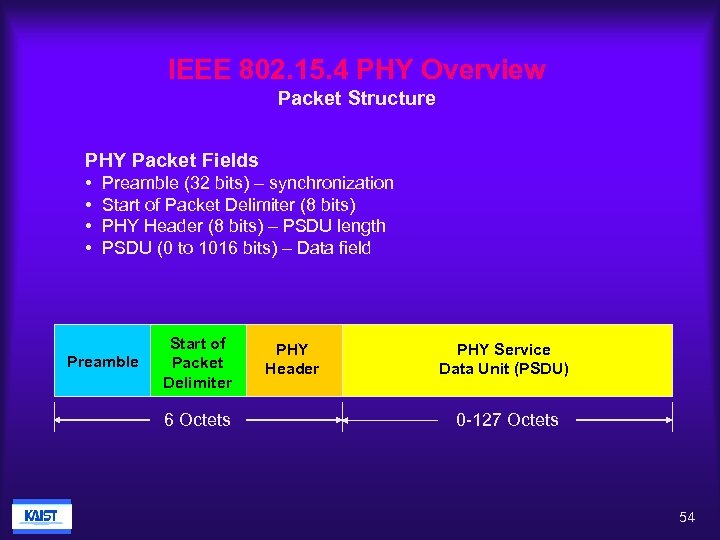

IEEE 802. 15. 4 PHY Overview Packet Structure PHY Packet Fields • • Preamble (32 bits) – synchronization Start of Packet Delimiter (8 bits) PHY Header (8 bits) – PSDU length PSDU (0 to 1016 bits) – Data field Preamble Start of Packet Delimiter 6 Octets PHY Header PHY Service Data Unit (PSDU) 0 -127 Octets 54

IEEE 802. 15. 4 PHY Overview Packet Structure PHY Packet Fields • • Preamble (32 bits) – synchronization Start of Packet Delimiter (8 bits) PHY Header (8 bits) – PSDU length PSDU (0 to 1016 bits) – Data field Preamble Start of Packet Delimiter 6 Octets PHY Header PHY Service Data Unit (PSDU) 0 -127 Octets 54

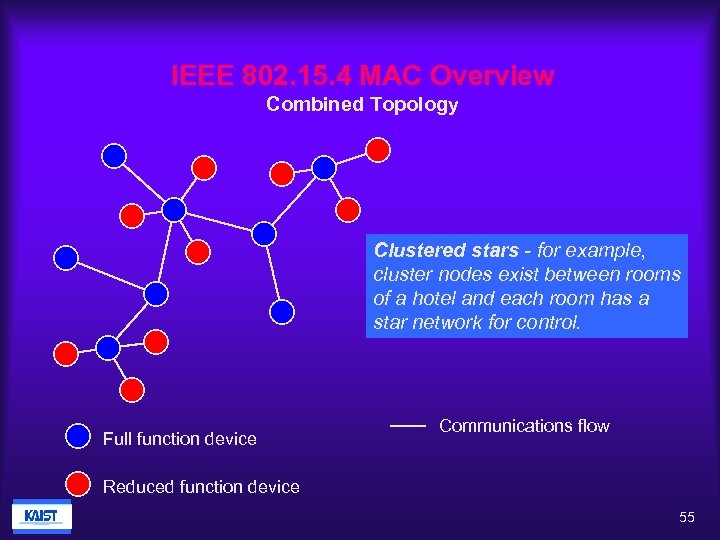

IEEE 802. 15. 4 MAC Overview Combined Topology Clustered stars - for example, cluster nodes exist between rooms of a hotel and each room has a star network for control. Full function device Communications flow Reduced function device 55

IEEE 802. 15. 4 MAC Overview Combined Topology Clustered stars - for example, cluster nodes exist between rooms of a hotel and each room has a star network for control. Full function device Communications flow Reduced function device 55

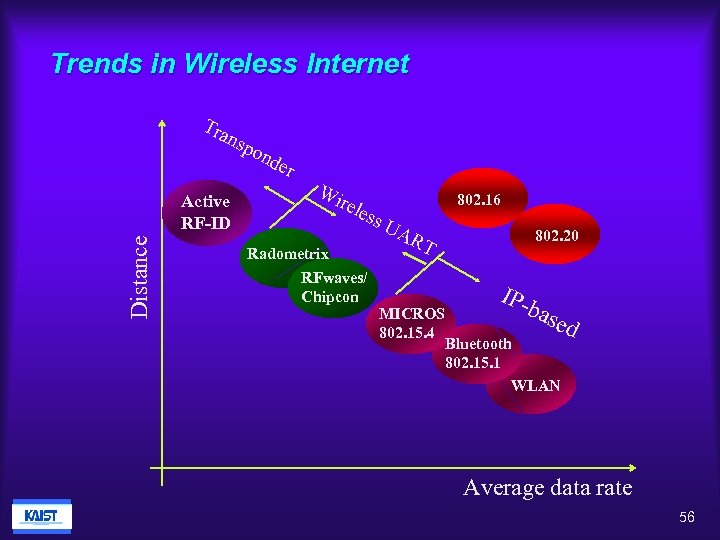

Trends in Wireless Internet Tra nsp Distance Active RF-ID ond er Wi rele 802. 16 ss U Radometrix RFwaves/ Chipcon AR T MICROS 802. 15. 4 802. 20 IP- bas ed Bluetooth 802. 15. 1 WLAN Average data rate 56

Trends in Wireless Internet Tra nsp Distance Active RF-ID ond er Wi rele 802. 16 ss U Radometrix RFwaves/ Chipcon AR T MICROS 802. 15. 4 802. 20 IP- bas ed Bluetooth 802. 15. 1 WLAN Average data rate 56

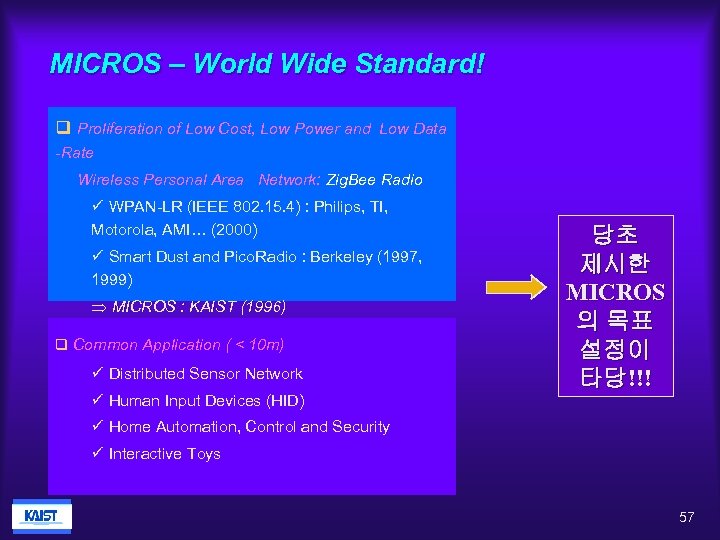

MICROS – World Wide Standard! q Proliferation of Low Cost, Low Power and Low Data -Rate Wireless Personal Area Network: Zig. Bee Radio ü WPAN-LR (IEEE 802. 15. 4) : Philips, TI, Motorola, AMI… (2000) ü Smart Dust and Pico. Radio : Berkeley (1997, 1999) Þ MICROS : KAIST (1996) q Common Application ( < 10 m) ü Distributed Sensor Network ü Human Input Devices (HID) 당초 제시한 MICROS 의 목표 설정이 타당!!! ü Home Automation, Control and Security ü Interactive Toys 57

MICROS – World Wide Standard! q Proliferation of Low Cost, Low Power and Low Data -Rate Wireless Personal Area Network: Zig. Bee Radio ü WPAN-LR (IEEE 802. 15. 4) : Philips, TI, Motorola, AMI… (2000) ü Smart Dust and Pico. Radio : Berkeley (1997, 1999) Þ MICROS : KAIST (1996) q Common Application ( < 10 m) ü Distributed Sensor Network ü Human Input Devices (HID) 당초 제시한 MICROS 의 목표 설정이 타당!!! ü Home Automation, Control and Security ü Interactive Toys 57

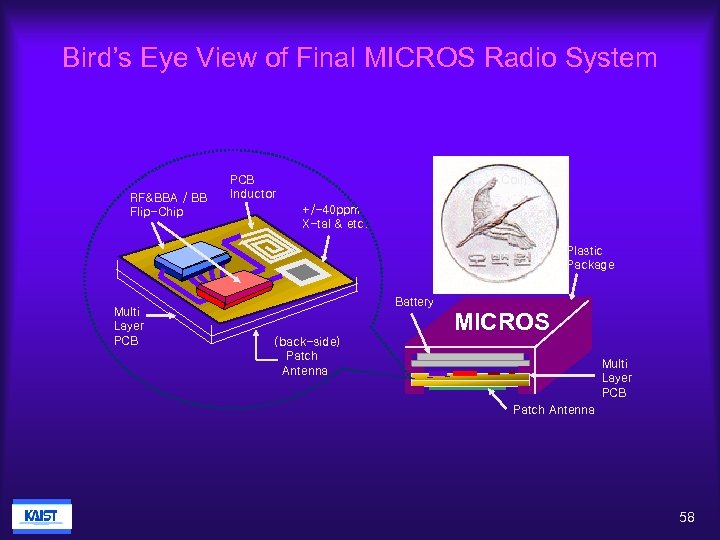

Bird’s Eye View of Final MICROS Radio System RF&BBA / BB Flip-Chip PCB Inductor Coin +/-40 ppm X-tal & etc. Plastic Package Multi Layer PCB Battery MICROS (back-side) Patch Antenna Multi Layer PCB Patch Antenna 58

Bird’s Eye View of Final MICROS Radio System RF&BBA / BB Flip-Chip PCB Inductor Coin +/-40 ppm X-tal & etc. Plastic Package Multi Layer PCB Battery MICROS (back-side) Patch Antenna Multi Layer PCB Patch Antenna 58

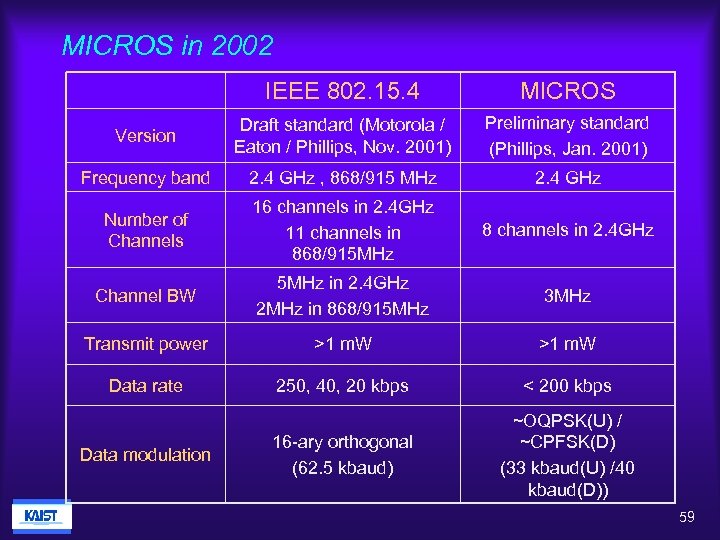

MICROS in 2002 IEEE 802. 15. 4 MICROS Version Draft standard (Motorola / Eaton / Phillips, Nov. 2001) Preliminary standard (Phillips, Jan. 2001) Frequency band 2. 4 GHz , 868/915 MHz 2. 4 GHz Number of Channels 16 channels in 2. 4 GHz 11 channels in 868/915 MHz 8 channels in 2. 4 GHz Channel BW 5 MHz in 2. 4 GHz 2 MHz in 868/915 MHz 3 MHz Transmit power >1 m. W Data rate 250, 40, 20 kbps < 200 kbps 16 -ary orthogonal (62. 5 kbaud) ~OQPSK(U) / ~CPFSK(D) (33 kbaud(U) /40 kbaud(D)) Data modulation 59

MICROS in 2002 IEEE 802. 15. 4 MICROS Version Draft standard (Motorola / Eaton / Phillips, Nov. 2001) Preliminary standard (Phillips, Jan. 2001) Frequency band 2. 4 GHz , 868/915 MHz 2. 4 GHz Number of Channels 16 channels in 2. 4 GHz 11 channels in 868/915 MHz 8 channels in 2. 4 GHz Channel BW 5 MHz in 2. 4 GHz 2 MHz in 868/915 MHz 3 MHz Transmit power >1 m. W Data rate 250, 40, 20 kbps < 200 kbps 16 -ary orthogonal (62. 5 kbaud) ~OQPSK(U) / ~CPFSK(D) (33 kbaud(U) /40 kbaud(D)) Data modulation 59

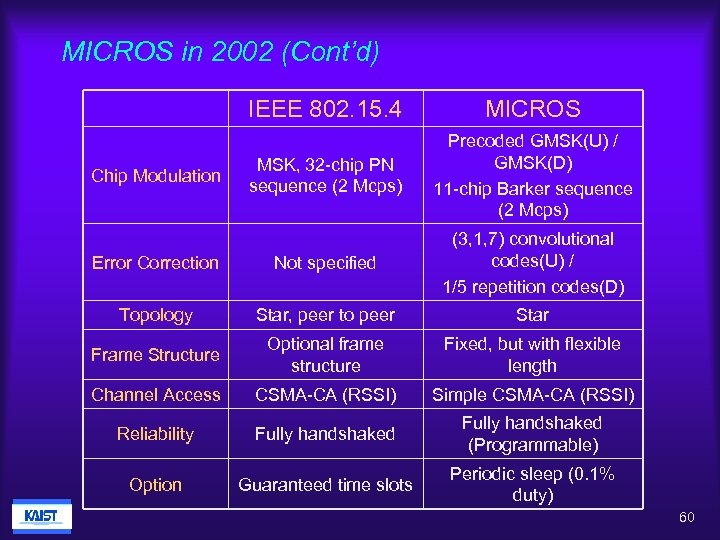

MICROS in 2002 (Cont’d) IEEE 802. 15. 4 MICROS MSK, 32 -chip PN sequence (2 Mcps) Precoded GMSK(U) / GMSK(D) 11 -chip Barker sequence (2 Mcps) Error Correction Not specified (3, 1, 7) convolutional codes(U) / 1/5 repetition codes(D) Topology Star, peer to peer Star Frame Structure Optional frame structure Fixed, but with flexible length Channel Access CSMA-CA (RSSI) Simple CSMA-CA (RSSI) Reliability Fully handshaked (Programmable) Option Guaranteed time slots Periodic sleep (0. 1% duty) Chip Modulation 60

MICROS in 2002 (Cont’d) IEEE 802. 15. 4 MICROS MSK, 32 -chip PN sequence (2 Mcps) Precoded GMSK(U) / GMSK(D) 11 -chip Barker sequence (2 Mcps) Error Correction Not specified (3, 1, 7) convolutional codes(U) / 1/5 repetition codes(D) Topology Star, peer to peer Star Frame Structure Optional frame structure Fixed, but with flexible length Channel Access CSMA-CA (RSSI) Simple CSMA-CA (RSSI) Reliability Fully handshaked (Programmable) Option Guaranteed time slots Periodic sleep (0. 1% duty) Chip Modulation 60

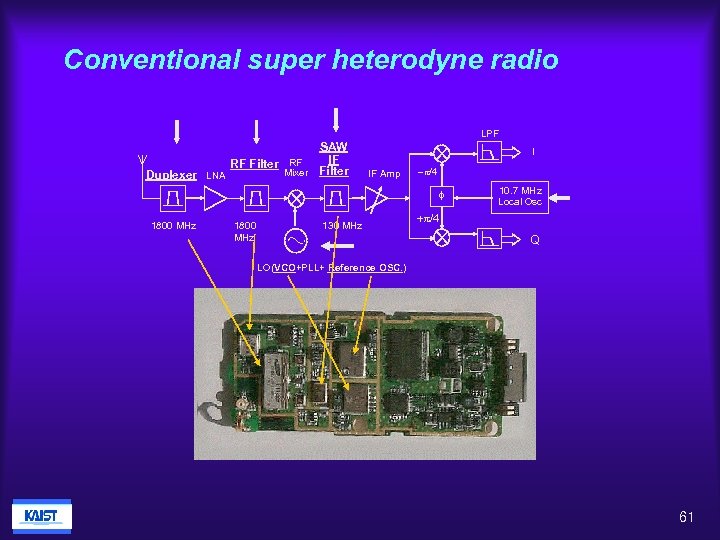

Conventional super heterodyne radio LPF SAW IF RF Filter Mixer Duplexer LNA I IF Amp p/4 f 1800 MHz 130 MHz 10. 7 MHz Local Osc +p/4 Q LO(VCO+PLL+ Reference OSC. ) 61

Conventional super heterodyne radio LPF SAW IF RF Filter Mixer Duplexer LNA I IF Amp p/4 f 1800 MHz 130 MHz 10. 7 MHz Local Osc +p/4 Q LO(VCO+PLL+ Reference OSC. ) 61

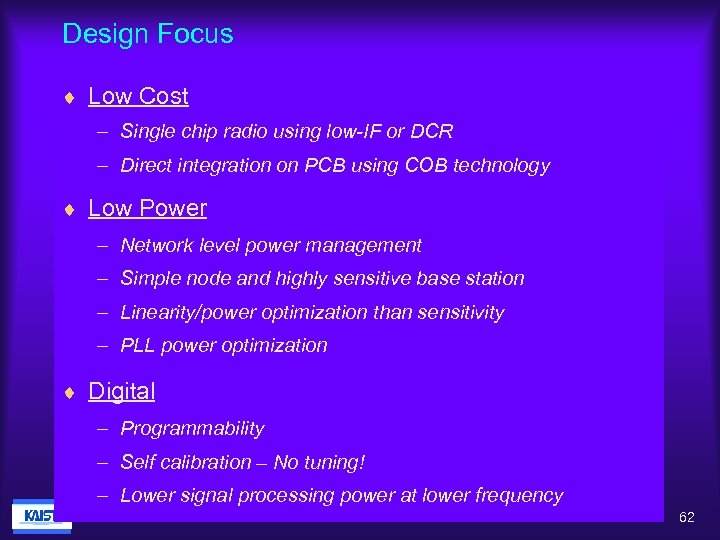

Design Focus ¨ Low Cost – Single chip radio using low-IF or DCR – Direct integration on PCB using COB technology ¨ Low Power – Network level power management – Simple node and highly sensitive base station – Linearity/power optimization than sensitivity – PLL power optimization ¨ Digital – Programmability – Self calibration – No tuning! – Lower signal processing power at lower frequency 62

Design Focus ¨ Low Cost – Single chip radio using low-IF or DCR – Direct integration on PCB using COB technology ¨ Low Power – Network level power management – Simple node and highly sensitive base station – Linearity/power optimization than sensitivity – PLL power optimization ¨ Digital – Programmability – Self calibration – No tuning! – Lower signal processing power at lower frequency 62

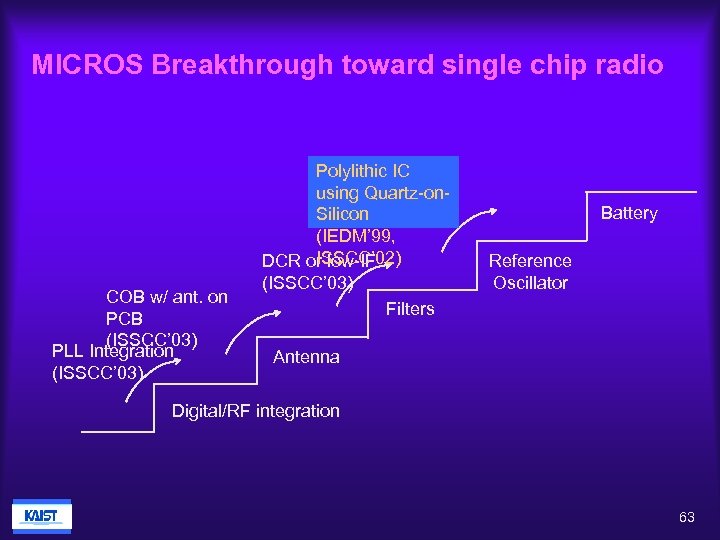

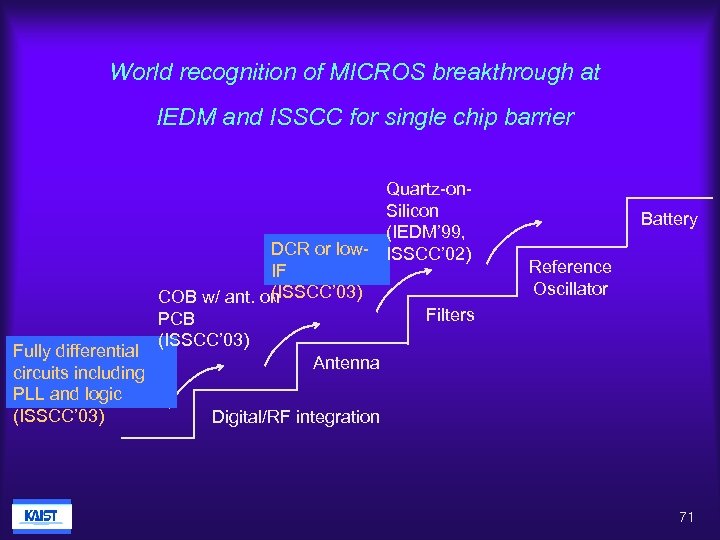

MICROS Breakthrough toward single chip radio COB w/ ant. on PCB (ISSCC’ 03) PLL Integration (ISSCC’ 03) Polylithic IC using Quartz-on. Silicon (IEDM’ 99, ISSCC’ 02) DCR or low-IF (ISSCC’ 03) Filters Battery Reference Oscillator Antenna Digital/RF integration 63

MICROS Breakthrough toward single chip radio COB w/ ant. on PCB (ISSCC’ 03) PLL Integration (ISSCC’ 03) Polylithic IC using Quartz-on. Silicon (IEDM’ 99, ISSCC’ 02) DCR or low-IF (ISSCC’ 03) Filters Battery Reference Oscillator Antenna Digital/RF integration 63

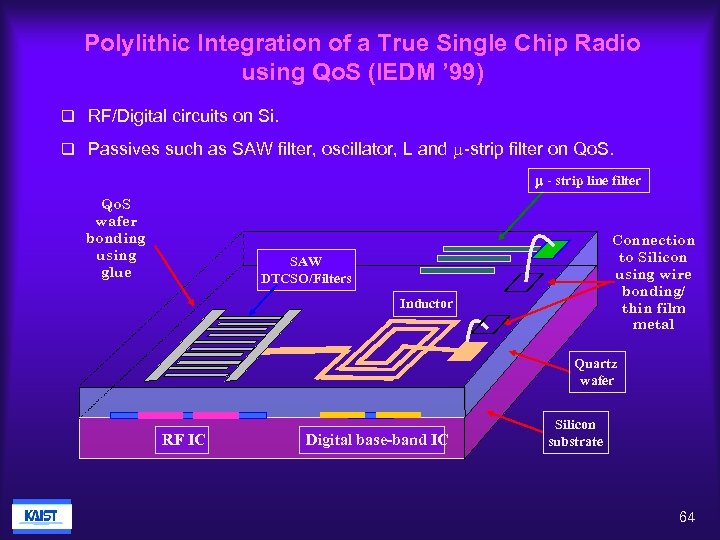

Polylithic Integration of a True Single Chip Radio using Qo. S (IEDM ’ 99) q RF/Digital circuits on Si. q Passives such as SAW filter, oscillator, L and -strip filter on Qo. S. - strip line filter Qo. S wafer bonding using glue Connection to Silicon using wire bonding/ thin film metal SAW DTCSO/Filters Inductor Quartz wafer RF IC Digital base-band IC Silicon substrate 64

Polylithic Integration of a True Single Chip Radio using Qo. S (IEDM ’ 99) q RF/Digital circuits on Si. q Passives such as SAW filter, oscillator, L and -strip filter on Qo. S. - strip line filter Qo. S wafer bonding using glue Connection to Silicon using wire bonding/ thin film metal SAW DTCSO/Filters Inductor Quartz wafer RF IC Digital base-band IC Silicon substrate 64

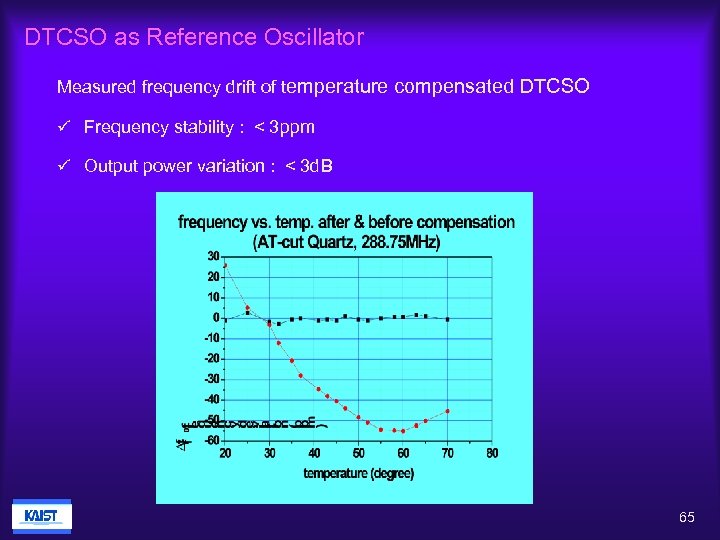

DTCSO as Reference Oscillator Measured frequency drift of temperature compensated DTCSO ü Frequency stability : < 3 ppm ü Output power variation : < 3 d. B 65

DTCSO as Reference Oscillator Measured frequency drift of temperature compensated DTCSO ü Frequency stability : < 3 ppm ü Output power variation : < 3 d. B 65

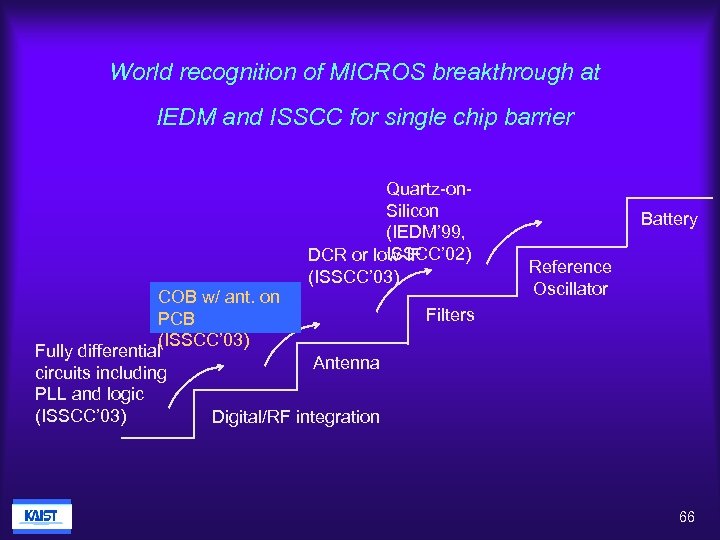

World recognition of MICROS breakthrough at IEDM and ISSCC for single chip barrier Quartz-on. Silicon (IEDM’ 99, ISSCC’ 02) DCR or low-IF (ISSCC’ 03) COB w/ ant. on PCB (ISSCC’ 03) Fully differential Antenna circuits including PLL and logic (ISSCC’ 03) Digital/RF integration Battery Reference Oscillator Filters 66

World recognition of MICROS breakthrough at IEDM and ISSCC for single chip barrier Quartz-on. Silicon (IEDM’ 99, ISSCC’ 02) DCR or low-IF (ISSCC’ 03) COB w/ ant. on PCB (ISSCC’ 03) Fully differential Antenna circuits including PLL and logic (ISSCC’ 03) Digital/RF integration Battery Reference Oscillator Filters 66

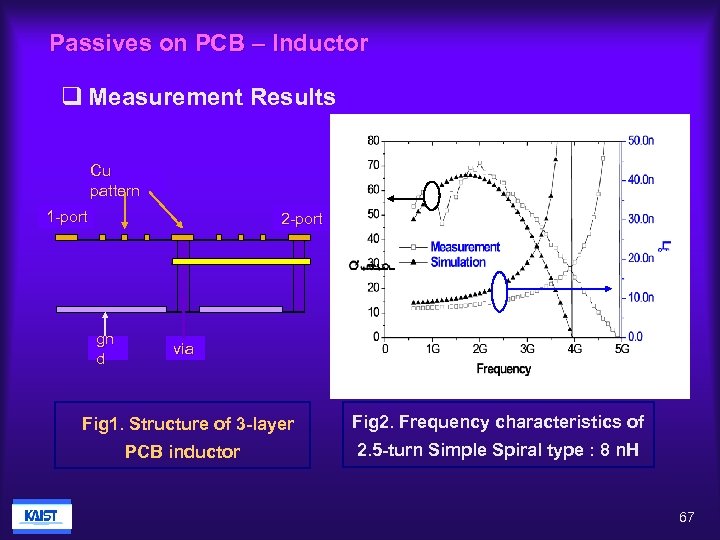

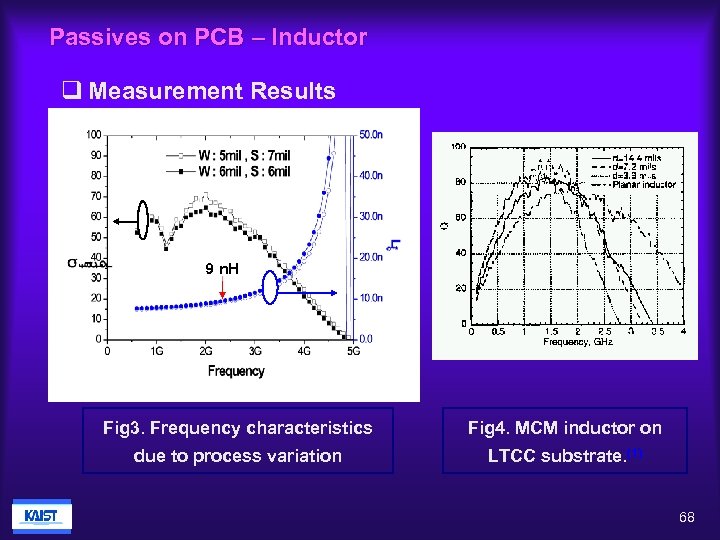

Passives on PCB – Inductor q Measurement Results Cu pattern 1 -port 2 -port gn d via Fig 1. Structure of 3 -layer Fig 2. Frequency characteristics of PCB inductor 2. 5 -turn Simple Spiral type : 8 n. H 67

Passives on PCB – Inductor q Measurement Results Cu pattern 1 -port 2 -port gn d via Fig 1. Structure of 3 -layer Fig 2. Frequency characteristics of PCB inductor 2. 5 -turn Simple Spiral type : 8 n. H 67

Passives on PCB – Inductor q Measurement Results 9 n. H Fig 3. Frequency characteristics Fig 4. MCM inductor on due to process variation LTCC substrate. (1) 68

Passives on PCB – Inductor q Measurement Results 9 n. H Fig 3. Frequency characteristics Fig 4. MCM inductor on due to process variation LTCC substrate. (1) 68

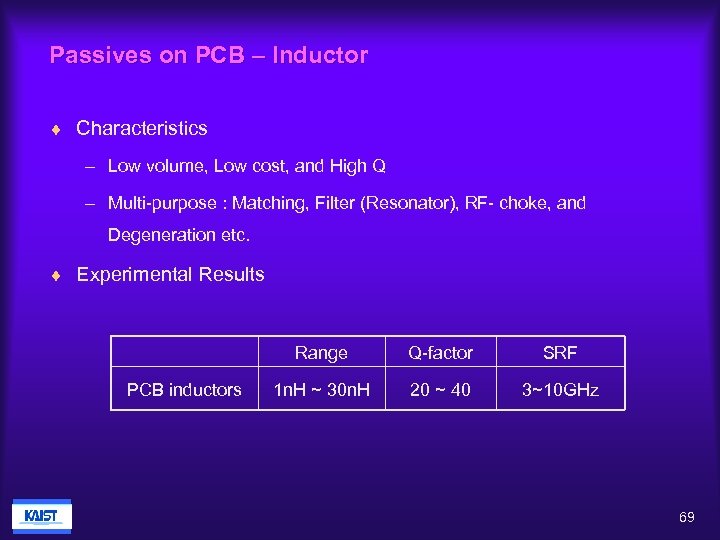

Passives on PCB – Inductor ¨ Characteristics – Low volume, Low cost, and High Q – Multi-purpose : Matching, Filter (Resonator), RF- choke, and Degeneration etc. ¨ Experimental Results Range PCB inductors Q-factor SRF 1 n. H ~ 30 n. H 20 ~ 40 3~10 GHz 69

Passives on PCB – Inductor ¨ Characteristics – Low volume, Low cost, and High Q – Multi-purpose : Matching, Filter (Resonator), RF- choke, and Degeneration etc. ¨ Experimental Results Range PCB inductors Q-factor SRF 1 n. H ~ 30 n. H 20 ~ 40 3~10 GHz 69

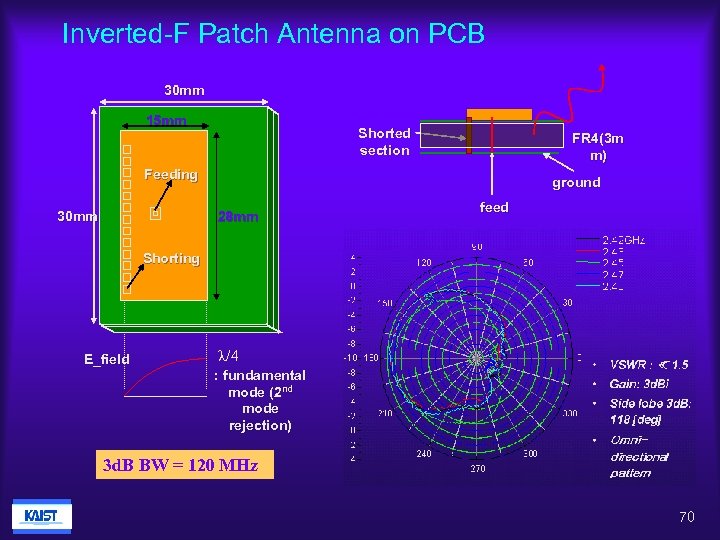

Inverted-F Patch Antenna on PCB 30 mm 15 mm Shorted section FR 4(3 m m) Feeding 30[mm] 30 mm 28 mm ground feed Shorting E_field l/4 : fundamental mode (2 nd mode rejection) 3 d. B BW = 120 MHz 70

Inverted-F Patch Antenna on PCB 30 mm 15 mm Shorted section FR 4(3 m m) Feeding 30[mm] 30 mm 28 mm ground feed Shorting E_field l/4 : fundamental mode (2 nd mode rejection) 3 d. B BW = 120 MHz 70

World recognition of MICROS breakthrough at IEDM and ISSCC for single chip barrier Fully differential circuits including PLL and logic (ISSCC’ 03) Quartz-on. Silicon (IEDM’ 99, DCR or low- ISSCC’ 02) IF (ISSCC’ 03) COB w/ ant. on Filters PCB (ISSCC’ 03) Antenna Battery Reference Oscillator Digital/RF integration 71

World recognition of MICROS breakthrough at IEDM and ISSCC for single chip barrier Fully differential circuits including PLL and logic (ISSCC’ 03) Quartz-on. Silicon (IEDM’ 99, DCR or low- ISSCC’ 02) IF (ISSCC’ 03) COB w/ ant. on Filters PCB (ISSCC’ 03) Antenna Battery Reference Oscillator Digital/RF integration 71

The use of Vertical NPN for DCR or Weaver DCR* * patented by MICROS 72

The use of Vertical NPN for DCR or Weaver DCR* * patented by MICROS 72

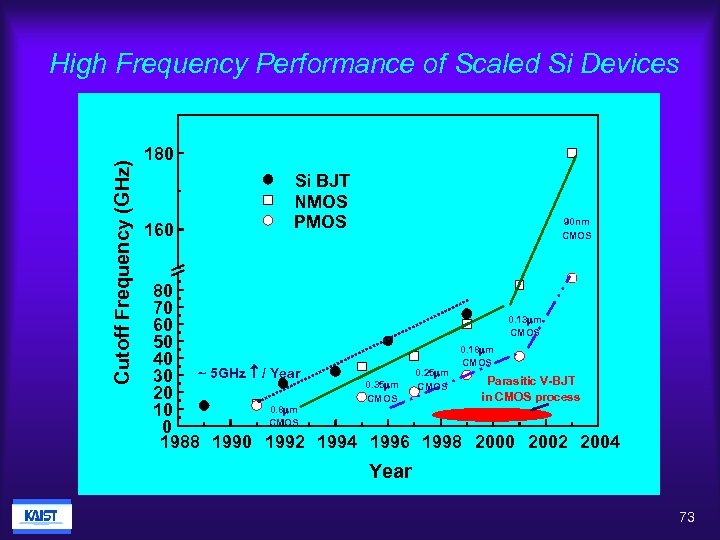

Cutoff Frequency (GHz) High Frequency Performance of Scaled Si Devices 180 160 Si BJT NMOS PMOS 90 nm CMOS 80 70 0. 13 m 60 CMOS 50 0. 18 m 40 CMOS 0. 25 m ~ 5 GHz / Year 30 Parasitic V-BJT 0. 35 m CMOS 20 in CMOS process CMOS 0. 8 m 10 CMOS 0 1988 1990 1992 1994 1996 1998 2000 2002 2004 Year 73

Cutoff Frequency (GHz) High Frequency Performance of Scaled Si Devices 180 160 Si BJT NMOS PMOS 90 nm CMOS 80 70 0. 13 m 60 CMOS 50 0. 18 m 40 CMOS 0. 25 m ~ 5 GHz / Year 30 Parasitic V-BJT 0. 35 m CMOS 20 in CMOS process CMOS 0. 8 m 10 CMOS 0 1988 1990 1992 1994 1996 1998 2000 2002 2004 Year 73

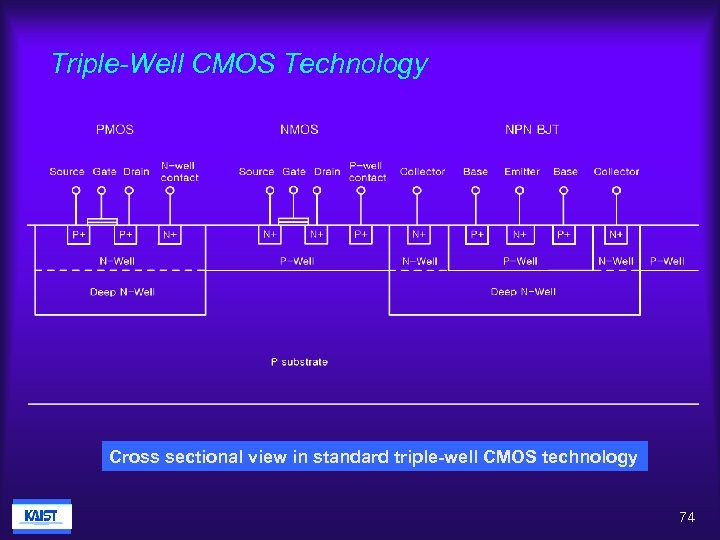

Triple-Well CMOS Technology Cross sectional view in standard triple-well CMOS technology 74

Triple-Well CMOS Technology Cross sectional view in standard triple-well CMOS technology 74

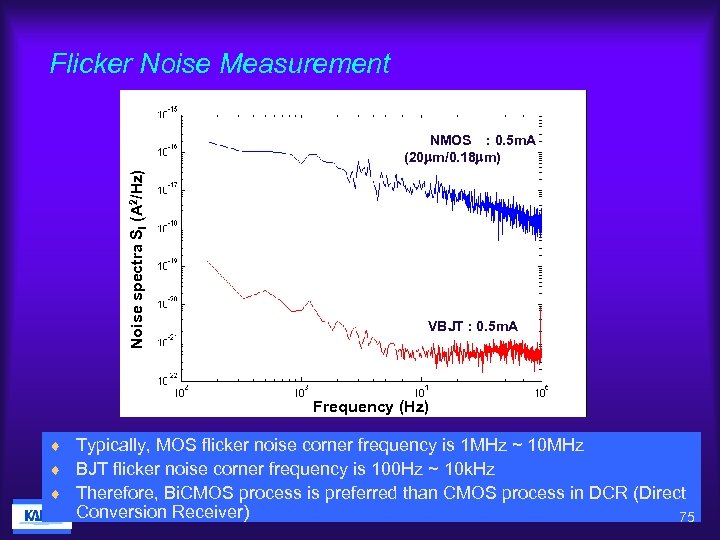

Flicker Noise Measurement Noise spectra SI (A 2/Hz) NMOS : 0. 5 m. A (20 m/0. 18 m) VBJT : 0. 5 m. A Frequency (Hz) ¨ Typically, MOS flicker noise corner frequency is 1 MHz ~ 10 MHz ¨ BJT flicker noise corner frequency is 100 Hz ~ 10 k. Hz ¨ Therefore, Bi. CMOS process is preferred than CMOS process in DCR (Direct Conversion Receiver) 75

Flicker Noise Measurement Noise spectra SI (A 2/Hz) NMOS : 0. 5 m. A (20 m/0. 18 m) VBJT : 0. 5 m. A Frequency (Hz) ¨ Typically, MOS flicker noise corner frequency is 1 MHz ~ 10 MHz ¨ BJT flicker noise corner frequency is 100 Hz ~ 10 k. Hz ¨ Therefore, Bi. CMOS process is preferred than CMOS process in DCR (Direct Conversion Receiver) 75

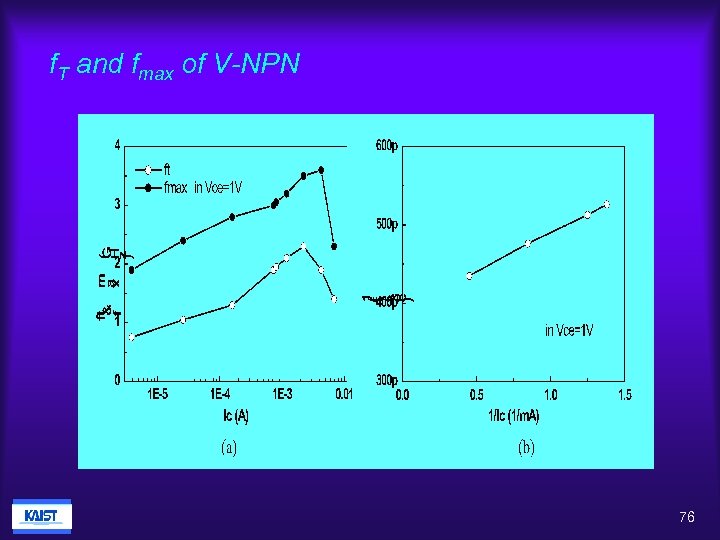

f. T and fmax of V-NPN 76

f. T and fmax of V-NPN 76

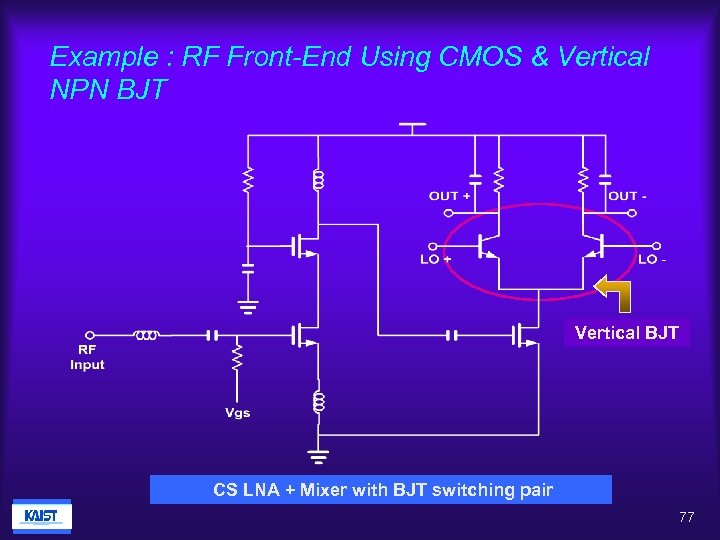

Example : RF Front-End Using CMOS & Vertical NPN BJT Vertical BJT CS LNA + Mixer with BJT switching pair 77

Example : RF Front-End Using CMOS & Vertical NPN BJT Vertical BJT CS LNA + Mixer with BJT switching pair 77

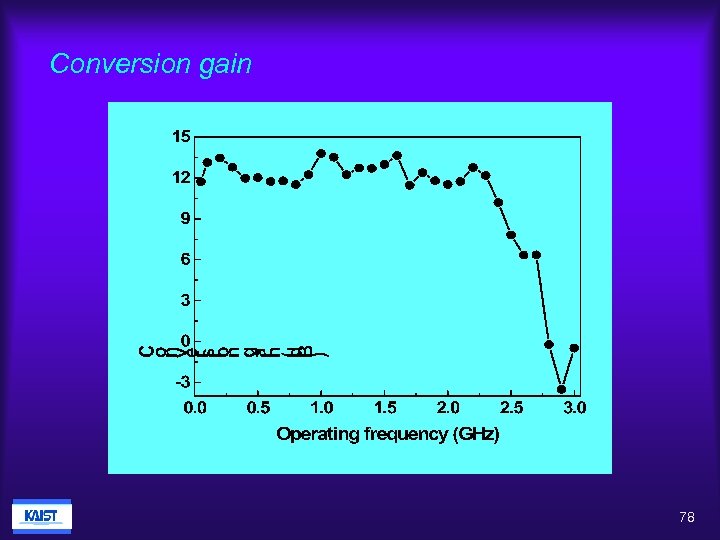

Conversion gain 78

Conversion gain 78

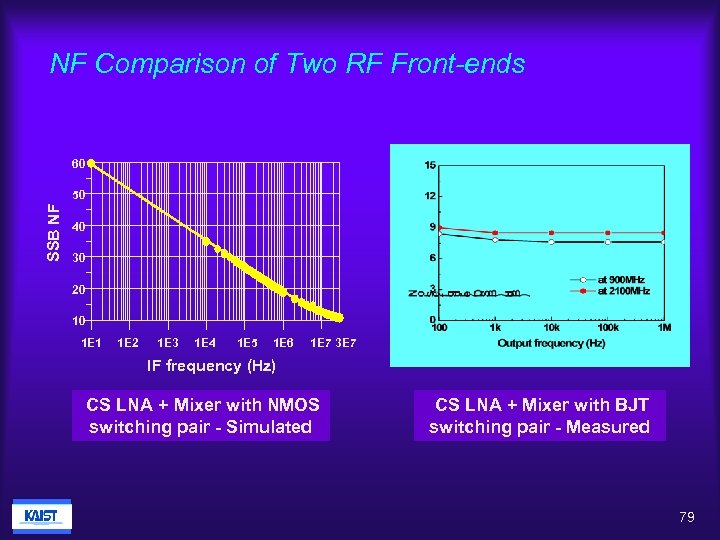

NF Comparison of Two RF Front-ends 60 SSB NF 50 40 30 20 10 1 E 1 1 E 2 1 E 3 1 E 4 1 E 5 1 E 6 1 E 7 3 E 7 IF frequency (Hz) CS LNA + Mixer with NMOS switching pair - Simulated CS LNA + Mixer with BJT switching pair - Measured 79

NF Comparison of Two RF Front-ends 60 SSB NF 50 40 30 20 10 1 E 1 1 E 2 1 E 3 1 E 4 1 E 5 1 E 6 1 E 7 3 E 7 IF frequency (Hz) CS LNA + Mixer with NMOS switching pair - Simulated CS LNA + Mixer with BJT switching pair - Measured 79

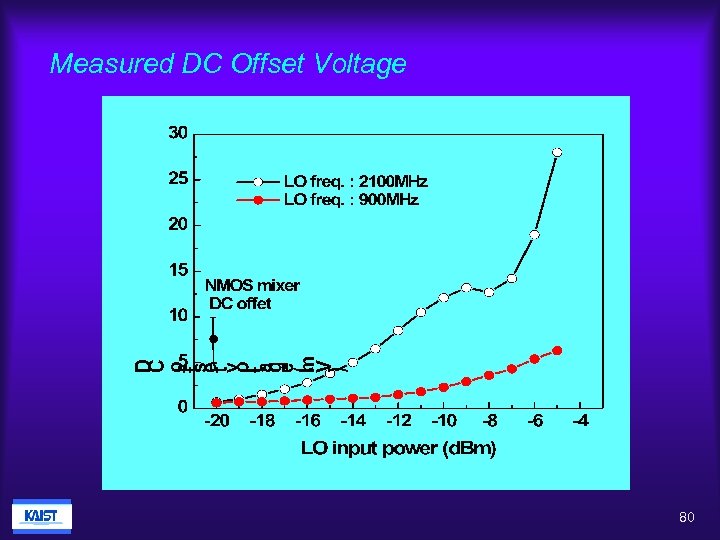

Measured DC Offset Voltage 80

Measured DC Offset Voltage 80

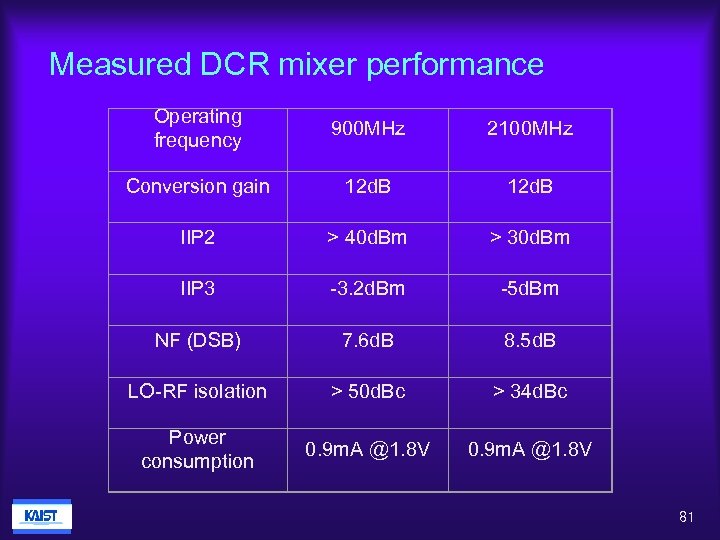

Measured DCR mixer performance Operating frequency 900 MHz 2100 MHz Conversion gain 12 d. B IIP 2 > 40 d. Bm > 30 d. Bm IIP 3 -3. 2 d. Bm -5 d. Bm NF (DSB) 7. 6 d. B 8. 5 d. B LO-RF isolation > 50 d. Bc > 34 d. Bc Power consumption 0. 9 m. A @1. 8 V 81

Measured DCR mixer performance Operating frequency 900 MHz 2100 MHz Conversion gain 12 d. B IIP 2 > 40 d. Bm > 30 d. Bm IIP 3 -3. 2 d. Bm -5 d. Bm NF (DSB) 7. 6 d. B 8. 5 d. B LO-RF isolation > 50 d. Bc > 34 d. Bc Power consumption 0. 9 m. A @1. 8 V 81

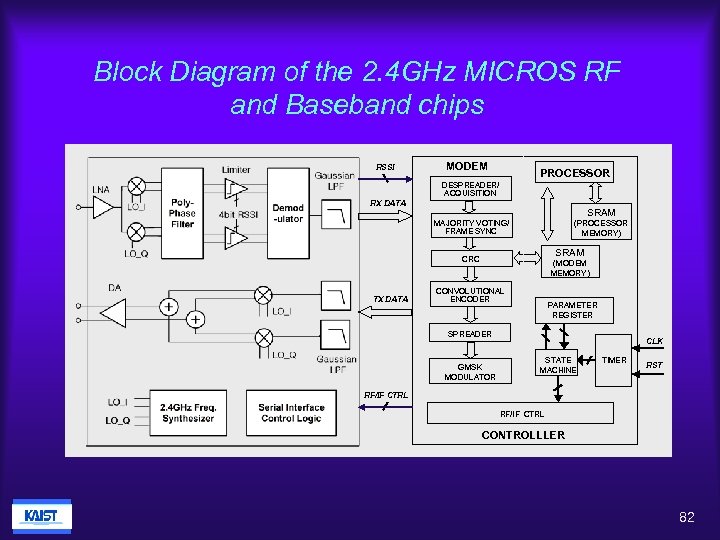

Block Diagram of the 2. 4 GHz MICROS RF and Baseband chips RSSI MODEM PROCESSOR DESPREADER/ ACQUISITION RX DATA SRAM MAJORITY VOTING/ FRAME SYNC (PROCESSOR MEMORY) SRAM CRC TX DATA (MODEM MEMORY) CONVOLUTIONAL ENCODER PARAMETER REGISTER SPREADER GMSK MODULATOR CLK STATE MACHINE TIMER RST RF/IF CTRL CONTROLLLER 82

Block Diagram of the 2. 4 GHz MICROS RF and Baseband chips RSSI MODEM PROCESSOR DESPREADER/ ACQUISITION RX DATA SRAM MAJORITY VOTING/ FRAME SYNC (PROCESSOR MEMORY) SRAM CRC TX DATA (MODEM MEMORY) CONVOLUTIONAL ENCODER PARAMETER REGISTER SPREADER GMSK MODULATOR CLK STATE MACHINE TIMER RST RF/IF CTRL CONTROLLLER 82

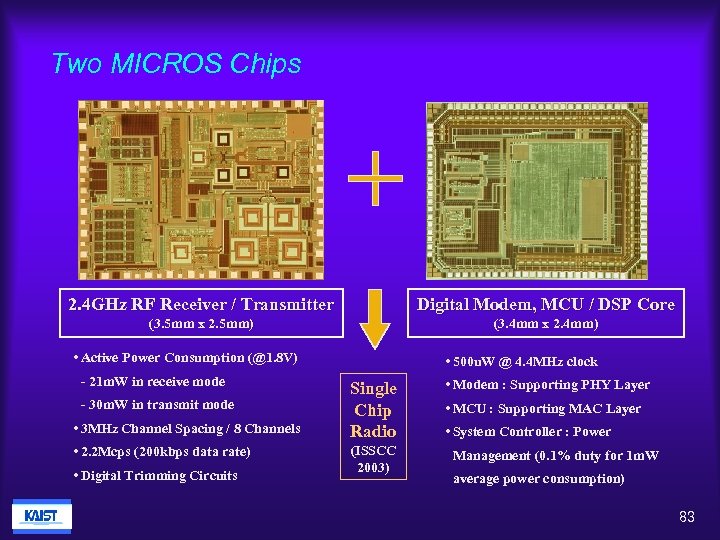

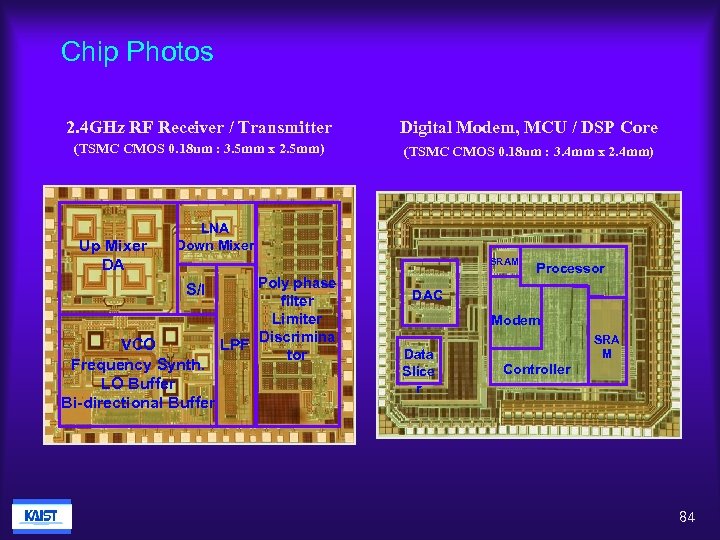

Two MICROS Chips 2. 4 GHz RF Receiver / Transmitter Digital Modem, MCU / DSP Core (3. 5 mm x 2. 5 mm) (3. 4 mm x 2. 4 mm) • Active Power Consumption (@1. 8 V) - 21 m. W in receive mode - 30 m. W in transmit mode • 3 MHz Channel Spacing / 8 Channels • 2. 2 Mcps (200 kbps data rate) • Digital Trimming Circuits • 500 u. W @ 4. 4 MHz clock Single Chip Radio (ISSCC 2003) • Modem : Supporting PHY Layer • MCU : Supporting MAC Layer • System Controller : Power Management (0. 1% duty for 1 m. W average power consumption) 83

Two MICROS Chips 2. 4 GHz RF Receiver / Transmitter Digital Modem, MCU / DSP Core (3. 5 mm x 2. 5 mm) (3. 4 mm x 2. 4 mm) • Active Power Consumption (@1. 8 V) - 21 m. W in receive mode - 30 m. W in transmit mode • 3 MHz Channel Spacing / 8 Channels • 2. 2 Mcps (200 kbps data rate) • Digital Trimming Circuits • 500 u. W @ 4. 4 MHz clock Single Chip Radio (ISSCC 2003) • Modem : Supporting PHY Layer • MCU : Supporting MAC Layer • System Controller : Power Management (0. 1% duty for 1 m. W average power consumption) 83

Chip Photos 2. 4 GHz RF Receiver / Transmitter Digital Modem, MCU / DSP Core (TSMC CMOS 0. 18 um : 3. 5 mm x 2. 5 mm) (TSMC CMOS 0. 18 um : 3. 4 mm x 2. 4 mm) Up Mixer DA LNA Down Mixer SRAM S/I VCO Frequency Synth. LO Buffer Bi-directional Buffer Poly phase filter Limiter Discrimina LPF tor Processor DAC Modem Data Slice r SRA M Controller 84

Chip Photos 2. 4 GHz RF Receiver / Transmitter Digital Modem, MCU / DSP Core (TSMC CMOS 0. 18 um : 3. 5 mm x 2. 5 mm) (TSMC CMOS 0. 18 um : 3. 4 mm x 2. 4 mm) Up Mixer DA LNA Down Mixer SRAM S/I VCO Frequency Synth. LO Buffer Bi-directional Buffer Poly phase filter Limiter Discrimina LPF tor Processor DAC Modem Data Slice r SRA M Controller 84

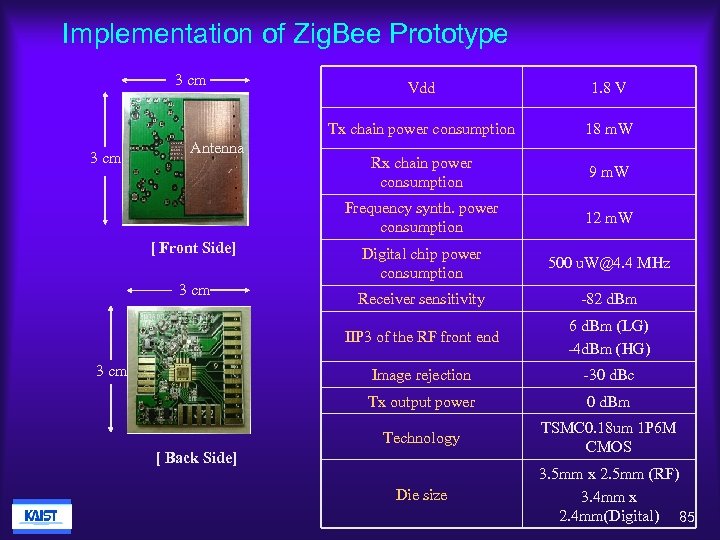

Implementation of Zig. Bee Prototype 3 cm 12 m. W Digital chip power consumption 500 u. W@4. 4 MHz Receiver sensitivity -82 d. Bm 6 d. Bm (LG) -4 d. Bm (HG) -30 d. Bc Tx output power 0 d. Bm Technology 3 cm 9 m. W Image rejection 3 cm Rx chain power consumption IIP 3 of the RF front end [ Front Side] 18 m. W Frequency synth. power consumption Antenna 1. 8 V Tx chain power consumption 3 cm Vdd TSMC 0. 18 um 1 P 6 M CMOS [ Back Side] Die size 3. 5 mm x 2. 5 mm (RF) 3. 4 mm x 2. 4 mm(Digital) 85

Implementation of Zig. Bee Prototype 3 cm 12 m. W Digital chip power consumption 500 u. W@4. 4 MHz Receiver sensitivity -82 d. Bm 6 d. Bm (LG) -4 d. Bm (HG) -30 d. Bc Tx output power 0 d. Bm Technology 3 cm 9 m. W Image rejection 3 cm Rx chain power consumption IIP 3 of the RF front end [ Front Side] 18 m. W Frequency synth. power consumption Antenna 1. 8 V Tx chain power consumption 3 cm Vdd TSMC 0. 18 um 1 P 6 M CMOS [ Back Side] Die size 3. 5 mm x 2. 5 mm (RF) 3. 4 mm x 2. 4 mm(Digital) 85

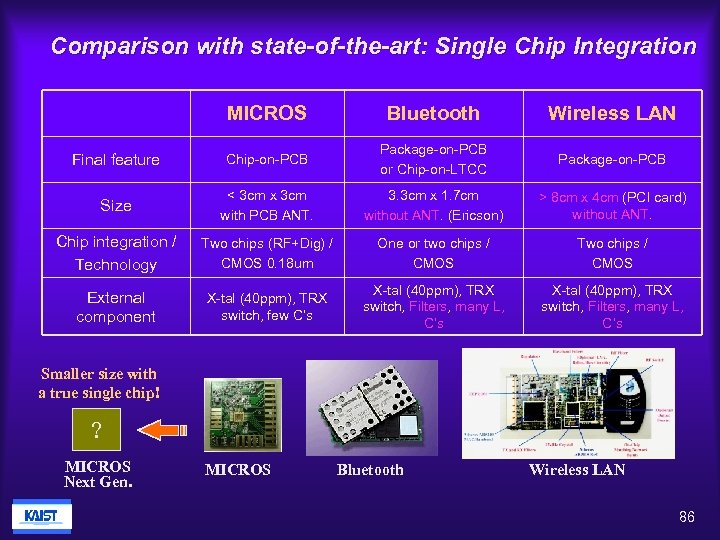

Comparison with state-of-the-art: Single Chip Integration MICROS Bluetooth Wireless LAN Final feature Chip-on-PCB Package-on-PCB or Chip-on-LTCC Package-on-PCB Size < 3 cm x 3 cm with PCB ANT. 3. 3 cm x 1. 7 cm without ANT. (Ericson) > 8 cm x 4 cm (PCI card) without ANT. Chip integration / Technology Two chips (RF+Dig) / CMOS 0. 18 um One or two chips / CMOS Two chips / CMOS External component X-tal (40 ppm), TRX switch, few C’s X-tal (40 ppm), TRX switch, Filters, many L, C’s Smaller size with a true single chip! ? MICROS Next Gen. MICROS Bluetooth Wireless LAN 86

Comparison with state-of-the-art: Single Chip Integration MICROS Bluetooth Wireless LAN Final feature Chip-on-PCB Package-on-PCB or Chip-on-LTCC Package-on-PCB Size < 3 cm x 3 cm with PCB ANT. 3. 3 cm x 1. 7 cm without ANT. (Ericson) > 8 cm x 4 cm (PCI card) without ANT. Chip integration / Technology Two chips (RF+Dig) / CMOS 0. 18 um One or two chips / CMOS Two chips / CMOS External component X-tal (40 ppm), TRX switch, few C’s X-tal (40 ppm), TRX switch, Filters, many L, C’s Smaller size with a true single chip! ? MICROS Next Gen. MICROS Bluetooth Wireless LAN 86

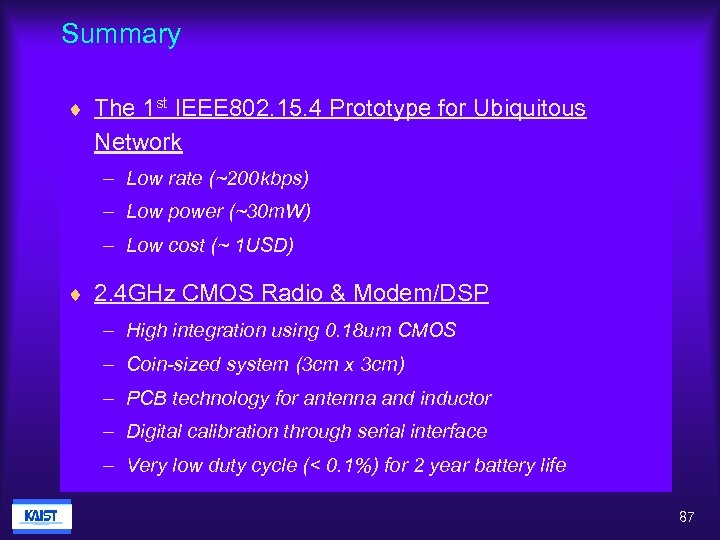

Summary ¨ The 1 st IEEE 802. 15. 4 Prototype for Ubiquitous Network – Low rate (~200 kbps) – Low power (~30 m. W) – Low cost (~ 1 USD) ¨ 2. 4 GHz CMOS Radio & Modem/DSP – High integration using 0. 18 um CMOS – Coin-sized system (3 cm x 3 cm) – PCB technology for antenna and inductor – Digital calibration through serial interface – Very low duty cycle (< 0. 1%) for 2 year battery life 87

Summary ¨ The 1 st IEEE 802. 15. 4 Prototype for Ubiquitous Network – Low rate (~200 kbps) – Low power (~30 m. W) – Low cost (~ 1 USD) ¨ 2. 4 GHz CMOS Radio & Modem/DSP – High integration using 0. 18 um CMOS – Coin-sized system (3 cm x 3 cm) – PCB technology for antenna and inductor – Digital calibration through serial interface – Very low duty cycle (< 0. 1%) for 2 year battery life 87

88

88

89

89

Dec. 2002, Nikkei. 90

Dec. 2002, Nikkei. 90

Feb. 2003, EETIMES. 91

Feb. 2003, EETIMES. 91

March 2003, Nikkei Electronics 92

March 2003, Nikkei Electronics 92

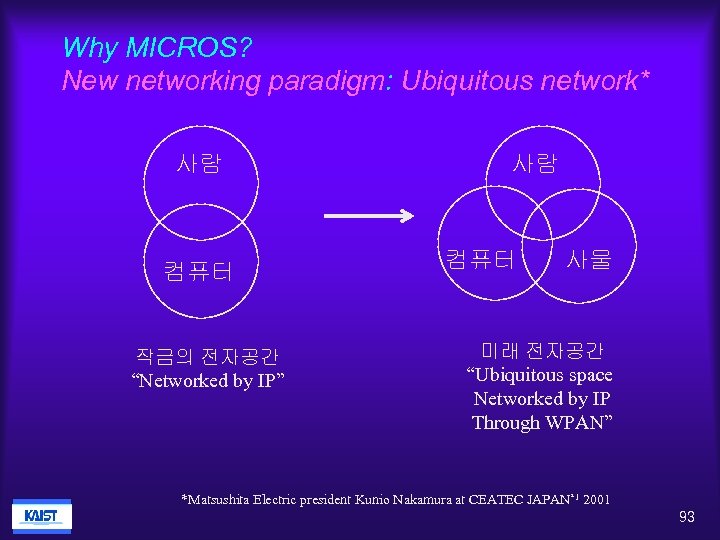

Why MICROS? New networking paradigm: Ubiquitous network* 사람 컴퓨터 작금의 전자공간 “Networked by IP” 사람 컴퓨터 사물 미래 전자공간 “Ubiquitous space Networked by IP Through WPAN” *Matsushita Electric president Kunio Nakamura at CEATEC JAPAN*1 2001 93

Why MICROS? New networking paradigm: Ubiquitous network* 사람 컴퓨터 작금의 전자공간 “Networked by IP” 사람 컴퓨터 사물 미래 전자공간 “Ubiquitous space Networked by IP Through WPAN” *Matsushita Electric president Kunio Nakamura at CEATEC JAPAN*1 2001 93

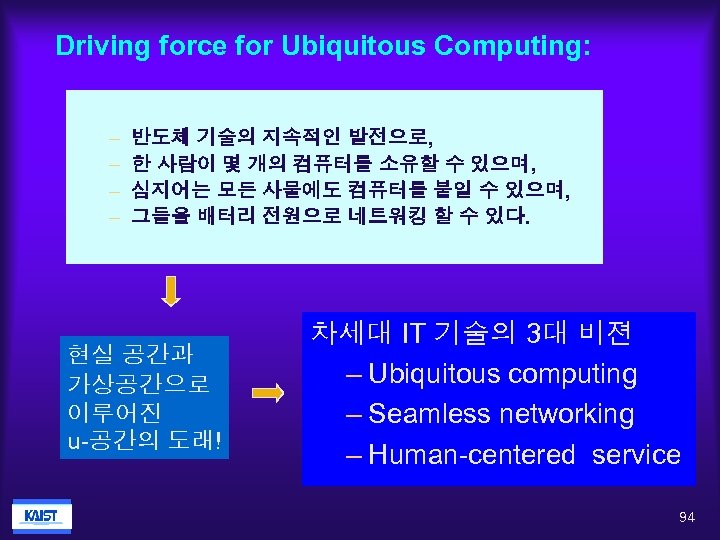

Driving force for Ubiquitous Computing: – – 반도체 기술의 지속적인 발전으로, 한 사람이 몇 개의 컴퓨터를 소유할 수 있으며, 심지어는 모든 사물에도 컴퓨터를 붙일 수 있으며, 그들을 배터리 전원으로 네트워킹 할 수 있다. 현실 공간과 가상공간으로 이루어진 u-공간의 도래! 차세대 IT 기술의 3대 비젼 – Ubiquitous computing – Seamless networking – Human-centered service 94

Driving force for Ubiquitous Computing: – – 반도체 기술의 지속적인 발전으로, 한 사람이 몇 개의 컴퓨터를 소유할 수 있으며, 심지어는 모든 사물에도 컴퓨터를 붙일 수 있으며, 그들을 배터리 전원으로 네트워킹 할 수 있다. 현실 공간과 가상공간으로 이루어진 u-공간의 도래! 차세대 IT 기술의 3대 비젼 – Ubiquitous computing – Seamless networking – Human-centered service 94

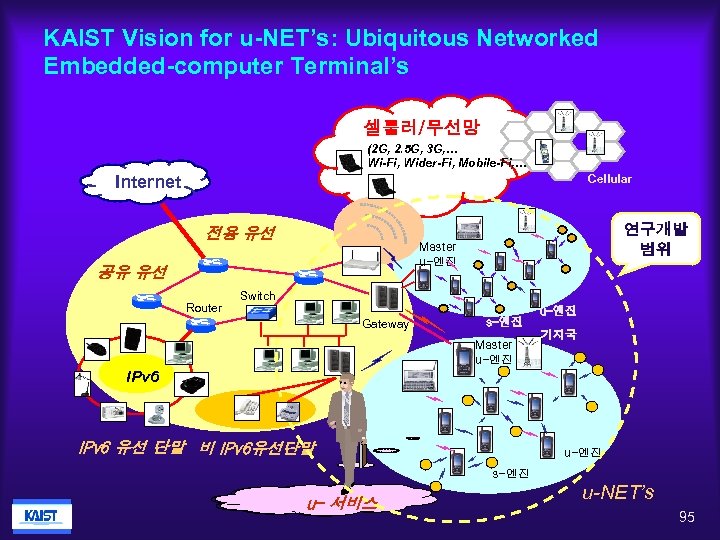

KAIST Vision for u-NET’s: Ubiquitous Networked Embedded-computer Terminal’s 셀룰러/무선망 (2 G, 2. 5 G, 3 G, … Wi-Fi, Wider-Fi, Mobile-Fi, … Internet Cellular 전용 유선 Master u-엔진 공유 유선 Router 연구개발 범위 Switch Gateway s-엔진 Master u-엔진 기지국 IPv 6 유선 단말 비 IPv 6유선단말 u-엔진 s-엔진 u- 서비스 u-NET’s 95

KAIST Vision for u-NET’s: Ubiquitous Networked Embedded-computer Terminal’s 셀룰러/무선망 (2 G, 2. 5 G, 3 G, … Wi-Fi, Wider-Fi, Mobile-Fi, … Internet Cellular 전용 유선 Master u-엔진 공유 유선 Router 연구개발 범위 Switch Gateway s-엔진 Master u-엔진 기지국 IPv 6 유선 단말 비 IPv 6유선단말 u-엔진 s-엔진 u- 서비스 u-NET’s 95

u-NET’s for Local Area Web 96

u-NET’s for Local Area Web 96

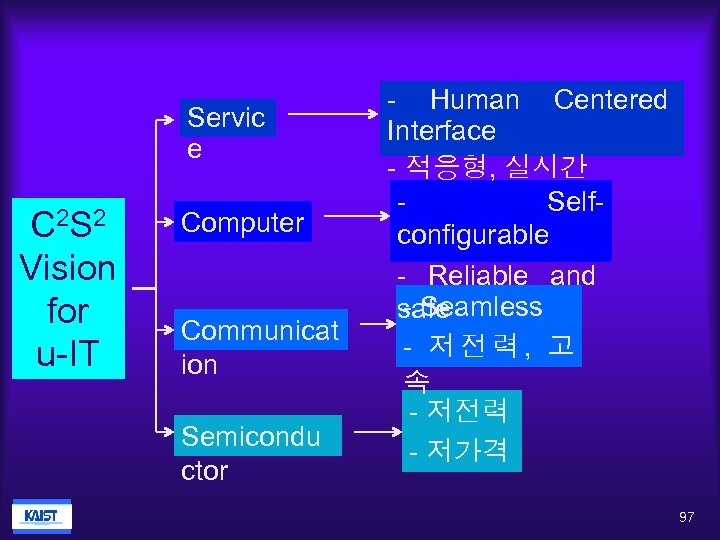

Servic e C 2 S 2 Vision for u-IT Computer Communicat ion Semicondu ctor - Human Centered Interface - 적응형, 실시간 Selfconfigurable - Reliable and - Seamless safe - 저전력, 고 속 - 저전력 - 저가격 97

Servic e C 2 S 2 Vision for u-IT Computer Communicat ion Semicondu ctor - Human Centered Interface - 적응형, 실시간 Selfconfigurable - Reliable and - Seamless safe - 저전력, 고 속 - 저전력 - 저가격 97

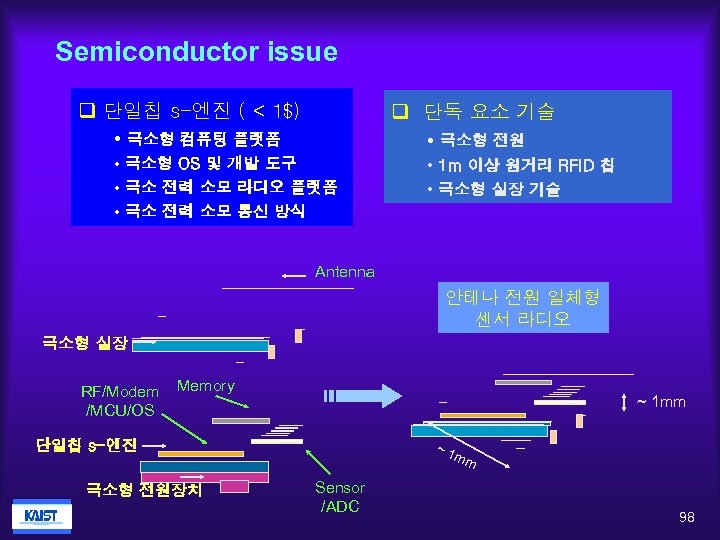

Semiconductor issue q 단일칩 s-엔진 ( < 1$) q 단독 요소 기술 • 극소형 컴퓨팅 플랫폼 • 극소형 전원 • 극소형 OS 및 개발 도구 • 극소 전력 소모 라디오 플랫폼 • 극소 전력 소모 통신 방식 • 1 m 이상 원거리 RFID 칩 • 극소형 실장 기술 Antenna 안테나 전원 일체형 센서 라디오 극소형 실장 RF/Modem /MCU/OS Memory ~ 1 mm 단일칩 s-엔진 극소형 전원장치 ~1 mm Sensor /ADC 98

Semiconductor issue q 단일칩 s-엔진 ( < 1$) q 단독 요소 기술 • 극소형 컴퓨팅 플랫폼 • 극소형 전원 • 극소형 OS 및 개발 도구 • 극소 전력 소모 라디오 플랫폼 • 극소 전력 소모 통신 방식 • 1 m 이상 원거리 RFID 칩 • 극소형 실장 기술 Antenna 안테나 전원 일체형 센서 라디오 극소형 실장 RF/Modem /MCU/OS Memory ~ 1 mm 단일칩 s-엔진 극소형 전원장치 ~1 mm Sensor /ADC 98

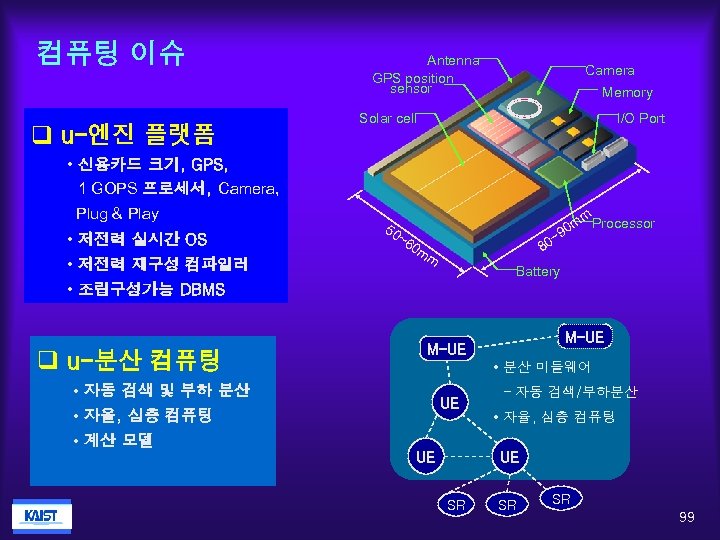

컴퓨팅 이슈 q u-엔진 플랫폼 Antenna GPS position sensor Camera Memory Solar cell I/O Port • 신용카드 크기, GPS, 1 GOPS 프로세서, Camera, Plug & Play • 저전력 실시간 OS • 저전력 재구성 컴파일러 50 ~ m 0 m Processor 9 ~ 60 mm 80 Battery • 조립구성가능 DBMS q u-분산 컴퓨팅 M-UE • 분산 미들웨어 • 자동 검색 및 부하 분산 UE • 자율, 심층 컴퓨팅 - 자동 검색/부하분산 • 자율, 심층 컴퓨팅 • 계산 모델 UE UE SR SR SR 99

컴퓨팅 이슈 q u-엔진 플랫폼 Antenna GPS position sensor Camera Memory Solar cell I/O Port • 신용카드 크기, GPS, 1 GOPS 프로세서, Camera, Plug & Play • 저전력 실시간 OS • 저전력 재구성 컴파일러 50 ~ m 0 m Processor 9 ~ 60 mm 80 Battery • 조립구성가능 DBMS q u-분산 컴퓨팅 M-UE • 분산 미들웨어 • 자동 검색 및 부하 분산 UE • 자율, 심층 컴퓨팅 - 자동 검색/부하분산 • 자율, 심층 컴퓨팅 • 계산 모델 UE UE SR SR SR 99

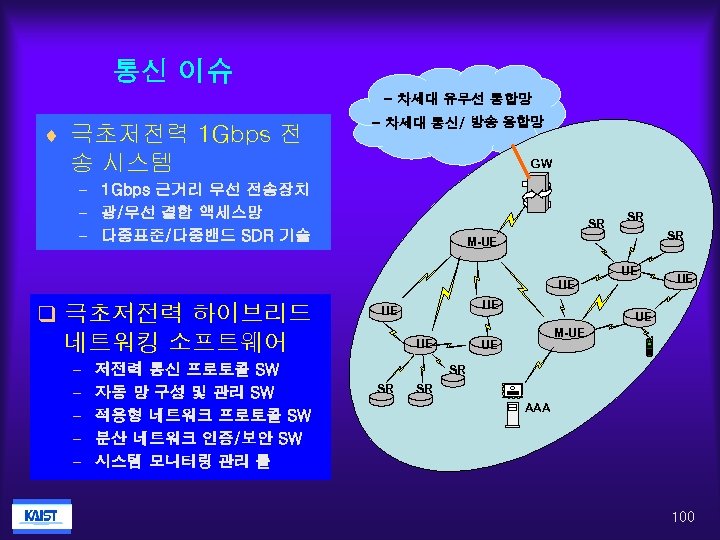

통신 이슈 - 차세대 유무선 통합망 ¨ 극초저전력 1 Gbps 전 - 차세대 통신/ 방송 융합망 송 시스템 GW – 1 Gbps 근거리 무선 전송장치 – 광/무선 결합 액세스망 – 다중표준/다중밴드 SDR 기술 SR SR SR M-UE UE UE q 극초저전력 하이브리드 네트워킹 소프트웨어 – – – 저전력 통신 프로토콜 SW 자동 망 구성 및 관리 SW 적응형 네트워크 프로토콜 SW 분산 네트워크 인증/보안 SW 시스템 모니터링 관리 툴 UE UE UE M-UE UE SR SR SR AAA 100

통신 이슈 - 차세대 유무선 통합망 ¨ 극초저전력 1 Gbps 전 - 차세대 통신/ 방송 융합망 송 시스템 GW – 1 Gbps 근거리 무선 전송장치 – 광/무선 결합 액세스망 – 다중표준/다중밴드 SDR 기술 SR SR SR M-UE UE UE q 극초저전력 하이브리드 네트워킹 소프트웨어 – – – 저전력 통신 프로토콜 SW 자동 망 구성 및 관리 SW 적응형 네트워크 프로토콜 SW 분산 네트워크 인증/보안 SW 시스템 모니터링 관리 툴 UE UE UE M-UE UE SR SR SR AAA 100

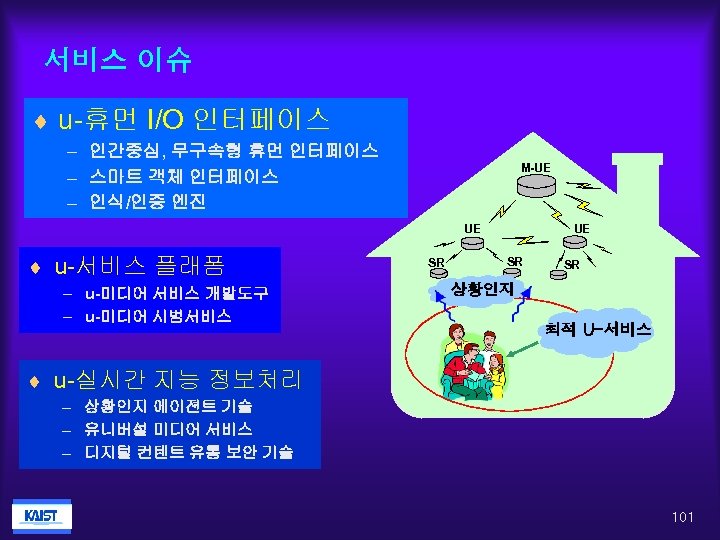

서비스 이슈 ¨ u-휴먼 I/O 인터페이스 – 인간중심, 무구속형 휴먼 인터페이스 – 스마트 객체 인터페이스 – 인식/인증 엔진 M-UE UE ¨ u-서비스 플래폼 – u-미디어 서비스 개발도구 – u-미디어 시범서비스 SR UE SR SR 상황인지 최적 U-서비스 ¨ u-실시간 지능 정보처리 – 상황인지 에이젼트 기술 – 유니버설 미디어 서비스 – 디지털 컨텐트 유통 보안 기술 101

서비스 이슈 ¨ u-휴먼 I/O 인터페이스 – 인간중심, 무구속형 휴먼 인터페이스 – 스마트 객체 인터페이스 – 인식/인증 엔진 M-UE UE ¨ u-서비스 플래폼 – u-미디어 서비스 개발도구 – u-미디어 시범서비스 SR UE SR SR 상황인지 최적 U-서비스 ¨ u-실시간 지능 정보처리 – 상황인지 에이젼트 기술 – 유니버설 미디어 서비스 – 디지털 컨텐트 유통 보안 기술 101

![u-산업 시장규모 규모 [조원] u-서비스 u-네트워크 u-분산 컴퓨팅 센서 라디오 586 총계 843 135 u-산업 시장규모 규모 [조원] u-서비스 u-네트워크 u-분산 컴퓨팅 센서 라디오 586 총계 843 135](https://present5.com/presentation/7faa883c6606fcb7c0373c4db21b454f/image-102.jpg) u-산업 시장규모 규모 [조원] u-서비스 u-네트워크 u-분산 컴퓨팅 센서 라디오 586 총계 843 135 총계 303 105 149 30 78 8 55 2005 2010 년도 참고: 일본 정보통신 총합 연구소 102

u-산업 시장규모 규모 [조원] u-서비스 u-네트워크 u-분산 컴퓨팅 센서 라디오 586 총계 843 135 총계 303 105 149 30 78 8 55 2005 2010 년도 참고: 일본 정보통신 총합 연구소 102

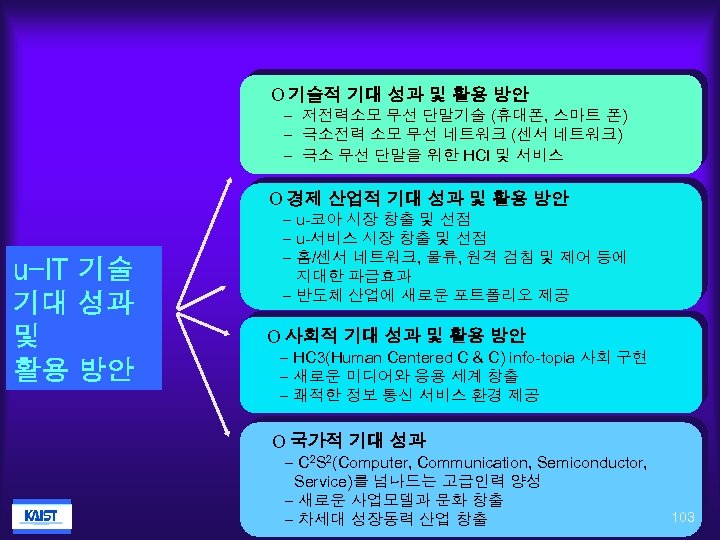

O 기술적 기대 성과 및 활용 방안 저전력소모 무선 단말기술 (휴대폰, 스마트 폰) 극소전력 소모 무선 네트워크 (센서 네트워크) 극소 무선 단말을 위한 HCI 및 서비스 O 경제 산업적 기대 성과 및 활용 방안 u-IT 기술 기대 성과 및 활용 방안 u-코아 시장 창출 및 선점 u-서비스 시장 창출 및 선점 홈/센서 네트워크, 물류, 원격 검침 및 제어 등에 지대한 파급효과 반도체 산업에 새로운 포트폴리오 제공 O 사회적 기대 성과 및 활용 방안 HC 3(Human Centered C & C) info-topia 사회 구현 새로운 미디어와 응용 세계 창출 쾌적한 정보 통신 서비스 환경 제공 O 국가적 기대 성과 C 2 S 2(Computer, Communication, Semiconductor, Service)를 넘나드는 고급인력 양성 새로운 사업모델과 문화 창출 차세대 성장동력 산업 창출 103

O 기술적 기대 성과 및 활용 방안 저전력소모 무선 단말기술 (휴대폰, 스마트 폰) 극소전력 소모 무선 네트워크 (센서 네트워크) 극소 무선 단말을 위한 HCI 및 서비스 O 경제 산업적 기대 성과 및 활용 방안 u-IT 기술 기대 성과 및 활용 방안 u-코아 시장 창출 및 선점 u-서비스 시장 창출 및 선점 홈/센서 네트워크, 물류, 원격 검침 및 제어 등에 지대한 파급효과 반도체 산업에 새로운 포트폴리오 제공 O 사회적 기대 성과 및 활용 방안 HC 3(Human Centered C & C) info-topia 사회 구현 새로운 미디어와 응용 세계 창출 쾌적한 정보 통신 서비스 환경 제공 O 국가적 기대 성과 C 2 S 2(Computer, Communication, Semiconductor, Service)를 넘나드는 고급인력 양성 새로운 사업모델과 문화 창출 차세대 성장동력 산업 창출 103

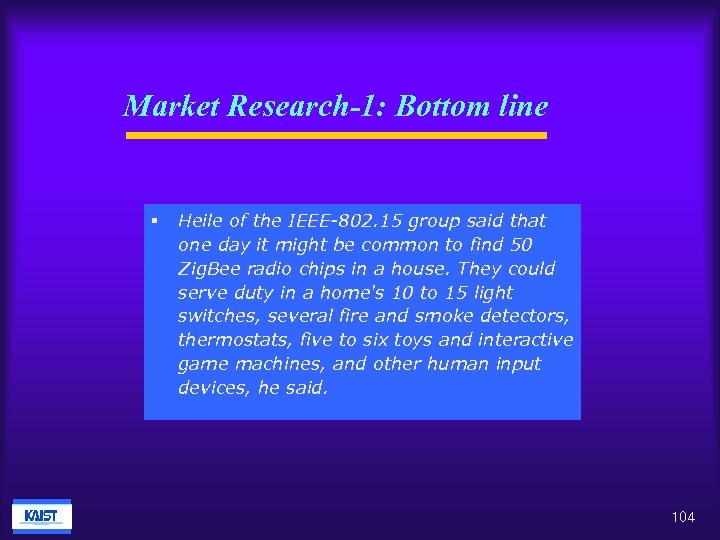

Market Research-1: Bottom line § Heile of the IEEE-802. 15 group said that one day it might be common to find 50 Zig. Bee radio chips in a house. They could serve duty in a home's 10 to 15 light switches, several fire and smoke detectors, thermostats, five to six toys and interactive game machines, and other human input devices, he said. 104

Market Research-1: Bottom line § Heile of the IEEE-802. 15 group said that one day it might be common to find 50 Zig. Bee radio chips in a house. They could serve duty in a home's 10 to 15 light switches, several fire and smoke detectors, thermostats, five to six toys and interactive game machines, and other human input devices, he said. 104

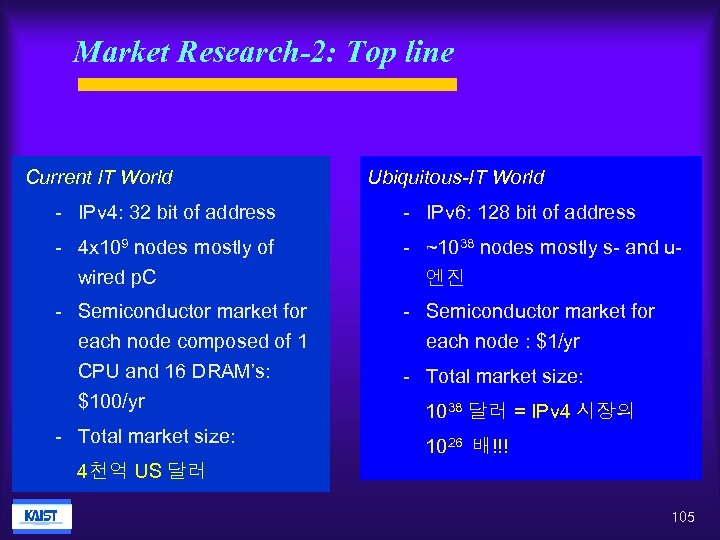

Market Research-2: Top line Current IT World Ubiquitous-IT World - IPv 4: 32 bit of address - IPv 6: 128 bit of address - 4 x 109 nodes mostly of - ~1038 nodes mostly s- and u- wired p. C - Semiconductor market for each node composed of 1 CPU and 16 DRAM’s: $100/yr - Total market size: 엔진 - Semiconductor market for each node : $1/yr - Total market size: 1038 달러 = IPv 4 시장의 1026 배!!! 4천억 US 달러 105

Market Research-2: Top line Current IT World Ubiquitous-IT World - IPv 4: 32 bit of address - IPv 6: 128 bit of address - 4 x 109 nodes mostly of - ~1038 nodes mostly s- and u- wired p. C - Semiconductor market for each node composed of 1 CPU and 16 DRAM’s: $100/yr - Total market size: 엔진 - Semiconductor market for each node : $1/yr - Total market size: 1038 달러 = IPv 4 시장의 1026 배!!! 4천억 US 달러 105

감사합니다 ! 인류의 행복을 위해서 무엇을 언제 어떻게 만들까? 주인님! 감시, 인식, 진단 등 단순 노동은 제게 맡기십시오 목표 1 : 스스로 필요한 기 술과 도구를 개발하며 이 것과 미래에 대한 비젼을 갖는 이상적인 기술인간, 궁금이 양성 목표 2 : 인간의 감시, 인식, 진단 등 단순 노동을 대신할 인조 충견, MICROS 창출 106

감사합니다 ! 인류의 행복을 위해서 무엇을 언제 어떻게 만들까? 주인님! 감시, 인식, 진단 등 단순 노동은 제게 맡기십시오 목표 1 : 스스로 필요한 기 술과 도구를 개발하며 이 것과 미래에 대한 비젼을 갖는 이상적인 기술인간, 궁금이 양성 목표 2 : 인간의 감시, 인식, 진단 등 단순 노동을 대신할 인조 충견, MICROS 창출 106

결론 & Epilog ¨ MICROS is recognized in overseas first after 6 years of effort. ¨ Accepted by domestic as well as international communities as an important ingredient for ubiquitous computing technology, new hope for IT industry. Waiting whether this is the gold mine or not. ¨ Other silicon consumption candidates: – – – MEMS? Bio chip? Lab on a chip? Solar cell? Amorphous silicon? …………. 107

결론 & Epilog ¨ MICROS is recognized in overseas first after 6 years of effort. ¨ Accepted by domestic as well as international communities as an important ingredient for ubiquitous computing technology, new hope for IT industry. Waiting whether this is the gold mine or not. ¨ Other silicon consumption candidates: – – – MEMS? Bio chip? Lab on a chip? Solar cell? Amorphous silicon? …………. 107

유럽편-이탈리아 ST마이크로일렉트로닉스 62년 지리적 악조건을 무릅쓰고 지역의 인재를 2003. 10. 21 [세계는 지금 '융합기술' 전쟁](9)유럽편-이탈리아 ST마이크로일렉트로닉스 62년 지리적 악조건을 무릅쓰고 지역의 인재를](https://present5.com/presentation/7faa883c6606fcb7c0373c4db21b454f/image-108.jpg) 2003. 10. 21 [세계는 지금 '융합기술' 전쟁](9)유럽편-이탈리아 ST마이크로일렉트로닉스 62년 지리적 악조건을 무릅쓰고 지역의 인재를 등용하고 경제를 일으키기 위해 시작한 아날로그 반도체 연구개발이 모태가 돼 세계적 반도체업체로 성 장한 ST는 이 카타니아 연구소와 생산공장을 발판으로 향후 10년을 대비한 포스트 실리콘 연구에 심혈을 기울이고 있다. ST의 차세대 기술 연구를 총괄하고 있는 살바토르 코파 SST(Soft computing, Si-optics and post-silicon Technologies)그룹 연구소장은 실 리콘 반도체 기술을 활용한 융합기술 개발의 중요성과 당위성을 새삼 강조했 다. “인류의 새 문명을 열어준 트랜지스터의 발명만큼 중요한 것이 지난 50년간 쌓은 실리콘 반도체 기술에 대한 노하우를 활용하는 것입니다. 실리콘처럼 전 인류가 매달려 소재의 특성을 파악하고 기술개발에 집중한 것도 전무할 것입 니다. 실리콘 기술을 기반으로 BT·NT 등 새로운 융합기술을 개발한다면 인류 는 새로운 IT의 세계를 앞당길 수 있다고 봅니다. ” 카타니아 연구소가 기반이 된 ST의 융합기술 개발은 바이오칩, 발광 실리 콘, 태양열 전지 등 기존 실리콘 반도체와는 다소 생경한 부문에 초점이 맞춰 져 있다. 그러나 이 모든 것이 나노미터급 실리콘 반도체 기술에 광학과 유기학 등을 결합한 것이라는 게 ST측의 설명. 또 월 수백만장의 웨이퍼(200㎜ 기준)를 가 공할 수 있는 전세계 반도체업체들의 무수한 생산라인을 재활용할 수 있다는 점에서도 아주 경제적이라는 게 ST측의 생각이다. ST는 이를 위해 세계 유수의 대학 및 연구소들과 광범위한 기술협력을 맺고 있다. 록펠러 재단으로부터는 바이오인포매틱스(bioinformatics)와 DNA칩 검 증 분야에 지원을 받고 있고, 모스크바 대학 및 러시아 과학 대학과는 실리콘 나노와이어 및 바이오일렉트로닉스에 협력하고 있다. 또한 이탈리아 국립 연구소 및 대학들과는 유기학 및 화학분야의 소재 합성 등에 대한 연구를 광범위하게 진행하고 있으며 샌디에이고 대학 및 버클리 대 학과는 복합 방법론 연구에 대해 협조하고 있다. 이같은 산학 협동은 ST의 차 세대 기술 연구방향을 명확하게 정의하고 연구인력의 교류, 연구설비의 공유 등을 통해 시너지 효과를 높이고 있다. ◇광합성 작용 응용한 저가형 태양전지=ST가 새롭게 도전장을 내민 곳은 나노기술 을 적용한 태양열 전지. 새로운 태양전지는 화석연료를 연소시키거나 핵 원자로 등의 전통적인 전기생성 방법과는 달리 햇빛에서 오는 에너지를 전기로 전환시켜 영구적으 로 사용할 수 있으면서도 제조비용을 낮추는데 초점이 맞춰져 있다. ◇CMOS 기술을 적용한 발광 실리콘=ST가 개발하고 있는 또하나의 융합기술은 발 광 반도체 기술. 가장 먼저 상용화가 가능할 것으로 보는 이 기술로 ST는 1∼ 2년내 옵 토커플러 시장에 진출한다는 계획을 밝혔다. 이 발광 디바이스는 이미 반도체 빛의 발산력 측정기준인 외부 총량 효율성이 팩터 1. 5로 기존 반도체 재료의 총량 효율성을 넘어섰으며 팩터 50까지 발산력을 최대로 증 가시킬 수 있다. 이는 실리콘 ㎟ 당 1 m. W 이상의 발광력을 만들어 내 빛의 효용성도 높 일 수 있다. ST는 이를 바탕으로 유기EL 등 차세대 디스플레이와 LED 같은 산업용 반도체 조명, 옵토 커플러 같은 제품을 만들어 상용화할 계획이다. ◇실리콘 기술의 총아, 바이오 테크놀러지=ST의 융합기술의 결정체는 바이오테크 놀러지에 모아져 있다. 카타니아의 200㎜ 웨이퍼 반도체 공장인 M 5 옆에는 연구소에 서 개발한 차세대 제품들을 테스트 생산해볼 수 있는 MEMS, 바이폴라, Bi-CMOS 등 다양한 시험 생산라인이 갖춰져 있었다. 기자가 찾아간 차세대 연구소 실험실에서는 연구원들이 혈액속의 DNA를 분석할 수 있는 바이오칩을 테스트 하느라 바쁘게 움직이고 있었다. MEMS 공정을 활용해 만들 었다는 이 바이오칩을 ST는 유럽의 유력 의학제품 제조업체들과 협력해 내년 대량생 산을 시작한다는 계획이다. ST는 인체내 질병을 진단하고 일부 치료까지 가능할 수 있는 인공지능의 바이오 센 서와 랩온어칩, 유체공학칩 등을 잇따라 개발해 바이오 일렉트로닉스의 새 장을 연다 는 전략을 세워놓고 있었다. ST의 유럽지역 연구개발을 총괄하는 리비오 발디 중앙 연구소장은 “포스트 실리콘 시대를 열어갈 대체제로 양자 컴퓨팅, 유기 디바이스, 탄소나노튜브 등이 있지만 어떤 것이 그 뒤를 이어갈지 아직 아무도 모른다”면서 “나노기술과 이를 접목한 융합기술의 개발은 앞으로를 대비한 경쟁력의 원천이 될 것”이라고 전망했다. 108

2003. 10. 21 [세계는 지금 '융합기술' 전쟁](9)유럽편-이탈리아 ST마이크로일렉트로닉스 62년 지리적 악조건을 무릅쓰고 지역의 인재를 등용하고 경제를 일으키기 위해 시작한 아날로그 반도체 연구개발이 모태가 돼 세계적 반도체업체로 성 장한 ST는 이 카타니아 연구소와 생산공장을 발판으로 향후 10년을 대비한 포스트 실리콘 연구에 심혈을 기울이고 있다. ST의 차세대 기술 연구를 총괄하고 있는 살바토르 코파 SST(Soft computing, Si-optics and post-silicon Technologies)그룹 연구소장은 실 리콘 반도체 기술을 활용한 융합기술 개발의 중요성과 당위성을 새삼 강조했 다. “인류의 새 문명을 열어준 트랜지스터의 발명만큼 중요한 것이 지난 50년간 쌓은 실리콘 반도체 기술에 대한 노하우를 활용하는 것입니다. 실리콘처럼 전 인류가 매달려 소재의 특성을 파악하고 기술개발에 집중한 것도 전무할 것입 니다. 실리콘 기술을 기반으로 BT·NT 등 새로운 융합기술을 개발한다면 인류 는 새로운 IT의 세계를 앞당길 수 있다고 봅니다. ” 카타니아 연구소가 기반이 된 ST의 융합기술 개발은 바이오칩, 발광 실리 콘, 태양열 전지 등 기존 실리콘 반도체와는 다소 생경한 부문에 초점이 맞춰 져 있다. 그러나 이 모든 것이 나노미터급 실리콘 반도체 기술에 광학과 유기학 등을 결합한 것이라는 게 ST측의 설명. 또 월 수백만장의 웨이퍼(200㎜ 기준)를 가 공할 수 있는 전세계 반도체업체들의 무수한 생산라인을 재활용할 수 있다는 점에서도 아주 경제적이라는 게 ST측의 생각이다. ST는 이를 위해 세계 유수의 대학 및 연구소들과 광범위한 기술협력을 맺고 있다. 록펠러 재단으로부터는 바이오인포매틱스(bioinformatics)와 DNA칩 검 증 분야에 지원을 받고 있고, 모스크바 대학 및 러시아 과학 대학과는 실리콘 나노와이어 및 바이오일렉트로닉스에 협력하고 있다. 또한 이탈리아 국립 연구소 및 대학들과는 유기학 및 화학분야의 소재 합성 등에 대한 연구를 광범위하게 진행하고 있으며 샌디에이고 대학 및 버클리 대 학과는 복합 방법론 연구에 대해 협조하고 있다. 이같은 산학 협동은 ST의 차 세대 기술 연구방향을 명확하게 정의하고 연구인력의 교류, 연구설비의 공유 등을 통해 시너지 효과를 높이고 있다. ◇광합성 작용 응용한 저가형 태양전지=ST가 새롭게 도전장을 내민 곳은 나노기술 을 적용한 태양열 전지. 새로운 태양전지는 화석연료를 연소시키거나 핵 원자로 등의 전통적인 전기생성 방법과는 달리 햇빛에서 오는 에너지를 전기로 전환시켜 영구적으 로 사용할 수 있으면서도 제조비용을 낮추는데 초점이 맞춰져 있다. ◇CMOS 기술을 적용한 발광 실리콘=ST가 개발하고 있는 또하나의 융합기술은 발 광 반도체 기술. 가장 먼저 상용화가 가능할 것으로 보는 이 기술로 ST는 1∼ 2년내 옵 토커플러 시장에 진출한다는 계획을 밝혔다. 이 발광 디바이스는 이미 반도체 빛의 발산력 측정기준인 외부 총량 효율성이 팩터 1. 5로 기존 반도체 재료의 총량 효율성을 넘어섰으며 팩터 50까지 발산력을 최대로 증 가시킬 수 있다. 이는 실리콘 ㎟ 당 1 m. W 이상의 발광력을 만들어 내 빛의 효용성도 높 일 수 있다. ST는 이를 바탕으로 유기EL 등 차세대 디스플레이와 LED 같은 산업용 반도체 조명, 옵토 커플러 같은 제품을 만들어 상용화할 계획이다. ◇실리콘 기술의 총아, 바이오 테크놀러지=ST의 융합기술의 결정체는 바이오테크 놀러지에 모아져 있다. 카타니아의 200㎜ 웨이퍼 반도체 공장인 M 5 옆에는 연구소에 서 개발한 차세대 제품들을 테스트 생산해볼 수 있는 MEMS, 바이폴라, Bi-CMOS 등 다양한 시험 생산라인이 갖춰져 있었다. 기자가 찾아간 차세대 연구소 실험실에서는 연구원들이 혈액속의 DNA를 분석할 수 있는 바이오칩을 테스트 하느라 바쁘게 움직이고 있었다. MEMS 공정을 활용해 만들 었다는 이 바이오칩을 ST는 유럽의 유력 의학제품 제조업체들과 협력해 내년 대량생 산을 시작한다는 계획이다. ST는 인체내 질병을 진단하고 일부 치료까지 가능할 수 있는 인공지능의 바이오 센 서와 랩온어칩, 유체공학칩 등을 잇따라 개발해 바이오 일렉트로닉스의 새 장을 연다 는 전략을 세워놓고 있었다. ST의 유럽지역 연구개발을 총괄하는 리비오 발디 중앙 연구소장은 “포스트 실리콘 시대를 열어갈 대체제로 양자 컴퓨팅, 유기 디바이스, 탄소나노튜브 등이 있지만 어떤 것이 그 뒤를 이어갈지 아직 아무도 모른다”면서 “나노기술과 이를 접목한 융합기술의 개발은 앞으로를 대비한 경쟁력의 원천이 될 것”이라고 전망했다. 108