df7f010d67757a18fa0f3e4cfd5a76e7.ppt

- Количество слайдов: 24

Implementation of Industrial FPGA Synthesis Flow Revisited Alan Mishchenko UC Berkeley 1

Implementation of Industrial FPGA Synthesis Flow Revisited Alan Mishchenko UC Berkeley 1

Overview Ø Introduction l l l Ø Motivation Structure of FPGA synthesis flow Overview of the previous system Lessons learned while developing new system l l l Verilog parsing Design representation Netlist datastructure Integration of application packages Customization Experimental results Ø Future work Ø 2

Overview Ø Introduction l l l Ø Motivation Structure of FPGA synthesis flow Overview of the previous system Lessons learned while developing new system l l l Verilog parsing Design representation Netlist datastructure Integration of application packages Customization Experimental results Ø Future work Ø 2

Motivation Ø Ø Ø ABC is a logic synthesis and verification tool developed at Berkeley (http: //www. bvsrc. org/) ABC has been in public domain since 2005, but it does not meet all of the industrial requirements New system is needed to fill the gap Magic was an industrial version of ABC developed in 2010 and used by several companies A new system to enhance ABC and replace Magic is being developed at this time This presentation shares this experience 3

Motivation Ø Ø Ø ABC is a logic synthesis and verification tool developed at Berkeley (http: //www. bvsrc. org/) ABC has been in public domain since 2005, but it does not meet all of the industrial requirements New system is needed to fill the gap Magic was an industrial version of ABC developed in 2010 and used by several companies A new system to enhance ABC and replace Magic is being developed at this time This presentation shares this experience 3

What Is Missing in ABC? Ø The baseline version of ABC is not applicable to industrial designs because it does not support l l Complex flops Multiple clock domains Special objects (adders, RAMs, DSPs, etc) Standard-cell libraries 4

What Is Missing in ABC? Ø The baseline version of ABC is not applicable to industrial designs because it does not support l l Complex flops Multiple clock domains Special objects (adders, RAMs, DSPs, etc) Standard-cell libraries 4

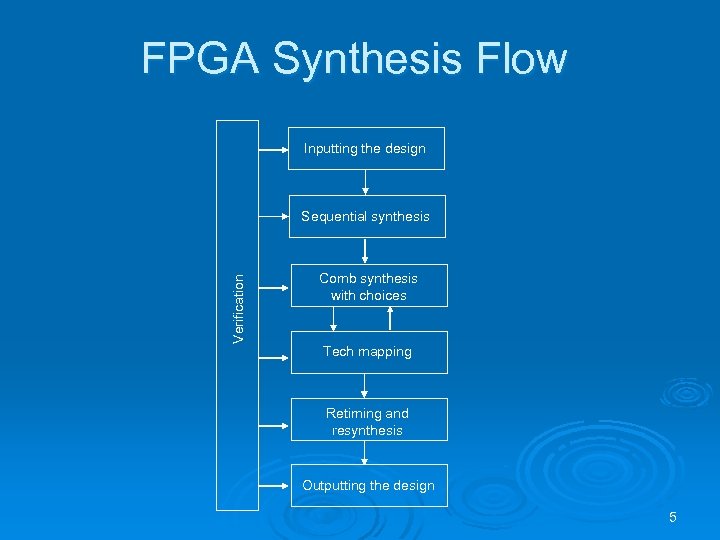

FPGA Synthesis Flow Inputting the design Verification Sequential synthesis Comb synthesis with choices Tech mapping Retiming and resynthesis Outputting the design 5

FPGA Synthesis Flow Inputting the design Verification Sequential synthesis Comb synthesis with choices Tech mapping Retiming and resynthesis Outputting the design 5

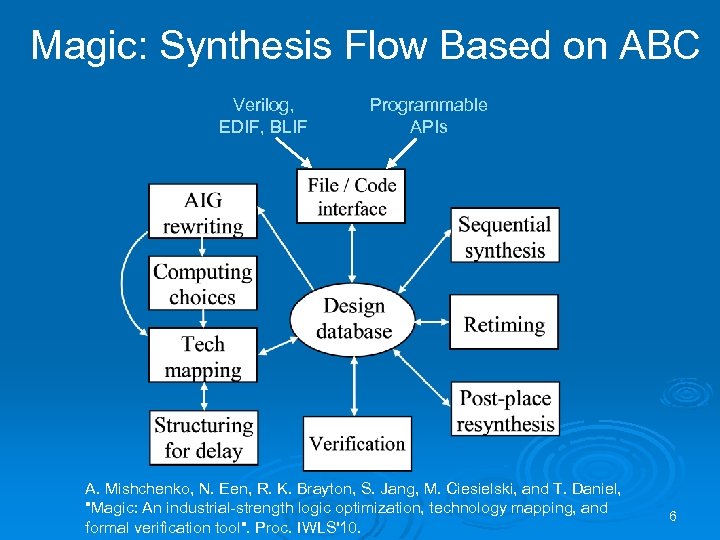

Magic: Synthesis Flow Based on ABC Verilog, EDIF, BLIF Programmable APIs A. Mishchenko, N. Een, R. K. Brayton, S. Jang, M. Ciesielski, and T. Daniel, "Magic: An industrial-strength logic optimization, technology mapping, and formal verification tool". Proc. IWLS'10. 6

Magic: Synthesis Flow Based on ABC Verilog, EDIF, BLIF Programmable APIs A. Mishchenko, N. Een, R. K. Brayton, S. Jang, M. Ciesielski, and T. Daniel, "Magic: An industrial-strength logic optimization, technology mapping, and formal verification tool". Proc. IWLS'10. 6

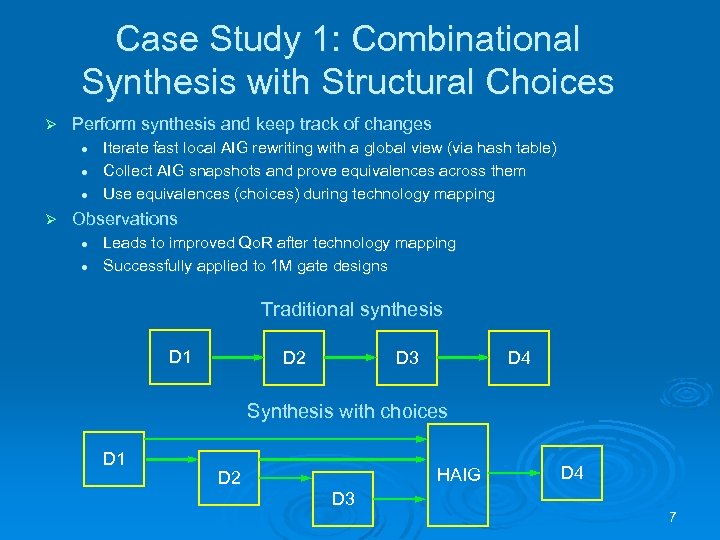

Case Study 1: Combinational Synthesis with Structural Choices Ø Perform synthesis and keep track of changes l l l Ø Iterate fast local AIG rewriting with a global view (via hash table) Collect AIG snapshots and prove equivalences across them Use equivalences (choices) during technology mapping Observations l l Leads to improved Qo. R after technology mapping Successfully applied to 1 M gate designs Traditional synthesis D 1 D 2 D 3 D 4 Synthesis with choices D 1 HAIG D 2 D 3 D 4 7

Case Study 1: Combinational Synthesis with Structural Choices Ø Perform synthesis and keep track of changes l l l Ø Iterate fast local AIG rewriting with a global view (via hash table) Collect AIG snapshots and prove equivalences across them Use equivalences (choices) during technology mapping Observations l l Leads to improved Qo. R after technology mapping Successfully applied to 1 M gate designs Traditional synthesis D 1 D 2 D 3 D 4 Synthesis with choices D 1 HAIG D 2 D 3 D 4 7

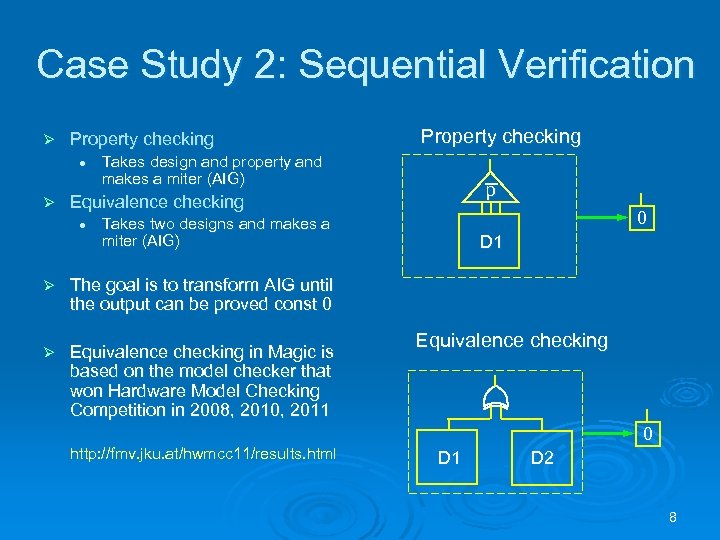

Case Study 2: Sequential Verification Ø Property checking l Ø Property checking Takes design and property and makes a miter (AIG) p Equivalence checking l 0 Takes two designs and makes a miter (AIG) Ø The goal is to transform AIG until the output can be proved const 0 Ø Equivalence checking in Magic is based on the model checker that won Hardware Model Checking Competition in 2008, 2010, 2011 D 1 http: //fmv. jku. at/hwmcc 11/results. html Equivalence checking 0 D 1 D 2 8

Case Study 2: Sequential Verification Ø Property checking l Ø Property checking Takes design and property and makes a miter (AIG) p Equivalence checking l 0 Takes two designs and makes a miter (AIG) Ø The goal is to transform AIG until the output can be proved const 0 Ø Equivalence checking in Magic is based on the model checker that won Hardware Model Checking Competition in 2008, 2010, 2011 D 1 http: //fmv. jku. at/hwmcc 11/results. html Equivalence checking 0 D 1 D 2 8

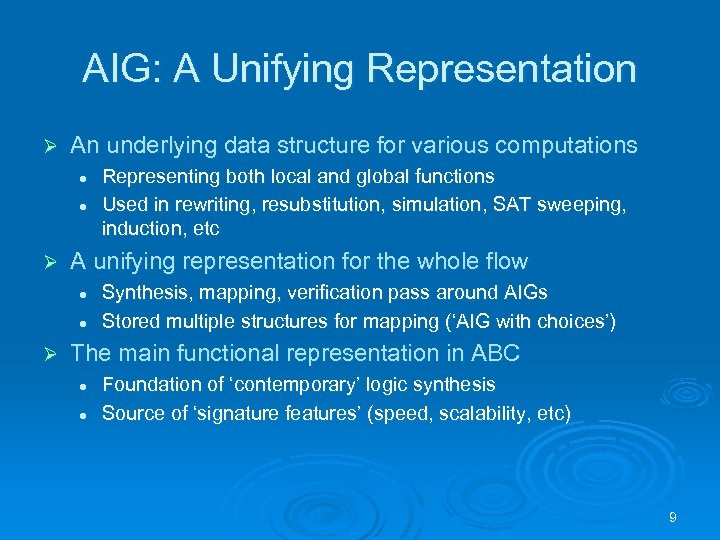

AIG: A Unifying Representation Ø An underlying data structure for various computations l l Ø A unifying representation for the whole flow l l Ø Representing both local and global functions Used in rewriting, resubstitution, simulation, SAT sweeping, induction, etc Synthesis, mapping, verification pass around AIGs Stored multiple structures for mapping (‘AIG with choices’) The main functional representation in ABC l l Foundation of ‘contemporary’ logic synthesis Source of ‘signature features’ (speed, scalability, etc) 9

AIG: A Unifying Representation Ø An underlying data structure for various computations l l Ø A unifying representation for the whole flow l l Ø Representing both local and global functions Used in rewriting, resubstitution, simulation, SAT sweeping, induction, etc Synthesis, mapping, verification pass around AIGs Stored multiple structures for mapping (‘AIG with choices’) The main functional representation in ABC l l Foundation of ‘contemporary’ logic synthesis Source of ‘signature features’ (speed, scalability, etc) 9

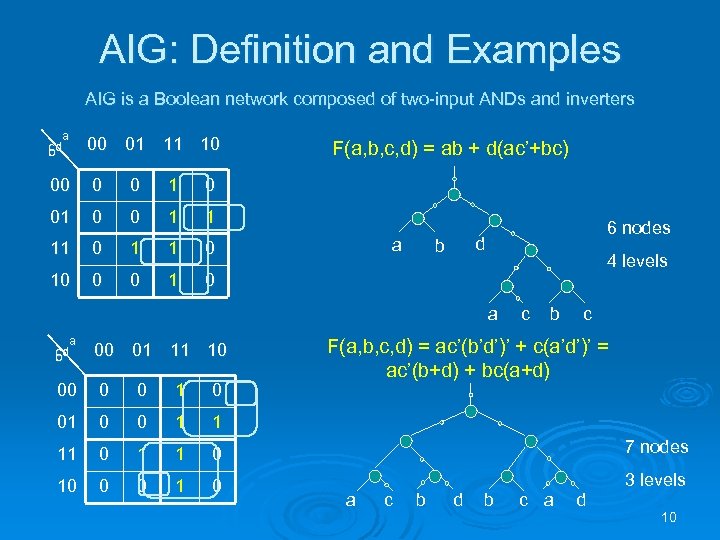

AIG: Definition and Examples AIG is a Boolean network composed of two-input ANDs and inverters a cd b 00 01 11 10 00 0 0 1 1 11 0 10 0 0 1 F(a, b, c, d) = ab + d(ac’+bc) 0 a 6 nodes d b 4 levels a a cd b 00 01 11 10 c b c F(a, b, c, d) = ac’(b’d’)’ + c(a’d’)’ = ac’(b+d) + bc(a+d) 00 0 0 1 1 11 0 1 1 0 7 nodes 10 0 0 1 0 3 levels a c b d b c a d 10

AIG: Definition and Examples AIG is a Boolean network composed of two-input ANDs and inverters a cd b 00 01 11 10 00 0 0 1 1 11 0 10 0 0 1 F(a, b, c, d) = ab + d(ac’+bc) 0 a 6 nodes d b 4 levels a a cd b 00 01 11 10 c b c F(a, b, c, d) = ac’(b’d’)’ + c(a’d’)’ = ac’(b+d) + bc(a+d) 00 0 0 1 1 11 0 1 1 0 7 nodes 10 0 0 1 0 3 levels a c b d b c a d 10

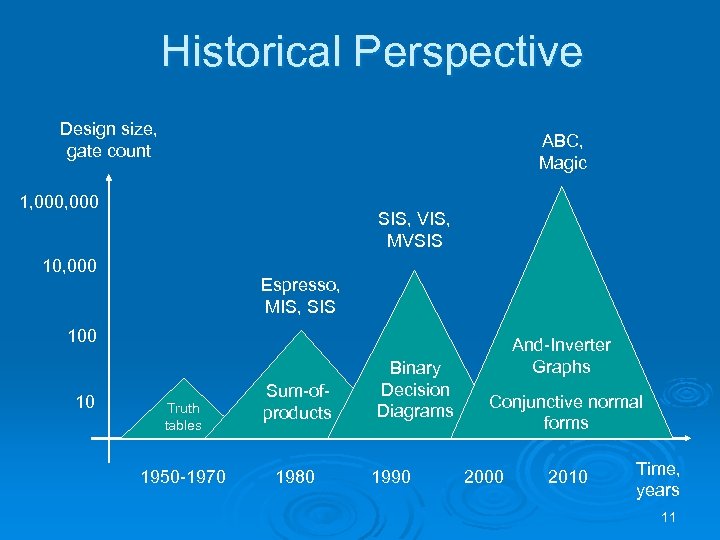

Historical Perspective Design size, gate count ABC, Magic 1, 000 SIS, VIS, MVSIS 10, 000 Espresso, MIS, SIS 100 10 Truth tables 1950 -1970 Sum-ofproducts 1980 Binary Decision Diagrams 1990 And-Inverter Graphs Conjunctive normal forms 2000 2010 Time, years 11

Historical Perspective Design size, gate count ABC, Magic 1, 000 SIS, VIS, MVSIS 10, 000 Espresso, MIS, SIS 100 10 Truth tables 1950 -1970 Sum-ofproducts 1980 Binary Decision Diagrams 1990 And-Inverter Graphs Conjunctive normal forms 2000 2010 Time, years 11

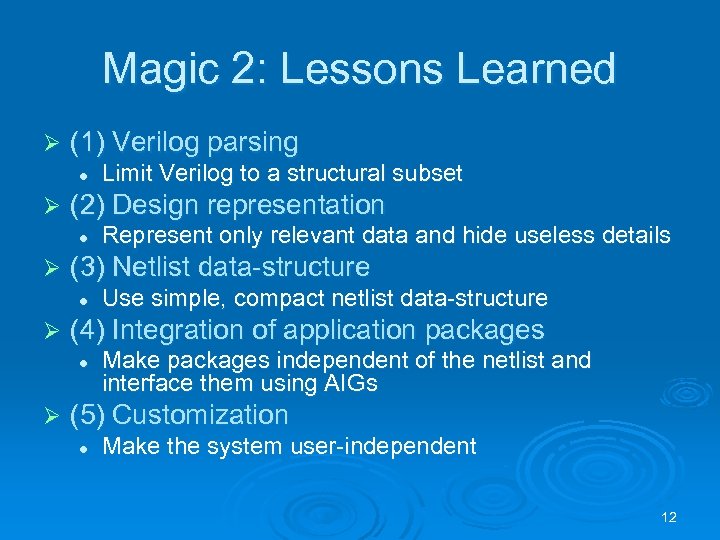

Magic 2: Lessons Learned Ø (1) Verilog parsing l Ø (2) Design representation l Ø Use simple, compact netlist data-structure (4) Integration of application packages l Ø Represent only relevant data and hide useless details (3) Netlist data-structure l Ø Limit Verilog to a structural subset Make packages independent of the netlist and interface them using AIGs (5) Customization l Make the system user-independent 12

Magic 2: Lessons Learned Ø (1) Verilog parsing l Ø (2) Design representation l Ø Use simple, compact netlist data-structure (4) Integration of application packages l Ø Represent only relevant data and hide useless details (3) Netlist data-structure l Ø Limit Verilog to a structural subset Make packages independent of the netlist and interface them using AIGs (5) Customization l Make the system user-independent 12

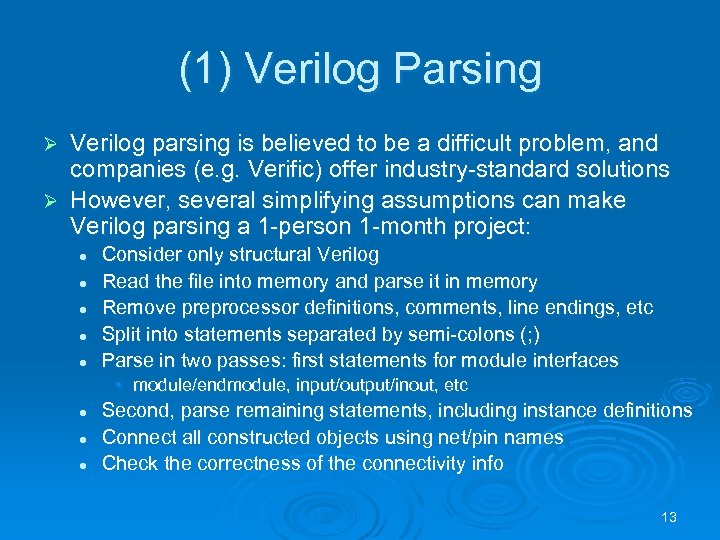

(1) Verilog Parsing Verilog parsing is believed to be a difficult problem, and companies (e. g. Verific) offer industry-standard solutions Ø However, several simplifying assumptions can make Verilog parsing a 1 -person 1 -month project: Ø l l l Consider only structural Verilog Read the file into memory and parse it in memory Remove preprocessor definitions, comments, line endings, etc Split into statements separated by semi-colons (; ) Parse in two passes: first statements for module interfaces • module/endmodule, input/output/inout, etc l l l Second, parse remaining statements, including instance definitions Connect all constructed objects using net/pin names Check the correctness of the connectivity info 13

(1) Verilog Parsing Verilog parsing is believed to be a difficult problem, and companies (e. g. Verific) offer industry-standard solutions Ø However, several simplifying assumptions can make Verilog parsing a 1 -person 1 -month project: Ø l l l Consider only structural Verilog Read the file into memory and parse it in memory Remove preprocessor definitions, comments, line endings, etc Split into statements separated by semi-colons (; ) Parse in two passes: first statements for module interfaces • module/endmodule, input/output/inout, etc l l l Second, parse remaining statements, including instance definitions Connect all constructed objects using net/pin names Check the correctness of the connectivity info 13

![Example module add 2( A, B, S, CO ); input [1: 0] A , Example module add 2( A, B, S, CO ); input [1: 0] A ,](https://present5.com/presentation/df7f010d67757a18fa0f3e4cfd5a76e7/image-14.jpg) Example module add 2( A, B, S, CO ); input [1: 0] A , B; output CO, S[1: 0]; wire n 1; fadd inst 1 (. ci(1’b 0), . a(A[0]), . b(B[0]), . s(S[0]) , . co(n 1) ); fadd inst 2 (. ci(n 1), . a(A[1]), . b(B[1]), . s(S[1]) , . co(CO) ); endmodule fadd( ci, a, b, s, co ); input ci, a, b; output s, co; assign s = ci ^ a ^ b; assign co = (ci & a) | (ci & b) | (a & b); endmodule 14

Example module add 2( A, B, S, CO ); input [1: 0] A , B; output CO, S[1: 0]; wire n 1; fadd inst 1 (. ci(1’b 0), . a(A[0]), . b(B[0]), . s(S[0]) , . co(n 1) ); fadd inst 2 (. ci(n 1), . a(A[1]), . b(B[1]), . s(S[1]) , . co(CO) ); endmodule fadd( ci, a, b, s, co ); input ci, a, b; output s, co; assign s = ci ^ a ^ b; assign co = (ci & a) | (ci & b) | (a & b); endmodule 14

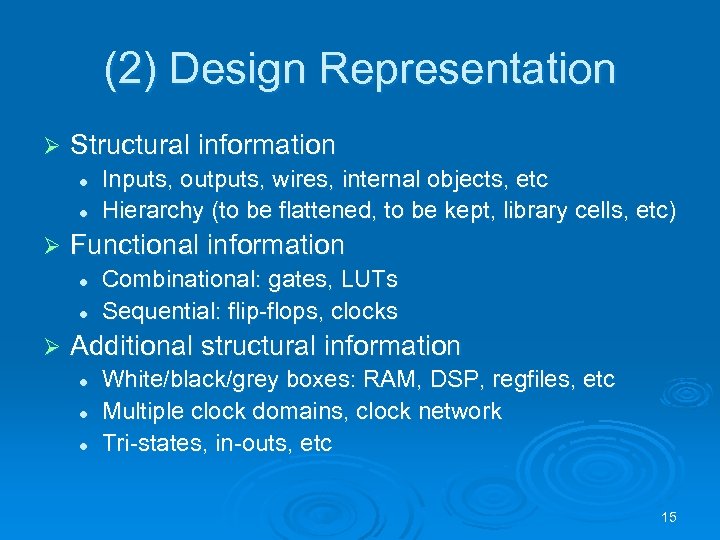

(2) Design Representation Ø Structural information l l Ø Functional information l l Ø Inputs, outputs, wires, internal objects, etc Hierarchy (to be flattened, to be kept, library cells, etc) Combinational: gates, LUTs Sequential: flip-flops, clocks Additional structural information l l l White/black/grey boxes: RAM, DSP, regfiles, etc Multiple clock domains, clock network Tri-states, in-outs, etc 15

(2) Design Representation Ø Structural information l l Ø Functional information l l Ø Inputs, outputs, wires, internal objects, etc Hierarchy (to be flattened, to be kept, library cells, etc) Combinational: gates, LUTs Sequential: flip-flops, clocks Additional structural information l l l White/black/grey boxes: RAM, DSP, regfiles, etc Multiple clock domains, clock network Tri-states, in-outs, etc 15

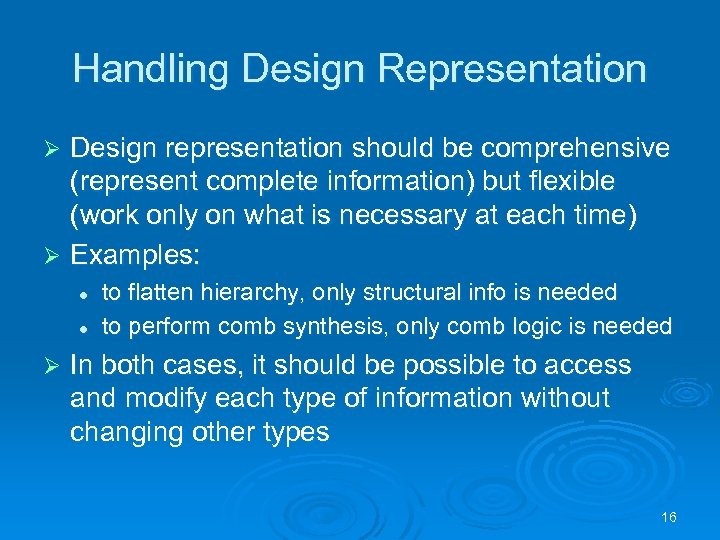

Handling Design Representation Design representation should be comprehensive (represent complete information) but flexible (work only on what is necessary at each time) Ø Examples: Ø l l Ø to flatten hierarchy, only structural info is needed to perform comb synthesis, only comb logic is needed In both cases, it should be possible to access and modify each type of information without changing other types 16

Handling Design Representation Design representation should be comprehensive (represent complete information) but flexible (work only on what is necessary at each time) Ø Examples: Ø l l Ø to flatten hierarchy, only structural info is needed to perform comb synthesis, only comb logic is needed In both cases, it should be possible to access and modify each type of information without changing other types 16

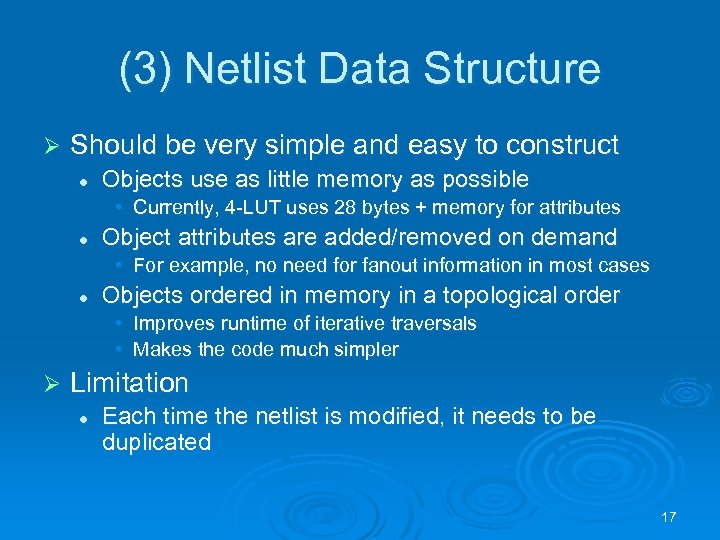

(3) Netlist Data Structure Ø Should be very simple and easy to construct l Objects use as little memory as possible • Currently, 4 -LUT uses 28 bytes + memory for attributes l Object attributes are added/removed on demand • For example, no need for fanout information in most cases l Objects ordered in memory in a topological order • Improves runtime of iterative traversals • Makes the code much simpler Ø Limitation l Each time the netlist is modified, it needs to be duplicated 17

(3) Netlist Data Structure Ø Should be very simple and easy to construct l Objects use as little memory as possible • Currently, 4 -LUT uses 28 bytes + memory for attributes l Object attributes are added/removed on demand • For example, no need for fanout information in most cases l Objects ordered in memory in a topological order • Improves runtime of iterative traversals • Makes the code much simpler Ø Limitation l Each time the netlist is modified, it needs to be duplicated 17

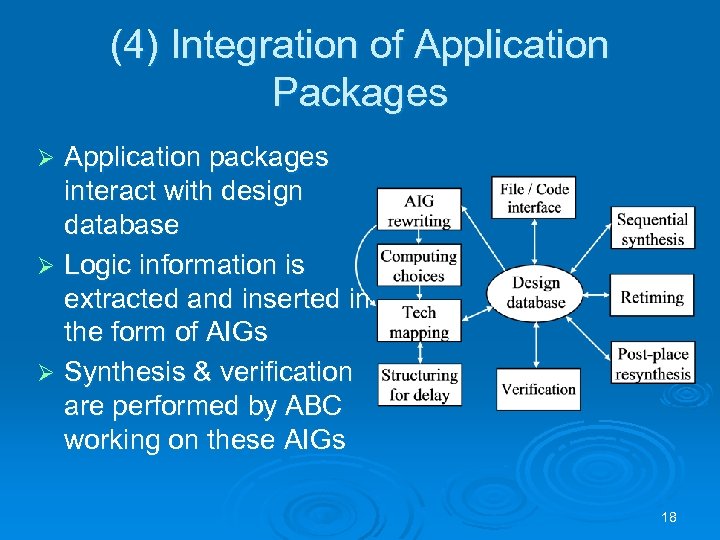

(4) Integration of Application Packages Application packages interact with design database Ø Logic information is extracted and inserted in the form of AIGs Ø Synthesis & verification are performed by ABC working on these AIGs Ø 18

(4) Integration of Application Packages Application packages interact with design database Ø Logic information is extracted and inserted in the form of AIGs Ø Synthesis & verification are performed by ABC working on these AIGs Ø 18

(5) Customization Ø The system should be easily customizable l l The source code is the same for all users Configuration files differ Ø Currently, the user “owns” the following: l l l The library of primitives (a Verilog file) Timing info for primitives (e. g. LUT pin delays) Timing models used for calculating data for boxes, complex flops, wires, etc 19

(5) Customization Ø The system should be easily customizable l l The source code is the same for all users Configuration files differ Ø Currently, the user “owns” the following: l l l The library of primitives (a Verilog file) Timing info for primitives (e. g. LUT pin delays) Timing models used for calculating data for boxes, complex flops, wires, etc 19

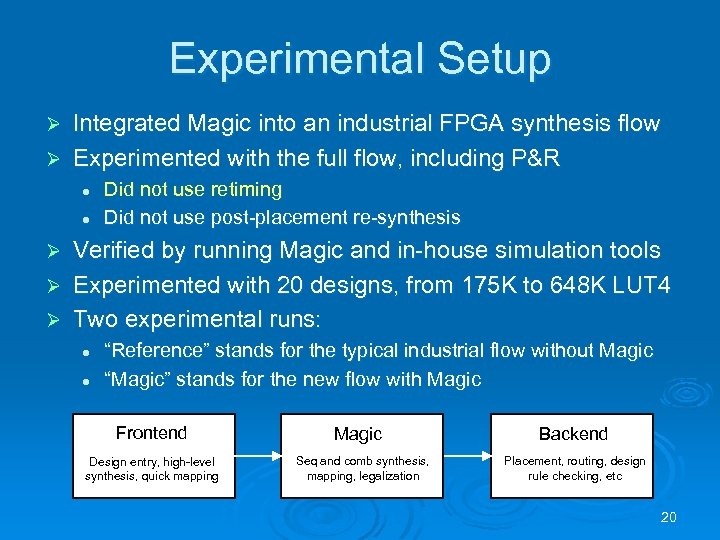

Experimental Setup Integrated Magic into an industrial FPGA synthesis flow Ø Experimented with the full flow, including P&R Ø l l Did not use retiming Did not use post-placement re-synthesis Verified by running Magic and in-house simulation tools Ø Experimented with 20 designs, from 175 K to 648 K LUT 4 Ø Two experimental runs: Ø l l “Reference” stands for the typical industrial flow without Magic “Magic” stands for the new flow with Magic Frontend Design entry, high-level synthesis, quick mapping Magic Seq and comb synthesis, mapping, legalization Backend Placement, routing, design rule checking, etc 20

Experimental Setup Integrated Magic into an industrial FPGA synthesis flow Ø Experimented with the full flow, including P&R Ø l l Did not use retiming Did not use post-placement re-synthesis Verified by running Magic and in-house simulation tools Ø Experimented with 20 designs, from 175 K to 648 K LUT 4 Ø Two experimental runs: Ø l l “Reference” stands for the typical industrial flow without Magic “Magic” stands for the new flow with Magic Frontend Design entry, high-level synthesis, quick mapping Magic Seq and comb synthesis, mapping, legalization Backend Placement, routing, design rule checking, etc 20

Experimental Results 21

Experimental Results 21

Cumulative Improvement (retiming excluded) 20. 00% Qo. R 10. 00% Improvement Pecentage 0. 00% Series 1 f. MAX 11. 80% LUT count -12. 70% Registers -9. 40% Levels -22. 30% Total Runtime P&R Runtime -3. 10% -50. 00% -10. 00% -20. 00% -30. 00% -40. 00% -50. 00% -60. 00% 22

Cumulative Improvement (retiming excluded) 20. 00% Qo. R 10. 00% Improvement Pecentage 0. 00% Series 1 f. MAX 11. 80% LUT count -12. 70% Registers -9. 40% Levels -22. 30% Total Runtime P&R Runtime -3. 10% -50. 00% -10. 00% -20. 00% -30. 00% -40. 00% -50. 00% -60. 00% 22

Future Work Ø Improve the integration l Ø Improve application packages l Ø AIG rewriting, tech-mapping, sequential synthesis, etc Integrate logic and physical synthesis l l Ø Simpler interfaces, better data consistency checking, etc Synthesis/mapping/retiming before placement Retiming/restructuring after placement Extend to work for various technologies l l Standard cells Macro cells LUT structures LUT/MUX structures 23

Future Work Ø Improve the integration l Ø Improve application packages l Ø AIG rewriting, tech-mapping, sequential synthesis, etc Integrate logic and physical synthesis l l Ø Simpler interfaces, better data consistency checking, etc Synthesis/mapping/retiming before placement Retiming/restructuring after placement Extend to work for various technologies l l Standard cells Macro cells LUT structures LUT/MUX structures 23

Abstract Ø This talk is inspired by the recent experiences gained while developing an industrial-strength system for FPGA synthesis and mapping. First, we review the design representation with "industrial stuff", such as black and while boxes, complex flops, multiple clock domains, tristates, inouts, etc, and how to handle them in the tool whose primary strength is applying combinational synthesis and mapping. Next, we discuss several ideas for implementing a custom Verilog parser for hierarchical designs. Finally, we propose a low-memory netlist representation used to store the data and interface various optimization engines. 24

Abstract Ø This talk is inspired by the recent experiences gained while developing an industrial-strength system for FPGA synthesis and mapping. First, we review the design representation with "industrial stuff", such as black and while boxes, complex flops, multiple clock domains, tristates, inouts, etc, and how to handle them in the tool whose primary strength is applying combinational synthesis and mapping. Next, we discuss several ideas for implementing a custom Verilog parser for hierarchical designs. Finally, we propose a low-memory netlist representation used to store the data and interface various optimization engines. 24