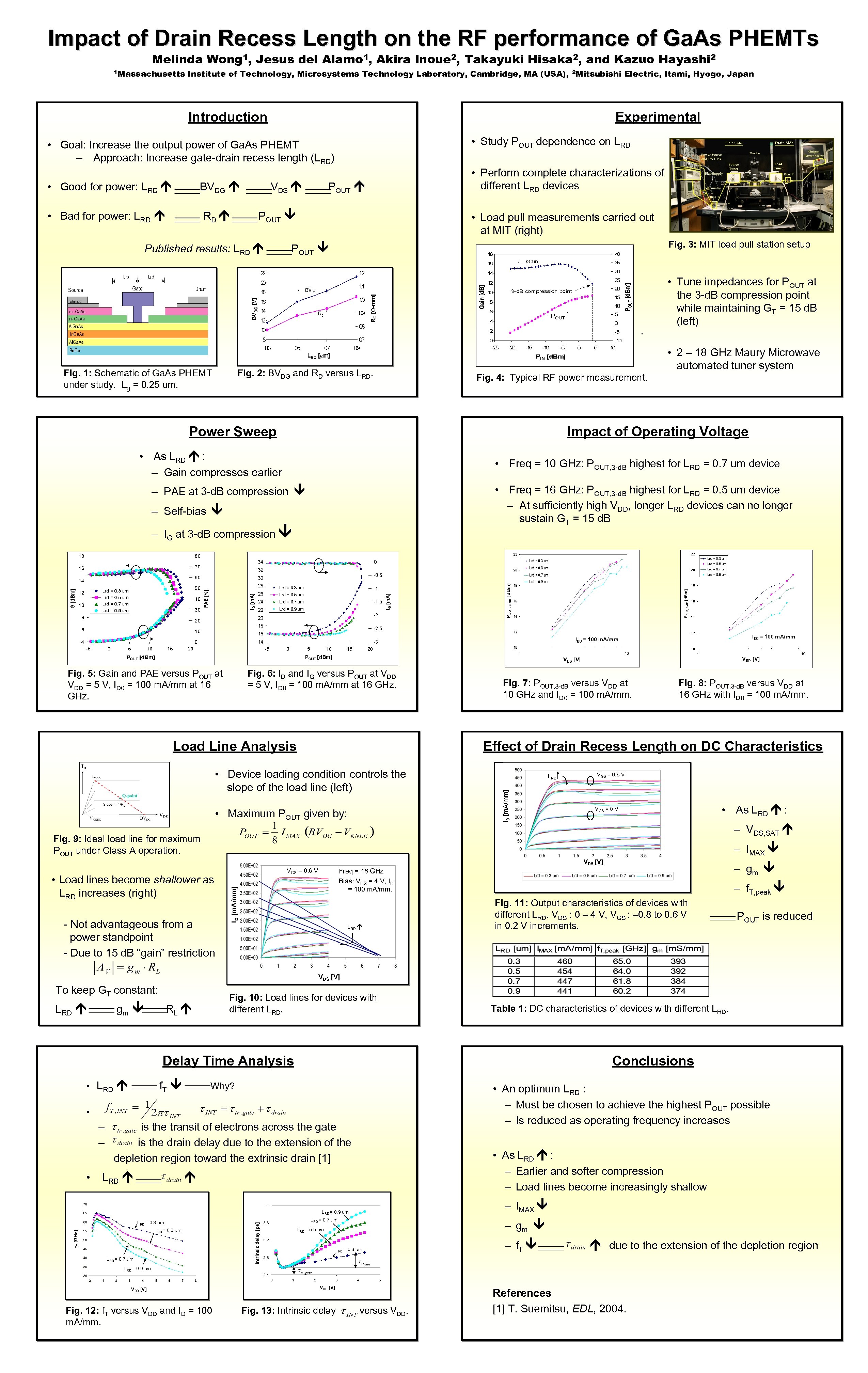

Impact of Drain Recess Length on the RF performance of Ga. As PHEMTs Melinda Wong 1, Jesus del Alamo 1, Akira Inoue 2, Takayuki Hisaka 2, and Kazuo Hayashi 2 1 Massachusetts Institute of Technology, Microsystems Technology Laboratory, Cambridge, MA (USA), 2 Mitsubishi Electric, Itami, Hyogo, Japan Introduction Experimental • Study POUT dependence on LRD • Goal: Increase the output power of Ga. As PHEMT – Approach: Increase gate-drain recess length (LRD) • Good for power: LRD BVDG • Bad for power: LRD VDS POUT Published results: LRD • Perform complete characterizations of different LRD devices • Load pull measurements carried out at MIT (right) Fig. 3: MIT load pull station setup POUT . Fig. 1: Schematic of Ga. As PHEMT under study. Lg = 0. 25 um. Fig. 2: BVDG and RD versus LRD. • 2 – 18 GHz Maury Microwave automated tuner system Fig. 4: Typical RF power measurement. Power Sweep Impact of Operating Voltage • As LRD : – Gain compresses earlier • Freq = 10 GHz: POUT, 3 -d. B highest for LRD = 0. 7 um device – PAE at 3 -d. B compression – Self-bias • Tune impedances for POUT at the 3 -d. B compression point while maintaining GT = 15 d. B (left) • Freq = 16 GHz: POUT, 3 -d. B highest for LRD = 0. 5 um device – At sufficiently high VDD, longer LRD devices can no longer sustain GT = 15 d. B – IG at 3 -d. B compression ID 0 = 100 m. A/mm VDD [V] Fig. 6: ID and IG versus POUT at VDD = 5 V, ID 0 = 100 m. A/mm at 16 GHz. Load Line Analysis Fig. 7: POUT, 3 -d. B versus VDD at 10 GHz and ID 0 = 100 m. A/mm. Fig. 8: POUT, 3 -d. B versus VDD at 16 GHz with ID 0 = 100 m. A/mm. Effect of Drain Recess Length on DC Characteristics • Device loading condition controls the slope of the load line (left) • Maximum POUT given by: LRD ID [m. A/mm] Fig. 5: Gain and PAE versus POUT at VDD = 5 V, ID 0 = 100 m. A/mm at 16 GHz. VGS = 0. 6 V VGS = 0 V • As LRD : – VDS, SAT Fig. 9: Ideal load line for maximum POUT under Class A operation. – IMAX VDS [V] - Not advantageous from a power standpoint - Due to 15 d. B “gain” restriction – f. T, peak – gm Freq = 16 GHz Bias: VDS = 4 V, ID = 100 m. A/mm. ID [m. A/mm] • Load lines become shallower as LRD increases (right) VGS = 0. 6 V LRD Fig. 11: Output characteristics of devices with different LRD. VDS : 0 – 4 V, VGS : – 0. 8 to 0. 6 V in 0. 2 V increments. POUT is reduced VDS [V] To keep GT constant: LRD gm Fig. 10: Load lines for devices with different LRD. RL Table 1: DC characteristics of devices with different LRD. Delay Time Analysis • LRD f. T Conclusions Why? • An optimum LRD : – Must be chosen to achieve the highest POUT possible – Is reduced as operating frequency increases • – – • is the transit of electrons across the gate is the drain delay due to the extension of the depletion region toward the extrinsic drain [1] LRD • As LRD : – Earlier and softer compression – Load lines become increasingly shallow – IMAX LRD = 0. 3 um f. T [GHz] LRD = 0. 5 um LRD = 0. 7 um LRD = 0. 9 um VDD [V] Fig. 12: f. T versus VDD and ID = 100 m. A/mm. Intrinsic delay [ps] LRD = 0. 9 um LRD = 0. 7 um – f. T – gm LRD = 0. 5 um LRD = 0. 3 um due to the extension of the depletion region t drain t tr , gate VDD [V] Fig. 13: Intrinsic delay versus VDD. References [1] T. Suemitsu, EDL, 2004.

Impact of Drain Recess Length on the RF performance of Ga. As PHEMTs Melinda Wong 1, Jesus del Alamo 1, Akira Inoue 2, Takayuki Hisaka 2, and Kazuo Hayashi 2 1 Massachusetts Institute of Technology, Microsystems Technology Laboratory, Cambridge, MA (USA), 2 Mitsubishi Electric, Itami, Hyogo, Japan Introduction Experimental • Study POUT dependence on LRD • Goal: Increase the output power of Ga. As PHEMT – Approach: Increase gate-drain recess length (LRD) • Good for power: LRD BVDG • Bad for power: LRD VDS POUT Published results: LRD • Perform complete characterizations of different LRD devices • Load pull measurements carried out at MIT (right) Fig. 3: MIT load pull station setup POUT . Fig. 1: Schematic of Ga. As PHEMT under study. Lg = 0. 25 um. Fig. 2: BVDG and RD versus LRD. • 2 – 18 GHz Maury Microwave automated tuner system Fig. 4: Typical RF power measurement. Power Sweep Impact of Operating Voltage • As LRD : – Gain compresses earlier • Freq = 10 GHz: POUT, 3 -d. B highest for LRD = 0. 7 um device – PAE at 3 -d. B compression – Self-bias • Tune impedances for POUT at the 3 -d. B compression point while maintaining GT = 15 d. B (left) • Freq = 16 GHz: POUT, 3 -d. B highest for LRD = 0. 5 um device – At sufficiently high VDD, longer LRD devices can no longer sustain GT = 15 d. B – IG at 3 -d. B compression ID 0 = 100 m. A/mm VDD [V] Fig. 6: ID and IG versus POUT at VDD = 5 V, ID 0 = 100 m. A/mm at 16 GHz. Load Line Analysis Fig. 7: POUT, 3 -d. B versus VDD at 10 GHz and ID 0 = 100 m. A/mm. Fig. 8: POUT, 3 -d. B versus VDD at 16 GHz with ID 0 = 100 m. A/mm. Effect of Drain Recess Length on DC Characteristics • Device loading condition controls the slope of the load line (left) • Maximum POUT given by: LRD ID [m. A/mm] Fig. 5: Gain and PAE versus POUT at VDD = 5 V, ID 0 = 100 m. A/mm at 16 GHz. VGS = 0. 6 V VGS = 0 V • As LRD : – VDS, SAT Fig. 9: Ideal load line for maximum POUT under Class A operation. – IMAX VDS [V] - Not advantageous from a power standpoint - Due to 15 d. B “gain” restriction – f. T, peak – gm Freq = 16 GHz Bias: VDS = 4 V, ID = 100 m. A/mm. ID [m. A/mm] • Load lines become shallower as LRD increases (right) VGS = 0. 6 V LRD Fig. 11: Output characteristics of devices with different LRD. VDS : 0 – 4 V, VGS : – 0. 8 to 0. 6 V in 0. 2 V increments. POUT is reduced VDS [V] To keep GT constant: LRD gm Fig. 10: Load lines for devices with different LRD. RL Table 1: DC characteristics of devices with different LRD. Delay Time Analysis • LRD f. T Conclusions Why? • An optimum LRD : – Must be chosen to achieve the highest POUT possible – Is reduced as operating frequency increases • – – • is the transit of electrons across the gate is the drain delay due to the extension of the depletion region toward the extrinsic drain [1] LRD • As LRD : – Earlier and softer compression – Load lines become increasingly shallow – IMAX LRD = 0. 3 um f. T [GHz] LRD = 0. 5 um LRD = 0. 7 um LRD = 0. 9 um VDD [V] Fig. 12: f. T versus VDD and ID = 100 m. A/mm. Intrinsic delay [ps] LRD = 0. 9 um LRD = 0. 7 um – f. T – gm LRD = 0. 5 um LRD = 0. 3 um due to the extension of the depletion region t drain t tr , gate VDD [V] Fig. 13: Intrinsic delay versus VDD. References [1] T. Suemitsu, EDL, 2004.