ea02003b62ac7b3173a07e7dcd162168.ppt

- Количество слайдов: 16

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 VLSI-SOC 2016 @ IFIP WG 10. 5 meeting Maksim Jenihhin Local Organization and Finance Chair Senior Research Fellow Tallinn University of Technology, Estonia

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 VLSI-SOC 2016 @ IFIP WG 10. 5 meeting Maksim Jenihhin Local Organization and Finance Chair Senior Research Fellow Tallinn University of Technology, Estonia

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 General details • 24 th edition, 35 years, the same age as me ; ) • Previous locations Edinburgh, Trondheim, Tokyo, Vancouver, Munich, Grenoble, Gramado, Lisbon, Montpellier, Darmstadt, Perth, Nice, Atlanta, Rhodes, Florianópolis, Madrid, Hong Kong, Santa Cruz, Istanbul, Playa del Carmen, and Daejeon in South Korea • Research and industrial results in EDA, design methodology, test, design, verification, devices, process, systems issues and application domains of VLSI and So. C • IFIP TC 10 Working Group 10. 5, IEEE CEDA and IEEE CASS Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 2

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 General details • 24 th edition, 35 years, the same age as me ; ) • Previous locations Edinburgh, Trondheim, Tokyo, Vancouver, Munich, Grenoble, Gramado, Lisbon, Montpellier, Darmstadt, Perth, Nice, Atlanta, Rhodes, Florianópolis, Madrid, Hong Kong, Santa Cruz, Istanbul, Playa del Carmen, and Daejeon in South Korea • Research and industrial results in EDA, design methodology, test, design, verification, devices, process, systems issues and application domains of VLSI and So. C • IFIP TC 10 Working Group 10. 5, IEEE CEDA and IEEE CASS Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 2

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 TUT Track Record – – – FPL 1998 ETS 2005 EAEEIE 2008 DDECS 2012 EWME 2014 Many Norchips, Nordic Test Forums, BECs • 2016 – Re. Co. So. C 2016, June 27 -29, 2016, Tallinn – IEEE BEC October 3 -5, 2016, Tallinn – ESWeek, October 2 -7, 2016, Pittsburgh, USA Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 3

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 TUT Track Record – – – FPL 1998 ETS 2005 EAEEIE 2008 DDECS 2012 EWME 2014 Many Norchips, Nordic Test Forums, BECs • 2016 – Re. Co. So. C 2016, June 27 -29, 2016, Tallinn – IEEE BEC October 3 -5, 2016, Tallinn – ESWeek, October 2 -7, 2016, Pittsburgh, USA Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 3

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Committees Steering Committee: General Chairs: Jaan Raik, Tallinn UT, Estonia Manfred Glesner, TU Darmstadt, Germany Ian O'Connor, ECL Lyon, France Salvador Mir, TIMA, France Program Chairs: Thomas Hollstein, Frankfurt UAS, Germany Michel Robert, U. Montpellier, France Krishnendu Chakrabarty, Duke University, USA Chi-Ying Tsui, HKUST, Hong Kong, China Publicity Chairs: Ricardo Reis, UFRGS, Brazil Matthew Guthaus, UC Santa Cruz, USA Masahiro Fujita, Tokyo Univ, Japan Ricardo Reis, UFRGS, Brazil Said Hamdioui, Delft Univ, Netherlands Luis Miguel Silveira, INESC ID, Portugal Special Session Chair: Matteo Sonza Reorda, POLITO, Italy Fatih Ugurdag, Ozyegin Univ. , Turkey Ph. D Forum Chair: Mario Schölzel, Potsdam Univ, Germany Finance/Local Chair: Maksim Jenihhin, Tallinn UT, Estonia Publication Chairs: Anton Tsertov, Tallinn UT, Estonia Sergei Kostin, Tallinn UT, Estonia Registration Chair: Siavoosh Azad, Tallinn UT, Estonia Web Chair: Tarmo Robal, Tallinn UT, Estonia Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 4

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Committees Steering Committee: General Chairs: Jaan Raik, Tallinn UT, Estonia Manfred Glesner, TU Darmstadt, Germany Ian O'Connor, ECL Lyon, France Salvador Mir, TIMA, France Program Chairs: Thomas Hollstein, Frankfurt UAS, Germany Michel Robert, U. Montpellier, France Krishnendu Chakrabarty, Duke University, USA Chi-Ying Tsui, HKUST, Hong Kong, China Publicity Chairs: Ricardo Reis, UFRGS, Brazil Matthew Guthaus, UC Santa Cruz, USA Masahiro Fujita, Tokyo Univ, Japan Ricardo Reis, UFRGS, Brazil Said Hamdioui, Delft Univ, Netherlands Luis Miguel Silveira, INESC ID, Portugal Special Session Chair: Matteo Sonza Reorda, POLITO, Italy Fatih Ugurdag, Ozyegin Univ. , Turkey Ph. D Forum Chair: Mario Schölzel, Potsdam Univ, Germany Finance/Local Chair: Maksim Jenihhin, Tallinn UT, Estonia Publication Chairs: Anton Tsertov, Tallinn UT, Estonia Sergei Kostin, Tallinn UT, Estonia Registration Chair: Siavoosh Azad, Tallinn UT, Estonia Web Chair: Tarmo Robal, Tallinn UT, Estonia Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 4

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Committees Technical Program Committee 91 members in total Track Chairs: José L. Ayala, Complutense University of Madrid, Spain Bernd Becker, University of Freiburg, Germany Lilian Bossuet, University St. Etienne, France Yiran Chen, University of Pittsburg, USA Jerzy Dabrowski, Linkoping University, Sweden Peeter Ellervee, Tallinn University of Technology, Estonia Ian Harris, University of California Irvine, USA Michael Hübner, Ruhr-Universität Bochum, Germany Mihalis Maniatakos, NYU Abu Dhabi, UAE Erik Larsson, Lund University, Sweden Makoto Nagata, Kobe University, Japan Tobias Noll, RWTH Aachen, Germany Zebo Peng, Linköping University, Sweden Graziano Pravadelli, University of Verona, Italy Dirk Stroobandt, Ghent University, Belgium Lionel Torres, LIRMM Montpellier, France Aida Todri-Sanial, LIRMM Montpellier, France Fatih Ugurdag, Ozyegin University, Turkey Vijaykrishnan Narayanan, Pennsylvania State University, USA Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 5

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Committees Technical Program Committee 91 members in total Track Chairs: José L. Ayala, Complutense University of Madrid, Spain Bernd Becker, University of Freiburg, Germany Lilian Bossuet, University St. Etienne, France Yiran Chen, University of Pittsburg, USA Jerzy Dabrowski, Linkoping University, Sweden Peeter Ellervee, Tallinn University of Technology, Estonia Ian Harris, University of California Irvine, USA Michael Hübner, Ruhr-Universität Bochum, Germany Mihalis Maniatakos, NYU Abu Dhabi, UAE Erik Larsson, Lund University, Sweden Makoto Nagata, Kobe University, Japan Tobias Noll, RWTH Aachen, Germany Zebo Peng, Linköping University, Sweden Graziano Pravadelli, University of Verona, Italy Dirk Stroobandt, Ghent University, Belgium Lionel Torres, LIRMM Montpellier, France Aida Todri-Sanial, LIRMM Montpellier, France Fatih Ugurdag, Ozyegin University, Turkey Vijaykrishnan Narayanan, Pennsylvania State University, USA Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 5

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Dates Abstract Submission: April 18, 2016 Paper Submission: April 25, 2016 Special Session Proposal: April 18, 2016 Review deadline: June 6, 2016 Notification of Acceptance: June 18, 2016 Camera-ready: July 10, 2016 Registration deadline: July 10, 2016 Conference: September 26 -28, 2016 Workshop: September 29 -30 or 28 afternoon-29, 2016 Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 6

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Dates Abstract Submission: April 18, 2016 Paper Submission: April 25, 2016 Special Session Proposal: April 18, 2016 Review deadline: June 6, 2016 Notification of Acceptance: June 18, 2016 Camera-ready: July 10, 2016 Registration deadline: July 10, 2016 Conference: September 26 -28, 2016 Workshop: September 29 -30 or 28 afternoon-29, 2016 Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 6

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Venue • VLSI-So. C 2016 will be held in Tallinn, Estonia • Well integrated: Schengen zone, Euro currency • Picturesque medieval Old Town (in the UNESCO World Heritage list) • The country of Skype and e-banking, e-voting, e-government Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 7

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Venue • VLSI-So. C 2016 will be held in Tallinn, Estonia • Well integrated: Schengen zone, Euro currency • Picturesque medieval Old Town (in the UNESCO World Heritage list) • The country of Skype and e-banking, e-voting, e-government Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 7

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Venue • VLSI-So. C 2016 will be held in Tallinn, Estonia – Park Inn by Radisson Meriton Conference & Spa Hotel – Special room rates for attendees Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 8

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Venue • VLSI-So. C 2016 will be held in Tallinn, Estonia – Park Inn by Radisson Meriton Conference & Spa Hotel – Special room rates for attendees Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 8

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Program at a glance Monday, Sept 26 Tuesday, Sept 27 Wednesday, Sept 28 9: 30 Opening and Keynote 1 9: 30 Keynote 2 Keynote 3 11: 00 Coffee 10: 30 Coffee 11: 30 13: 00 14: 30 16: 00 16: 30 18: 00 19: 30 21: 30 Sessions M 1 A M 1 B 12: 30 Lunch Sessions M 1 A M 1 B Coffee + Posters Sessions M 1 A 11: 00 M 1 B Welcome Reception 14: 00 15: 30 T 1 A T 1 B Lunch T 2 A W 1 B Lunch T 2 B Coffee + Posters W 2 A W 2 B Coffee Closing 16: 30 Social Event 21: 00 Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 9

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Program at a glance Monday, Sept 26 Tuesday, Sept 27 Wednesday, Sept 28 9: 30 Opening and Keynote 1 9: 30 Keynote 2 Keynote 3 11: 00 Coffee 10: 30 Coffee 11: 30 13: 00 14: 30 16: 00 16: 30 18: 00 19: 30 21: 30 Sessions M 1 A M 1 B 12: 30 Lunch Sessions M 1 A M 1 B Coffee + Posters Sessions M 1 A 11: 00 M 1 B Welcome Reception 14: 00 15: 30 T 1 A T 1 B Lunch T 2 A W 1 B Lunch T 2 B Coffee + Posters W 2 A W 2 B Coffee Closing 16: 30 Social Event 21: 00 Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 9

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Keynote speakers • Giovanni De Micheli, EPF Lausanne, Switzerland – A visionary talk • Niraj K. Jha, Princeton University, USA – Fin. FETs • Artur Jutman, Testonica, Estonia – Fault management Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 10

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Keynote speakers • Giovanni De Micheli, EPF Lausanne, Switzerland – A visionary talk • Niraj K. Jha, Princeton University, USA – Fin. FETs • Artur Jutman, Testonica, Estonia – Fault management Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 10

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Social activities Welcome Reception 19: 30 Mon, Sept 26 Seaplane Harbour / Maritime Museum Social event 16: 30 Tue, Sept 27 Estonian Open Air Museum Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 11

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Social activities Welcome Reception 19: 30 Mon, Sept 26 Seaplane Harbour / Maritime Museum Social event 16: 30 Tue, Sept 27 Estonian Open Air Museum Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 11

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Social activities Welcome Reception 19: 30 Mon, Sept 26 Seaplane Harbour / Maritime Museum Social event 16: 30 Tue, Sept 27 Estonian Open Air Museum Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 12

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Social activities Welcome Reception 19: 30 Mon, Sept 26 Seaplane Harbour / Maritime Museum Social event 16: 30 Tue, Sept 27 Estonian Open Air Museum Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 12

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Co-located: Meetings Sunday, September 25, 2016 At Tallinn UT (6 km from the hotel) • 14: 30 -16: 20 IFIP TC 10. 5 Meeting • 16: 30 -18: 30 VLSI-So. C 2016 TPC Meeting 19: 00 Dinner in the city center (shuttle taxis) Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 13

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Co-located: Meetings Sunday, September 25, 2016 At Tallinn UT (6 km from the hotel) • 14: 30 -16: 20 IFIP TC 10. 5 Meeting • 16: 30 -18: 30 VLSI-So. C 2016 TPC Meeting 19: 00 Dinner in the city center (shuttle taxis) Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 13

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Co-located: Workshop A Joint Workshop • REES Workshop by edacentrum – Resiliency in Embedded Electronic Systems • FP 7 BASTION project – Testonica, Infineon, Aster + Torino, Twente, Lund, Tallinn, HSHL – Board and So. C Test Instrumentation for Ageing and No Failure Found • H 2020 TUTORIAL project (Tallinn, DLR, Torino, Delft) – Nanoelectronics Based Dependable Cyber-Physical Systems a 2 -day event on Thu-Fri September 29 -30, 2016 – same hotel, estimated 50 participants, participation fee Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 14

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Co-located: Workshop A Joint Workshop • REES Workshop by edacentrum – Resiliency in Embedded Electronic Systems • FP 7 BASTION project – Testonica, Infineon, Aster + Torino, Twente, Lund, Tallinn, HSHL – Board and So. C Test Instrumentation for Ageing and No Failure Found • H 2020 TUTORIAL project (Tallinn, DLR, Torino, Delft) – Nanoelectronics Based Dependable Cyber-Physical Systems a 2 -day event on Thu-Fri September 29 -30, 2016 – same hotel, estimated 50 participants, participation fee Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 14

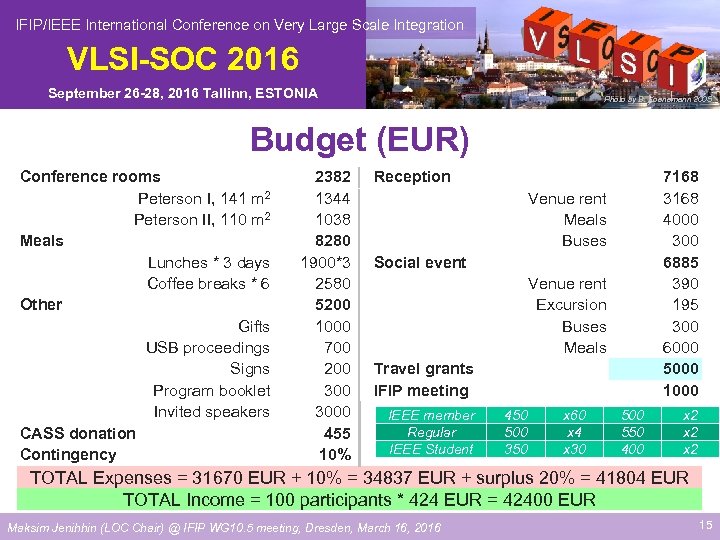

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Budget (EUR) Conference rooms Peterson I, 141 m 2 Peterson II, 110 m 2 Meals Lunches * 3 days Coffee breaks * 6 Other Gifts USB proceedings Signs Program booklet Invited speakers CASS donation Contingency 2382 1344 1038 8280 1900*3 2580 5200 1000 700 200 3000 455 10% Reception 7168 3168 4000 300 6885 390 195 300 6000 5000 1000 Venue rent Meals Buses Social event Venue rent Excursion Buses Meals Travel grants IFIP meeting IEEE member Regular IEEE Student 450 500 350 x 60 x 4 x 30 500 550 400 x 2 x 2 TOTAL Expenses = 31670 EUR + 10% = 34837 EUR + surplus 20% = 41804 EUR TOTAL Income = 100 participants * 424 EUR = 42400 EUR Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 15

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Budget (EUR) Conference rooms Peterson I, 141 m 2 Peterson II, 110 m 2 Meals Lunches * 3 days Coffee breaks * 6 Other Gifts USB proceedings Signs Program booklet Invited speakers CASS donation Contingency 2382 1344 1038 8280 1900*3 2580 5200 1000 700 200 3000 455 10% Reception 7168 3168 4000 300 6885 390 195 300 6000 5000 1000 Venue rent Meals Buses Social event Venue rent Excursion Buses Meals Travel grants IFIP meeting IEEE member Regular IEEE Student 450 500 350 x 60 x 4 x 30 500 550 400 x 2 x 2 TOTAL Expenses = 31670 EUR + 10% = 34837 EUR + surplus 20% = 41804 EUR TOTAL Income = 100 participants * 424 EUR = 42400 EUR Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 15

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Sponsors • Technical – IFIP – CASS – CEDA • Financial – Tallinn University of Technology – Industry ? Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 16

IFIP/IEEE International Conference on Very Large Scale Integration VLSI-SOC 2016 September 26 -28, 2016 Tallinn, ESTONIA Photo by B. Koenemann 2005 Sponsors • Technical – IFIP – CASS – CEDA • Financial – Tallinn University of Technology – Industry ? Maksim Jenihhin (LOC Chair) @ IFIP WG 10. 5 meeting, Dresden, March 16, 2016 16