676a2b1198838044b5362707d71cdff2.ppt

- Количество слайдов: 43

ID 115 C: Low Pin Count V 850: Small but Powerful MCU for portable application Renesas Electronics America Inc. Bobby Wong V 850 Product Marketing Manager 12 October 2010 Version: 1. 0 © 2010 Renesas Electronics America Inc. All rights reserved.

ID 115 C: Low Pin Count V 850: Small but Powerful MCU for portable application Renesas Electronics America Inc. Bobby Wong V 850 Product Marketing Manager 12 October 2010 Version: 1. 0 © 2010 Renesas Electronics America Inc. All rights reserved.

Mr. Bobby Wong n V 850 Product Marketing Manager l Conduct competitive analysis and product positioning l Responsible for product launch and next generation product definition n Previous Experience l Over 10 years experience in embedded system/ASIC design l Intel IA 64 benchmarking and architecture research l Infineon Tri. Core and Tensilica Xtensa processor IP application l Holds a BS EECS from UC Berkeley l Holds a MSEE degree from Stanford University 2 © 2010 Renesas Electronics America Inc. All rights reserved.

Mr. Bobby Wong n V 850 Product Marketing Manager l Conduct competitive analysis and product positioning l Responsible for product launch and next generation product definition n Previous Experience l Over 10 years experience in embedded system/ASIC design l Intel IA 64 benchmarking and architecture research l Infineon Tri. Core and Tensilica Xtensa processor IP application l Holds a BS EECS from UC Berkeley l Holds a MSEE degree from Stanford University 2 © 2010 Renesas Electronics America Inc. All rights reserved.

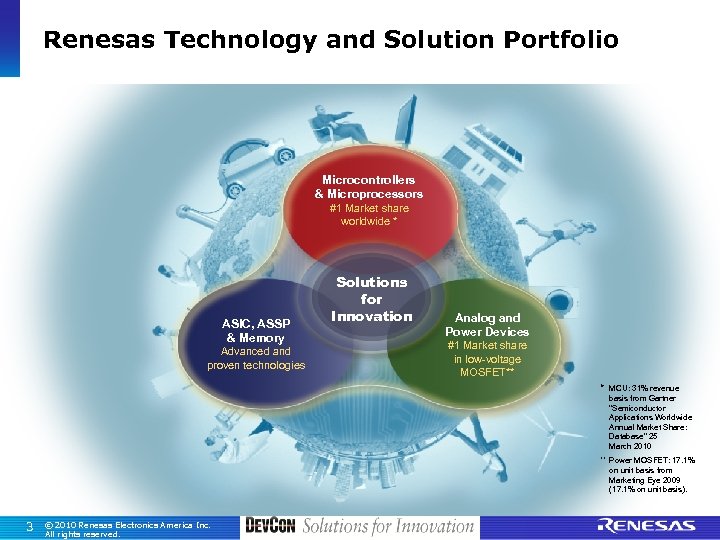

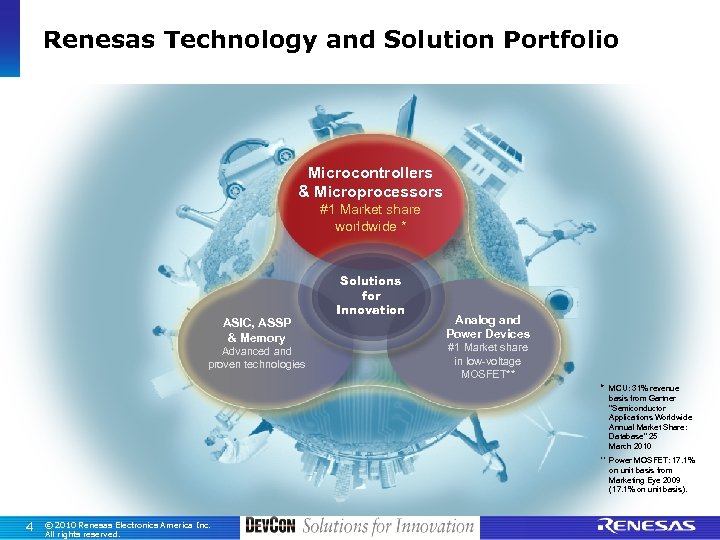

Renesas Technology and Solution Portfolio Microcontrollers & Microprocessors #1 Market share worldwide * ASIC, ASSP & Memory Advanced and proven technologies Solutions for Innovation Analog and Power Devices #1 Market share in low-voltage MOSFET** * MCU: 31% revenue basis from Gartner "Semiconductor Applications Worldwide Annual Market Share: Database" 25 March 2010 ** Power MOSFET: 17. 1% on unit basis from Marketing Eye 2009 (17. 1% on unit basis). 3 © 2010 Renesas Electronics America Inc. All rights reserved.

Renesas Technology and Solution Portfolio Microcontrollers & Microprocessors #1 Market share worldwide * ASIC, ASSP & Memory Advanced and proven technologies Solutions for Innovation Analog and Power Devices #1 Market share in low-voltage MOSFET** * MCU: 31% revenue basis from Gartner "Semiconductor Applications Worldwide Annual Market Share: Database" 25 March 2010 ** Power MOSFET: 17. 1% on unit basis from Marketing Eye 2009 (17. 1% on unit basis). 3 © 2010 Renesas Electronics America Inc. All rights reserved.

Renesas Technology and Solution Portfolio Microcontrollers & Microprocessors #1 Market share worldwide * ASIC, ASSP & Memory Advanced and proven technologies Solutions for Innovation Analog and Power Devices #1 Market share in low-voltage MOSFET** * MCU: 31% revenue basis from Gartner "Semiconductor Applications Worldwide Annual Market Share: Database" 25 March 2010 ** Power MOSFET: 17. 1% on unit basis from Marketing Eye 2009 (17. 1% on unit basis). 4 © 2010 Renesas Electronics America Inc. All rights reserved.

Renesas Technology and Solution Portfolio Microcontrollers & Microprocessors #1 Market share worldwide * ASIC, ASSP & Memory Advanced and proven technologies Solutions for Innovation Analog and Power Devices #1 Market share in low-voltage MOSFET** * MCU: 31% revenue basis from Gartner "Semiconductor Applications Worldwide Annual Market Share: Database" 25 March 2010 ** Power MOSFET: 17. 1% on unit basis from Marketing Eye 2009 (17. 1% on unit basis). 4 © 2010 Renesas Electronics America Inc. All rights reserved.

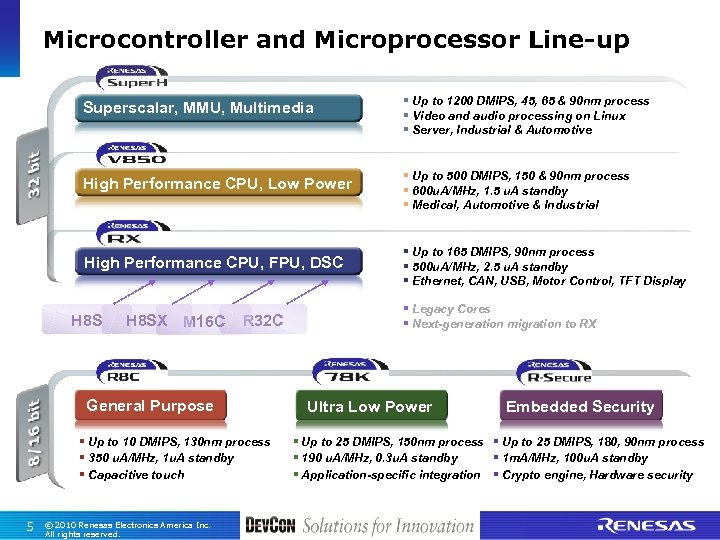

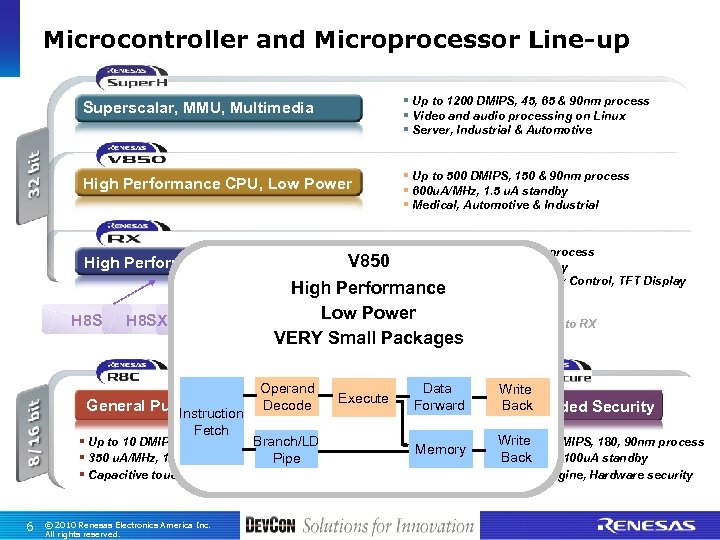

Microcontroller and Microprocessor Line-up Superscalar, MMU, Multimedia § Up to 1200 DMIPS, 45, 65 & 90 nm process § Video and audio processing on Linux § Server, Industrial & Automotive High Performance CPU, Low Power § Up to 500 DMIPS, 150 & 90 nm process § 600 u. A/MHz, 1. 5 u. A standby § Medical, Automotive & Industrial High Performance CPU, FPU, DSC H 8 SX M 16 C R 32 C General Purpose § Up to 10 DMIPS, 130 nm process § 350 u. A/MHz, 1 u. A standby § Capacitive touch 5 © 2010 Renesas Electronics America Inc. All rights reserved. § Up to 165 DMIPS, 90 nm process § 500 u. A/MHz, 2. 5 u. A standby § Ethernet, CAN, USB, Motor Control, TFT Display § Legacy Cores § Next-generation migration to RX Ultra Low Power Embedded Security § Up to 25 DMIPS, 150 nm process § Up to 25 DMIPS, 180, 90 nm process § 190 u. A/MHz, 0. 3 u. A standby § 1 m. A/MHz, 100 u. A standby § Application-specific integration § Crypto engine, Hardware security

Microcontroller and Microprocessor Line-up Superscalar, MMU, Multimedia § Up to 1200 DMIPS, 45, 65 & 90 nm process § Video and audio processing on Linux § Server, Industrial & Automotive High Performance CPU, Low Power § Up to 500 DMIPS, 150 & 90 nm process § 600 u. A/MHz, 1. 5 u. A standby § Medical, Automotive & Industrial High Performance CPU, FPU, DSC H 8 SX M 16 C R 32 C General Purpose § Up to 10 DMIPS, 130 nm process § 350 u. A/MHz, 1 u. A standby § Capacitive touch 5 © 2010 Renesas Electronics America Inc. All rights reserved. § Up to 165 DMIPS, 90 nm process § 500 u. A/MHz, 2. 5 u. A standby § Ethernet, CAN, USB, Motor Control, TFT Display § Legacy Cores § Next-generation migration to RX Ultra Low Power Embedded Security § Up to 25 DMIPS, 150 nm process § Up to 25 DMIPS, 180, 90 nm process § 190 u. A/MHz, 0. 3 u. A standby § 1 m. A/MHz, 100 u. A standby § Application-specific integration § Crypto engine, Hardware security

Microcontroller and Microprocessor Line-up Superscalar, MMU, Multimedia § Up to 1200 DMIPS, 45, 65 & 90 nm process § Video and audio processing on Linux § Server, Industrial & Automotive High Performance CPU, Low Power § Up to 500 DMIPS, 150 & 90 nm process § 600 u. A/MHz, 1. 5 u. A standby § Medical, Automotive & Industrial High Performance CPU, FPU, DSC V 850 § Up to 165 DMIPS, 90 nm process § 500 u. A/MHz, 2. 5 u. A standby § Ethernet, CAN, USB, Motor Control, TFT Display H 8 S High Performance § Legacy Cores Low Power H 8 SX M 16 C R 32 C § Next-generation migration to RX VERY Small Packages General Purpose Instruction Fetch Data Operand Execute Forward Decode Ultra Low Power Write Back Embedded Security § Up Branch/LD to 25 DMIPS, 150 nm process §Write 25 DMIPS, 180, 90 nm process § Up to 10 DMIPS, 130 nm process Up to Memory § § 350 u. A/MHz, 1 u. A standby § Back 1 m. A/MHz, 100 u. A standby Pipe 190 u. A/MHz, 0. 3 u. A standby § Application-specific integration § Crypto engine, Hardware security § Capacitive touch 6 © 2010 Renesas Electronics America Inc. All rights reserved.

Microcontroller and Microprocessor Line-up Superscalar, MMU, Multimedia § Up to 1200 DMIPS, 45, 65 & 90 nm process § Video and audio processing on Linux § Server, Industrial & Automotive High Performance CPU, Low Power § Up to 500 DMIPS, 150 & 90 nm process § 600 u. A/MHz, 1. 5 u. A standby § Medical, Automotive & Industrial High Performance CPU, FPU, DSC V 850 § Up to 165 DMIPS, 90 nm process § 500 u. A/MHz, 2. 5 u. A standby § Ethernet, CAN, USB, Motor Control, TFT Display H 8 S High Performance § Legacy Cores Low Power H 8 SX M 16 C R 32 C § Next-generation migration to RX VERY Small Packages General Purpose Instruction Fetch Data Operand Execute Forward Decode Ultra Low Power Write Back Embedded Security § Up Branch/LD to 25 DMIPS, 150 nm process §Write 25 DMIPS, 180, 90 nm process § Up to 10 DMIPS, 130 nm process Up to Memory § § 350 u. A/MHz, 1 u. A standby § Back 1 m. A/MHz, 100 u. A standby Pipe 190 u. A/MHz, 0. 3 u. A standby § Application-specific integration § Crypto engine, Hardware security § Capacitive touch 6 © 2010 Renesas Electronics America Inc. All rights reserved.

Innovation Systems are smaller Designs are not less complicated Oscilloscope Battery-operated Heat Scanner DJ Mixer Thermal Printer Scanner 7 © 2010 Renesas Electronics America Inc. All rights reserved. Medical equipment

Innovation Systems are smaller Designs are not less complicated Oscilloscope Battery-operated Heat Scanner DJ Mixer Thermal Printer Scanner 7 © 2010 Renesas Electronics America Inc. All rights reserved. Medical equipment

V 850 Low Pin Count Microcontrollers Renesas offers a family of V 850 32 -bit Microcontrollers that are High Performance, Low Power and are available in Small Packages. 8 © 2010 Renesas Electronics America Inc. All rights reserved.

V 850 Low Pin Count Microcontrollers Renesas offers a family of V 850 32 -bit Microcontrollers that are High Performance, Low Power and are available in Small Packages. 8 © 2010 Renesas Electronics America Inc. All rights reserved.

Agenda n Design Consideration of High Performance and Low Power Portable Application n V 850 energy efficient architecture n Many small packages to support design n Features Supporting Low Power Portable Application 9 © 2010 Renesas Electronics America Inc. All rights reserved.

Agenda n Design Consideration of High Performance and Low Power Portable Application n V 850 energy efficient architecture n Many small packages to support design n Features Supporting Low Power Portable Application 9 © 2010 Renesas Electronics America Inc. All rights reserved.

Key Takeaways By the end of this session you will be able to: n Understand the Energy Efficient V 850 ES MCUs n Understand the different small packages n Understand the different operating modes and features of V 850 ES for your portable application 10 © 2010 Renesas Electronics America Inc. All rights reserved.

Key Takeaways By the end of this session you will be able to: n Understand the Energy Efficient V 850 ES MCUs n Understand the different small packages n Understand the different operating modes and features of V 850 ES for your portable application 10 © 2010 Renesas Electronics America Inc. All rights reserved.

Portable Application Requirements DJ Mixer Oscilloscope Heat Scanner Thermal Printer Medical equipment Scanner 11 © 2010 Renesas Electronics America Inc. All rights reserved.

Portable Application Requirements DJ Mixer Oscilloscope Heat Scanner Thermal Printer Medical equipment Scanner 11 © 2010 Renesas Electronics America Inc. All rights reserved.

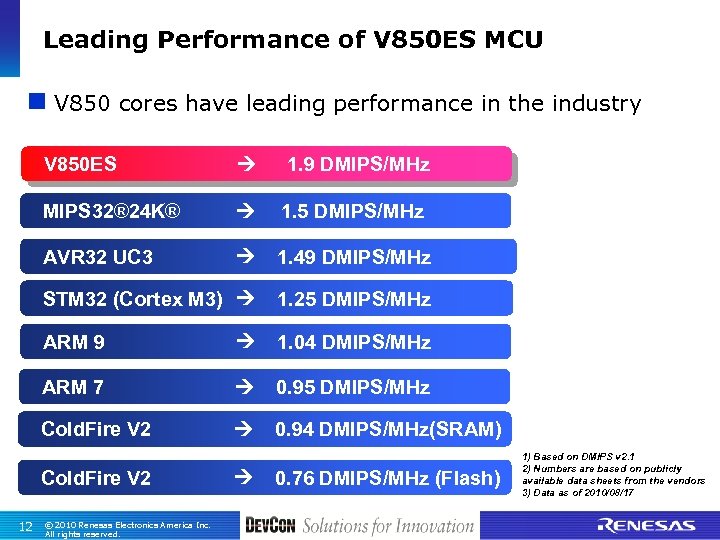

Leading Performance of V 850 ES MCU n V 850 cores have leading performance in the industry 1. 9 DMIPS/MHz V 850 ES MIPS 32® 24 K® 1. 5 DMIPS/MHz AVR 32 UC 3 1. 49 DMIPS/MHz STM 32 (Cortex M 3) 1. 25 DMIPS/MHz ARM 9 1. 04 DMIPS/MHz ARM 7 0. 95 DMIPS/MHz Cold. Fire V 2 0. 94 DMIPS/MHz(SRAM) Cold. Fire V 2 12 © 2010 Renesas Electronics America Inc. All rights reserved. 0. 76 DMIPS/MHz (Flash) 1) Based on DMIPS v 2. 1 2) Numbers are based on publicly available data sheets from the vendors 3) Data as of 2010/08/17

Leading Performance of V 850 ES MCU n V 850 cores have leading performance in the industry 1. 9 DMIPS/MHz V 850 ES MIPS 32® 24 K® 1. 5 DMIPS/MHz AVR 32 UC 3 1. 49 DMIPS/MHz STM 32 (Cortex M 3) 1. 25 DMIPS/MHz ARM 9 1. 04 DMIPS/MHz ARM 7 0. 95 DMIPS/MHz Cold. Fire V 2 0. 94 DMIPS/MHz(SRAM) Cold. Fire V 2 12 © 2010 Renesas Electronics America Inc. All rights reserved. 0. 76 DMIPS/MHz (Flash) 1) Based on DMIPS v 2. 1 2) Numbers are based on publicly available data sheets from the vendors 3) Data as of 2010/08/17

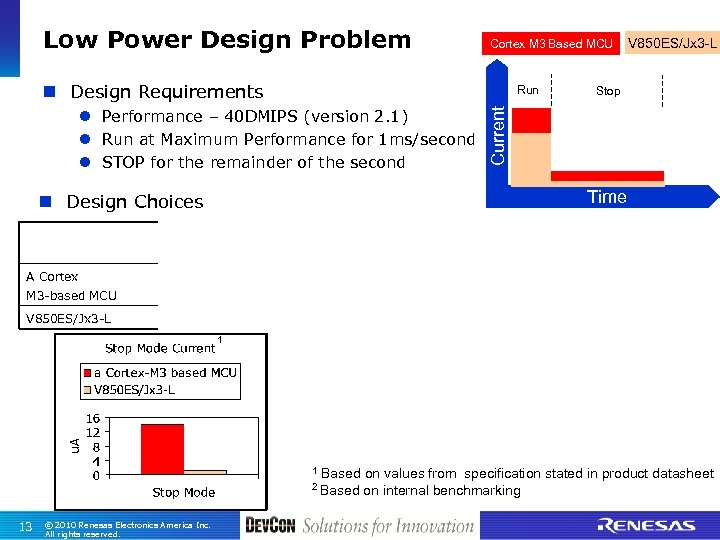

Low Power Design Problem Cortex M 3 Based MCU n Design Requirements l Performance – 40 DMIPS (version 2. 1) l Run at Maximum Performance for 1 ms/second l STOP for the remainder of the second Stop Current Run V 850 ES/Jx 3 -L Time n Design Choices DMIPS (2. 1) 2 DMIPS/MHz CPU Freq. 1 Run Current 3. 3 V 25 C 1 A Cortex 40 DMIPS 1. 25 36 MHz M 3 -based MCU V 850 ES/Jx 3 -L 17. 3 m. A (Flash access needs 1 wait state) 39 DMIPS 1. 95 20 MHz 12 m. A 1 1 Based on values from specification stated in product datasheet on internal benchmarking 2 Based 13 © 2010 Renesas Electronics America Inc. All rights reserved.

Low Power Design Problem Cortex M 3 Based MCU n Design Requirements l Performance – 40 DMIPS (version 2. 1) l Run at Maximum Performance for 1 ms/second l STOP for the remainder of the second Stop Current Run V 850 ES/Jx 3 -L Time n Design Choices DMIPS (2. 1) 2 DMIPS/MHz CPU Freq. 1 Run Current 3. 3 V 25 C 1 A Cortex 40 DMIPS 1. 25 36 MHz M 3 -based MCU V 850 ES/Jx 3 -L 17. 3 m. A (Flash access needs 1 wait state) 39 DMIPS 1. 95 20 MHz 12 m. A 1 1 Based on values from specification stated in product datasheet on internal benchmarking 2 Based 13 © 2010 Renesas Electronics America Inc. All rights reserved.

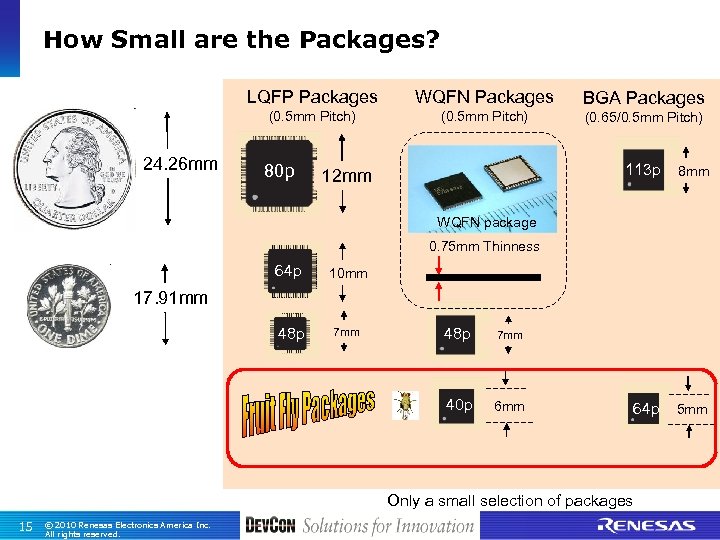

How Small are the Packages? LQFP Packages BGA Packages (0. 5 mm Pitch) 24. 26 mm WQFN Packages (0. 5 mm Pitch) (0. 65/0. 5 mm Pitch) 80 p 113 p 12 mm 8 mm 64 p 5 mm WQFN package 0. 75 mm Thinness 64 p 10 mm 48 p 7 mm 17. 91 mm 48 p 7 mm 40 p 6 mm Only a small selection of packages 15 © 2010 Renesas Electronics America Inc. All rights reserved.

How Small are the Packages? LQFP Packages BGA Packages (0. 5 mm Pitch) 24. 26 mm WQFN Packages (0. 5 mm Pitch) (0. 65/0. 5 mm Pitch) 80 p 113 p 12 mm 8 mm 64 p 5 mm WQFN package 0. 75 mm Thinness 64 p 10 mm 48 p 7 mm 17. 91 mm 48 p 7 mm 40 p 6 mm Only a small selection of packages 15 © 2010 Renesas Electronics America Inc. All rights reserved.

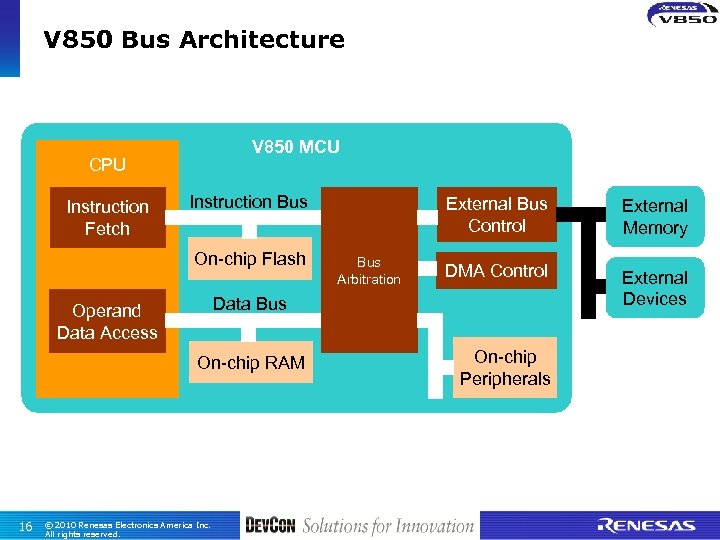

V 850 Bus Architecture V 850 MCU CPU Instruction Fetch Instruction Bus On-chip Flash Bus Arbitration External Memory DMA Control External Devices Data Bus Operand Data Access On-chip RAM 16 External Bus Control © 2010 Renesas Electronics America Inc. All rights reserved. On-chip Peripherals

V 850 Bus Architecture V 850 MCU CPU Instruction Fetch Instruction Bus On-chip Flash Bus Arbitration External Memory DMA Control External Devices Data Bus Operand Data Access On-chip RAM 16 External Bus Control © 2010 Renesas Electronics America Inc. All rights reserved. On-chip Peripherals

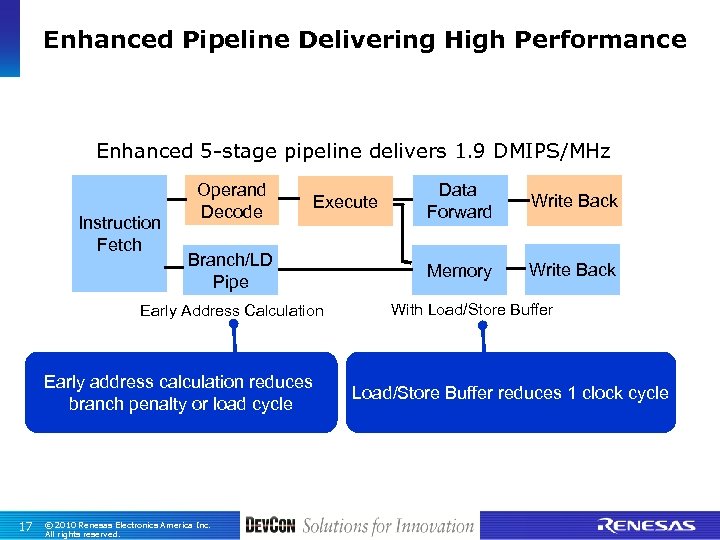

Enhanced Pipeline Delivering High Performance Regular 5 -stage pipeline Enhanced 5 -stage pipeline delivers 1. 9 DMIPS/MHz Instruction Fetch Operand Decode Branch/LD Pipe Early Address Calculation Early address calculation reduces branch penalty or load cycle 17 © 2010 Renesas Electronics America Inc. All rights reserved. Data Memory Forward Write Back Memory Execute Write Back With Load/Store Buffer reduces 1 clock cycle

Enhanced Pipeline Delivering High Performance Regular 5 -stage pipeline Enhanced 5 -stage pipeline delivers 1. 9 DMIPS/MHz Instruction Fetch Operand Decode Branch/LD Pipe Early Address Calculation Early address calculation reduces branch penalty or load cycle 17 © 2010 Renesas Electronics America Inc. All rights reserved. Data Memory Forward Write Back Memory Execute Write Back With Load/Store Buffer reduces 1 clock cycle

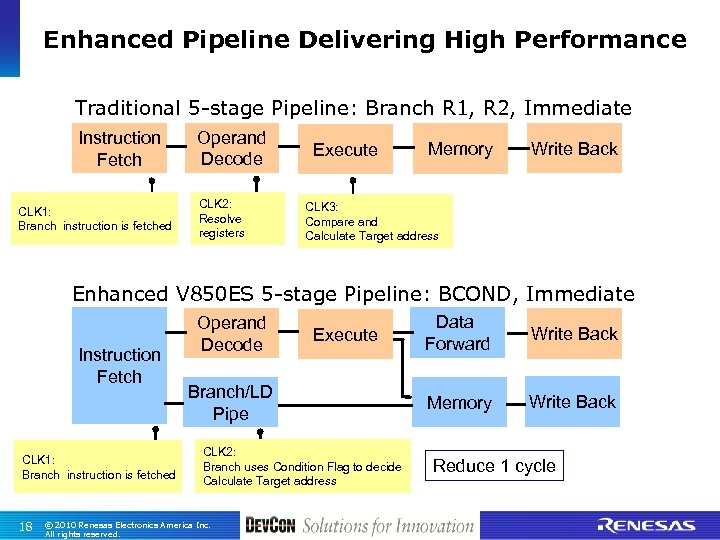

Enhanced Pipeline Delivering High Performance Traditional 5 -stage Pipeline: Branch R 1, R 2, Immediate Instruction Fetch CLK 1: Branch instruction is fetched Operand Decode CLK 2: Resolve registers Execute Memory Write Back CLK 3: Compare and Calculate Target address Enhanced V 850 ES 5 -stage Pipeline: BCOND, Immediate Instruction Fetch CLK 1: Branch instruction is fetched 18 Operand Decode Execute Branch/LD Pipe CLK 2: Branch uses Condition Flag to decide Calculate Target address © 2010 Renesas Electronics America Inc. All rights reserved. Data Forward Write Back Memory Write Back Reduce 1 cycle

Enhanced Pipeline Delivering High Performance Traditional 5 -stage Pipeline: Branch R 1, R 2, Immediate Instruction Fetch CLK 1: Branch instruction is fetched Operand Decode CLK 2: Resolve registers Execute Memory Write Back CLK 3: Compare and Calculate Target address Enhanced V 850 ES 5 -stage Pipeline: BCOND, Immediate Instruction Fetch CLK 1: Branch instruction is fetched 18 Operand Decode Execute Branch/LD Pipe CLK 2: Branch uses Condition Flag to decide Calculate Target address © 2010 Renesas Electronics America Inc. All rights reserved. Data Forward Write Back Memory Write Back Reduce 1 cycle

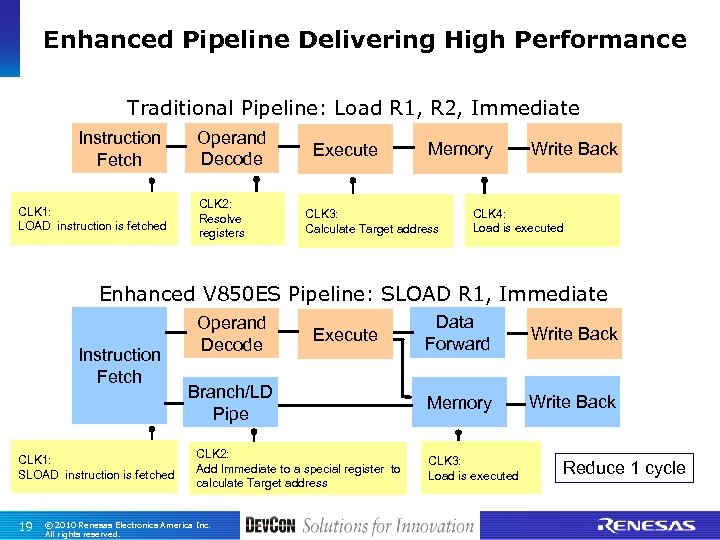

Enhanced Pipeline Delivering High Performance Traditional Pipeline: Load R 1, R 2, Immediate Instruction Fetch CLK 1: LOAD instruction is fetched Operand Decode CLK 2: Resolve registers Execute Memory CLK 3: Calculate Target address Write Back CLK 4: Load is executed Enhanced V 850 ES Pipeline: SLOAD R 1, Immediate Instruction Fetch CLK 1: SLOAD instruction is fetched 19 Operand Decode Execute Branch/LD Pipe CLK 2: Add Immediate to a special register to calculate Target address © 2010 Renesas Electronics America Inc. All rights reserved. Data Forward Write Back Memory Write Back CLK 3: Load is executed Reduce 1 cycle

Enhanced Pipeline Delivering High Performance Traditional Pipeline: Load R 1, R 2, Immediate Instruction Fetch CLK 1: LOAD instruction is fetched Operand Decode CLK 2: Resolve registers Execute Memory CLK 3: Calculate Target address Write Back CLK 4: Load is executed Enhanced V 850 ES Pipeline: SLOAD R 1, Immediate Instruction Fetch CLK 1: SLOAD instruction is fetched 19 Operand Decode Execute Branch/LD Pipe CLK 2: Add Immediate to a special register to calculate Target address © 2010 Renesas Electronics America Inc. All rights reserved. Data Forward Write Back Memory Write Back CLK 3: Load is executed Reduce 1 cycle

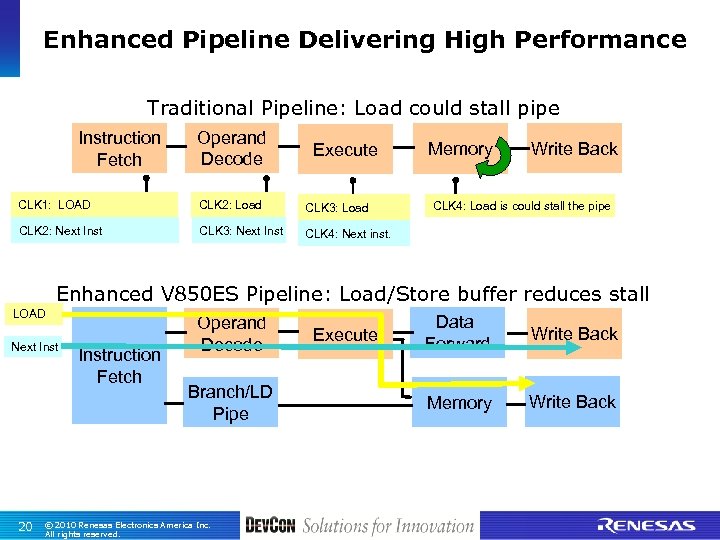

Enhanced Pipeline Delivering High Performance Traditional Pipeline: Load could stall pipe Instruction Fetch Operand Decode Execute CLK 1: LOAD CLK 2: Load CLK 3: Load CLK 2: Next Inst CLK 3: Next Inst Memory Write Back CLK 4: Next inst. CLK 4: Load is could stall the pipe Enhanced V 850 ES Pipeline: Load/Store buffer reduces stall LOAD Next Inst 20 Instruction Fetch Operand Decode Branch/LD Pipe © 2010 Renesas Electronics America Inc. All rights reserved. Execute Data Forward Write Back Memory Write Back

Enhanced Pipeline Delivering High Performance Traditional Pipeline: Load could stall pipe Instruction Fetch Operand Decode Execute CLK 1: LOAD CLK 2: Load CLK 3: Load CLK 2: Next Inst CLK 3: Next Inst Memory Write Back CLK 4: Next inst. CLK 4: Load is could stall the pipe Enhanced V 850 ES Pipeline: Load/Store buffer reduces stall LOAD Next Inst 20 Instruction Fetch Operand Decode Branch/LD Pipe © 2010 Renesas Electronics America Inc. All rights reserved. Execute Data Forward Write Back Memory Write Back

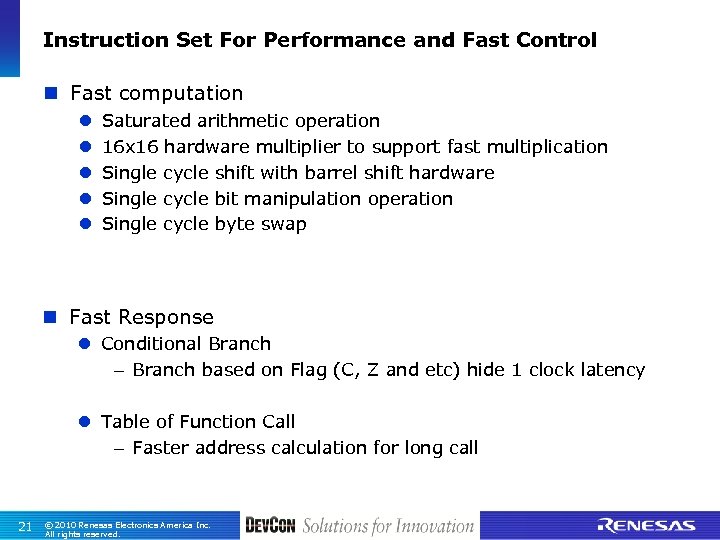

Instruction Set For Performance and Fast Control n Fast computation l l l Saturated arithmetic operation 16 x 16 hardware multiplier to support fast multiplication Single cycle shift with barrel shift hardware Single cycle bit manipulation operation Single cycle byte swap n Fast Response l Conditional Branch – Branch based on Flag (C, Z and etc) hide 1 clock latency l Table of Function Call – Faster address calculation for long call 21 © 2010 Renesas Electronics America Inc. All rights reserved.

Instruction Set For Performance and Fast Control n Fast computation l l l Saturated arithmetic operation 16 x 16 hardware multiplier to support fast multiplication Single cycle shift with barrel shift hardware Single cycle bit manipulation operation Single cycle byte swap n Fast Response l Conditional Branch – Branch based on Flag (C, Z and etc) hide 1 clock latency l Table of Function Call – Faster address calculation for long call 21 © 2010 Renesas Electronics America Inc. All rights reserved.

High Performance = Low Power? n Delivering High Performance and Low Power at the same time sounds like a contradiction? n Higher Performance delivered by raising frequency will not reduce power n Delivering more processing power by DMIPS/MHz can reduce power consumption n Doing more work at a lower operating frequency means low power and low EMI!! 22 © 2010 Renesas Electronics America Inc. All rights reserved.

High Performance = Low Power? n Delivering High Performance and Low Power at the same time sounds like a contradiction? n Higher Performance delivered by raising frequency will not reduce power n Delivering more processing power by DMIPS/MHz can reduce power consumption n Doing more work at a lower operating frequency means low power and low EMI!! 22 © 2010 Renesas Electronics America Inc. All rights reserved.

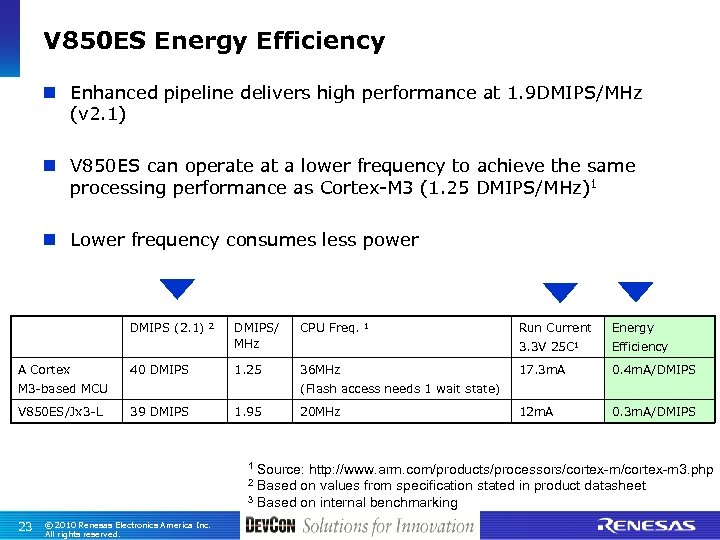

V 850 ES Energy Efficiency n Enhanced pipeline delivers high performance at 1. 9 DMIPS/MHz (v 2. 1) n V 850 ES can operate at a lower frequency to achieve the same processing performance as Cortex-M 3 (1. 25 DMIPS/MHz) 1 n Lower frequency consumes less power DMIPS (2. 1) A Cortex 2 40 DMIPS/ MHz CPU Freq. 1. 25 36 MHz M 3 -based MCU V 850 ES/Jx 3 -L 1 Run Current 3. 3 V 25 C 1 Energy Efficiency 17. 3 m. A 0. 4 m. A/DMIPS 12 m. A 0. 3 m. A/DMIPS (Flash access needs 1 wait state) 39 DMIPS 1. 95 20 MHz Source: http: //www. arm. com/products/processors/cortex-m 3. php Based on values from specification stated in product datasheet 3 Based on internal benchmarking 1 2 23 © 2010 Renesas Electronics America Inc. All rights reserved.

V 850 ES Energy Efficiency n Enhanced pipeline delivers high performance at 1. 9 DMIPS/MHz (v 2. 1) n V 850 ES can operate at a lower frequency to achieve the same processing performance as Cortex-M 3 (1. 25 DMIPS/MHz) 1 n Lower frequency consumes less power DMIPS (2. 1) A Cortex 2 40 DMIPS/ MHz CPU Freq. 1. 25 36 MHz M 3 -based MCU V 850 ES/Jx 3 -L 1 Run Current 3. 3 V 25 C 1 Energy Efficiency 17. 3 m. A 0. 4 m. A/DMIPS 12 m. A 0. 3 m. A/DMIPS (Flash access needs 1 wait state) 39 DMIPS 1. 95 20 MHz Source: http: //www. arm. com/products/processors/cortex-m 3. php Based on values from specification stated in product datasheet 3 Based on internal benchmarking 1 2 23 © 2010 Renesas Electronics America Inc. All rights reserved.

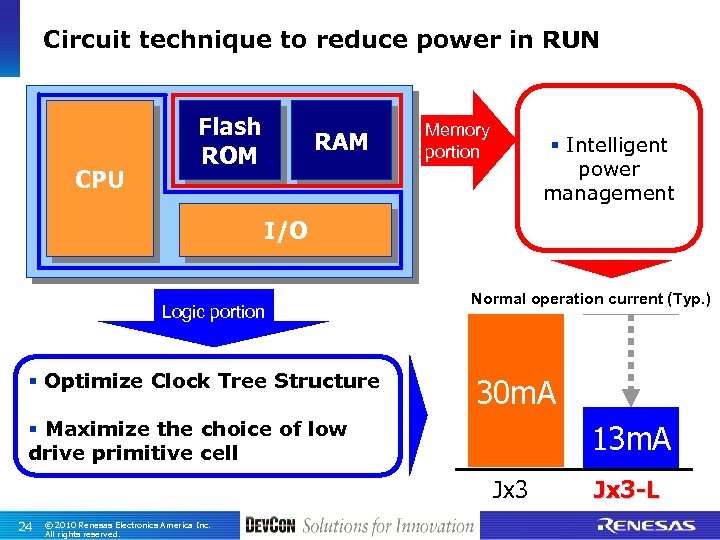

Circuit technique to reduce power in RUN CPU Flash ROM RAM Memory portion § Intelligent power management I/O Logic portion § Optimize Clock Tree Structure Normal operation current (Typ. ) 30 m. A § Maximize the choice of low drive primitive cell 13 m. A Jx 3 24 © 2010 Renesas Electronics America Inc. All rights reserved. Jx 3 -L

Circuit technique to reduce power in RUN CPU Flash ROM RAM Memory portion § Intelligent power management I/O Logic portion § Optimize Clock Tree Structure Normal operation current (Typ. ) 30 m. A § Maximize the choice of low drive primitive cell 13 m. A Jx 3 24 © 2010 Renesas Electronics America Inc. All rights reserved. Jx 3 -L

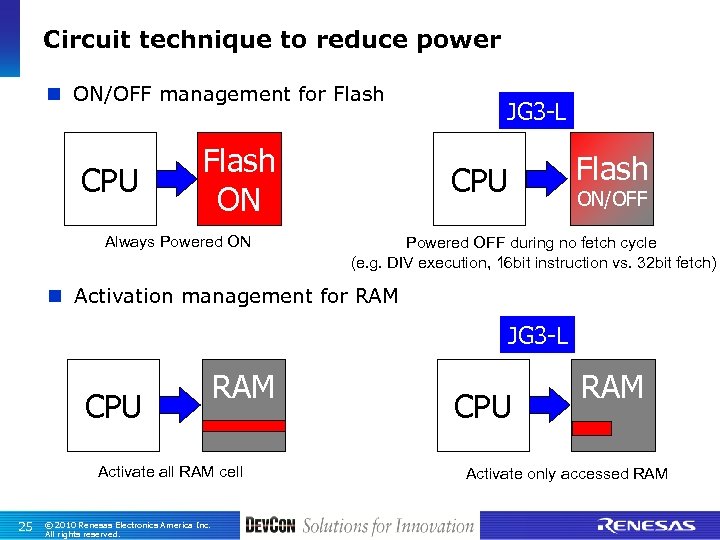

Circuit technique to reduce power n ON/OFF management for Flash CPU Flash ON Always Powered ON JG 3 -L CPU Flash ON/OFF Powered OFF during no fetch cycle (e. g. DIV execution, 16 bit instruction vs. 32 bit fetch) n Activation management for RAM JG 3 -L CPU RAM Activate all RAM cell 25 © 2010 Renesas Electronics America Inc. All rights reserved. CPU RAM Activate only accessed RAM

Circuit technique to reduce power n ON/OFF management for Flash CPU Flash ON Always Powered ON JG 3 -L CPU Flash ON/OFF Powered OFF during no fetch cycle (e. g. DIV execution, 16 bit instruction vs. 32 bit fetch) n Activation management for RAM JG 3 -L CPU RAM Activate all RAM cell 25 © 2010 Renesas Electronics America Inc. All rights reserved. CPU RAM Activate only accessed RAM

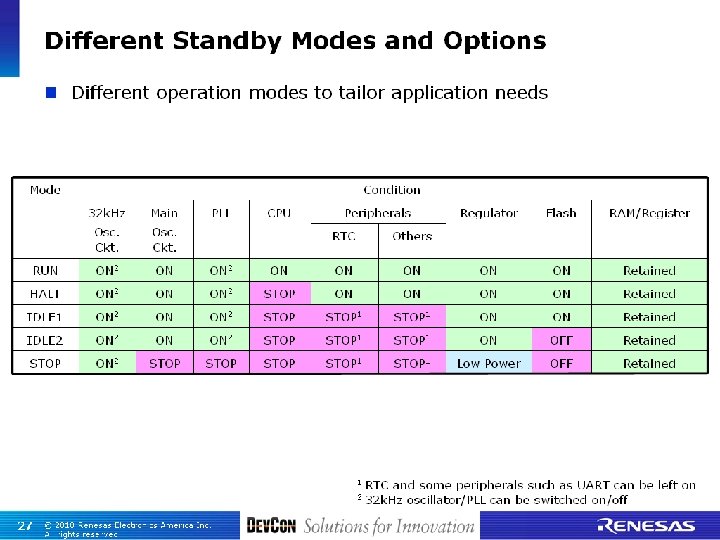

Different Standby Modes and Options n Different operation modes to tailor application needs Mode Condition 32 k. Hz Main PLL Osc. Ckt. RUN ON 2 ON ON 2 HALT ON 2 ON IDLE 1 ON 2 IDLE 2 STOP CPU Peripherals Flash RAM/Register RTC Others ON ON ON Retained ON 2 STOP ON ON Retained ON ON 2 STOP 1 ON ON Retained ON 2 ON ON 2 STOP 1 ON OFF Retained ON 2 STOP 1 STOP 1 Low Power OFF Retained 1 2 26 Regulator © 2010 Renesas Electronics America Inc. All rights reserved. RTC and some peripherals such as UART can be left on 32 k. Hz oscillator/PLL can be switched on/off

Different Standby Modes and Options n Different operation modes to tailor application needs Mode Condition 32 k. Hz Main PLL Osc. Ckt. RUN ON 2 ON ON 2 HALT ON 2 ON IDLE 1 ON 2 IDLE 2 STOP CPU Peripherals Flash RAM/Register RTC Others ON ON ON Retained ON 2 STOP ON ON Retained ON ON 2 STOP 1 ON ON Retained ON 2 ON ON 2 STOP 1 ON OFF Retained ON 2 STOP 1 STOP 1 Low Power OFF Retained 1 2 26 Regulator © 2010 Renesas Electronics America Inc. All rights reserved. RTC and some peripherals such as UART can be left on 32 k. Hz oscillator/PLL can be switched on/off

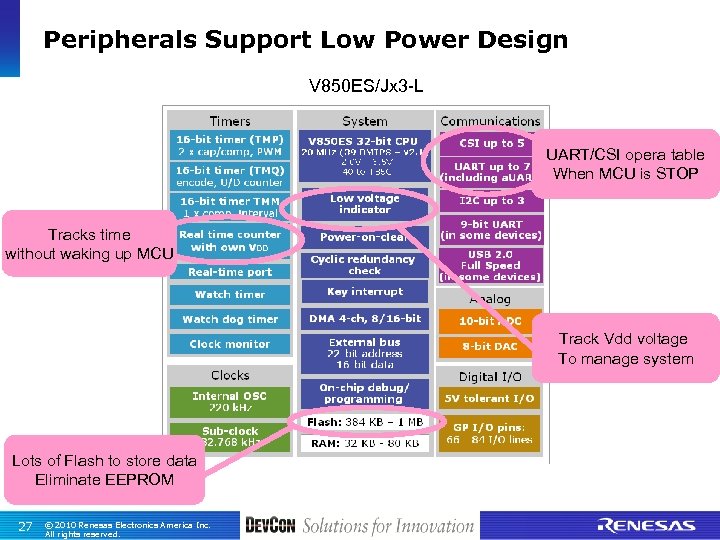

Peripherals Support Low Power Design V 850 ES/Jx 3 -L UART/CSI opera table When MCU is STOP Tracks time without waking up MCU Track Vdd voltage To manage system Lots of Flash to store data Eliminate EEPROM 27 © 2010 Renesas Electronics America Inc. All rights reserved.

Peripherals Support Low Power Design V 850 ES/Jx 3 -L UART/CSI opera table When MCU is STOP Tracks time without waking up MCU Track Vdd voltage To manage system Lots of Flash to store data Eliminate EEPROM 27 © 2010 Renesas Electronics America Inc. All rights reserved.

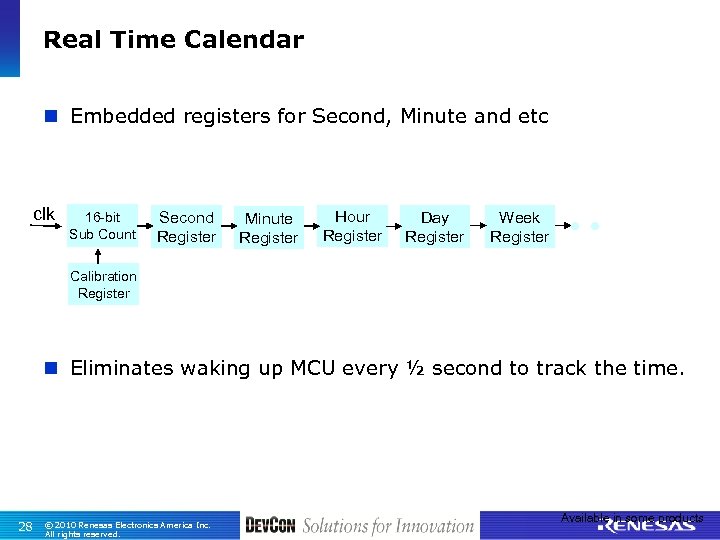

Real Time Calendar n Embedded registers for Second, Minute and etc clk 16 -bit Sub Count Second Register Minute Register Hour Register Day Register Week Register Calibration Register n Eliminates waking up MCU every ½ second to track the time. 28 © 2010 Renesas Electronics America Inc. All rights reserved. Available in some products

Real Time Calendar n Embedded registers for Second, Minute and etc clk 16 -bit Sub Count Second Register Minute Register Hour Register Day Register Week Register Calibration Register n Eliminates waking up MCU every ½ second to track the time. 28 © 2010 Renesas Electronics America Inc. All rights reserved. Available in some products

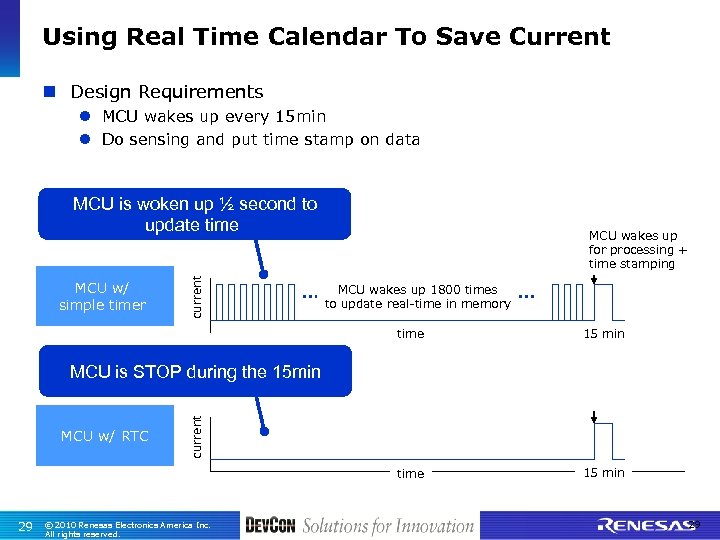

Using Real Time Calendar To Save Current n Design Requirements l MCU wakes up every 15 min l Do sensing and put time stamp on data MCU w/ simple timer current MCU is woken up ½ second to update time MCU wakes up for processing + time stamping MCU wakes up 1800 times to update real-time in memory time 15 min MCU w/ RTC 29 current MCU is STOP during the 15 min © 2010 Renesas Electronics America Inc. All rights reserved. 29

Using Real Time Calendar To Save Current n Design Requirements l MCU wakes up every 15 min l Do sensing and put time stamp on data MCU w/ simple timer current MCU is woken up ½ second to update time MCU wakes up for processing + time stamping MCU wakes up 1800 times to update real-time in memory time 15 min MCU w/ RTC 29 current MCU is STOP during the 15 min © 2010 Renesas Electronics America Inc. All rights reserved. 29

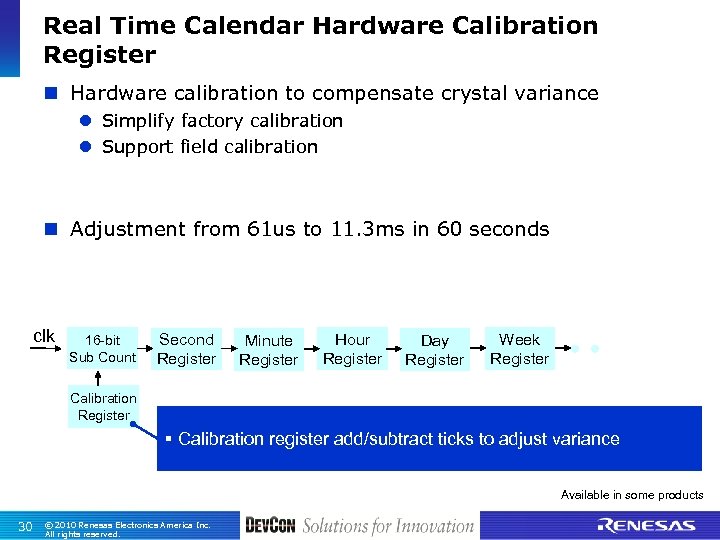

Real Time Calendar Hardware Calibration Register n Hardware calibration to compensate crystal variance l Simplify factory calibration l Support field calibration n Adjustment from 61 us to 11. 3 ms in 60 seconds clk 16 -bit Sub Count Second Register Minute Register Hour Register Day Register Week Register Calibration Register § Calibration register add/subtract ticks to adjust variance Available in some products 30 © 2010 Renesas Electronics America Inc. All rights reserved.

Real Time Calendar Hardware Calibration Register n Hardware calibration to compensate crystal variance l Simplify factory calibration l Support field calibration n Adjustment from 61 us to 11. 3 ms in 60 seconds clk 16 -bit Sub Count Second Register Minute Register Hour Register Day Register Week Register Calibration Register § Calibration register add/subtract ticks to adjust variance Available in some products 30 © 2010 Renesas Electronics America Inc. All rights reserved.

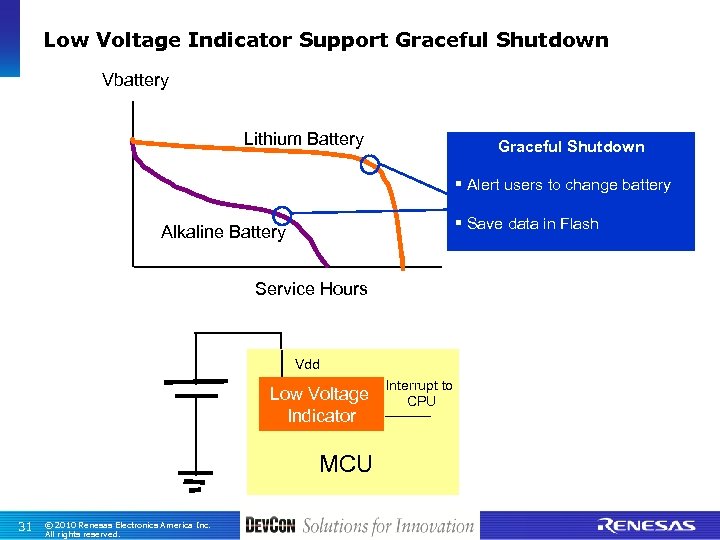

Low Voltage Indicator Support Graceful Shutdown Vbattery Lithium Battery Graceful Shutdown § Alert users to change battery § Save data in Flash Alkaline Battery Service Hours Vdd Low Voltage Indicator MCU 31 © 2010 Renesas Electronics America Inc. All rights reserved. Interrupt to CPU

Low Voltage Indicator Support Graceful Shutdown Vbattery Lithium Battery Graceful Shutdown § Alert users to change battery § Save data in Flash Alkaline Battery Service Hours Vdd Low Voltage Indicator MCU 31 © 2010 Renesas Electronics America Inc. All rights reserved. Interrupt to CPU

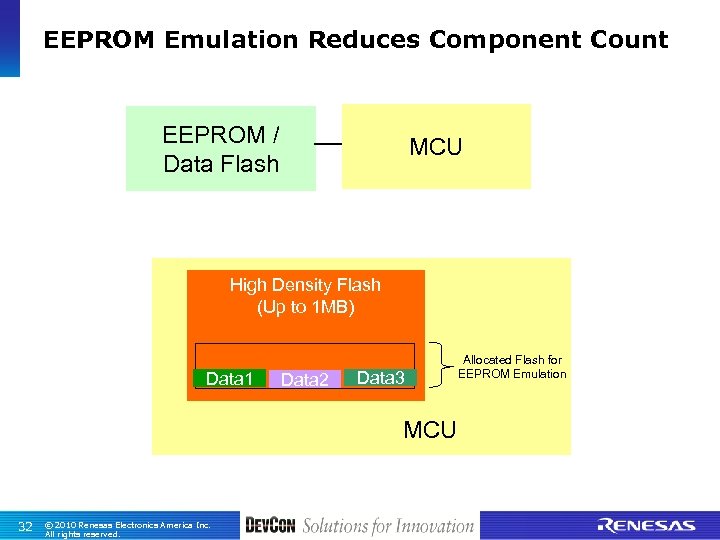

EEPROM Emulation Reduces Component Count EEPROM / Data Flash MCU High Density Flash (Up to 1 MB) Data 1 Data 2 Data 3 MCU 32 © 2010 Renesas Electronics America Inc. All rights reserved. Allocated Flash for EEPROM Emulation

EEPROM Emulation Reduces Component Count EEPROM / Data Flash MCU High Density Flash (Up to 1 MB) Data 1 Data 2 Data 3 MCU 32 © 2010 Renesas Electronics America Inc. All rights reserved. Allocated Flash for EEPROM Emulation

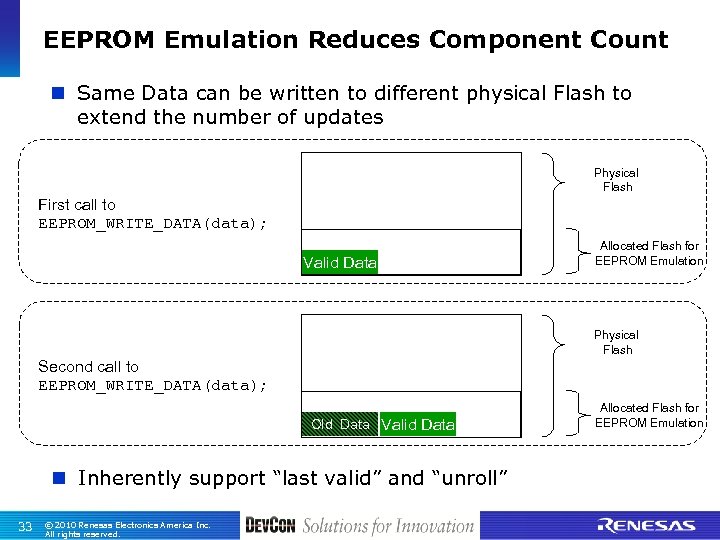

EEPROM Emulation Reduces Component Count n Same Data can be written to different physical Flash to extend the number of updates Physical Flash First call to EEPROM_WRITE_DATA(data); Valid Data Allocated Flash for EEPROM Emulation Physical Flash Second call to EEPROM_WRITE_DATA(data); Old Data Valid Data n Inherently support “last valid” and “unroll” 33 © 2010 Renesas Electronics America Inc. All rights reserved. Allocated Flash for EEPROM Emulation

EEPROM Emulation Reduces Component Count n Same Data can be written to different physical Flash to extend the number of updates Physical Flash First call to EEPROM_WRITE_DATA(data); Valid Data Allocated Flash for EEPROM Emulation Physical Flash Second call to EEPROM_WRITE_DATA(data); Old Data Valid Data n Inherently support “last valid” and “unroll” 33 © 2010 Renesas Electronics America Inc. All rights reserved. Allocated Flash for EEPROM Emulation

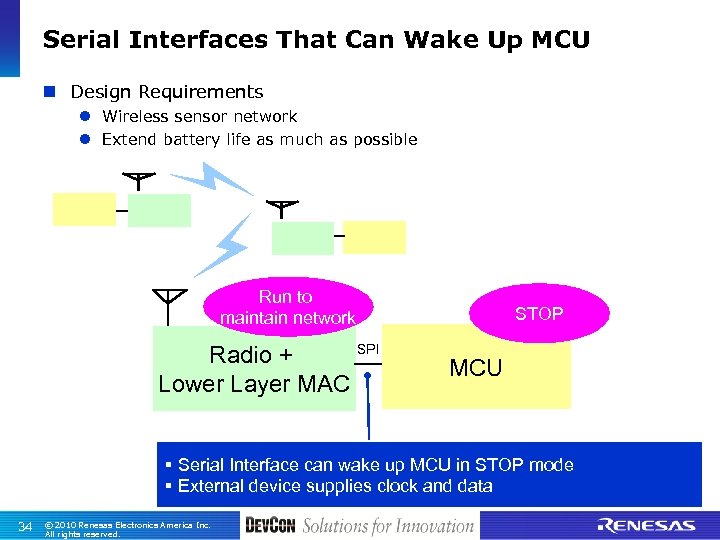

Serial Interfaces That Can Wake Up MCU n Design Requirements l Wireless sensor network l Extend battery life as much as possible Run to maintain network SPI Radio + Lower Layer MAC STOP MCU § Serial Interface can wake up MCU in STOP mode § External device supplies clock and data 34 © 2010 Renesas Electronics America Inc. All rights reserved.

Serial Interfaces That Can Wake Up MCU n Design Requirements l Wireless sensor network l Extend battery life as much as possible Run to maintain network SPI Radio + Lower Layer MAC STOP MCU § Serial Interface can wake up MCU in STOP mode § External device supplies clock and data 34 © 2010 Renesas Electronics America Inc. All rights reserved.

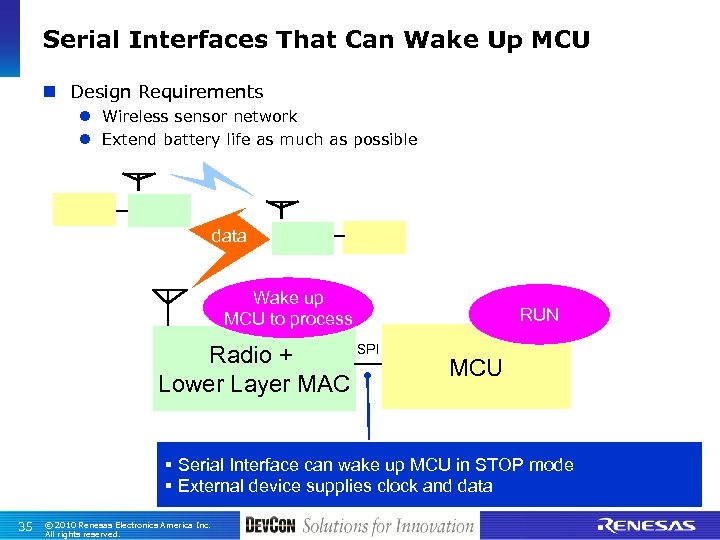

Serial Interfaces That Can Wake Up MCU n Design Requirements l Wireless sensor network l Extend battery life as much as possible data Run up Waketo maintain process MCU to network SPI Radio + Lower Layer MAC STOP RUN MCU § Serial Interface can wake up MCU in STOP mode § External device supplies clock and data 35 © 2010 Renesas Electronics America Inc. All rights reserved.

Serial Interfaces That Can Wake Up MCU n Design Requirements l Wireless sensor network l Extend battery life as much as possible data Run up Waketo maintain process MCU to network SPI Radio + Lower Layer MAC STOP RUN MCU § Serial Interface can wake up MCU in STOP mode § External device supplies clock and data 35 © 2010 Renesas Electronics America Inc. All rights reserved.

V 850 ES MCUs Support Low Power Portable Applications High performance V 850 ES delivers 1. 9 DMIPS/MHz Energy Efficient for Portable Application V 850 ES/Jx 3 -L delivers 0. 3 m. A/DMIPS Small Packages 64 -pin WQFN as small as 7 x 7 mm. BGA in 5 x 5 mm Features support Low Power Portable Application Real Time Counter, Low Voltage Indicator, EEPROM Emulation and more 36 © 2010 Renesas Electronics America Inc. All rights reserved.

V 850 ES MCUs Support Low Power Portable Applications High performance V 850 ES delivers 1. 9 DMIPS/MHz Energy Efficient for Portable Application V 850 ES/Jx 3 -L delivers 0. 3 m. A/DMIPS Small Packages 64 -pin WQFN as small as 7 x 7 mm. BGA in 5 x 5 mm Features support Low Power Portable Application Real Time Counter, Low Voltage Indicator, EEPROM Emulation and more 36 © 2010 Renesas Electronics America Inc. All rights reserved.

Commitment to Portable Application Next generation V 850 ES/Jx 4 n 1. 5 -2 x performance improvement n Smaller packages to 33 -pin Today V 850 ES Jx 3 series 37 © 2010 Renesas Electronics America Inc. All rights reserved. n >50% reduction in current consumption n Specialized peripherals to reduce power

Commitment to Portable Application Next generation V 850 ES/Jx 4 n 1. 5 -2 x performance improvement n Smaller packages to 33 -pin Today V 850 ES Jx 3 series 37 © 2010 Renesas Electronics America Inc. All rights reserved. n >50% reduction in current consumption n Specialized peripherals to reduce power

Innovation Possible DJ Mixer Oscilloscope Heat Scanner Thermal Printer Medical equipment Scanner 38 © 2010 Renesas Electronics America Inc. All rights reserved.

Innovation Possible DJ Mixer Oscilloscope Heat Scanner Thermal Printer Medical equipment Scanner 38 © 2010 Renesas Electronics America Inc. All rights reserved.

Thank You! 39 © 2010 Renesas Electronics America Inc. All rights reserved.

Thank You! 39 © 2010 Renesas Electronics America Inc. All rights reserved.

Appendix 40 © 2010 Renesas Electronics America Inc. All rights reserved.

Appendix 40 © 2010 Renesas Electronics America Inc. All rights reserved.

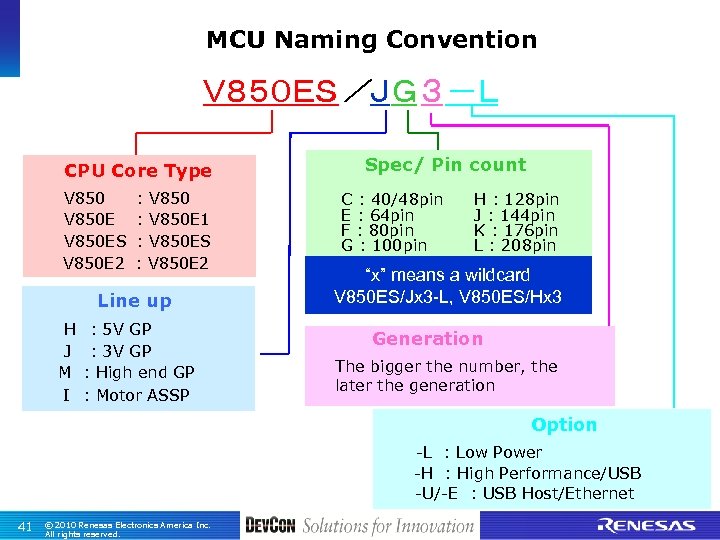

MCU Naming Convention V850ES /JG 3 -L CPU Core Type V 850 ES V 850 E 2 : V 850 E 1 : V 850 ES : V 850 E 2 Line up H J M I : 5 V GP : 3 V GP : High end GP : Motor ASSP Spec/ Pin count C : 40/48 pin E : 64 pin F : 80 pin G : 100 pin H : 128 pin J : 144 pin K : 176 pin L : 208 pin “x” means a wildcard V 850 ES/Jx 3 -L, V 850 ES/Hx 3 Generation The bigger the number, the later the generation Option -L : Low Power -H : High Performance/USB -U/-E : USB Host/Ethernet 41 © 2010 Renesas Electronics America Inc. All rights reserved.

MCU Naming Convention V850ES /JG 3 -L CPU Core Type V 850 ES V 850 E 2 : V 850 E 1 : V 850 ES : V 850 E 2 Line up H J M I : 5 V GP : 3 V GP : High end GP : Motor ASSP Spec/ Pin count C : 40/48 pin E : 64 pin F : 80 pin G : 100 pin H : 128 pin J : 144 pin K : 176 pin L : 208 pin “x” means a wildcard V 850 ES/Jx 3 -L, V 850 ES/Hx 3 Generation The bigger the number, the later the generation Option -L : Low Power -H : High Performance/USB -U/-E : USB Host/Ethernet 41 © 2010 Renesas Electronics America Inc. All rights reserved.

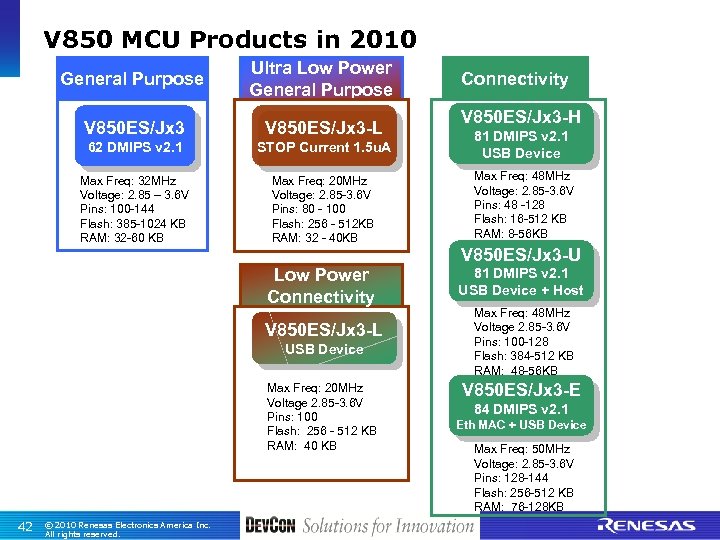

V 850 MCU Products in 2010 General Purpose Ultra Low Power General Purpose V 850 ES/Jx 3 -L 62 DMIPS v 2. 1 STOP Current 1. 5 u. A 81 DMIPS v 2. 1 USB Device Max Freq: 32 MHz Voltage: 2. 85 – 3. 6 V Pins: 100 -144 Flash: 385 -1024 KB RAM: 32 -60 KB Max Freq: 20 MHz Voltage: 2. 85 -3. 6 V Pins: 80 - 100 Flash: 256 - 512 KB RAM: 32 - 40 KB Max Freq: 48 MHz Voltage: 2. 85 -3. 6 V Pins: 48 -128 Flash: 16 -512 KB RAM: 8 -56 KB Low Power Connectivity V 850 ES/Jx 3 -L USB Device Max Freq: 20 MHz Voltage 2. 85 -3. 6 V Pins: 100 Flash: 256 - 512 KB RAM: 40 KB 42 © 2010 Renesas Electronics America Inc. All rights reserved. Connectivity V 850 ES/Jx 3 -H V 850 ES/Jx 3 -U 81 DMIPS v 2. 1 USB Device + Host Max Freq: 48 MHz Voltage 2. 85 -3. 6 V Pins: 100 -128 Flash: 384 -512 KB RAM: 48 -56 KB V 850 ES/Jx 3 -E 84 DMIPS v 2. 1 Eth MAC + USB Device Max Freq: 50 MHz Voltage: 2. 85 -3. 6 V Pins: 128 -144 Flash: 256 -512 KB RAM: 76 -128 KB

V 850 MCU Products in 2010 General Purpose Ultra Low Power General Purpose V 850 ES/Jx 3 -L 62 DMIPS v 2. 1 STOP Current 1. 5 u. A 81 DMIPS v 2. 1 USB Device Max Freq: 32 MHz Voltage: 2. 85 – 3. 6 V Pins: 100 -144 Flash: 385 -1024 KB RAM: 32 -60 KB Max Freq: 20 MHz Voltage: 2. 85 -3. 6 V Pins: 80 - 100 Flash: 256 - 512 KB RAM: 32 - 40 KB Max Freq: 48 MHz Voltage: 2. 85 -3. 6 V Pins: 48 -128 Flash: 16 -512 KB RAM: 8 -56 KB Low Power Connectivity V 850 ES/Jx 3 -L USB Device Max Freq: 20 MHz Voltage 2. 85 -3. 6 V Pins: 100 Flash: 256 - 512 KB RAM: 40 KB 42 © 2010 Renesas Electronics America Inc. All rights reserved. Connectivity V 850 ES/Jx 3 -H V 850 ES/Jx 3 -U 81 DMIPS v 2. 1 USB Device + Host Max Freq: 48 MHz Voltage 2. 85 -3. 6 V Pins: 100 -128 Flash: 384 -512 KB RAM: 48 -56 KB V 850 ES/Jx 3 -E 84 DMIPS v 2. 1 Eth MAC + USB Device Max Freq: 50 MHz Voltage: 2. 85 -3. 6 V Pins: 128 -144 Flash: 256 -512 KB RAM: 76 -128 KB

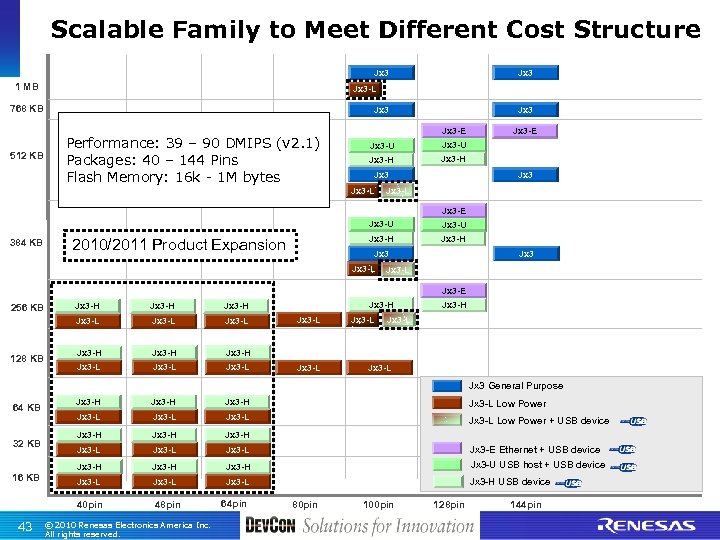

Scalable Family to Meet Different Cost Structure Jx 3 1 MB Jx 3 -L 768 KB 512 KB Jx 3 Performance: 39 – 90 DMIPS (v 2. 1) Packages: 40 – 144 Pins Flash Memory: 16 k - 1 M bytes Jx 3 -U Jx 3 -E Jx 3 -U Jx 3 -H Jx 3 -L Jx 3 -U 384 KB Jx 3 -E Jx 3 -U Jx 3 -H 2010/2011 Product Expansion Jx 3 -E Jx 3 -H Jx 3 -L Jx 3 -E 256 KB Jx 3 -H Jx 3 -L 128 KB Jx 3 -H Jx 3 -L Jx 3 -L Jx 3 -H Jx 3 -L Jx 3 General Purpose 32 KB 16 KB 43 Jx 3 -H Jx 3 -L Low Power Jx 3 -L Low Power + USB device Jx 3 -H Jx 3 -L Jx 3 -E Ethernet + USB device Jx 3 -H Jx 3 -U USB host + USB device Jx 3 -L Jx 3 -H USB device 40 pin 64 KB 48 pin © 2010 Renesas Electronics America Inc. All rights reserved. 64 pin 80 pin 100 pin 128 pin 144 pin

Scalable Family to Meet Different Cost Structure Jx 3 1 MB Jx 3 -L 768 KB 512 KB Jx 3 Performance: 39 – 90 DMIPS (v 2. 1) Packages: 40 – 144 Pins Flash Memory: 16 k - 1 M bytes Jx 3 -U Jx 3 -E Jx 3 -U Jx 3 -H Jx 3 -L Jx 3 -U 384 KB Jx 3 -E Jx 3 -U Jx 3 -H 2010/2011 Product Expansion Jx 3 -E Jx 3 -H Jx 3 -L Jx 3 -E 256 KB Jx 3 -H Jx 3 -L 128 KB Jx 3 -H Jx 3 -L Jx 3 -L Jx 3 -H Jx 3 -L Jx 3 General Purpose 32 KB 16 KB 43 Jx 3 -H Jx 3 -L Low Power Jx 3 -L Low Power + USB device Jx 3 -H Jx 3 -L Jx 3 -E Ethernet + USB device Jx 3 -H Jx 3 -U USB host + USB device Jx 3 -L Jx 3 -H USB device 40 pin 64 KB 48 pin © 2010 Renesas Electronics America Inc. All rights reserved. 64 pin 80 pin 100 pin 128 pin 144 pin

Renesas Electronics America Inc.

Renesas Electronics America Inc.