f7b7944291c64c5c02b677b74a890756.ppt

- Количество слайдов: 111

HSPICE 사용법 및 실습 2013 아날로그집적회로 실습

Overview 1 SPICE ? ! ! SPICE : == Simulation Program with Integrated Circuit Emphasis A Powerful, general-purpose circuit analysis program Ⅴ Developed By U. C. Berkeley in the Late 1960’s Ⅴ Originally Christened CANCER by Lawrence Nagel (Ph. D. thesis) Was limited to C, R, L, Bipolar diodes and transistors. 100 node maximum Ⅴ SPICE 1, 1971 Added MOS, JFET’s, Gummel-Poon, subcircuits Ⅴ SPICE 2, 1975 17, 000 lines of FORTRAN coded Added “E” and “G” elements Improved both speed and accuracy of transient analysis Released as version G. 6 in 1983 Ⅴ SPICE 3 A superset of 2 G. 6, re-written in C to include: Multiple netlists, poly. caps and inductors, inline resistor TC’s, Temp sweep analysis, topology checking, more.

Overview 2 History of Star-HSPICE 1981 Introduced 1984 Capable of 50, 000 node analysis 1985 Labs established 1987 Optimization added 1988 Speed increased by 10 -100 X capacity increased to 100, 000 transistors 1989 Inroduced mixed signal analysis P. C. version marketed 1990 Included lossy transmission line analysis 1992 Major improvements in speed, accuracy and convergence 1993 Several improvements, including auto-memory allocation 1995 Improvements in speed and versatility 1996 Flex. LM, CD install, better speed and convergence, major fixes in lossy transmission Line models, BSIM 3 v 3 and Mos 9 MOS models added 1997 Multiconductor lossy frequency-dependent transmission line model(W element) added

Overview 3 SPICE Capabilities Ⅴ General purpose circuit simulator which performs many kind of analysis of a circuit Ⅴ Ⅴ Ⅴ Nonlinear DC analysis : determines the DC operating point of the circuit Nonlinear transient : determines the response as a function of time over a specified time interval Linear AC analysis : calculates the frequency response of the circuit Small signal DC transfer function analysis of a circuit from a specified input to a specified o/p ETC : DC small signal sensitivity, distortion, Noise, fourier, temperature, statistical analysis etc. Ⅴ Contains built-in models Ⅴ Passive elements : resistors, capacitors, inductors, transmission lines, mutual inductor etc Ⅴ Active elements : Diode, BJT, JFET, MESFET, MOSFET, SOI, etc Ⅴ Independent Sources, dependent Sources (VCVS: E, VCCS: G, CCVS: H, CCCS: F), etc

Overview 4 Fundamentals q Files & Suffixes q Netlist Structure q Naming Conventions q Units & Scale Factors q Components ü Passive ü Active q Sources ü Independent ü Dependent

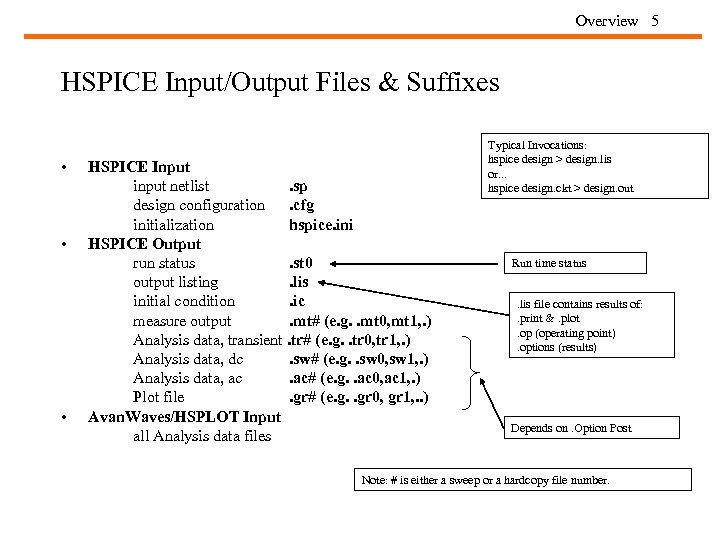

Overview 5 HSPICE Input/Output Files & Suffixes • • • HSPICE Input input netlist . sp design configuration . cfg initialization hspice. ini HSPICE Output run status . st 0 output listing . lis initial condition . ic measure output . mt# (e. g. . mt 0, mt 1, . ) Analysis data, transient. tr# (e. g. . tr 0, tr 1, . ) Analysis data, dc . sw# (e. g. . sw 0, sw 1, . ) Analysis data, ac . ac# (e. g. . ac 0, ac 1, . ) Plot file . gr# (e. g. . gr 0, gr 1, . . ) Avan. Waves/HSPLOT Input all Analysis data files Typical Invocations: hspice design > design. lis or. . . hspice design. ckt > design. out Run time status . lis file contains results of: . print &. plot . op (operating point) . options (results) Depends on. Option Post Note: # is either a sweep or a hardcopy file number.

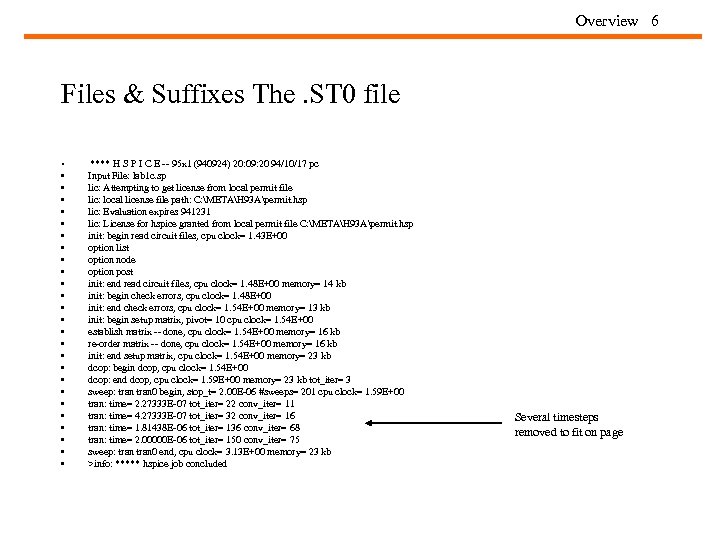

Overview 6 Files & Suffixes The. ST 0 file • **** H S P I C E -- 95 x 1 (940924) 20: 09: 20 94/10/17 pc • • • • • • • Input File: lab 1 c. sp lic: Attempting to get license from local permit file lic: local license file path: C: METAH 93 Apermit. hsp lic: Evaluation expires 941231 lic: License for hspice granted from local permit file C: METAH 93 Apermit. hsp init: begin read circuit files, cpu clock= 1. 43 E+00 option list option node option post init: end read circuit files, cpu clock= 1. 48 E+00 memory= 14 kb init: begin check errors, cpu clock= 1. 48 E+00 init: end check errors, cpu clock= 1. 54 E+00 memory= 13 kb init: begin setup matrix, pivot= 10 cpu clock= 1. 54 E+00 establish matrix -- done, cpu clock= 1. 54 E+00 memory= 16 kb re-order matrix -- done, cpu clock= 1. 54 E+00 memory= 16 kb init: end setup matrix, cpu clock= 1. 54 E+00 memory= 23 kb dcop: begin dcop, cpu clock= 1. 54 E+00 dcop: end dcop, cpu clock= 1. 59 E+00 memory= 23 kb tot_iter= 3 sweep: tran 0 begin, stop_t= 2. 00 E-06 #sweeps= 201 cpu clock= 1. 59 E+00 tran: time= 2. 27333 E-07 tot_iter= 22 conv_iter= 11 tran: time= 4. 27333 E-07 tot_iter= 32 conv_iter= 16 tran: time= 1. 81438 E-06 tot_iter= 136 conv_iter= 68 tran: time= 2. 00000 E-06 tot_iter= 150 conv_iter= 75 sweep: tran 0 end, cpu clock= 3. 13 E+00 memory= 23 kb >info: ***** hspice job concluded Several timesteps removed to fit on page

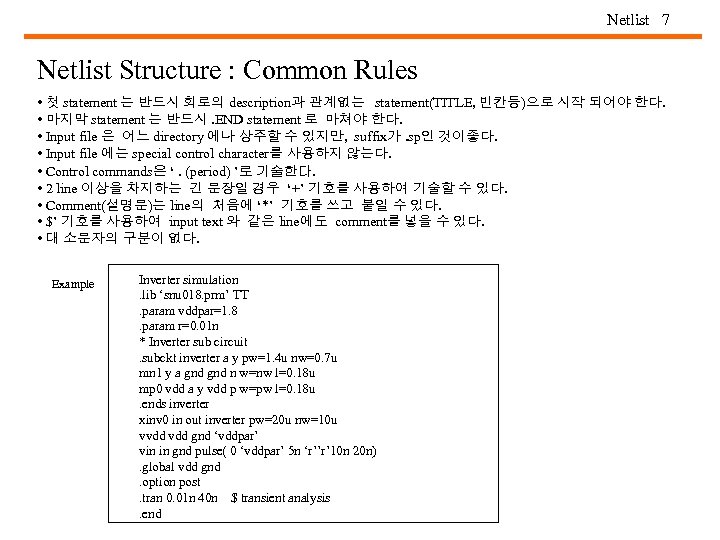

Netlist 7 Netlist Structure : Common Rules • 첫 statement 는 반드시 회로의 description과 관계없는 statement(TITLE, 빈칸등)으로 시작 되어야 한다. • 마지막 statement 는 반드시. END statement 로 마쳐야 한다. • Input file 은 어느 directory 에나 상주할 수 있지만, suffix가. sp인 것이좋다. • Input file 에는 special control character를 사용하지 않는다. • Control commands은 ‘. (period) ’로 기술한다. • 2 line 이상을 차지하는 긴 문장일 경우 ‘+’ 기호를 사용하여 기술할 수 있다. • Comment(설명문)는 line의 처음에 ‘*’ 기호를 쓰고 붙일 수 있다. • $’ 기호를 사용하여 input text 와 같은 line에도 comment를 넣을 수 있다. • 대 소문자의 구분이 없다. Example Inverter simulation . lib ‘snu 018. prm’ TT . param vddpar=1. 8 . param r=0. 01 n * Inverter sub circuit . subckt inverter a y pw=1. 4 u nw=0. 7 u mn 1 y a gnd n w=nw l=0. 18 u mp 0 vdd a y vdd p w=pw l=0. 18 u . ends inverter xinv 0 in out inverter pw=20 u nw=10 u vvdd gnd ‘vddpar’ vin in gnd pulse( 0 ‘vddpar’ 5 n ‘r’’r’ 10 n 20 n) . global vdd gnd . option post . tran 0. 01 n 40 n $ transient analysis . end

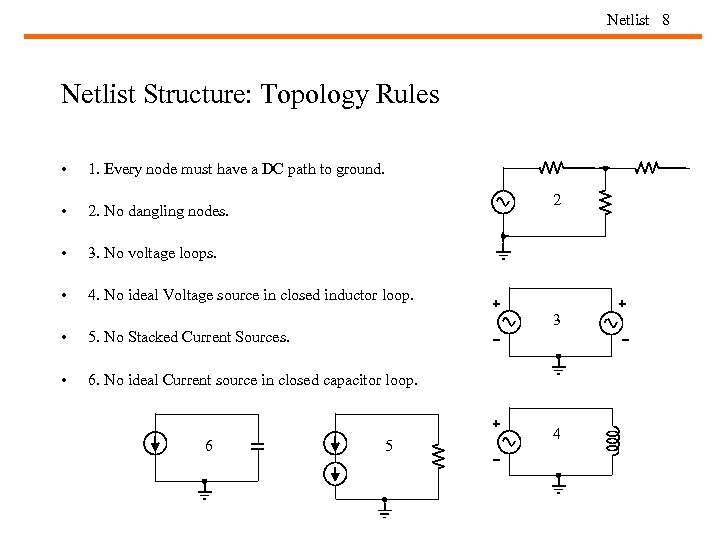

Netlist 8 Netlist Structure: Topology Rules • 1. Every node must have a DC path to ground. • 2. No dangling nodes. • 3. No voltage loops. • 4. No ideal Voltage source in closed inductor loop. 2 + + 3 • 5. No Stacked Current Sources. • 6. No ideal Current source in closed capacitor loop. - + 6 5 - - 4

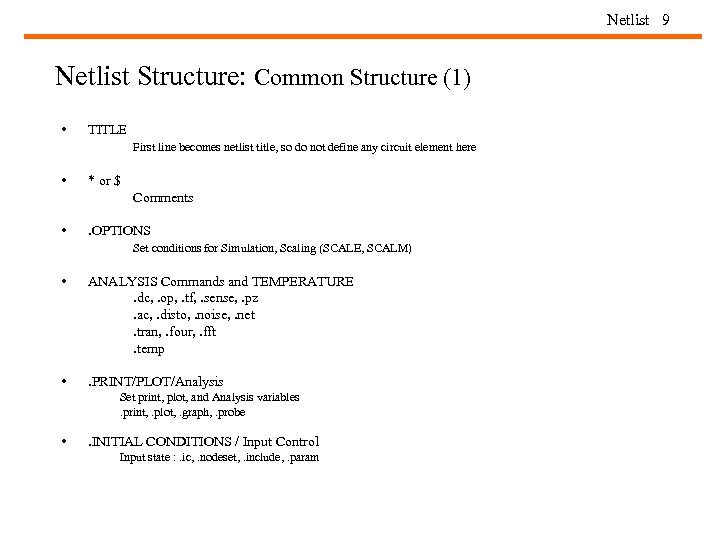

Netlist 9 Netlist Structure: Common Structure (1) • TITLE First line becomes netlist title, so do not define any circuit element here • * or $ Comments • . OPTIONS Set conditions for Simulation, Scaling (SCALE, SCALM) • ANALYSIS Commands and TEMPERATURE . dc, . op, . tf, . sense, . pz . ac, . disto, . noise, . net . tran, . four, . fft . temp • . PRINT/PLOT/Analysis Set print, plot, and Analysis variables . print, . plot, . graph, . probe • . INITIAL CONDITIONS / Input Control Input state : . ic, . nodeset, . include, . param

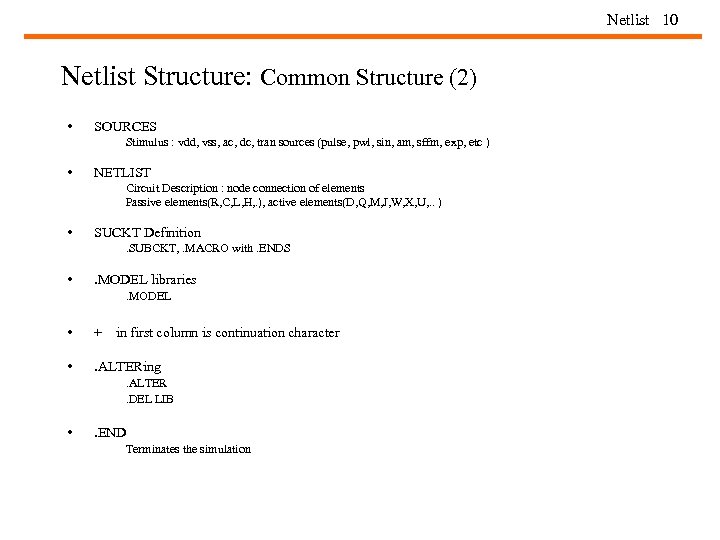

Netlist 10 Netlist Structure: Common Structure (2) • SOURCES Stimulus : vdd, vss, ac, dc, tran sources (pulse, pwl, sin, am, sffm, exp, etc ) • NETLIST Circuit Description : node connection of elements Passive elements(R, C, L, H, . ), active elements(D, Q, M, J, W, X, U, . . ) • SUCKT Definition . SUBCKT, . MACRO with. ENDS • . MODEL libraries . MODEL • + in first column is continuation character • . ALTERing . ALTER . DEL LIB • . END Terminates the simulation

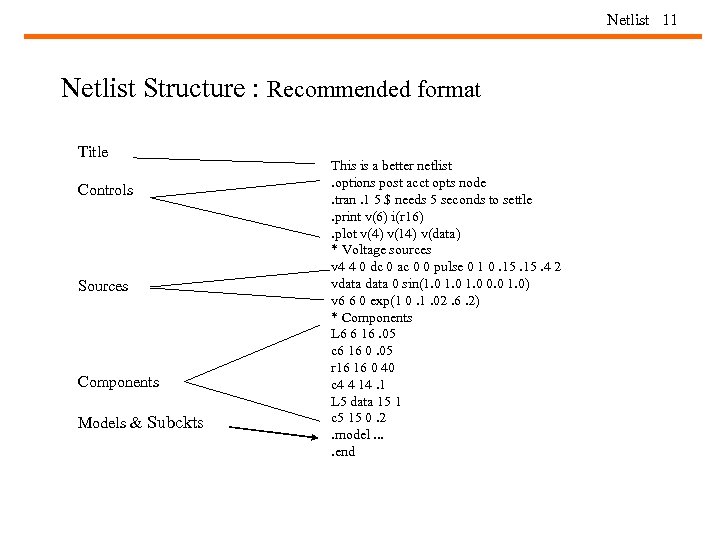

Netlist 11 Netlist Structure : Recommended format Title Controls Sources Components Models & Subckts This is a better netlist . options post acct opts node . tran. 1 5 $ needs 5 seconds to settle . print v(6) i(r 16) . plot v(4) v(14) v(data) * Voltage sources v 4 4 0 dc 0 ac 0 0 pulse 0 1 0. 15. 4 2 vdata 0 sin(1. 0 0. 0 1. 0) v 6 6 0 exp(1 0. 1. 02. 6. 2) * Components L 6 6 16. 05 c 6 16 0. 05 r 16 16 0 40 c 4 4 14. 1 L 5 data 15 1 c 5 15 0. 2 . model. . end

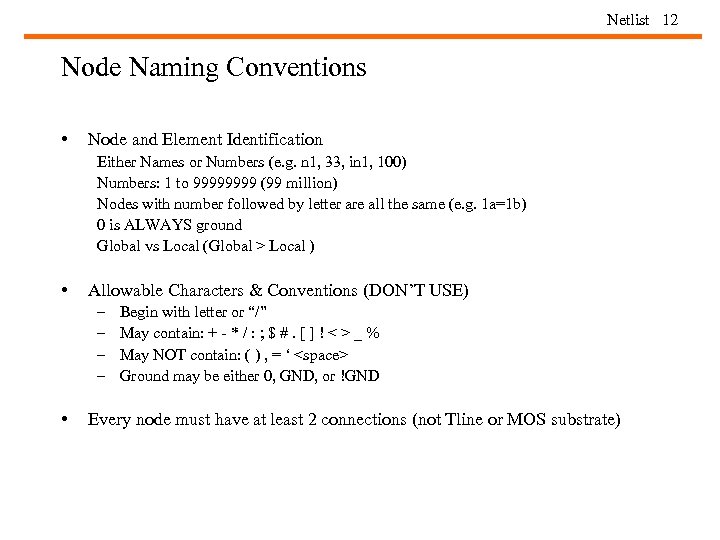

Netlist 12 Node Naming Conventions • Node and Element Identification Either Names or Numbers (e. g. n 1, 33, in 1, 100) Numbers: 1 to 9999 (99 million) Nodes with number followed by letter are all the same (e. g. 1 a=1 b) 0 is ALWAYS ground Global vs Local (Global > Local ) • Allowable Characters & Conventions (DON’T USE) – – • Begin with letter or “/” May contain: + - * / : ; $ #. [ ] ! < > _ % May NOT contain: ( ) , = ‘ <space> Ground may be either 0, GND, or !GND Every node must have at least 2 connections (not Tline or MOS substrate)

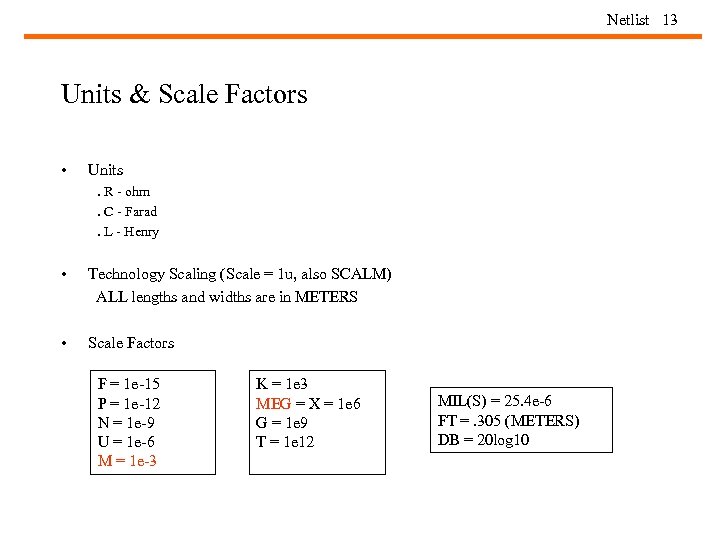

Netlist 13 Units & Scale Factors • Units . R - ohm . C - Farad . L - Henry • • Technology Scaling (Scale = 1 u, also SCALM) ALL lengths and widths are in METERS Scale Factors F = 1 e-15 P = 1 e-12 N = 1 e-9 U = 1 e-6 M = 1 e-3 K = 1 e 3 MEG = X = 1 e 6 G = 1 e 9 T = 1 e 12 MIL(S) = 25. 4 e-6 FT =. 305 (METERS) DB = 20 log 10

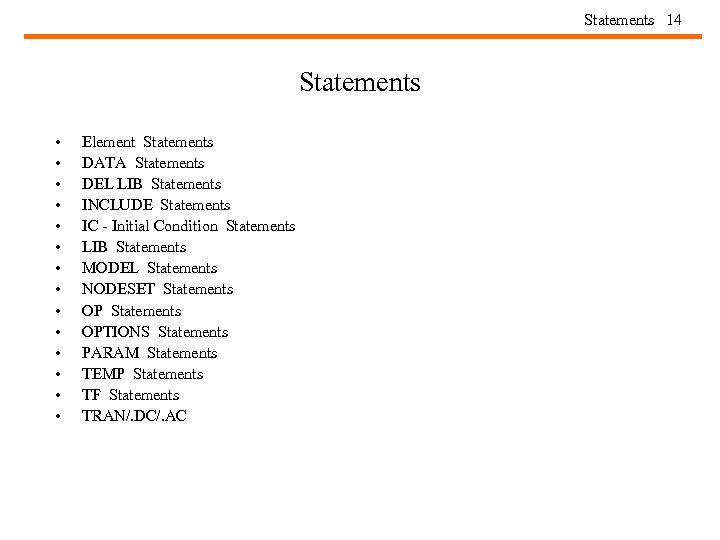

Statements 14 Statements • • • • Element Statements DATA Statements DEL LIB Statements INCLUDE Statements IC - Initial Condition Statements LIB Statements MODEL Statements NODESET Statements OPTIONS Statements PARAM Statements TEMP Statements TF Statements TRAN/. DC/. AC

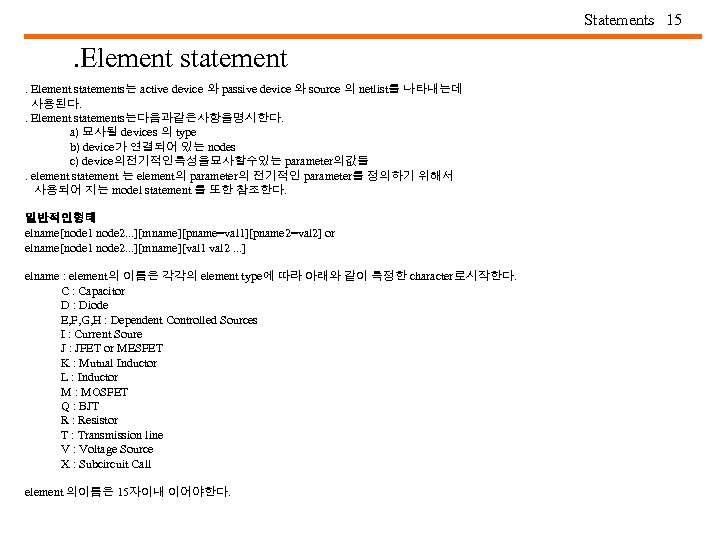

Statements 15 . Element statements는 active device 와 passive device 와 source 의 netlist를 나타내는데 사용된다. . Element statements는다음과같은사항을명시한다. a) 묘사될 devices 의 type b) device가 연결되어 있는 nodes c) device의전기적인특성을묘사할수있는 parameter의값들 . element statement 는 element의 parameter의 전기적인 parameter를 정의하기 위해서 사용되어 지는 model statement 를 또한 참조한다. 일반적인형태 elname[node 1 node 2. . . ][mname][pname=val 1][pname 2=val 2] or elname[node 1 node 2. . . ][mname][val 1 val 2. . . ] elname : element의 이름은 각각의 element type에 따라 아래와 같이 특정한 character로시작한다. C : Capacitor D : Diode E, F, G, H : Dependent Controlled Sources I : Current Soure J : JFET or MESFET K : Mutual Inductor L : Inductor M : MOSFET Q : BJT R : Resistor T : Transmission line V : Voltage Source X : Subcircuit Call element 의이름은 15자이내 이어야한다.

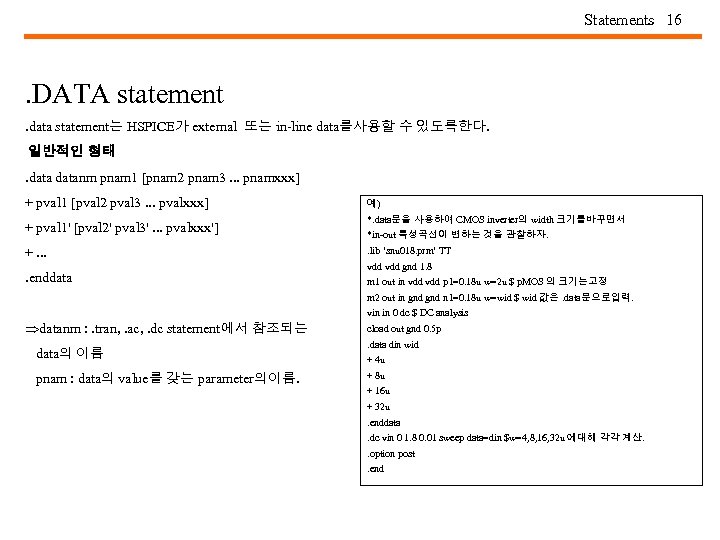

Statements 16 . DATA statement . data statement는 HSPICE가 external 또는 in-line data를사용할 수 있도록한다. 일반적인 형태 . datanm pnam 1 [pnam 2 pnam 3. . . pnamxxx] + pval 1 [pval 2 pval 3. . . pvalxxx] + pval 1' [pval 2' pval 3'. . . pvalxxx'] +. . enddata 예) *. data문을 사용하여 CMOS inverter의 width 크기를바꾸면서 *in-out 특성곡선이 변하는 것을 관찰하자. . lib ‘snu 018. prm’ TT vdd gnd 1. 8 m 1 out in vdd p l=0. 18 u w=2 u $ p. MOS 의 크기는고정 m 2 out in gnd n l=0. 18 u w=wid $ wid 값은. data문으로입력. Þdatanm : . tran, . ac, . dc statement에서 참조되는 data의 이름 pnam : data의 value를 갖는 parameter의이름. vin in 0 dc $ DC analysis cload out gnd 0. 5 p . data din wid + 4 u + 8 u + 16 u + 32 u . enddata . dc vin 0 1. 8 0. 01 sweep data=din $w=4, 8, 16, 32 u 에대해 각각 계산. . option post . end

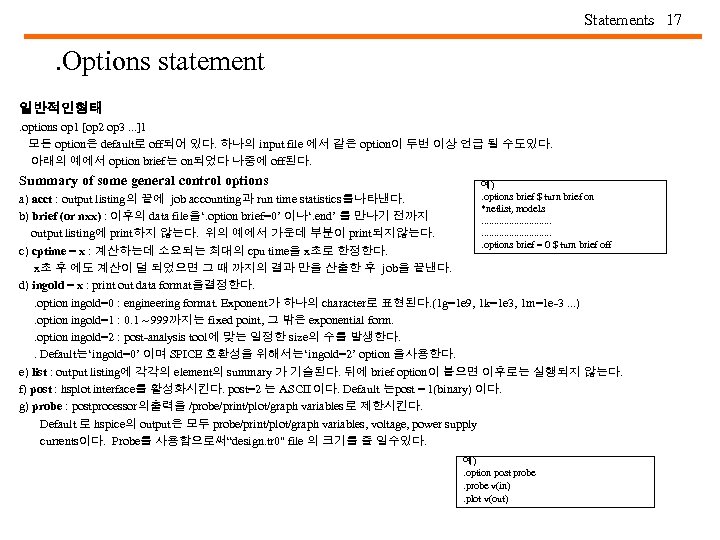

Statements 17 . Options statement 일반적인형태. options op 1 [op 2 op 3. . . ]1 모든 option은 default로 off되어 있다. 하나의 input file 에서 같은 option이 두번 이상 언급 될 수도있다. 아래의 예에서 option brief는 on되었다 나중에 off된다. Summary of some general control options 예) . options brief $ turn brief on a) acct : output listing의 끝에 job accounting과 run time statistics를나타낸다. *netlist, models b) brief (or nxx) : 이후의 data file을‘. option brief=0’ 이나‘. end’ 를 만나기 전까지. . . . output listing에 print하지 않는다. 위의 예에서 가운데 부분이 print되지않는다. . options brief = 0 $ turn brief off c) cptime = x : 계산하는데 소요되는 최대의 cpu time을 x초로 한정한다. x초 후 에도 계산이 덜 되었으면 그 때 까지의 결과 만을 산출한 후 job을 끝낸다. d) ingold = x : print out data format을결정한다. . option ingold=0 : engineering format. Exponent가 하나의 character로 표현된다. (1 g=1 e 9, 1 k=1 e 3, 1 m=1 e-3. . . ) . option ingold=1 : 0. 1 ~ 999까지는 fixed point, 그 밖은 exponential form. . option ingold=2 : post-analysis tool에 맞는 일정한 size의 수를 발생한다. . Default는‘ingold=0’ 이며 SPICE 호환성을 위해서는‘ingold=2’ option 을사용한다. e) list : output listing에 각각의 element의 summary 가 기술된다. 뒤에 brief option이 붙으면 이후로는 실행되지 않는다. f) post : hsplot interface를 활성화시킨다. post=2 는 ASCII 이다. Default 는post = 1(binary) 이다. g) probe : postprocessor의출력을 /probe/print/plot/graph variables로 제한시킨다. Default 로 hspice의 output은 모두 probe/print/plot/graph variables, voltage, power supply currents이다. Probe를 사용함으로써“design. tr 0" file 의 크기를 줄 일수있다. 예) . option post probe v(in) . plot v(out)

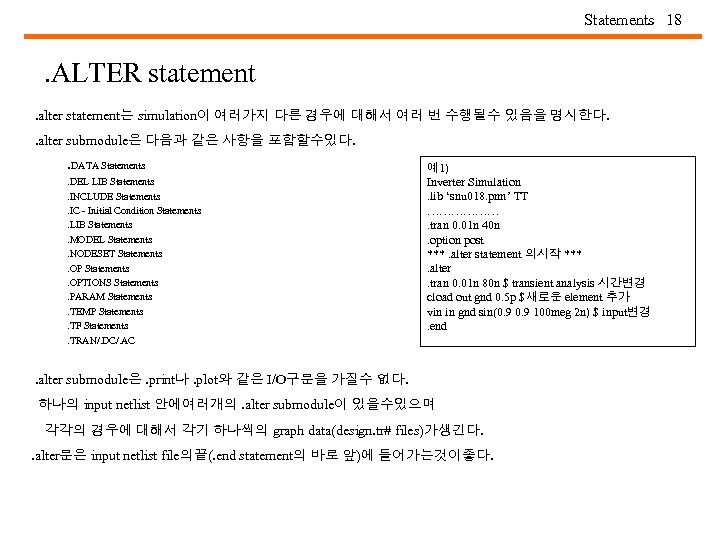

Statements 18 . ALTER statement . alter statement는 simulation이 여러가지 다른 경우에 대해서 여러 번 수행될수 있음을 명시한다. . alter submodule은 다음과 같은 사항을 포함할수있다. . DATA Statements . DEL LIB Statements . INCLUDE Statements . IC - Initial Condition Statements . LIB Statements . MODEL Statements . NODESET Statements . OPTIONS Statements . PARAM Statements . TEMP Statements . TF Statements . TRAN/. DC/. AC 예1) Inverter Simulation . lib ‘snu 018. prm’ TT ……………… . tran 0. 01 n 40 n . option post ***. alter statement 의시작 *** . alter . tran 0. 01 n 80 n $ transient analysis 시간변경 cload out gnd 0. 5 p $새로운 element 추가 vin in gnd sin(0. 9 100 meg 2 n) $ input변경. end . alter submodule은. print나. plot와 같은 I/O구문을 가질수 없다. 하나의 input netlist 안에여러개의. alter submodule이 있을수있으며 각각의 경우에 대해서 각기 하나씩의 graph data(design. tr# files)가생긴다. . alter문은 input netlist file의끝(. end statement의 바로 앞)에 들어가는것이좋다.

![Statements 19 . INCLUDE statement 일반적인형태 . include '[filepath]filename' or . inc '[filepath]filename' . Statements 19 . INCLUDE statement 일반적인형태 . include '[filepath]filename' or . inc '[filepath]filename' .](https://present5.com/presentation/f7b7944291c64c5c02b677b74a890756/image-20.jpg)

Statements 19 . INCLUDE statement 일반적인형태 . include '[filepath]filename' or . inc '[filepath]filename' . include statement의아래에 file의 내용을 그대로 patch한다. output listing에서 쉽게 확인 할수있다. . lib statement 자주이용되는명령, device models, subcircuits등은 library file에두고 . lib statement로 불러 쓸 수있다. . library 호출문의 일반적인형태 lib '[filepath]filename' entryname . include와는 달리 library 내의 한정된 부분(entry)만이호출된다. 예) . lib 'MOS 1: [robby]macro. lib' lm 101 . lib 'models' cmos 1 $ models library내의 cmos 1 entry를 호출. .

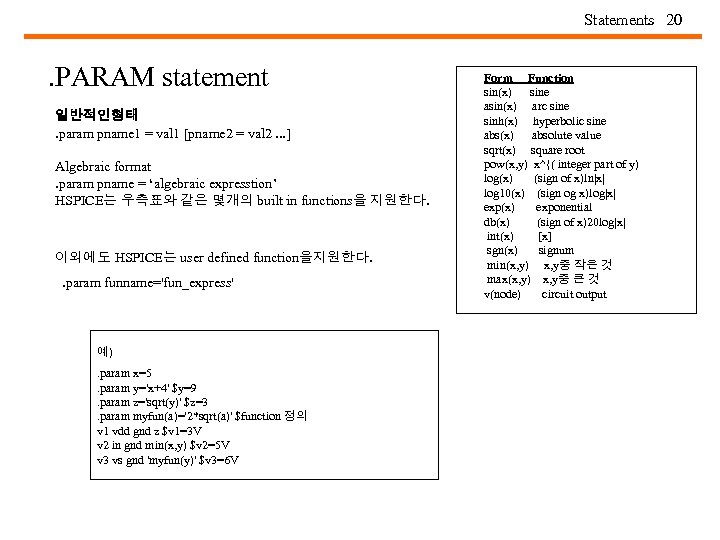

Statements 20 . PARAM statement 일반적인형태 . param pname 1 = val 1 [pname 2 = val 2. . . ] Algebraic format . param pname = ‘algebraic expresstion’ HSPICE는 우측표와 같은 몇개의 built in functions을 지원한다. 이외에도 HSPICE는 user defined function을지원한다. . param funname='fun_express' 예) . param x=5 . param y='x+4' $y=9 . param z='sqrt(y)' $z=3 . param myfun(a)='2*sqrt(a)' $function 정의 v 1 vdd gnd z $v 1=3 V v 2 in gnd min(x, y) $v 2=5 V v 3 vs gnd 'myfun(y)' $v 3=6 V Form Function sin(x) sine asin(x) arc sine sinh(x) hyperbolic sine abs(x) absolute value sqrt(x) square root pow(x, y) x^{( integer part of y) log(x) (sign of x)ln|x| log 10(x) (sign og x)log|x| exp(x) exponential db(x) (sign of x)20 log|x| int(x) [x] sgn(x) signum min(x, y) x, y중 작은 것 max(x, y) x, y중 큰 것 v(node) circuit output

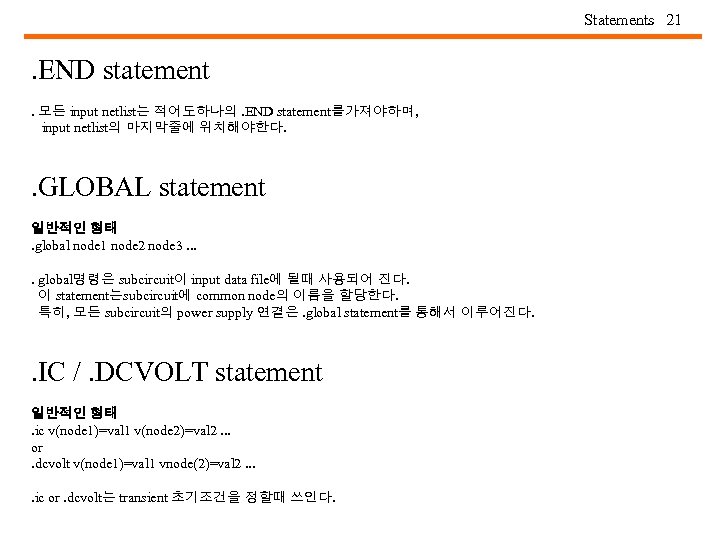

Statements 21 . END statement . 모든 input netlist는 적어도하나의. END statement를가져야하며, input netlist의 마지막줄에 위치해야한다. . GLOBAL statement 일반적인 형태 . global node 1 node 2 node 3. . global명령은 subcircuit이 input data file에 될때 사용되어 진다. 이 statement는subcircuit에 common node의 이름을 할당한다. 특히, 모든 subcircuit의 power supply 연결은. global statement를 통해서 이루어진다. . IC /. DCVOLT statement 일반적인 형태 . ic v(node 1)=val 1 v(node 2)=val 2. . . or . dcvolt v(node 1)=val 1 vnode(2)=val 2. . ic or. dcvolt는 transient 초기조건을 정할때 쓰인다.

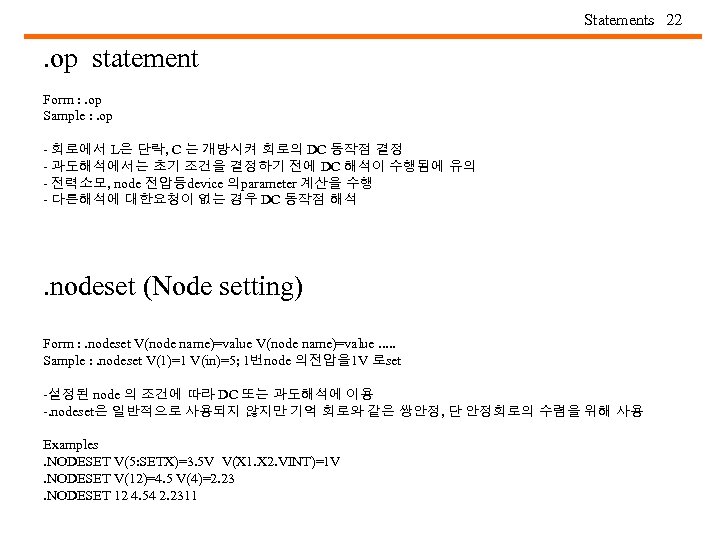

Statements 22 . op statement Form : . op Sample : . op - 회로에서 L은 단락, C 는 개방시켜 회로의 DC 동작점 결정 - 과도해석에서는 초기 조건을 결정하기 전에 DC 해석이 수행됨에 유의 - 전력소모, node 전압등device 의parameter 계산을 수행 - 다른해석에 대한요청이 없는 경우 DC 동작점 해석 . nodeset (Node setting) Form : . nodeset V(node name)=value. . . Sample : . nodeset V(1)=1 V(in)=5; 1번node 의전압을1 V 로set -설정된 node 의 조건에 따라 DC 또는 과도해석에 이용 -. nodeset은 일반적으로 사용되지 않지만 기억 회로와 같은 쌍안정, 단 안정회로의 수렴을 위해 사용 Examples . NODESET V(5: SETX)=3. 5 V V(X 1. X 2. VINT)=1 V . NODESET V(12)=4. 5 V(4)=2. 23 . NODESET 12 4. 54 2. 2311

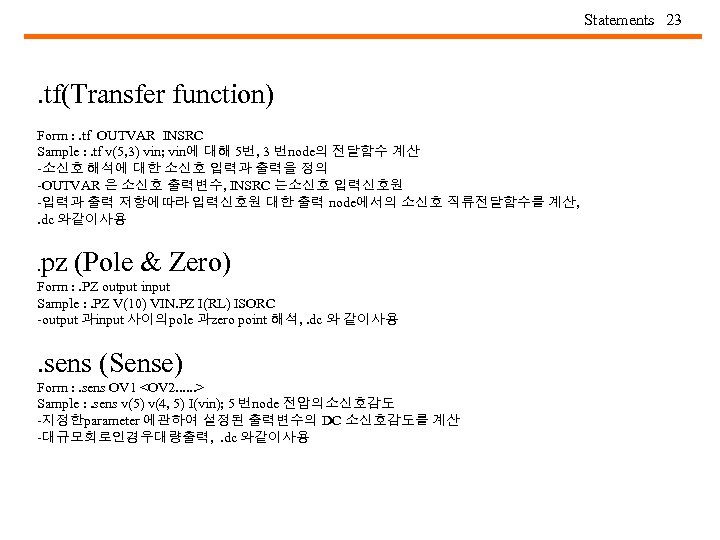

Statements 23 . tf(Transfer function) Form : . tf OUTVAR INSRC Sample : . tf v(5, 3) vin; vin에 대해 5번, 3 번node의 전달함수 계산 -소신호 해석에 대한 소신호 입력과 출력을 정의 -OUTVAR 은 소신호 출력변수, INSRC 는소신호 입력신호원 -입력과 출력 저항에따라 입력신호원 대한 출력 node에서의 소신호 직류전달함수를 계산, . dc 와같이사용 pz (Pole & Zero) . Form : . PZ output input Sample : . PZ V(10) VIN. PZ I(RL) ISORC -output 과input 사이의pole 과zero point 해석, . dc 와 같이사용 . sens (Sense) Form : . sens OV 1 <OV 2. . . > Sample : . sens v(5) v(4, 5) I(vin); 5 번node 전압의소신호감도 -지정한parameter 에관하여 설정된 출력변수의 DC 소신호감도를 계산 -대규모회로인경우대량출력, . dc 와같이사용

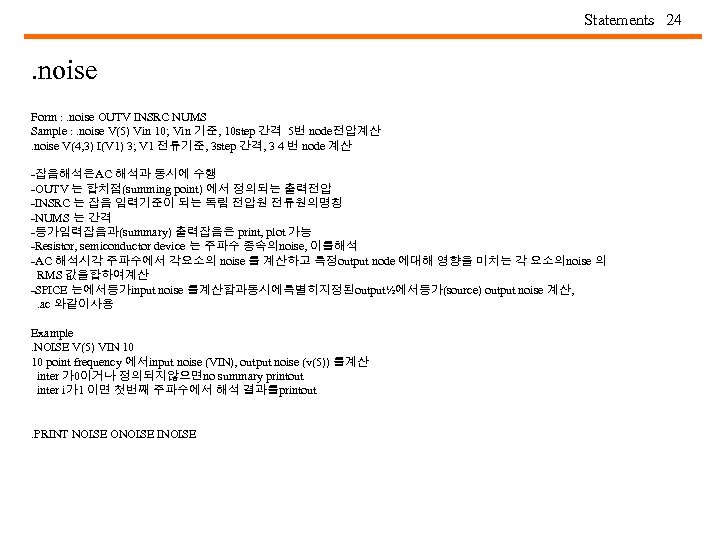

Statements 24 . noise Form : . noise OUTV INSRC NUMS Sample : . noise V(5) Vin 10; Vin 기준, 10 step 간격 5번 node전압계산 . noise V(4, 3) I(V 1) 3; V 1 전류기준, 3 step 간격, 3 4 번 node 계산 -잡음해석은AC 해석과 동시에 수행 -OUTV 는 합치점(summing point) 에서 정의되는 출력전압 -INSRC 는 잡음 입력기준이 되는 독립 전압원 전류원의명칭 -NUMS 는 간격 -등가입력잡음과(summary) 출력잡음은 print, plot 가능 -Resistor, semiconductor device 는 주파수 종속의noise, 이를해석 -AC 해석시각 주파수에서 각요소의 noise 를 계산하고 특정output node 에대해 영향을 미치는 각 요소의noise 의 RMS 값을합하여계산 -SPICE 는에서등가input noise 를계산함과동시에특별히지정된output½에서등가(source) output noise 계산, . ac 와같이사용 Example . NOISE V(5) VIN 10 10 point frequency 에서input noise (VIN), output noise (v(5)) 를계산 inter 가0이거나 정의되지않으면no summary printout inter i가1 이면 첫번째 주파수에서 해석 결과를printout . PRINT NOISE ONOISE INOISE

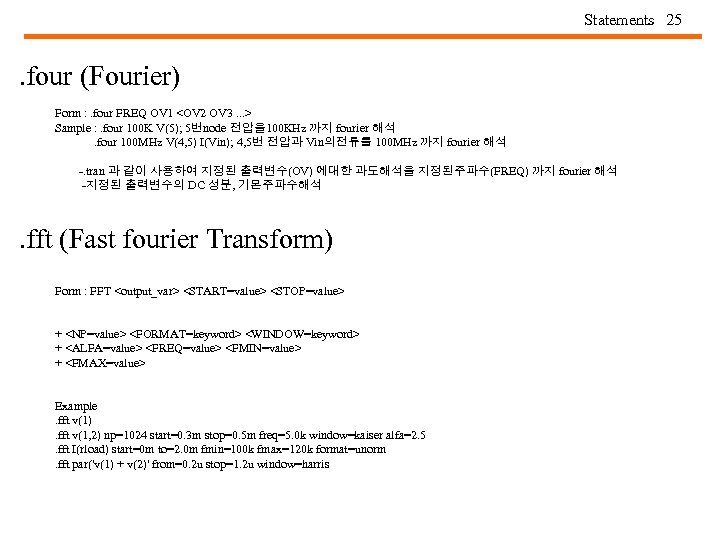

Statements 25 . four (Fourier) Form : . four FREQ OV 1 <OV 2 OV 3. . . > Sample : . four 100 K V(5); 5번node 전압을100 KHz 까지 fourier 해석 . four 100 MHz V(4, 5) I(Vin); 4, 5번 전압과 Vin의전류를 100 MHz 까지 fourier 해석 -. tran 과 같이 사용하여 지정된 출력변수(OV) 에대한 과도해석을 지정된주파수(FREQ) 까지 fourier 해석 -지정된 출력변수의 DC 성분, 기본주파수해석 . fft (Fast fourier Transform) Form : FFT <output_var> <START=value> <STOP=value> + <NP=value> <FORMAT=keyword> <WINDOW=keyword> + <ALFA=value> <FREQ=value> <FMIN=value> + <FMAX=value> Example . fft v(1) . fft v(1, 2) np=1024 start=0. 3 m stop=0. 5 m freq=5. 0 k window=kaiser alfa=2. 5 . fft I(rload) start=0 m to=2. 0 m fmin=100 k fmax=120 k format=unorm . fft par('v(1) + v(2)' from=0. 2 u stop=1. 2 u window=harris

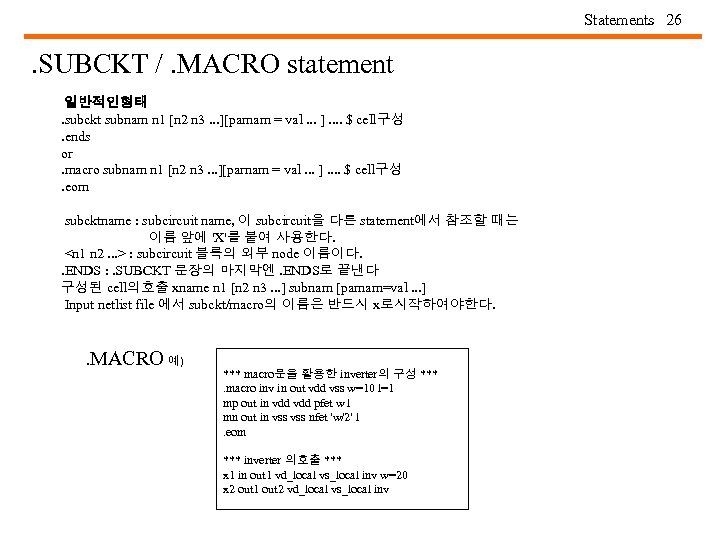

Statements 26 . SUBCKT /. MACRO statement 일반적인형태 . subckt subnam n 1 [n 2 n 3. . . ][parnam = val. . . ]. . $ cell구성. ends or . macro subnam n 1 [n 2 n 3. . . ][parnam = val. . . ]. . $ cell구성 . eom subcktname : subcircuit name, 이 subcircuit을 다른 statement에서 참조할 때는 이름 앞에 'X'를 붙여 사용한다. <n 1 n 2. . . > : subcircuit 블록의 외부 node 이름이다. . ENDS : . SUBCKT 문장의 마지막엔. ENDS로 끝낸다 구성된 cell의호출 xname n 1 [n 2 n 3. . . ] subnam [parnam=val. . . ] Input netlist file 에서 subckt/macro의 이름은 반드시 x로시작하여야한다. . MACRO 예) *** macro문을 활용한 inverter의 구성 *** . macro inv in out vdd vss w=10 l=1 mp out in vdd pfet w l mn out in vss nfet 'w/2' l . eom *** inverter 의호출 *** x 1 in out 1 vd_local vs_local inv w=20 x 2 out 1 out 2 vd_local vs_local inv

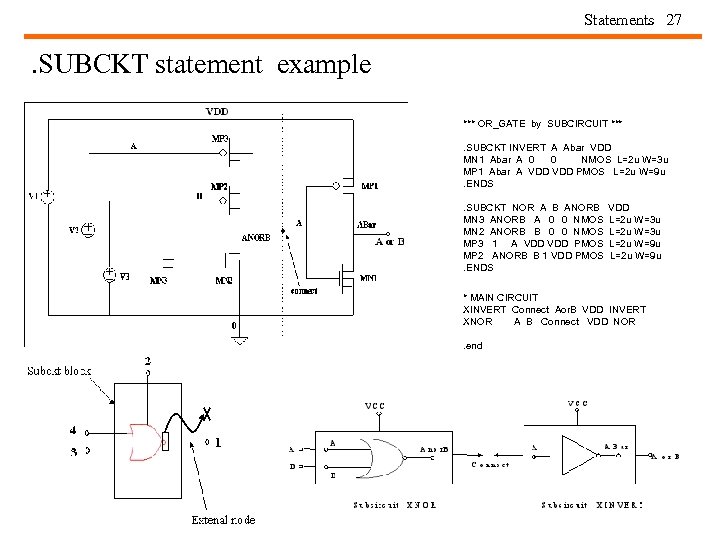

Statements 27 . SUBCKT statement example *** OR_GATE by SUBCIRCUIT ***. SUBCKT INVERT A Abar VDD MN 1 Abar A 0 0 NMOS L=2 u W=3 u MP 1 Abar A VDD PMOS L=2 u W=9 u. ENDS. SUBCKT NOR A B ANORB MN 3 ANORB A 0 0 NMOS MN 2 ANORB B 0 0 NMOS MP 3 1 A VDD PMOS MP 2 ANORB B 1 VDD PMOS. ENDS VDD L=2 u W=3 u L=2 u W=9 u * MAIN CIRCUIT XINVERT Connect Aor. B VDD INVERT XNOR A B Connect VDD NOR. end

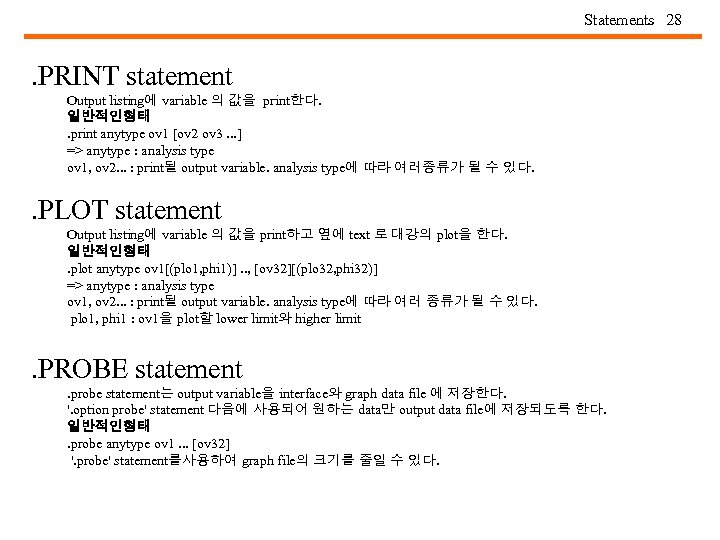

Statements 28 . PRINT statement Output listing에 variable 의 값을 print한다. 일반적인형태. print anytype ov 1 [ov 2 ov 3. . . ] => anytype : analysis type ov 1, ov 2. . . : print될 output variable. analysis type에 따라 여러종류가 될 수 있다. . PLOT statement Output listing에 variable 의 값을 print하고 옆에 text 로 대강의 plot을 한다. 일반적인형태 . plot anytype ov 1[(plo 1, phi 1)]. . , [ov 32][(plo 32, phi 32)] => anytype : analysis type ov 1, ov 2. . . : print될 output variable. analysis type에 따라 여러 종류가 될 수 있다. plo 1, phi 1 : ov 1을 plot할 lower limit와 higher limit . PROBE statement . probe statement는 output variable을 interface와 graph data file 에 저장한다. '. option probe' statement 다음에 사용되어 원하는 data만 output data file에 저장되도록 한다. 일반적인형태 . probe anytype ov 1. . . [ov 32] '. probe' statement를사용하여 graph file의 크기를 줄일 수 있다.

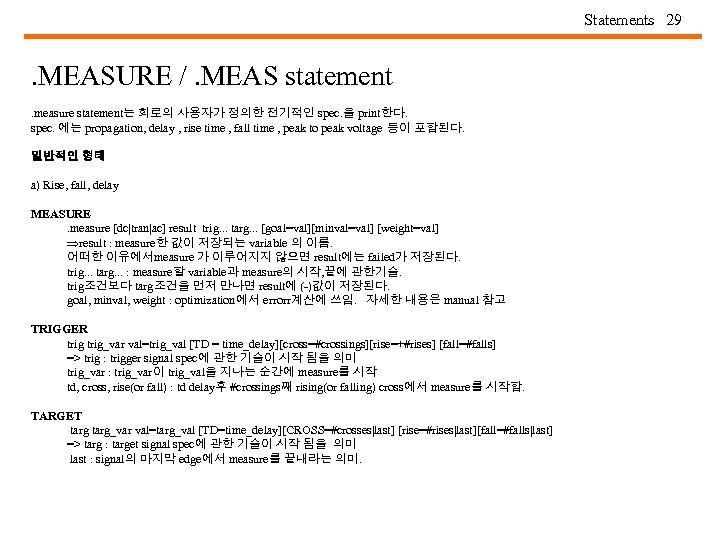

Statements 29 . MEASURE /. MEAS statement . measure statement는 회로의 사용자가 정의한 전기적인 spec. 을 print한다. spec. 에는 propagation, delay , rise time , fall time , peak to peak voltage 등이 포함된다. 일반적인 형태 a) Rise, fall, delay MEASURE . measure [dc|tran|ac] result trig. . . targ. . . [goal=val][minval=val] [weight=val] Þresult : measure한 값이 저장되는 variable 의 이름. 어떠한 이유에서measure 가 이루어지지 않으면 result에는 failed가 저장된다. trig. . . targ. . . : measure할 variable과 measure의 시작, 끝에 관한기술. trig조건보다 targ조건을 먼저 만나면 result에 (-)값이 저장된다. goal, minval, weight : optimization에서 errorr계산에 쓰임. 자세한 내용은 manual 참고 TRIGGER trig_var val=trig_val [TD = time_delay][cross=#crossings][rise=+#rises] [fall=#falls] => trig : trigger signal spec에 관한 기술이 시작 됨을 의미 trig_var : trig_var이 trig_val을 지나는 순간에 measure를 시작 td, cross, rise(or fall) : td delay후 #crossings째 rising(or falling) cross에서 measure를 시작함. TARGET targ_var val=targ_val [TD=time_delay][CROSS=#crosses|last] [rise=#rises|last][fall=#falls|last] => targ : target signal spec에 관한 기술이 시작 됨을 의미 last : signal의 마지막 edge에서 measure를 끝내라는 의미.

![Statements 30 b) Average, RMS, MIN, MAX, and peak to peak measurements . measure[dc|tran|ac] Statements 30 b) Average, RMS, MIN, MAX, and peak to peak measurements . measure[dc|tran|ac]](https://present5.com/presentation/f7b7944291c64c5c02b677b74a890756/image-31.jpg)

Statements 30 b) Average, RMS, MIN, MAX, and peak to peak measurements . measure[dc|tran|ac] result func out_var[from=val][to=val] + [goal=val][minval=val][weight=val] => result : 측정한 결과를 result에 보관 func : avg, max, min, pp(peak to peak), rms, integ 중선택 . measure statement의 결과는 output listing에 result값이 print되고 자세한 내용은 *. mt 0 file 이 생성되며 그 안에 기술된다. . gl의 graph window에서 measurement를 turn on하고 zoom in, zoom out을 적당히 조절하여 measure를 할 수 도있 다. 예) **10 ns 이후 v(1)이 2. 5 V를 지나는 두 번째 rising edge에서 ***v(2)가 2. 5 V를 지나는 두번째 falling edge까지의시간을 ***측정하여 tdlay에저장하기. . measure tran tdlay trig v(1) val=2. 5 td=10 n rise=2 targ v(2) val=2. 5 fall=2 *** 10 ns 에서 55 ns까지 v(10)의 평균 값을 구하여 avg_val에저장 . meas tran avg_val avg v(10) from=10 ns to 55 ns 예) ***inverter의 propagation delay 측정*** . lib ‘snu 018. prm’ TT vdd gnd 1. 8 vin in gnd pulse(0 1. 8 2 n 2 n 2 n 10 n 26 n) m 1 out in vdd p l=0. 18 u w=5 u m 2 out in gnd n l=0. 18 u w=2 u cload out gnd 0. 5 p . tran 1 n 100 n . option post . measure tran tdelay trig v(in) val=0. 9 td=10 n rise=2 + targ v(out) val=0. 9 fall=2 . end => 결과 : output listing과 *. mt 0 file에 'tdelay=6. 962 e-10'라는 Message를 확인 할 수 있다.

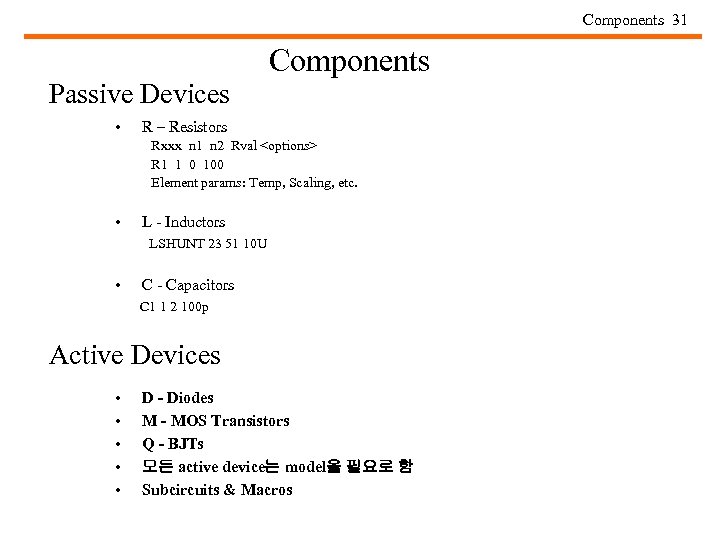

Components 31 Components Passive Devices • R – Resistors Rxxx n 1 n 2 Rval <options> R 1 1 0 100 Element params: Temp, Scaling, etc. • L - Inductors LSHUNT 23 51 10 U • C - Capacitors C 1 1 2 100 p Active Devices • • • D - Diodes M - MOS Transistors Q - BJTs 모든 active device는 model을 필요로 함 Subcircuits & Macros

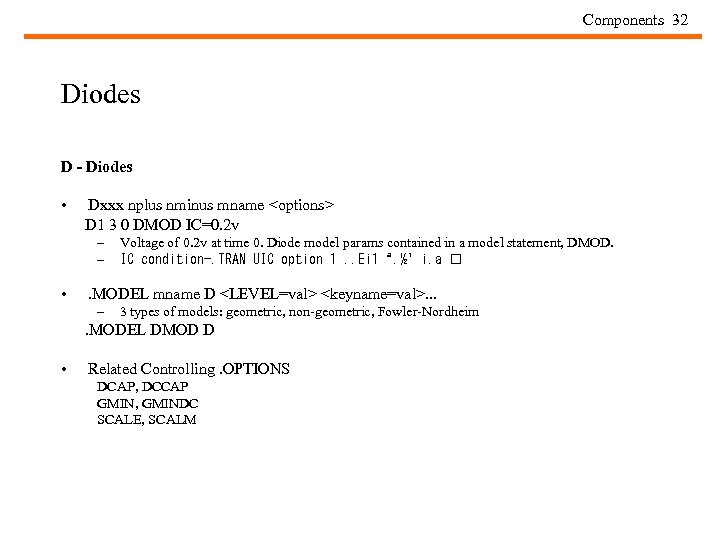

Components 32 Diodes D - Diodes • Dxxx nplus nminus mname <options> D 1 3 0 DMOD IC=0. 2 v – – • Voltage of 0. 2 v at time 0. Diode model params contained in a model statement, DMOD. IC condition-. TRAN UIC option 1. . Ei 1 ª. ½¹ i. a . MODEL mname D <LEVEL=val> <keyname=val>. . . – 3 types of models: geometric, non-geometric, Fowler-Nordheim . MODEL DMOD D • Related Controlling. OPTIONS DCAP, DCCAP GMIN, GMINDC SCALE, SCALM

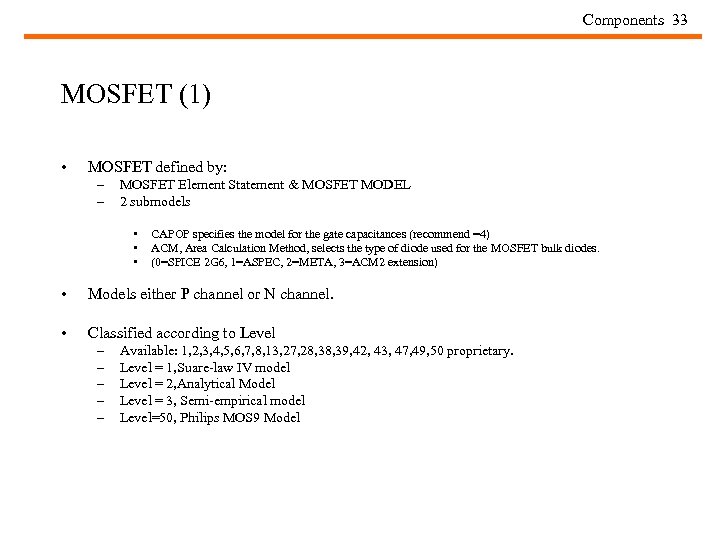

Components 33 MOSFET (1) • MOSFET defined by: – – MOSFET Element Statement & MOSFET MODEL 2 submodels • • • CAPOP specifies the model for the gate capacitances (recommend =4) ACM, Area Calculation Method, selects the type of diode used for the MOSFET bulk diodes. (0=SPICE 2 G 6, 1=ASPEC, 2=META, 3=ACM 2 extension) • Models either P channel or N channel. • Classified according to Level – – – Available: 1, 2, 3, 4, 5, 6, 7, 8, 13, 27, 28, 39, 42, 43, 47, 49, 50 proprietary. Level = 1, Suare-law IV model Level = 2, Analytical Model Level = 3, Semi-empirical model Level=50, Philips MOS 9 Model

Components 34 MOSFET (2) • BSIM(Berkeley Short channel IGFET Model) – BSIM은 여러 개의 small device 효과를 설명하고 있고, 실험적으로 유도된 input값을 받아 들인다. – BSIM의 parameter는 empirically-based값이므로 SPICEI로 하여금 simple device model의 한 계를 극복함 – BSIM은 비교적 정확한 회로 simulation을 가능케 함 – Level=13, BSIM 1 – Level=28, BSIM 1 derivative; Avan proprietary - excellent model – Level=39, BSIM 2 – Level=49, BSIM 3 v 3; Level=47, BSIM 3 v 2; Level=42, BSIM 3 v 1

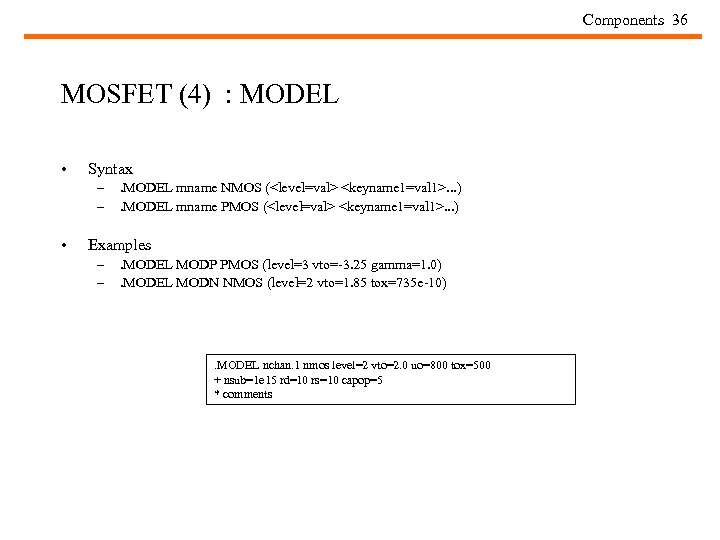

Components 35 MOSFET (3) : Element description • Syntax – – • Mxxx DRAIN GATE SOURCE BULK Examples – – – • Mxxx nd ng ns <nb> mname <L=val> <W=val> <options. . . > Mxxx nd ng ns <nb> mname lval wval. . . M 1 3 4 5 0 nch 5 u 10 u M 31 2 17 6 10 MODM l=5 u w=2 u Mabc 2 9 3 0 mymod l=10 u w=5 u ad=100 p as=100 p pd=40 u ps=40 u SCALING (See Controls & Options Session) – – Units are controlled by. OPTION SCALE and MODEL param SCALM. Default L and W: METERS!!! M 1 10 20 30 0 modnam l=5 u w=10 u . OPTION SCALE=1 e-6 equivalent M 1 10 20 30 0 modnam l=5 w=10

Components 36 MOSFET (4) : MODEL • Syntax – – • . MODEL mname NMOS (<level=val> <keyname 1=val 1>. . . ) . MODEL mname PMOS (<level=val> <keyname 1=val 1>. . . ) Examples – – . MODEL MODP PMOS (level=3 vto=-3. 25 gamma=1. 0) . MODEL MODN NMOS (level=2 vto=1. 85 tox=735 e-10) . MODEL nchan. 1 nmos level=2 vto=2. 0 uo=800 tox=500 + nsub=1 e 15 rd=10 rs=10 capop=5 * comments

Components 37 JFET/MESFET • Element Syntax – • Examples – – • Jxxx nd ng ns <nb> mname <W=val> <L=val> <options> Jxxx DRAIN GATE SOURCE BULK J 1 7 2 3 JM 1 jmes xload gdrive common jmodel SCALING (See Controls & Options Session) – – – Units are controlled by. OPTION SCALE and MODEL param SCALM. Controlled by element parameters: M and AREA Default L and W: METERS!!!

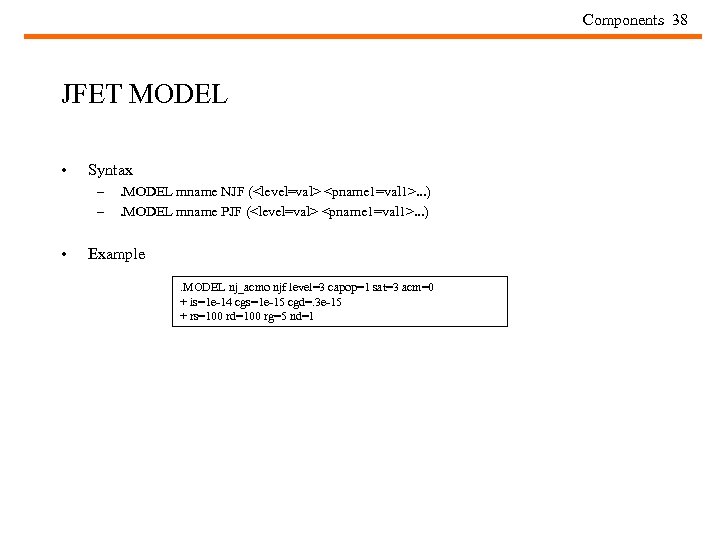

Components 38 JFET MODEL • Syntax – – • . MODEL mname NJF (<level=val> <pname 1=val 1>. . . ) . MODEL mname PJF (<level=val> <pname 1=val 1>. . . ) Example. MODEL nj_acmo njf level=3 capop=1 sat=3 acm=0 + is=1 e-14 cgs=1 e-15 cgd=. 3 e-15 + rs=100 rd=100 rg=5 nd=1

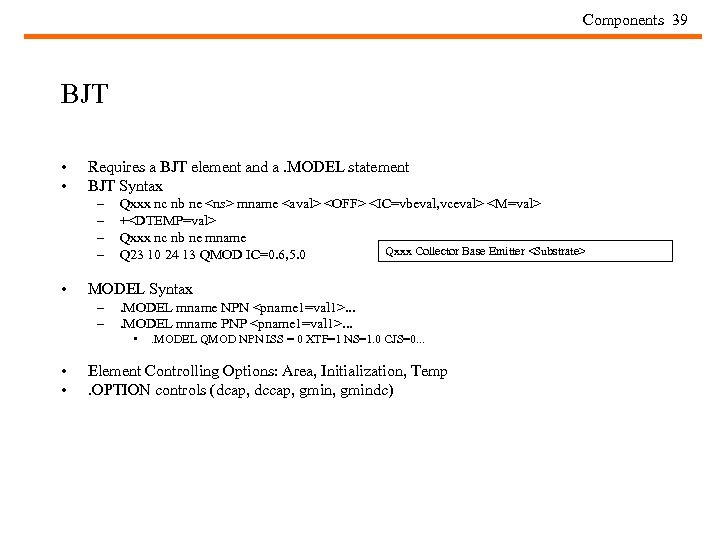

Components 39 BJT • • Requires a BJT element and a. MODEL statement BJT Syntax – – • Qxxx nc nb ne <ns> mname <aval> <OFF> <IC=vbeval, vceval> <M=val> +<DTEMP=val> Qxxx nc nb ne mname Qxxx Collector Base Emitter <Substrate> Q 23 10 24 13 QMOD IC=0. 6, 5. 0 MODEL Syntax – – . MODEL mname NPN <pname 1=val 1>. . MODEL mname PNP <pname 1=val 1>. . . • • • . MODEL QMOD NPN ISS = 0 XTF=1 NS=1. 0 CJS=0. . . Element Controlling Options: Area, Initialization, Temp . OPTION controls (dcap, dccap, gmindc)

Sources 40 Sources Independent Sources: • Independent Sources, Voltage or Current – – – DC AC Transient (Time Varying) • • • Pulse SIN PWL – • • • Data Driven (Imported as time/value pairs) AM, SFFM EXP Mixed (Composite)

Sources 41 Independent Sources : DC, AC • Syntax – – – • DC Sources – – • Vxxx n+ n- <<DC=> dcval> <tranfun> <AC=acmag, acphase> or Iyyy n+ n- <<DC=> dcval> <tranfun> <AC=acmag, acphase> <M=val> V 1 1 0 DC=5 V (def. = 0 v) V 1 1 0 5 V I 1 1 0 DC=5 ma DC sweep range is specified in the. DC analysis statment. AC Sources – – impulse functions used for an AC analysis AC (freq. Domain analysis provides the impulse response of the circuit V 1 1 0 AC=10 v, 90 (def. ACMAG=1 v, ACPHASE=0 degree) AC frequency sweep range is specified in the. AC analysis statment.

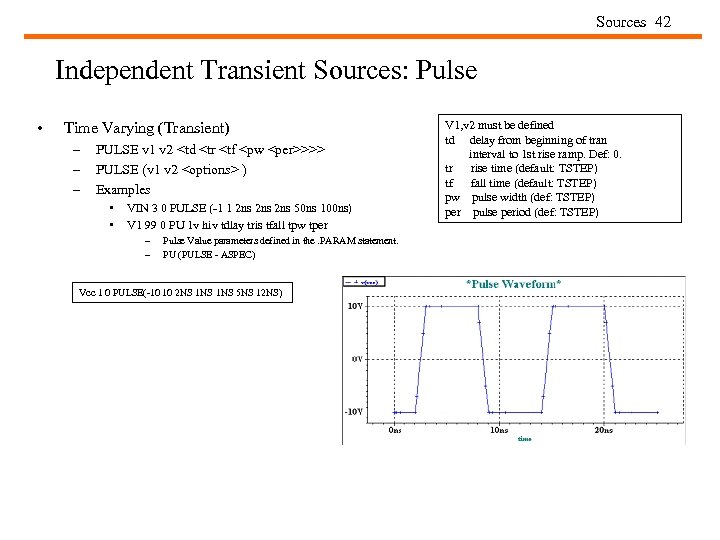

Sources 42 Independent Transient Sources: Pulse • Time Varying (Transient) – – – PULSE v 1 v 2 <td <tr <tf <pw <per>>>> PULSE (v 1 v 2 <options> ) Examples • • VIN 3 0 PULSE (-1 1 2 ns 2 ns 50 ns 100 ns) V 1 99 0 PU 1 v hiv tdlay tris tfall tpw tper – – Pulse Value parameters defined in the. PARAM statement. PU (PULSE - ASPEC) Vcc 1 0 PULSE(-10 10 2 NS 1 NS 5 NS 12 NS) V 1, v 2 must be defined td delay from beginning of tran interval to 1 st rise ramp. Def: 0. tr rise time (default: TSTEP) tf fall time (default: TSTEP) pw pulse width (def: TSTEP) per pulse period (def: TSTEP)

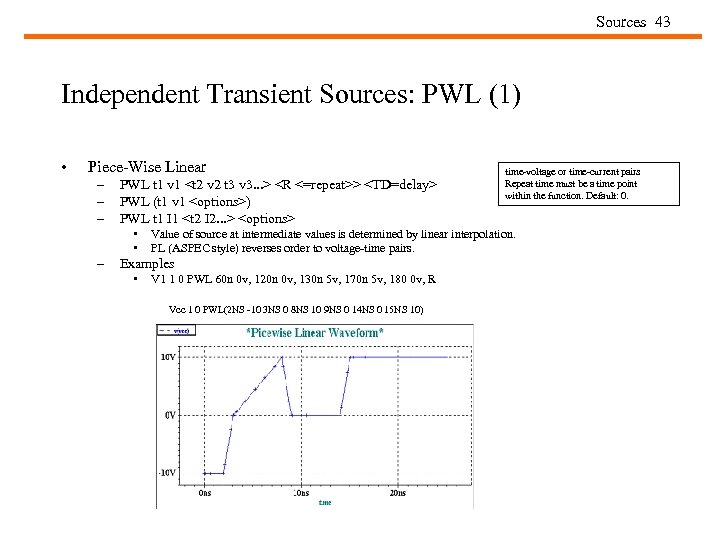

Sources 43 Independent Transient Sources: PWL (1) • Piece-Wise Linear – – – PWL t 1 v 1 <t 2 v 2 t 3 v 3. . . > <R <=repeat>> <TD=delay> PWL (t 1 v 1 <options>) PWL t 1 I 1 <t 2 I 2. . . > <options> • • – Value of source at intermediate values is determined by linear interpolation. PL (ASPEC style) reverses order to voltage-time pairs. Examples • time-voltage or time-current pairs Repeat time must be a time point within the function. Default: 0. V 1 1 0 PWL 60 n 0 v, 120 n 0 v, 130 n 5 v, 170 n 5 v, 180 0 v, R Vcc 1 0 PWL(2 NS -10 3 NS 0 8 NS 10 9 NS 0 14 NS 0 15 NS 10)

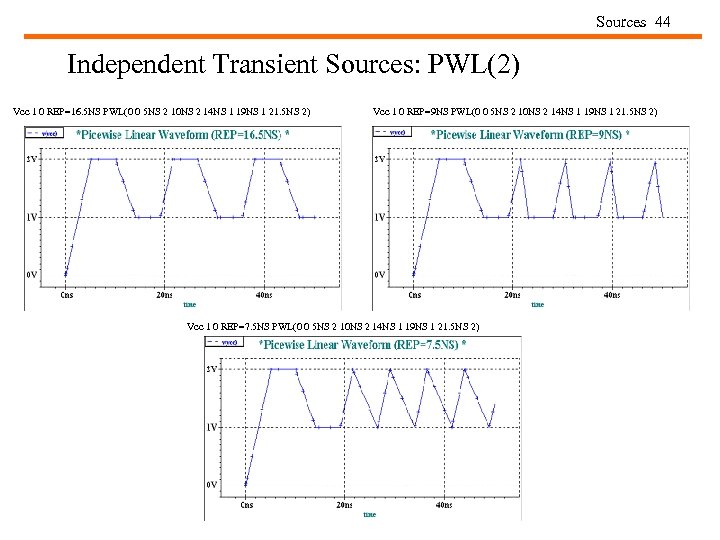

Sources 44 Independent Transient Sources: PWL(2) Vcc 1 0 REP=16. 5 NS PWL(0 0 5 NS 2 10 NS 2 14 NS 1 19 NS 1 21. 5 NS 2) Vcc 1 0 REP=9 NS PWL(0 0 5 NS 2 10 NS 2 14 NS 1 19 NS 1 21. 5 NS 2) Vcc 1 0 REP=7. 5 NS PWL(0 0 5 NS 2 10 NS 2 14 NS 1 19 NS 1 21. 5 NS 2)

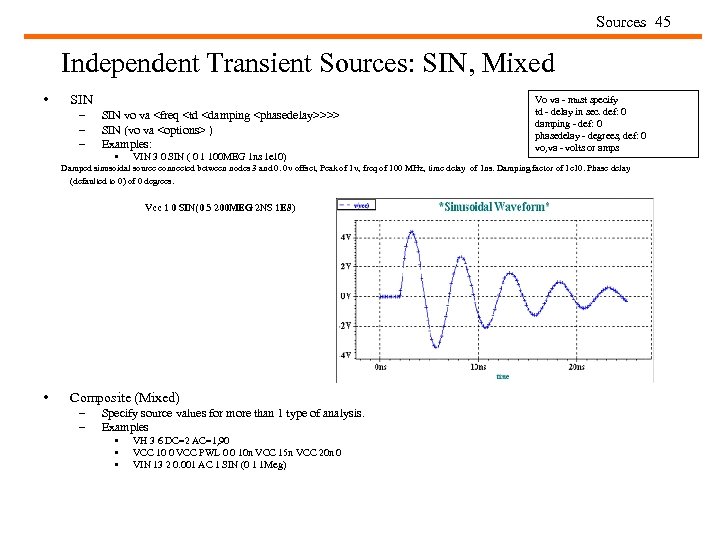

Sources 45 Independent Transient Sources: SIN, Mixed • SIN – – – SIN vo va <freq <td <damping <phasedelay>>>> SIN (vo va <options> ) Examples: • VIN 3 0 SIN ( 0 1 100 MEG 1 ns 1 e 10) Vo va - must specify td - delay in sec. def: 0 damping - def: 0 phasedelay - degrees, def: 0 vo, va - volts or amps Damped sinusoidal source connected between nodes 3 and 0. 0 v offset, Peak of 1 v, freq of 100 MHz, time delay of 1 ns. Damping factor of 1 e 10. Phase delay (defaulted to 0) of 0 degrees. Vcc 1 0 SIN(0 5 200 MEG 2 NS 1 E 8) • Composite (Mixed) – – Specify source values for more than 1 type of analysis. Examples • • • VH 3 6 DC=2 AC=1, 90 VCC 10 0 VCC PWL 0 0 10 n VCC 15 n VCC 20 n 0 VIN 13 2 0. 001 AC 1 SIN (0 1 1 Meg)

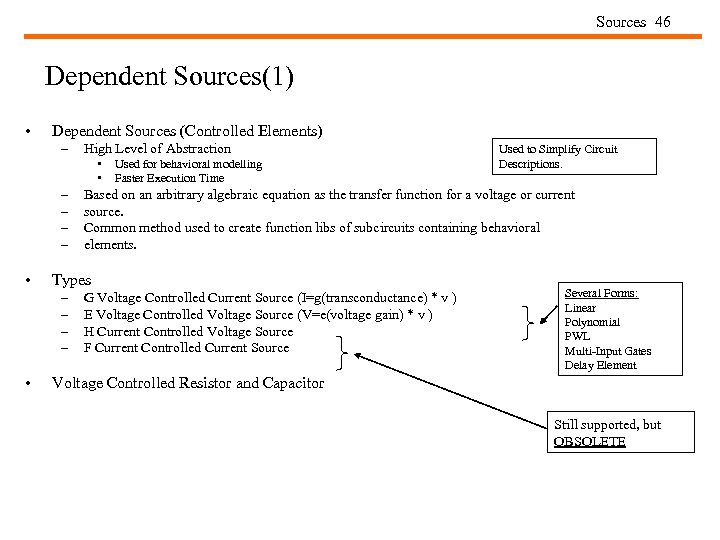

Sources 46 Dependent Sources(1) • Dependent Sources (Controlled Elements) – High Level of Abstraction • • – – • Used to Simplify Circuit Descriptions. Based on an arbitrary algebraic equation as the transfer function for a voltage or current source. Common method used to create function libs of subcircuits containing behavioral elements. Types – – • Used for behavioral modelling Faster Execution Time G Voltage Controlled Current Source (I=g(transconductance) * v ) E Voltage Controlled Voltage Source (V=e(voltage gain) * v ) H Current Controlled Voltage Source F Current Controlled Current Source Several Forms: Linear Polynomial PWL Multi-Input Gates Delay Element Voltage Controlled Resistor and Capacitor Still supported, but OBSOLETE

Sources 47 Dependent Sources(2) • What you can do with Dependent Sources – – – • AND, NAND, OR, NOR gates MOS, Bipolar Transistors OP Amps, Summers, Comparators Switched Capacitor Circuits, etc. Switches ( using VCR) Syntax – Linear • • Exxx n+ n- <VCVS> in+ in- gain <options> Egain 3 0 Vp Vn 1 E 3 n+, n- Controlled nodes in+, in- Controlling nodes

Analysis 48 Analysis • • Analysis Types Output & Formatting Output variables . print/. plot

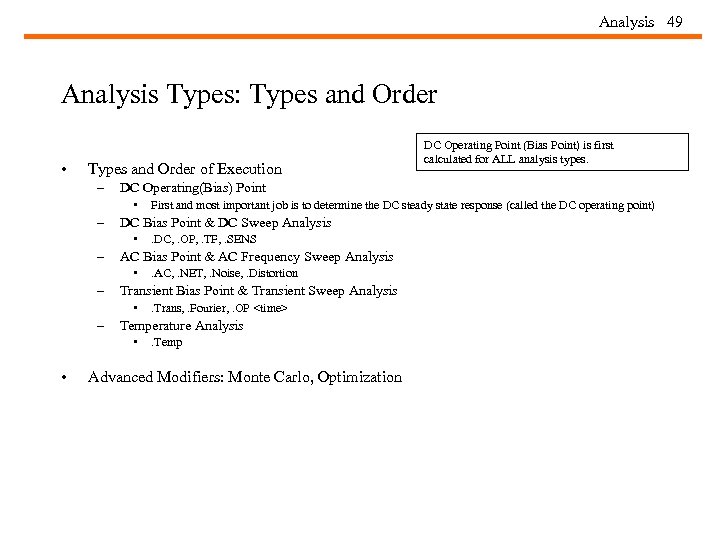

Analysis 49 Analysis Types: Types and Order • Types and Order of Execution – DC Operating(Bias) Point • – . Trans, . Fourier, . OP <time> Temperature Analysis • • . AC, . NET, . Noise, . Distortion Transient Bias Point & Transient Sweep Analysis • – . DC, . OP, . TF, . SENS AC Bias Point & AC Frequency Sweep Analysis • – First and most important job is to determine the DC steady state response (called the DC operating point) DC Bias Point & DC Sweep Analysis • – DC Operating Point (Bias Point) is first calculated for ALL analysis types. . Temp Advanced Modifiers: Monte Carlo, Optimization

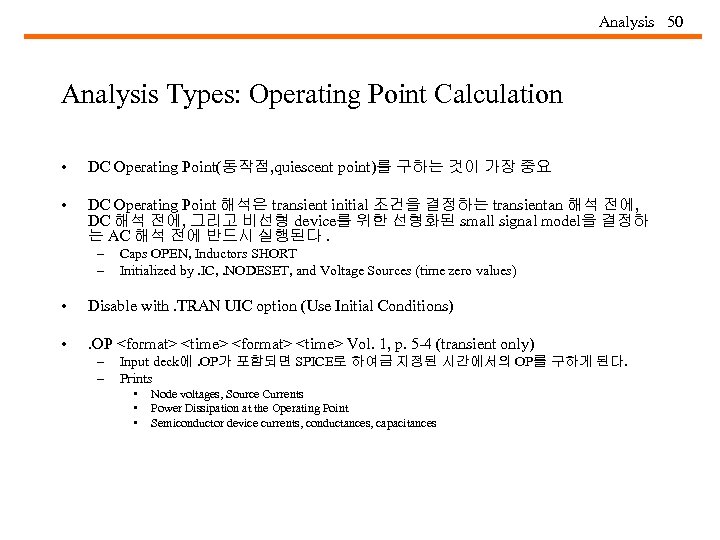

Analysis 50 Analysis Types: Operating Point Calculation • DC Operating Point(동작점, quiescent point)를 구하는 것이 가장 중요 • DC Operating Point 해석은 transient initial 조건을 결정하는 transientan 해석 전에, DC 해석 전에, 그리고 비선형 device를 위한 선형화된 small signal model을 결정하 는 AC 해석 전에 반드시 실행된다. – – Caps OPEN, Inductors SHORT Initialized by. IC, . NODESET, and Voltage Sources (time zero values) • Disable with. TRAN UIC option (Use Initial Conditions) • . OP <format> <time> Vol. 1, p. 5 -4 (transient only) – – Input deck에. OP가 포함되면 SPICE로 하여금 지정된 시간에서의 OP를 구하게 된다. Prints • • • Node voltages, Source Currents Power Dissipation at the Operating Point Semiconductor device currents, conductances, capacitances

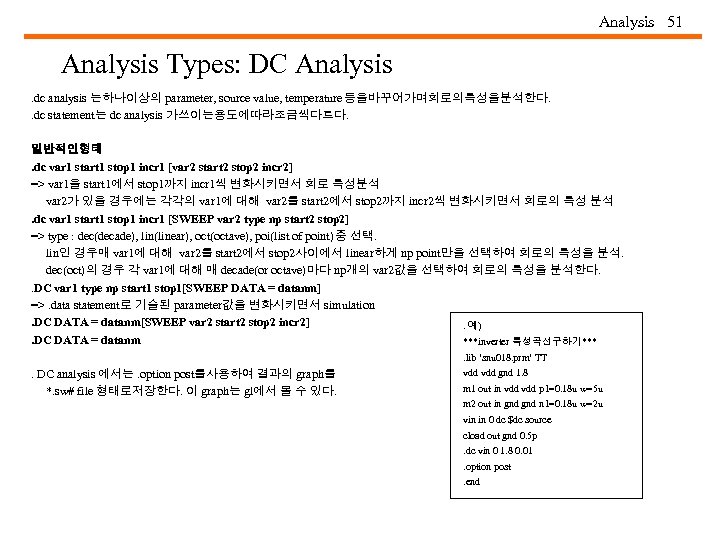

Analysis 51 Analysis Types: DC Analysis. dc analysis 는하나이상의 parameter, source value, temperature등을바꾸어가며회로의특성을분석한다. . dc statement는 dc analysis 가쓰이는용도에따라조금씩다르다. 일반적인형태 . dc var 1 start 1 stop 1 incr 1 [var 2 start 2 stop 2 incr 2] => var 1을 start 1에서 stop 1까지 incr 1씩 변화시키면서 회로 특성분석 var 2가 있을 경우에는 각각의 var 1에 대해 var 2를 start 2에서 stop 2까지 incr 2씩 변화시키면서 회로의 특성 분석 . dc var 1 start 1 stop 1 incr 1 [SWEEP var 2 type np start 2 stop 2] => type : dec(decade), lin(linear), oct(octave), poi(list of point) 중 선택. lin인 경우매 var 1에 대해 var 2를 start 2에서 stop 2사이에서 linear하게 np point만을 선택하여 회로의 특성을 분석. dec(oct)의 경우 각 var 1에 대해 매 decade(or octave)마다 np개의 var 2값을 선택하여 회로의 특성을 분석한다. . DC var 1 type np start 1 stop 1[SWEEP DATA = datanm] =>. data statement로 기술된 parameter값을 변화시키면서 simulation . DC DATA = datanm[SWEEP var 2 start 2 stop 2 incr 2]. 예) . DC DATA = datanm ***inverter 특성곡선구하기*** . lib ‘snu 018. prm’ TT . DC analysis 에서는. option post를사용하여 결과의 graph를 *. sw# file 형태로저장한다. 이 graph는 gl에서 볼 수 있다. vdd gnd 1. 8 m 1 out in vdd p l=0. 18 u w=5 u m 2 out in gnd n l=0. 18 u w=2 u vin in 0 dc $dc source cload out gnd 0. 5 p . dc vin 0 1. 8 0. 01 . option post . end

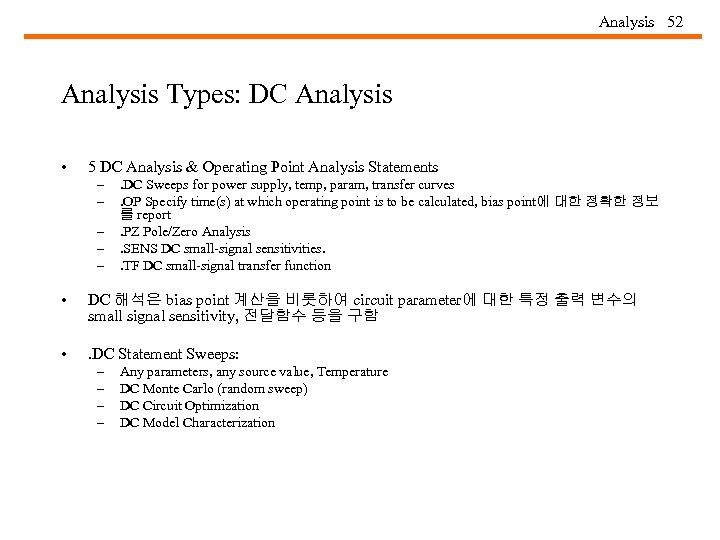

Analysis 52 Analysis Types: DC Analysis • 5 DC Analysis & Operating Point Analysis Statements – – – . DC Sweeps for power supply, temp, param, transfer curves . OP Specify time(s) at which operating point is to be calculated, bias point에 대한 정확한 정보 를 report . PZ Pole/Zero Analysis . SENS DC small-signal sensitivities. . TF DC small-signal transfer function • DC 해석은 bias point 계산을 비롯하여 circuit parameter에 대한 특정 출력 변수의 small signal sensitivity, 전달함수 등을 구함 • . DC Statement Sweeps: – – Any parameters, any source value, Temperature DC Monte Carlo (random sweep) DC Circuit Optimization DC Model Characterization

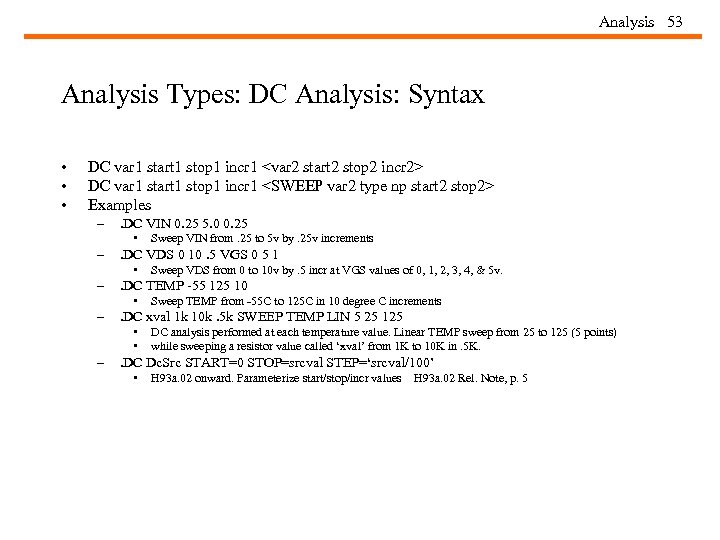

Analysis 53 Analysis Types: DC Analysis: Syntax • • • DC var 1 start 1 stop 1 incr 1 <var 2 start 2 stop 2 incr 2> DC var 1 start 1 stop 1 incr 1 <SWEEP var 2 type np start 2 stop 2> Examples – . DC VIN 0. 25 5. 0 0. 25 • – . DC VDS 0 10. 5 VGS 0 5 1 • – Sweep TEMP from -55 C to 125 C in 10 degree C increments . DC xval 1 k 10 k. 5 k SWEEP TEMP LIN 5 25 125 • • – Sweep VDS from 0 to 10 v by. 5 incr at VGS values of 0, 1, 2, 3, 4, & 5 v. . DC TEMP -55 125 10 • – Sweep VIN from. 25 to 5 v by. 25 v increments DC analysis performed at each temperature value. Linear TEMP sweep from 25 to 125 (5 points) while sweeping a resistor value called ‘xval’ from 1 K to 10 K in. 5 K. . DC Dc. Src START=0 STOP=srcval STEP=‘srcval/100’ • H 93 a. 02 onward. Parameterize start/stop/incr values H 93 a. 02 Rel. Note, p. 5

Analysis 54 Analysis Types: DC Analysis: . TF, . SENS • . TF Outvar INSRC – – Small-signal DC gain, input resistance, output resistance 계산 Examples • . DC V(4) V(1) – – – • DC Gain : V(4) / V(1) Input resistance : node 1과 node 0 사이의 저항 Ouput resistance : node 4과 node 0 사이의 저항 . SENS OV 1 <OV 2 … > – – . 모든 circuit parameter에 대해 특정 출력 변수의 DC small signal sensitivity를 결정 Example • . SENS V(9) V(4, 3) V(17) I(VCC)

Analysis 55 Analysis Types: AC Analysis • 주어진 주파수 범위 내에서 주파수 응답을 구함 • 만약 회로내에 비선형 element가 있으면 회로 해석 전에 element의 small signal 선형 model을 결정하여 이를 회 로 해석에 사용 • DC OP 계산을 수행한 후, 모든 nonlinear device에 대하여 OP를 중심으로 small signal 선형 model을 결정한다. • Resistor, semiconductor device에 의한 white noise 계산 • Flicker noise 계산 (device model의 KF, AF 사용) • AC Analysis Statements Vol. 1, p. 8 -1 – . AC Compute output variables as a function of frequency • requires an A. C. source (v 2 n 1 n 2 5 ac 1. . . ) • set to 1 volt for normalized db plot – – . DISTO Distortion Analysis – . NET Network analysis – • . NOISE Noise Analysis . SAMPLE Sampling Noise . AC Sweep Statements: – Frequency, Element Value, Temperature, Model parameter Value – Random Sweep (Monte Carlo), Optimization and AC Design Analysis

Analysis 56 Analysis Types: AC Analysis: Syntax • . AC type np fstart fstop <SWEEP var start stop incr> • Examples – . AC DEC 10 1 K 100 MEG • Freq sweep 10 points per decade for 1 KHz to 100 MHz • 주파수 범위가 1 k~100 M이므로 log(100 M/1 K) = 5 Decades 이고, decade당 10 point이므로 모두 10 * 5 + 1 = 51 point frequence에서 AC 해석함 • – OCT : Octave = Decade / Log 2 , OCT, DEC는 주파수 범위가 넓을 때 사용 . AC LIN 100 1 100 hz • • – Linear Sweep 100 points from 1 hz to 100 Hz, 매 1 Hz마다 AC 해석 LIN은 주파수 범위가 좁을 때 사용 NOTE: ‘cload’ is a variable, NOT a capacitor . AC DEC 10 1 10 K SWEEP cload LIN 20 1 pf 10 pf • AC analysis for each value of cload, with a linear sweep of cload between 1 pf and 10 pf (20 points). • Sweeping frequency 10 points per decade from 1 Hz to 10 KHz. (41 point freq.

Analysis 57 Analysis Types: AC Analysis: . NOISE • Resistor. semiconductor device는 주파수 종속의 noise 발생, 이를 해석함 • . NOISE 해석은. AC 해석과 더불어 사용 • AC 해석시 각 주파수에서 호로 각 요소의 noise를 계산하고 특정 output node에 대해 영향 끼치 는 각 요소의 noise의 RMS 값을 합하여 계산 • SPICE는 src에서 등가 input noise를 계산함과 동시에 특별히 지정된 output에서 등가 output noise를 계산 • . NOISE ovv srcnam inter – . NOISE V(5) VIN 10 • • Inter가 0이거나 정의되지 않으면 no summary printout • – 10 point frequency에서 input noise(VIN), output noise(v(5)) 계산 Inter가 1이면 첫번째 주파수에서의 해석 결과를 printout . PRINT NOISE ONOISE INOISE

Analysis 58 Analysis Types: Transient Analysis • Transient Analysis Statements – • Compute circuit solution as a function of time over a time range . TRAN Statement Can be Used for: – Transient Operating Point (eg. . OP 20 n) – Transient Temperature Sweep – Transient Monte Carlo Analysis (random sweep) – Transient Parameter Sweep – Transient Optimization

Analysis 59 Analysis Types: Transient Analysis: Syntax • . TRAN tincr 1 tstop 1 <tincr 2 tstop 2. . . ><START=val> <UIC> <SWEEP. . > • DC bias point를 초기값으로 사용함. • Examples – . TRAN 1 ns 100 ns • – TINCR 1 known as the “PRINT INTERVAL” (NOT the timestep interval). TMAX = MIN(TINCR, (TSTOP-TINCR)/50) Transient analysis is made and printed every 1 ns for 100 ns. . TRAN. 1 ns 25 ns 1 ns 40 ns START=10 ns • Calculation is made every. 1 ns for the first 25 ns, and then every 1 ns until 40 ns. The printing and plotting begin at 10 ns. – . TRAN 10 ns 1 us SWEEP cload POI 3 1 pf 5 pf 10 pf • Calculation is made every 10 ns for 1 us at three cload. (POI - Points of Interests)

Analysis 60 Analysis Types: Transient Analysis : Control options a) bypass : latent MOSFETs ( 예를들어 , off transistor )를 analysis iteration 에서 제외함으로써 simulation속도를 향상시킨다. bypass를실행시키기위해서는. option bypass=1을 추가하면 된다. Default=0. 8 bit RCA에서 약 30% 정도계산 시간이 단축됨 b) cshunt : 각 node에 ground와의 사이에 작은 capacitor를 단다. 이러한 option을사용함으로써 high freq oscillation으로 인하여 발생하는 “internal time step too small” 이라는 error를 제거할 수 있다. c) dvdt : time step조절. 0, 1, 2, 3, 4 다섯가지 값을 가질수 있으며 default는 4. 0 : 원래알고리즘 1 : fast 2 : accurate 3, 4 : balance speed and accuracy d) gshunt : cshunt와 같은 역할을 하나 conductance를단다는 점이 틀리다. e) lvltim : timestep 알고리즘선택. 1, 2, 3 세값을가지는데 2의 경우 정확성을 보장하며 1의경우“internal time step too small” error 를줄일수있다. f) method : 적분방식을결정. method=gear 혹은 meathod=trap 두가지경우가있다. default는 trap이다. Gear의 경우 정확한 계산을 보장하며 자동적으로 lvltim=2 로 setting한다. g) fast : 계산을 수행하는데 있어 latent device의 voltage값을 update하지 않고 계산함으로써 계산의속도를높인다. 한번의계산이 수행 되었을때 변하는 device의voltage의 양이 HSPICE 내부의 정해진 값(bytol control option에 의해 조정가능.

Analysis 61 Analysis Types: Capacitance Options • . OPTION DCCAP – – • Default = 0 See the demonstration file mosivcv. sp. $installdir/demo/hspice/mos – • Forces the voltage variable capacitors to be evaluated during a DC sweep. Generate C-V plots (mos devices) Print out capacitance values of a circuit during a DC analysis. C-V plots often generated using a DC sweep of the capacitor. Vol. 3, p. 11 -6 to 11 -10 for a template. . OPTION CAPTAB – Print a table of single plate nodal capacitance for diodes, BJTs, MOS, JFETs, and passive capacitors at each operating point.

Output & Formatting 62 Output & Formatting: Output • Output Commands – . PRINT, . PLOT, . GRAPH, . PROBE, and. MEASURE – Each statement specifies: • output variable • simulation result to be displayed • . GRAPH sends hardcopy to printer automatically • . GRAPH is not implemented on P. C. • . PROBE can limit. TR# file size ( requires. options probe) • . MEASURE has several special forms

Output & Formatting 63 Output & Formatting: . PLOT, . PROBE • . PLOT syntax – . PLOT antype ov 1 <ov 2. . . > <plo 1, phi 1. . . plo 32, phi 32> • • • Add <plo 1, phi 1> to set lower and upper plot limits. . PROBE syntax (Only works when. OPTIONS PROBE is used) – • Same syntax as. PRINT . PROBE antype ov 1 <ov 2. . . ov 32> Using with Subcircuits (Xnnn) – Specify nodes ‘local’ to a subcircuit. (Nodes on ‘calling’ line replace local nodes). – Concatenate circuit pathname with the node name through the ‘. ’ • – X 1. XBIAS. M 5 or. . . Based on unique number automatically assigned to each subcircuit (. OPTION LIST) • 56: M 5 (in this case Hspice assigned 56 to X 1. XBIAS)

Output & Formatting 64 Output & Formatting: . GRAPH, Avan. Waves • . GRAPH – – Placed in netlist to automatically generate a printout when HSPICE is run – • Non interactive Not supported on PC Avan. Waves – Interactive – For display and analyzing Hspice simulation results – Opening a design file, e. g. . sp file, will automatically open all the output files under the same design filename – On-line help

Output & Formatting 65 Output & Formatting: . PRINT syntax • . PRINT antype ov 1 <ov 2. . . ov 32> – . PRINT tran v(4) i(vin) par(‘v(out)/v(in)’) • – . PRINT AC VM(4, 2) VR(7) VP(8, 3) Ii(R 1) • – Print AC magnitude of the voltage difference between nodes 4 and 2. Real part of the AC voltage between nodes 7 and ground. VP is phase difference between nodes 8 and 3. Ii is the imaginary part of the current through element R 1. . PRINT LX 8(m 1) • – Print results of transient analysis for nodal voltage named 4, current through voltage source named vin, and the ratio of the nodal voltage at node ‘out’ and ‘in’. Print the drain-source conductance of element m 1. SWEEPS • Appear as multiple, concatenated runs.

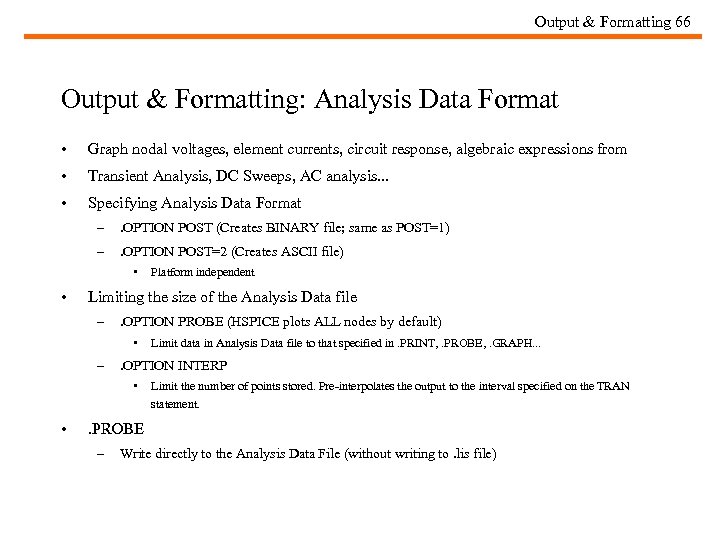

Output & Formatting 66 Output & Formatting: Analysis Data Format • Graph nodal voltages, element currents, circuit response, algebraic expressions from • Transient Analysis, DC Sweeps, AC analysis. . . • Specifying Analysis Data Format – . OPTION POST (Creates BINARY file; same as POST=1) – . OPTION POST=2 (Creates ASCII file) • • Limiting the size of the Analysis Data file – . OPTION PROBE (HSPICE plots ALL nodes by default) • – Limit data in Analysis Data file to that specified in. PRINT, . PROBE, . GRAPH. . . . OPTION INTERP • • Platform independent Limit the number of points stored. Pre-interpolates the output to the interval specified on the TRAN statement. . PROBE – Write directly to the Analysis Data File (without writing to. lis file)

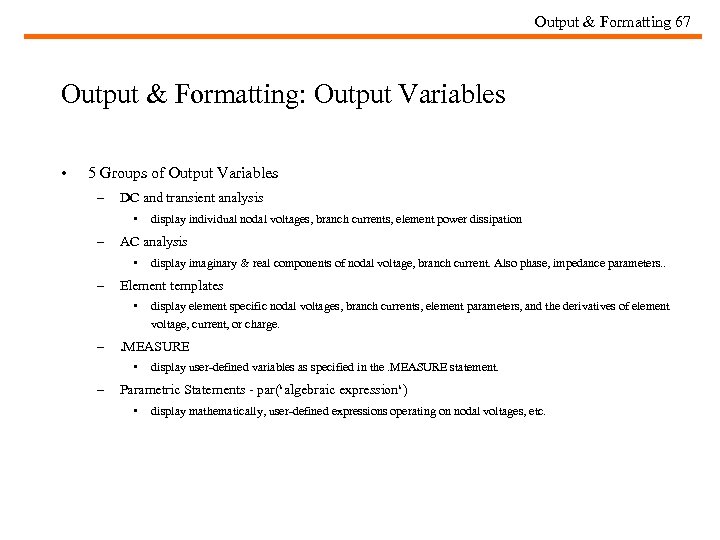

Output & Formatting 67 Output & Formatting: Output Variables • 5 Groups of Output Variables – DC and transient analysis • – AC analysis • – display element specific nodal voltages, branch currents, element parameters, and the derivatives of element voltage, current, or charge. . MEASURE • – display imaginary & real components of nodal voltage, branch current. Also phase, impedance parameters. . Element templates • – display individual nodal voltages, branch currents, element power dissipation display user-defined variables as specified in the. MEASURE statement. Parametric Statements - par(‘algebraic expression‘) • display mathematically, user-defined expressions operating on nodal voltages, etc.

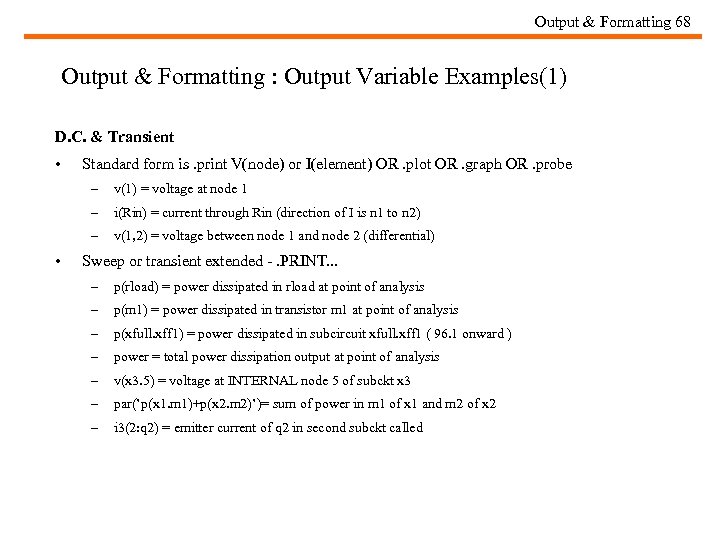

Output & Formatting 68 Output & Formatting : Output Variable Examples(1) D. C. & Transient • Standard form is. print V(node) or I(element) OR. plot OR. graph OR. probe – – i(Rin) = current through Rin (direction of I is n 1 to n 2) – • v(1) = voltage at node 1 v(1, 2) = voltage between node 1 and node 2 (differential) Sweep or transient extended -. PRINT. . . – p(rload) = power dissipated in rload at point of analysis – p(m 1) = power dissipated in transistor m 1 at point of analysis – p(xfull. xff 1) = power dissipated in subcircuit xfull. xff 1 ( 96. 1 onward ) – power = total power dissipation output at point of analysis – v(x 3. 5) = voltage at INTERNAL node 5 of subckt x 3 – par(’p(x 1. m 1)+p(x 2. m 2)’)= sum of power in m 1 of x 1 and m 2 of x 2 – i 3(2: q 2) = emitter current of q 2 in second subckt called

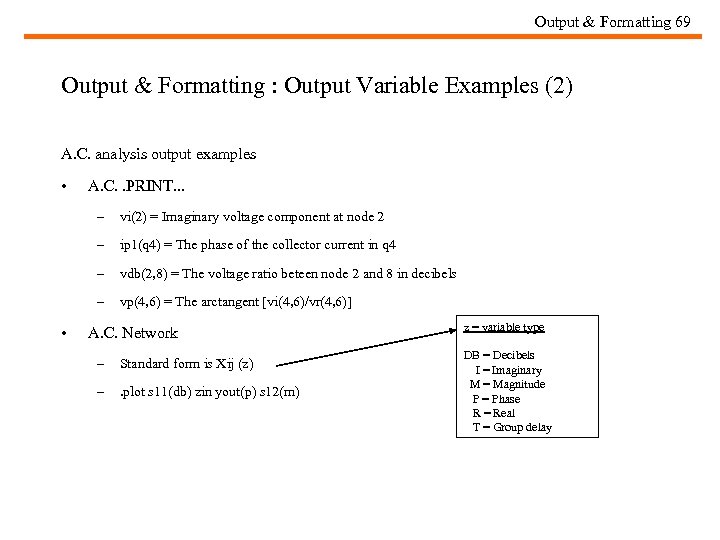

Output & Formatting 69 Output & Formatting : Output Variable Examples (2) A. C. analysis output examples • A. C. . PRINT. . . – – ip 1(q 4) = The phase of the collector current in q 4 – vdb(2, 8) = The voltage ratio beteen node 2 and 8 in decibels – • vi(2) = Imaginary voltage component at node 2 vp(4, 6) = The arctangent [vi(4, 6)/vr(4, 6)] A. C. Network – Standard form is Xij (z) – . plot s 11(db) zin yout(p) s 12(m) z = variable type DB = Decibels I = Imaginary M = Magnitude P = Phase R = Real T = Group delay

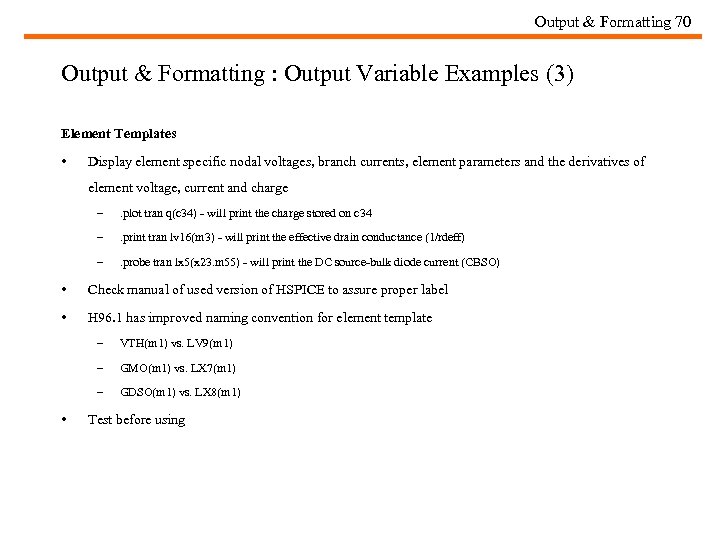

Output & Formatting 70 Output & Formatting : Output Variable Examples (3) Element Templates • Display element specific nodal voltages, branch currents, element parameters and the derivatives of element voltage, current and charge – . plot tran q(c 34) - will print the charge stored on c 34 – . print tran lv 16(m 3) - will print the effective drain conductance (1/rdeff) – . probe tran lx 5(x 23. m 55) - will print the DC source-bulk diode current (CBSO) • Check manual of used version of HSPICE to assure proper label • H 96. 1 has improved naming convention for element template – – GMO(m 1) vs. LX 7(m 1) – • VTH(m 1) vs. LV 9(m 1) GDSO(m 1) vs. LX 8(m 1) Test before using

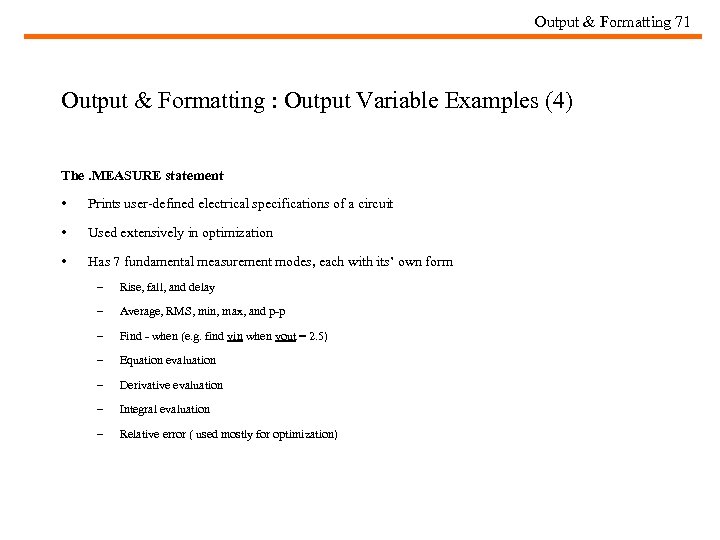

Output & Formatting 71 Output & Formatting : Output Variable Examples (4) The. MEASURE statement • Prints user-defined electrical specifications of a circuit • Used extensively in optimization • Has 7 fundamental measurement modes, each with its’ own form – Rise, fall, and delay – Average, RMS, min, max, and p-p – Find - when (e. g. find vin when vout = 2. 5) – Equation evaluation – Derivative evaluation – Integral evaluation – Relative error ( used mostly for optimization)

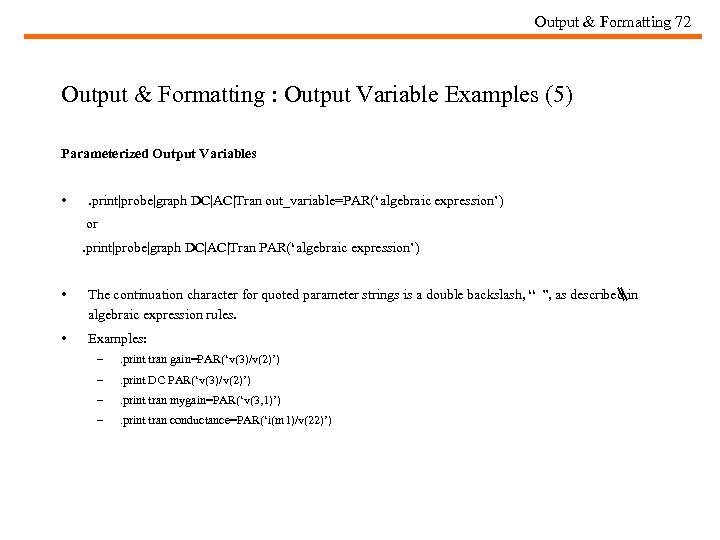

Output & Formatting 72 Output & Formatting : Output Variable Examples (5) Parameterized Output Variables • . print|probe|graph DC|AC|Tran out_variable=PAR(‘algebraic expression’) or . print|probe|graph DC|AC|Tran PAR(‘algebraic expression’) • The continuation character for quoted parameter strings is a double backslash, “ ”, as described in algebraic expression rules. • Examples: – . print tran gain=PAR(‘v(3)/v(2)’) – . print DC PAR(‘v(3)/v(2)’) – . print tran mygain=PAR(‘v(3, 1)’) – . print tran conductance=PAR(‘i(m 1)/v(22)’)

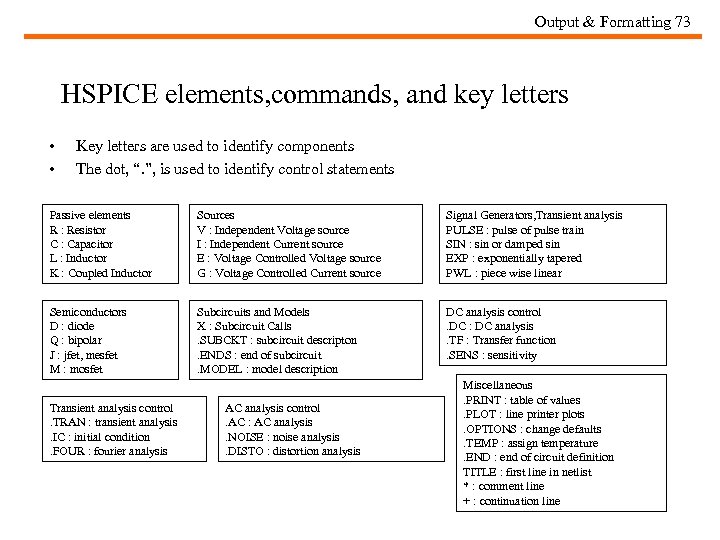

Output & Formatting 73 HSPICE elements, commands, and key letters • • Key letters are used to identify components The dot, “. ”, is used to identify control statements Passive elements R : Resistor C : Capacitor L : Inductor K : Coupled Inductor Sources V : Independent Voltage source I : Independent Current source E : Voltage Controlled Voltage source G : Voltage Controlled Current source Signal Generators, Transient analysis PULSE : pulse of pulse train SIN : sin or damped sin EXP : exponentially tapered PWL : piece wise linear Semiconductors D : diode Q : bipolar J : jfet, mesfet M : mosfet Subcircuits and Models X : Subcircuit Calls . SUBCKT : subcircuit descripton . ENDS : end of subcircuit . MODEL : model description DC analysis control . DC : DC analysis . TF : Transfer function . SENS : sensitivity Transient analysis control . TRAN : transient analysis . IC : initial condition . FOUR : fourier analysis AC analysis control . AC : AC analysis . NOISE : noise analysis . DISTO : distortion analysis Miscellaneous . PRINT : table of values . PLOT : line printer plots . OPTIONS : change defaults . TEMP : assign temperature . END : end of circuit definition TITLE : first line in netlist * : comment line + : continuation line

실습 74 SPICE 시뮬레이션 실습 (1) 실습문제 1. 수동소자인 저항으로 이루어진 회로의 동작점(노드전압) 구하기 실습문제 2. 수동소자인 저항과 캐패시터으로 이루어진 회로의 동작점과 주파수 특성 구하기 실습문제 3. 수동소자인 저항과 캐패시터으로 이루어진 회로에 Pulse전압을 인가하여 transient 해석하기 실습문제 4. 4차 바터워스 저역통과 필터의 주파수 특성와 시간영역 특성 해석하기 실습문제 5. 능동소자 Diode의 device model의 rs가 회로의 DC 특성에 미치는 영향을 DC analysis를 통하여 분석하기 실습문제 6. Peak Detector 특성 분석하기 실습문제 7. MOSFET의 Inverter 특성 분석하기

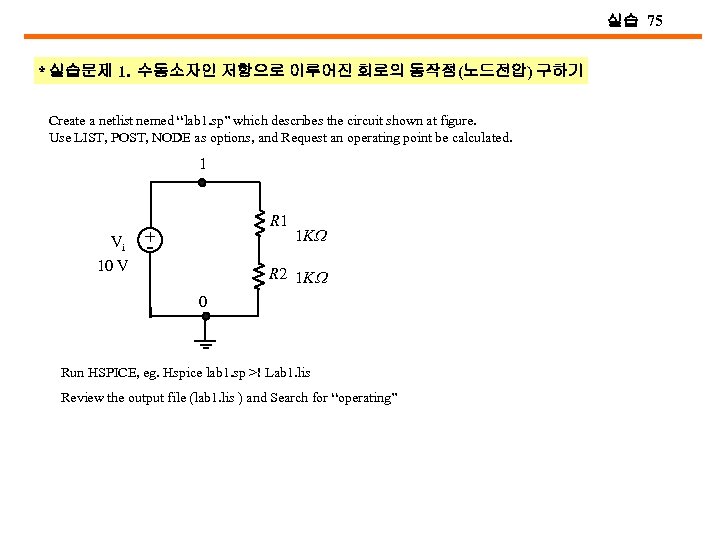

실습 75 * 실습문제 1. 수동소자인 저항으로 이루어진 회로의 동작점(노드전압) 구하기 Create a netlist nemed “lab 1. sp” which describes the circuit shown at figure. Use LIST, POST, NODE as options, and Request an operating point be calculated. 1 Vi 10 V R 1 + - 1 KW R 2 1 KW 0 Run HSPICE, eg. Hspice lab 1. sp >! Lab 1. lis Review the output file (lab 1. lis ) and Search for “operating”

실습 76 * 실습문제 1 해답. lab 1. sp passive R circuit operating point calculation V 1 1 0 dc 10 R 1 1 2 1 k R 2 2 0 1 k. option list post node. print dc v(1) v(2). end lab 1. lis ~ ~ ***** operating point status is all simulation time is 0. node =voltage +0: 1 = 10. 0000 0: 2 = 5. 0000

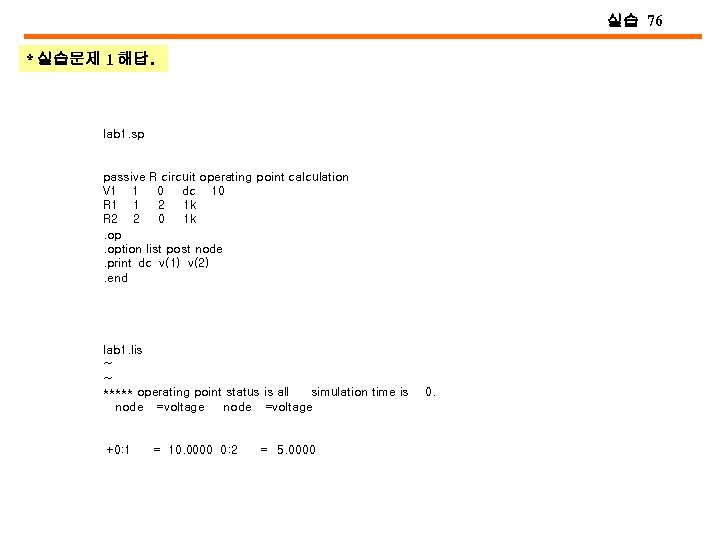

실습 77 * 실습문제 2. 수동소자인 저항과 캐패시터으로 이루어진 회로의 동작점과 주파수 특성 구하기 Create a netlist named “lab 2. sp” which describes the circuit shown at figure. Use LIST, POST, NODE as options, and request an operating point be calculated. And request an ac sweep 10 points per decade from 1 k. Hz to 1 MHz, and a print the AC voltage at nodes 1 and 2, and the AC current through r 2 and c 1. 1 + Vi DC 10 V AC 1 V R 1 2 - 1 KW R 2 1 KW 0 C 1 0. 001 u. F Run HSPICE, eg. Hspice lab 2. sp >! Lab 2. lis Review the output file (lab 2. lis ) and search for “ac analysis”. After then, run awaves and call up lab 1 b. sp. Display the voltage at node 2. Change the X axis to log.

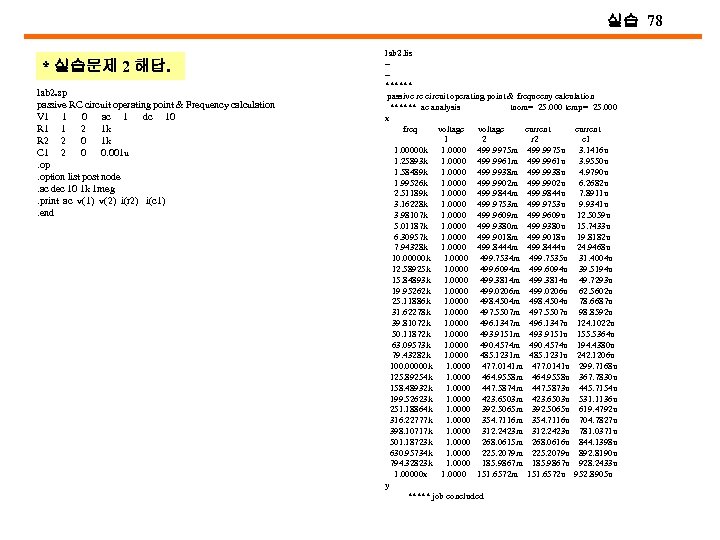

실습 78 * 실습문제 2 해답. lab 2. sp passive RC circuit operating point & Frequency calculation V 1 1 0 ac 1 dc 10 R 1 1 2 1 k R 2 2 0 1 k C 1 2 0 0. 001 u . option list post node . ac dec 10 1 k 1 meg . print ac v(1) v(2) i(r 2) i(c 1) . end lab 2. lis ~ ~ ****** passive rc circuit operating point & frequecny calculation ****** ac analysis tnom= 25. 000 temp= 25. 000 x freq voltage current 1 2 r 2 c 1 1. 00000 k 1. 0000 499. 9975 m 499. 9975 u 3. 1416 u 1. 25893 k 1. 0000 499. 9961 m 499. 9961 u 3. 9550 u 1. 58489 k 1. 0000 499. 9938 m 499. 9938 u 4. 9790 u 1. 99526 k 1. 0000 499. 9902 m 499. 9902 u 6. 2682 u 2. 51189 k 1. 0000 499. 9844 m 499. 9844 u 7. 8911 u 3. 16228 k 1. 0000 499. 9753 m 499. 9753 u 9. 9341 u 3. 98107 k 1. 0000 499. 9609 m 499. 9609 u 12. 5059 u 5. 01187 k 1. 0000 499. 9380 m 499. 9380 u 15. 7433 u 6. 30957 k 1. 0000 499. 9018 m 499. 9018 u 19. 8182 u 7. 94328 k 1. 0000 499. 8444 m 499. 8444 u 24. 9468 u 10. 00000 k 1. 0000 499. 7534 m 499. 7535 u 31. 4004 u 12. 58925 k 1. 0000 499. 6094 m 499. 6094 u 39. 5194 u 15. 84893 k 1. 0000 499. 3814 m 499. 3814 u 49. 7293 u 19. 95262 k 1. 0000 499. 0206 m 499. 0206 u 62. 5602 u 25. 11886 k 1. 0000 498. 4504 m 498. 4504 u 78. 6687 u 31. 62278 k 1. 0000 497. 5507 m 497. 5507 u 98. 8592 u 39. 81072 k 1. 0000 496. 1347 m 496. 1347 u 124. 1022 u 50. 11872 k 1. 0000 493. 9151 m 493. 9151 u 155. 5364 u 63. 09573 k 1. 0000 490. 4574 m 490. 4574 u 194. 4380 u 79. 43282 k 1. 0000 485. 1231 m 485. 1231 u 242. 1206 u 100. 00000 k 1. 0000 477. 0141 m 477. 0141 u 299. 7168 u 125. 89254 k 1. 0000 464. 9558 m 464. 9558 u 367. 7830 u 158. 48932 k 1. 0000 447. 5874 m 447. 5873 u 445. 7154 u 199. 52623 k 1. 0000 423. 6503 m 423. 6503 u 531. 1136 u 251. 18864 k 1. 0000 392. 5065 m 392. 5065 u 619. 4792 u 316. 22777 k 1. 0000 354. 7116 m 354. 7116 u 704. 7827 u 398. 10717 k 1. 0000 312. 2423 m 312. 2423 u 781. 0371 u 501. 18723 k 1. 0000 268. 0615 m 268. 0616 u 844. 1398 u 630. 95734 k 1. 0000 225. 2079 m 225. 2079 u 892. 8190 u 794. 32823 k 1. 0000 185. 9867 m 185. 9867 u 928. 2433 u 1. 00000 x 1. 0000 151. 6572 m 151. 6572 u 952. 8905 u y ***** job concluded

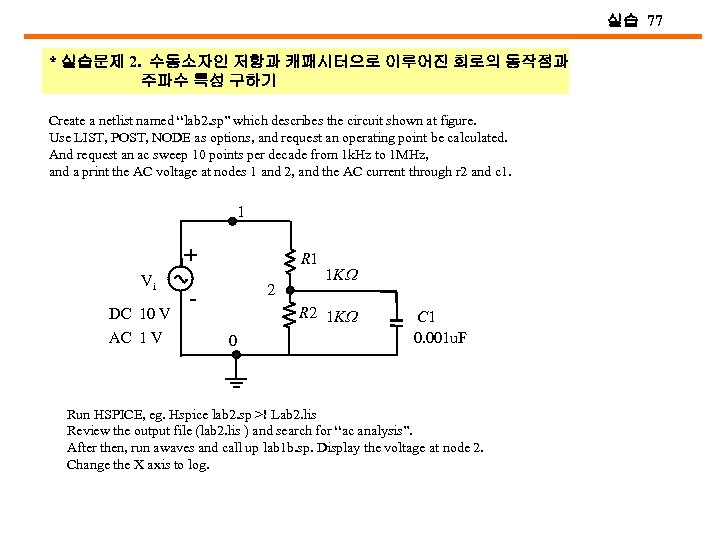

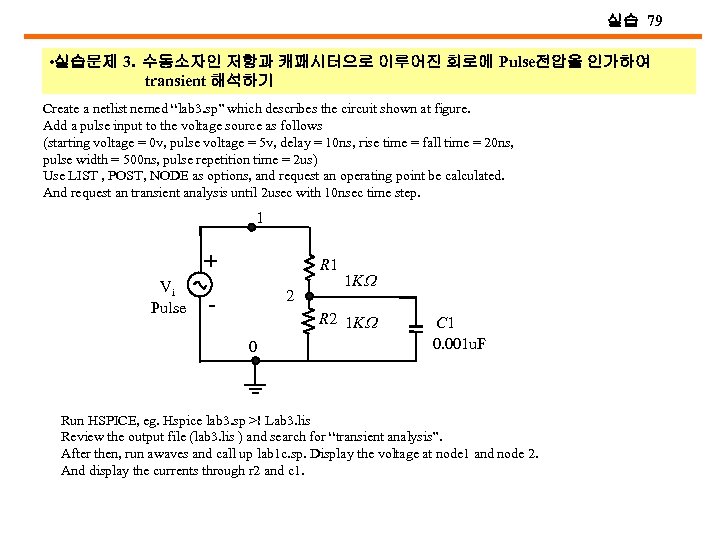

실습 79 • 실습문제 3. 수동소자인 저항과 캐패시터으로 이루어진 회로에 Pulse전압을 인가하여 transient 해석하기 Create a netlist nemed “lab 3. sp” which describes the circuit shown at figure. Add a pulse input to the voltage source as follows (starting voltage = 0 v, pulse voltage = 5 v, delay = 10 ns, rise time = fall time = 20 ns, pulse width = 500 ns, pulse repetition time = 2 us) Use LIST , POST, NODE as options, and request an operating point be calculated. And request an transient analysis until 2 usec with 10 nsec time step. 1 + Vi Pulse R 1 2 - 1 KW R 2 1 KW 0 C 1 0. 001 u. F Run HSPICE, eg. Hspice lab 3. sp >! Lab 3. lis Review the output file (lab 3. lis ) and search for “transient analysis”. After then, run awaves and call up lab 1 c. sp. Display the voltage at node 1 and node 2. And display the currents through r 2 and c 1.

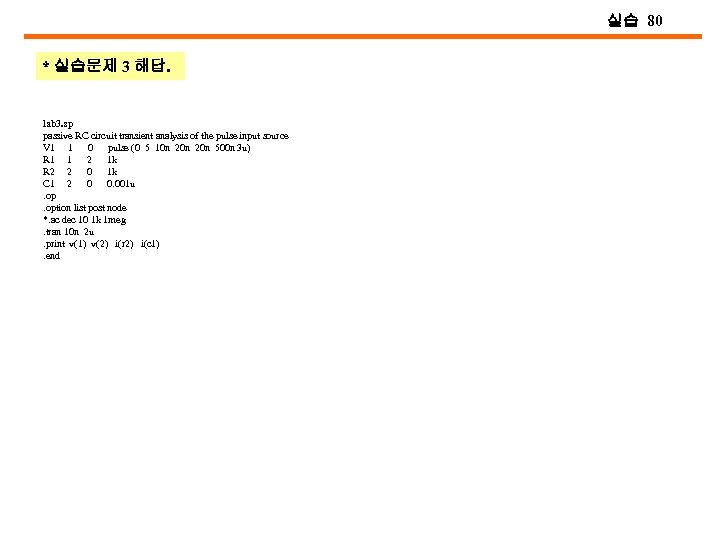

실습 80 * 실습문제 3 해답. lab 3. sp passive RC circuit transient analysis of the pulse input source V 1 1 0 pulse (0 5 10 n 20 n 500 n 3 u) R 1 1 2 1 k R 2 2 0 1 k C 1 2 0 0. 001 u . option list post node *. ac dec 10 1 k 1 meg . tran 10 n 2 u . print v(1) v(2) i(r 2) i(c 1) . end

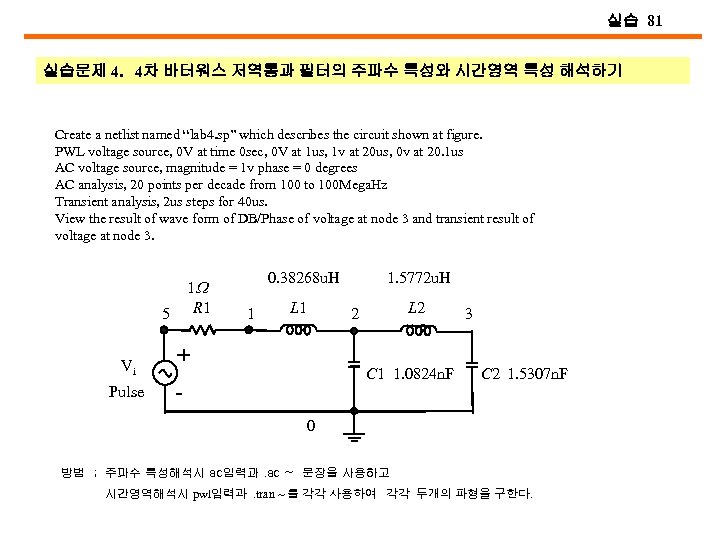

실습 81 실습문제 4. 4차 바터워스 저역통과 필터의 주파수 특성와 시간영역 특성 해석하기 Create a netlist named “lab 4. sp” which describes the circuit shown at figure. PWL voltage source, 0 V at time 0 sec, 0 V at 1 us, 1 v at 20 us, 0 v at 20. 1 us AC voltage source, magnitude = 1 v phase = 0 degrees AC analysis, 20 points per decade from 100 to 100 Mega. Hz Transient analysis, 2 us steps for 40 us. View the result of wave form of DB/Phase of voltage at node 3 and transient result of voltage at node 3. 5 Vi Pulse 1 W R 1 0. 38268 u. H 1 L 1 1. 5772 u. H L 2 2 + - C 1 1. 0824 n. F 3 C 2 1. 5307 n. F 0 방법 ; 주파수 특성해석시 ac입력과. ac ~ 문장을 사용하고 시간영역해석시 pwl입력과 . tran ~ 를 각각 사용하여 각각 두개의 파형을 구한다.

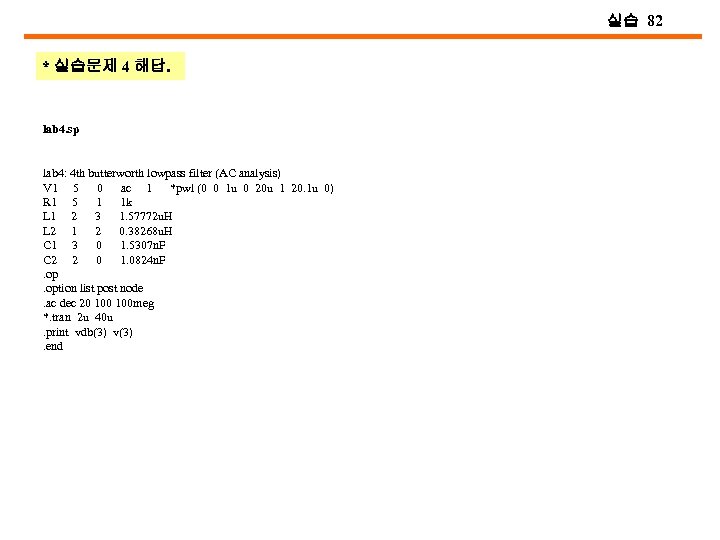

실습 82 * 실습문제 4 해답. lab 4. sp lab 4: 4 th butterworth lowpass filter (AC analysis) V 1 5 0 ac 1 *pwl (0 0 1 u 0 20 u 1 20. 1 u 0) R 1 5 1 1 k L 1 2 3 1. 57772 u. H L 2 1 2 0. 38268 u. H C 1 3 0 1. 5307 n. F C 2 2 0 1. 0824 n. F . option list post node . ac dec 20 100 meg *. tran 2 u 40 u . print vdb(3) v(3) . end

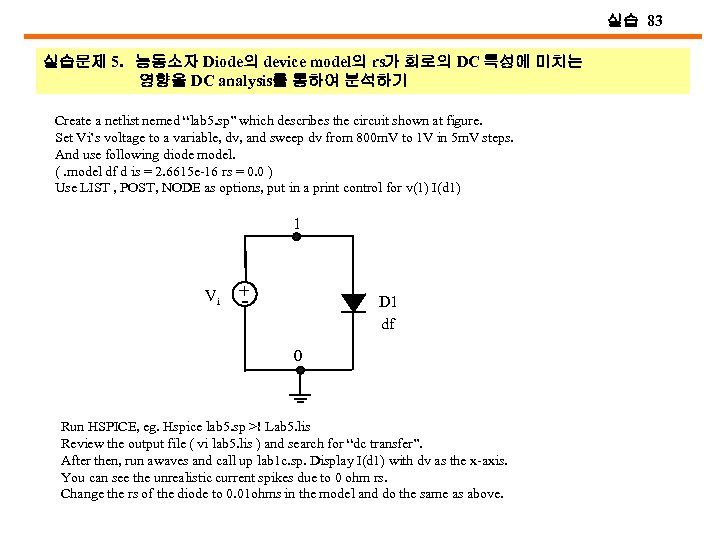

실습 83 실습문제 5. 능동소자 Diode의 device model의 rs가 회로의 DC 특성에 미치는 영향을 DC analysis를 통하여 분석하기 Create a netlist nemed “lab 5. sp” which describes the circuit shown at figure. Set Vi’s voltage to a variable, dv, and sweep dv from 800 m. V to 1 V in 5 m. V steps. And use following diode model. (. model df d is = 2. 6615 e-16 rs = 0. 0 ) Use LIST , POST, NODE as options, put in a print control for v(1) I(d 1) 1 Vi + - D 1 df 0 Run HSPICE, eg. Hspice lab 5. sp >! Lab 5. lis Review the output file ( vi lab 5. lis ) and search for “dc transfer”. After then, run awaves and call up lab 1 c. sp. Display I(d 1) with dv as the x-axis. You can see the unrealistic current spikes due to 0 ohm rs. Change the rs of the diode to 0. 01 ohms in the model and do the same as above.

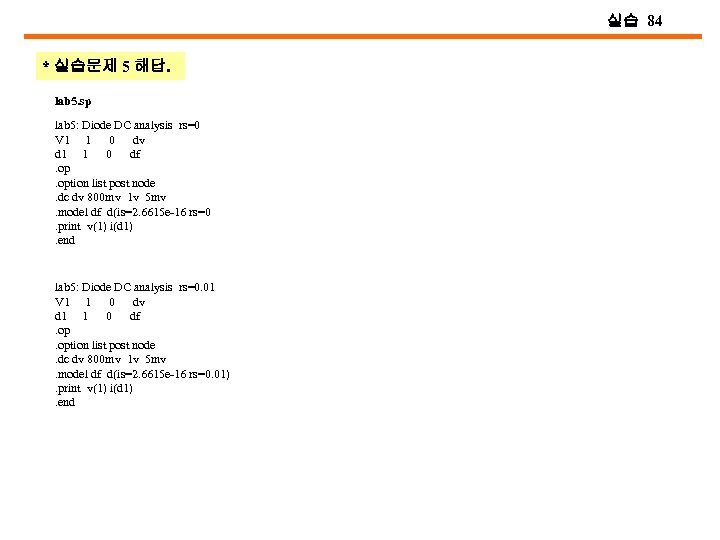

실습 84 * 실습문제 5 해답. lab 5. sp lab 5: Diode DC analysis rs=0 V 1 1 0 dv d 1 1 0 df . option list post node . dc dv 800 mv 1 v 5 mv . model df d(is=2. 6615 e-16 rs=0. print v(1) i(d 1) . end lab 5: Diode DC analysis rs=0. 01 V 1 1 0 dv d 1 1 0 df . option list post node . dc dv 800 mv 1 v 5 mv . model df d(is=2. 6615 e-16 rs=0. 01) . print v(1) i(d 1) . end

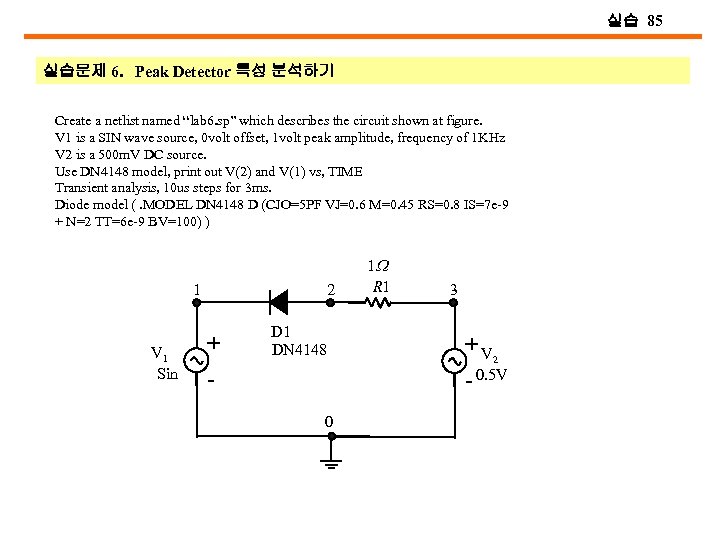

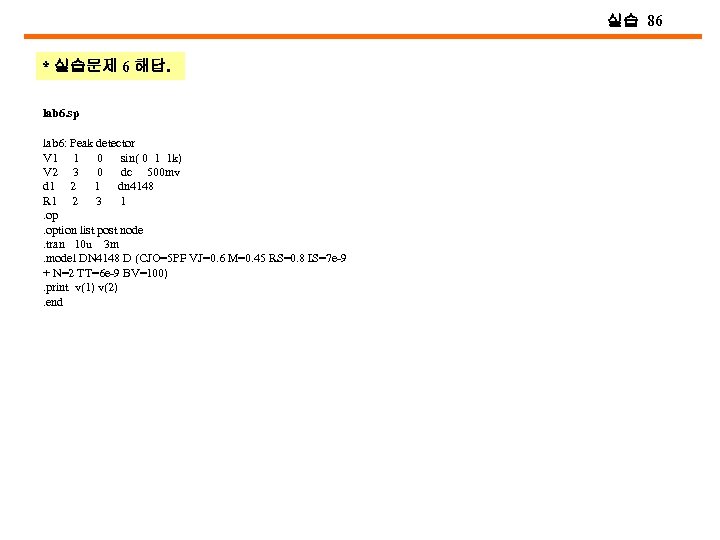

실습 85 실습문제 6. Peak Detector 특성 분석하기 Create a netlist named “lab 6. sp” which describes the circuit shown at figure. V 1 is a SIN wave source, 0 volt offset, 1 volt peak amplitude, frequency of 1 KHz V 2 is a 500 m. V DC source. Use DN 4148 model, print out V(2) and V(1) vs, TIME Transient analysis, 10 us steps for 3 ms. Diode model (. MODEL DN 4148 D (CJO=5 PF VJ=0. 6 M=0. 45 RS=0. 8 IS=7 e-9 + N=2 TT=6 e-9 BV=100) ) 1 V 1 Sin 2 + - D 1 DN 4148 0 1 W R 1 3 + V 2 - 0. 5 V

실습 86 * 실습문제 6 해답. lab 6. sp lab 6: Peak detector V 1 1 0 sin( 0 1 1 k) V 2 3 0 dc 500 mv d 1 2 1 dn 4148 R 1 2 3 1 . option list post node . tran 10 u 3 m . model DN 4148 D (CJO=5 PF VJ=0. 6 M=0. 45 RS=0. 8 IS=7 e-9 + N=2 TT=6 e-9 BV=100) . print v(1) v(2) . end

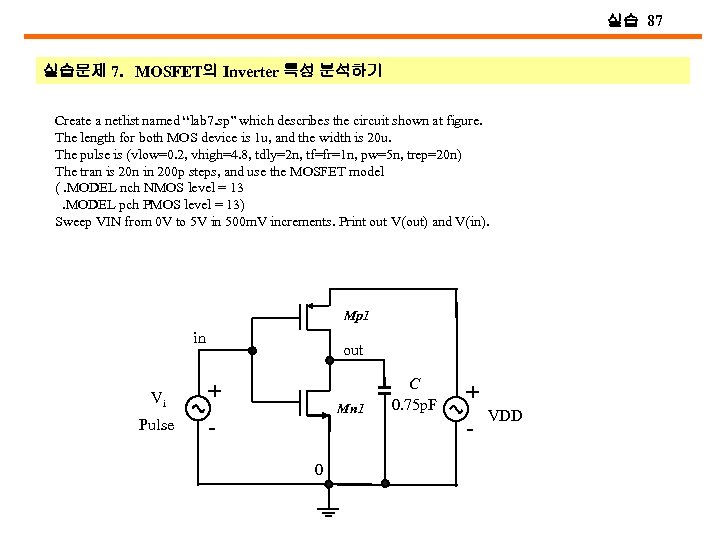

실습 87 실습문제 7. MOSFET의 Inverter 특성 분석하기 Create a netlist named “lab 7. sp” which describes the circuit shown at figure. The length for both MOS device is 1 u, and the width is 20 u. The pulse is (vlow=0. 2, vhigh=4. 8, tdly=2 n, tf=fr=1 n, pw=5 n, trep=20 n) The tran is 20 n in 200 p steps, and use the MOSFET model (. MODEL nch NMOS level = 13 . MODEL pch PMOS level = 13) Sweep VIN from 0 V to 5 V in 500 m. V increments. Print out V(out) and V(in). Mp 1 in Vi Pulse out + - Mn 1 0 C 0. 75 p. F + - VDD

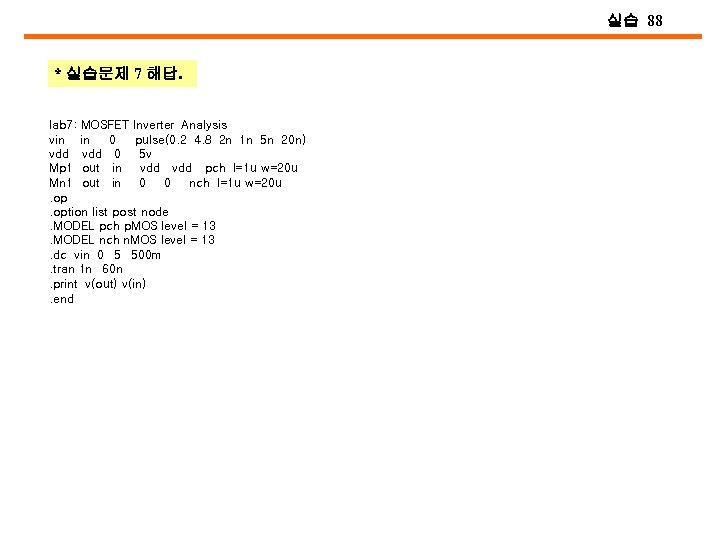

실습 88 * 실습문제 7 해답. lab 7: MOSFET Inverter Analysis vin in 0 pulse(0. 2 4. 8 2 n 1 n 5 n 20 n) vdd 0 5 v Mp 1 out in vdd pch l=1 u w=20 u Mn 1 out in 0 0 nch l=1 u w=20 u. option list post node. MODEL pch p. MOS level = 13 . MODEL nch n. MOS level = 13 . dc vin 0 5 500 m. tran 1 n 60 n. print v(out) v(in). end

실습 89 SPICE 시뮬레이션 실습 (2) 실습 1. Op-amp SPICE 시뮬레이션 따라하기 실습 2. Folded cascode Op-amp SPICE 시뮬레이션 통해 특성 구해보기

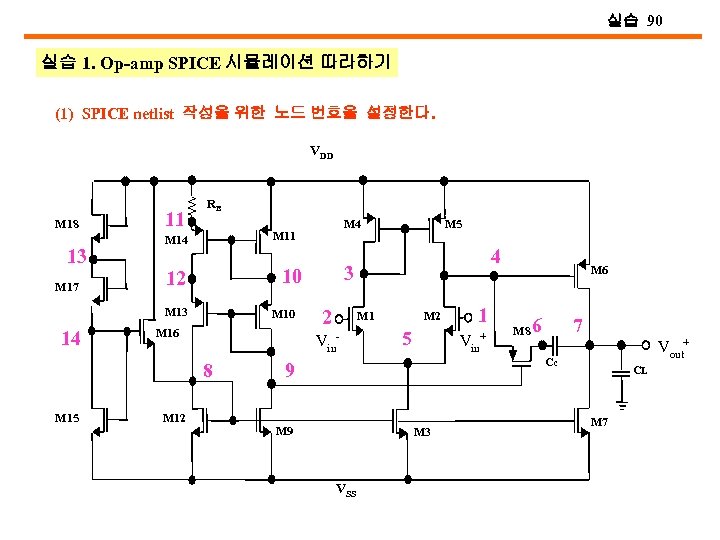

실습 90 실습 1. Op-amp SPICE 시뮬레이션 따라하기 (1) SPICE netlist 작성을 위한 노드 번호을 설정한다. VDD M 18 13 M 17 11 RB M 10 M 16 M 15 M 12 2 4 M 1 Vin- 8 M 5 3 10 12 M 13 14 M 11 M 14 M 2 5 1 Vin+ M 6 M 8 6 7 Vout+ Cc 9 M 3 VSS CL M 7

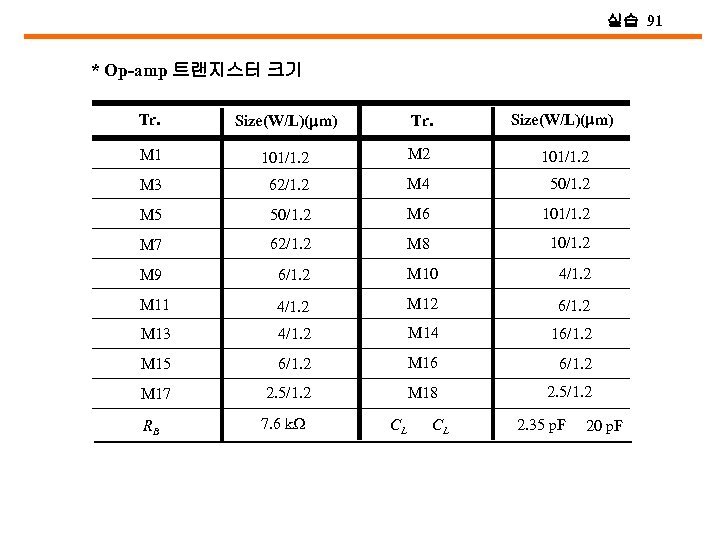

실습 91 * Op-amp 트랜지스터 크기 Tr. Size(W/L)(mm) M 1 101/1. 2 M 2 101/1. 2 M 3 62/1. 2 M 4 50/1. 2 M 5 50/1. 2 M 6 101/1. 2 M 7 62/1. 2 M 8 10/1. 2 M 9 6/1. 2 M 10 4/1. 2 M 11 4/1. 2 M 12 6/1. 2 M 13 4/1. 2 M 14 16/1. 2 M 15 6/1. 2 M 16 6/1. 2 M 17 2. 5/1. 2 M 18 2. 5/1. 2 RB 7. 6 k. W CL CL 2. 35 p. F 20 p. F

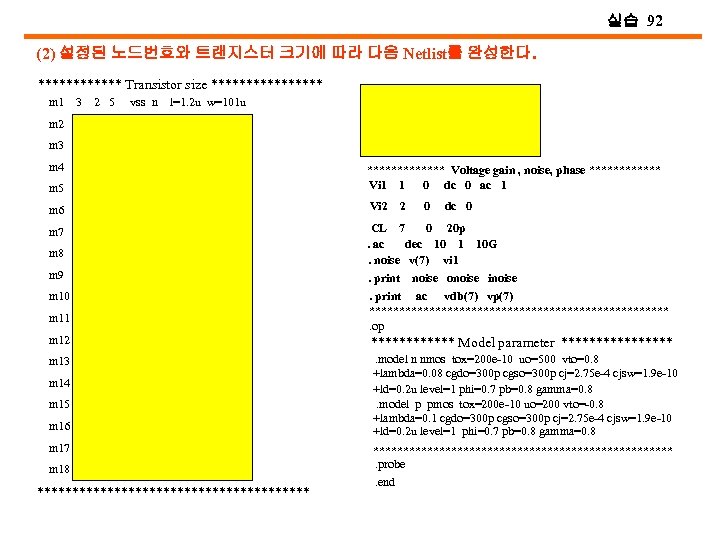

실습 92 (2) 설정된 노드번호와 트랜지스터 크기에 따라 다음 Netlist를 완성한다. ****** Transistor size ******** m 1 3 2 5 vss n l=1. 2 u w=101 u m 2 4 1 5 vss n l=1. 2 u w=101 u m 3 5 8 vss n l=1. 2 u w=62 u m 4 3 3 vdd p l=1. 2 u w=50 u RB vdd 11 7. 6 k Cc 6 7 2. 35 p vdd 0 dc 2. 5 vss 0 dc -2. 5 m 5 4 3 vdd p l=1. 2 u w=50 u ******* Voltage gain , noise, phase ****** Vi 1 1 0 dc 0 ac 1 m 6 7 4 vdd p l=1. 2 u w=101 u Vi 2 m 7 7 8 vss n l=1. 2 u w=62 u CL 7 0 20 p. ac dec 10 1 10 G. noise v(7) vi 1. print noise onoise inoise. print ac vdb(7) vp(7) *************************. op m 8 6 9 4 vdd p l=1. 2 u w=10 u m 9 9 8 vss n l=1. 2 u w=6 u m 10 9 9 10 vdd p l=1. 2 u w=4 u m 11 10 10 vdd p l=1. 2 u w=4 u 2 0 dc 0 m 12 8 8 vss n l=1. 2 u w=6 u ****** Model parameter ******** m 13 8 9 12 vdd p l=1. 2 u w=4 u . model n nmos tox=200 e-10 uo=500 vto=0. 8 +lambda=0. 08 cgdo=300 p cgso=300 p cj=2. 75 e-4 cjsw=1. 9 e-10 +ld=0. 2 u level=1 phi=0. 7 pb=0. 8 gamma=0. 8. model p pmos tox=200 e-10 uo=200 vto=-0. 8 +lambda=0. 1 cgdo=300 p cgso=300 p cj=2. 75 e-4 cjsw=1. 9 e-10 +ld=0. 2 u level=1 phi=0. 7 pb=0. 8 gamma=0. 8 m 14 12 10 11 vdd p l=1. 2 u w=16 u m 15 14 14 vss n l=1. 2 u w=6 u m 16 vdd 14 8 vss n l=1. 2 u w=6 u m 17 13 14 vss n l=150 u w=2. 5 u m 18 vdd 13 vss n l=150 u w=2. 5 u *********************************************. probe. end

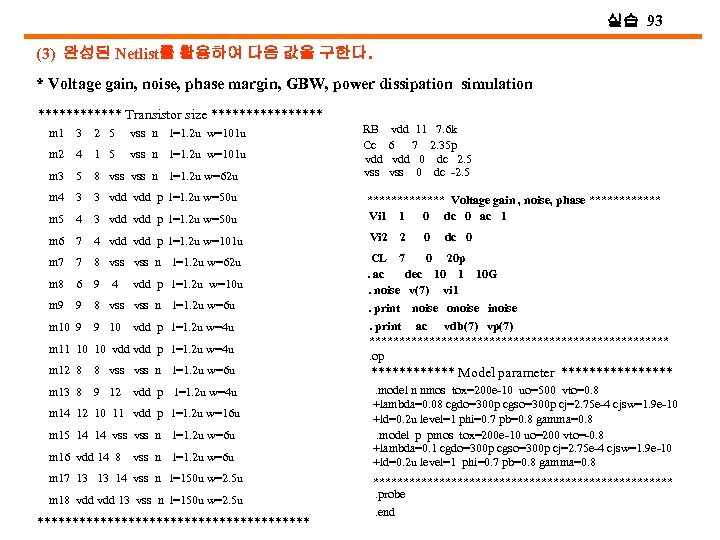

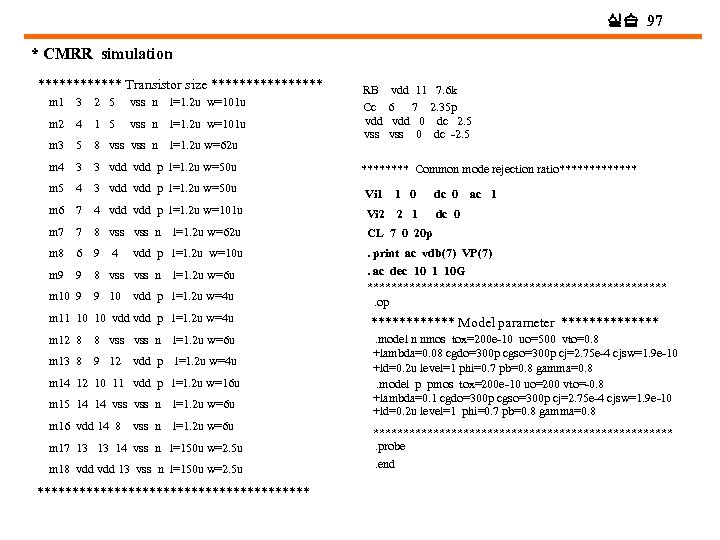

실습 93 (3) 완성된 Netlist를 활용하여 다음 값을 구한다. * Voltage gain, noise, phase margin, GBW, power dissipation simulation ****** Transistor size ******** m 1 3 2 5 vss n l=1. 2 u w=101 u m 2 4 1 5 vss n l=1. 2 u w=101 u m 3 5 8 vss n l=1. 2 u w=62 u m 4 3 3 vdd p l=1. 2 u w=50 u RB vdd 11 7. 6 k Cc 6 7 2. 35 p vdd 0 dc 2. 5 vss 0 dc -2. 5 m 5 4 3 vdd p l=1. 2 u w=50 u ******* Voltage gain , noise, phase ****** Vi 1 1 0 dc 0 ac 1 m 6 7 4 vdd p l=1. 2 u w=101 u Vi 2 m 7 7 8 vss n l=1. 2 u w=62 u CL 7 0 20 p. ac dec 10 1 10 G. noise v(7) vi 1. print noise onoise inoise. print ac vdb(7) vp(7) *************************. op m 8 6 9 4 vdd p l=1. 2 u w=10 u m 9 9 8 vss n l=1. 2 u w=6 u m 10 9 9 10 vdd p l=1. 2 u w=4 u m 11 10 10 vdd p l=1. 2 u w=4 u 2 0 dc 0 m 12 8 8 vss n l=1. 2 u w=6 u ****** Model parameter ******** m 13 8 9 12 vdd p l=1. 2 u w=4 u . model n nmos tox=200 e-10 uo=500 vto=0. 8 +lambda=0. 08 cgdo=300 p cgso=300 p cj=2. 75 e-4 cjsw=1. 9 e-10 +ld=0. 2 u level=1 phi=0. 7 pb=0. 8 gamma=0. 8. model p pmos tox=200 e-10 uo=200 vto=-0. 8 +lambda=0. 1 cgdo=300 p cgso=300 p cj=2. 75 e-4 cjsw=1. 9 e-10 +ld=0. 2 u level=1 phi=0. 7 pb=0. 8 gamma=0. 8 m 14 12 10 11 vdd p l=1. 2 u w=16 u m 15 14 14 vss n l=1. 2 u w=6 u m 16 vdd 14 8 vss n l=1. 2 u w=6 u m 17 13 14 vss n l=150 u w=2. 5 u m 18 vdd 13 vss n l=150 u w=2. 5 u *********************************************. probe. end

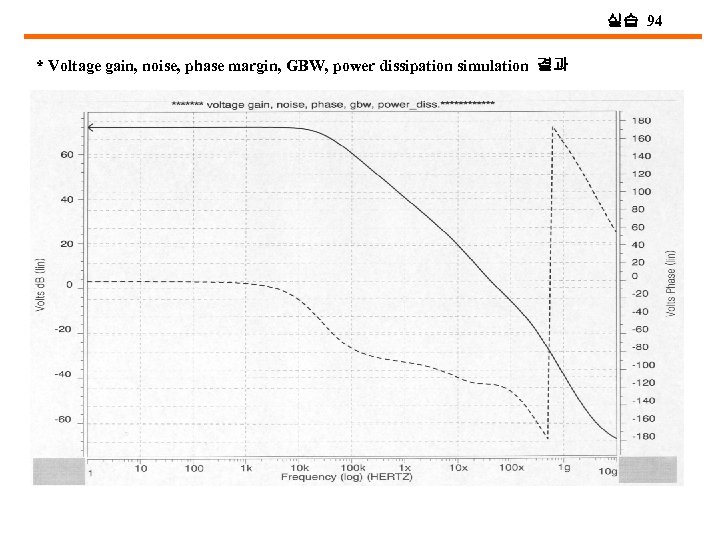

실습 94 * Voltage gain, noise, phase margin, GBW, power dissipation simulation 결과

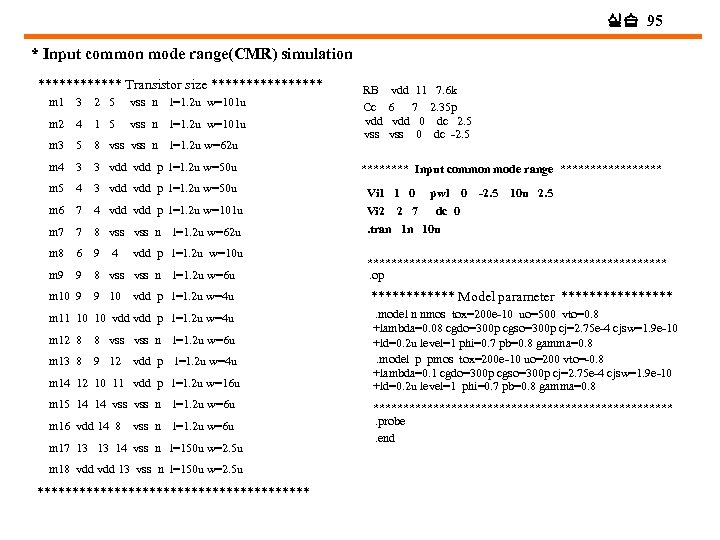

실습 95 * Input common mode range(CMR) simulation ****** Transistor size ******** m 1 3 2 5 vss n l=1. 2 u w=101 u m 2 4 1 5 vss n l=1. 2 u w=101 u m 3 5 8 vss n l=1. 2 u w=62 u m 4 3 3 vdd p l=1. 2 u w=50 u m 5 4 3 vdd p l=1. 2 u w=50 u m 6 7 4 vdd p l=1. 2 u w=101 u m 7 7 8 vss n l=1. 2 u w=62 u m 8 6 9 4 vdd p l=1. 2 u w=10 u m 9 9 8 vss n l=1. 2 u w=6 u RB vdd 11 7. 6 k Cc 6 7 2. 35 p vdd 0 dc 2. 5 vss 0 dc -2. 5 **** Input common mode range ********* Vi 1 1 0 pwl 0 Vi 2 2 7 dc 0. tran 1 n 10 u -2. 5 10 u 2. 5 *************************. op m 10 9 9 10 vdd p l=1. 2 u w=4 u ****** Model parameter ******** m 11 10 10 vdd p l=1. 2 u w=4 u . model n nmos tox=200 e-10 uo=500 vto=0. 8 +lambda=0. 08 cgdo=300 p cgso=300 p cj=2. 75 e-4 cjsw=1. 9 e-10 +ld=0. 2 u level=1 phi=0. 7 pb=0. 8 gamma=0. 8. model p pmos tox=200 e-10 uo=200 vto=-0. 8 +lambda=0. 1 cgdo=300 p cgso=300 p cj=2. 75 e-4 cjsw=1. 9 e-10 +ld=0. 2 u level=1 phi=0. 7 pb=0. 8 gamma=0. 8 m 12 8 8 vss n l=1. 2 u w=6 u m 13 8 9 12 vdd p l=1. 2 u w=4 u m 14 12 10 11 vdd p l=1. 2 u w=16 u m 15 14 14 vss n l=1. 2 u w=6 u m 16 vdd 14 8 vss n l=1. 2 u w=6 u m 17 13 14 vss n l=150 u w=2. 5 u m 18 vdd 13 vss n l=150 u w=2. 5 u *********************************************. probe. end

실습 96 * Input common mode range(CMR) simulation 결과

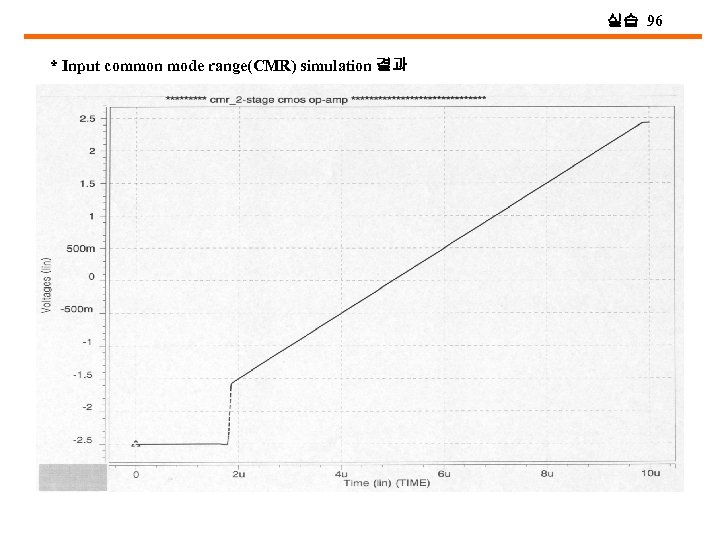

실습 97 * CMRR simulation ****** Transistor size ******** m 1 3 2 5 vss n l=1. 2 u w=101 u m 2 4 1 5 vss n l=1. 2 u w=101 u m 3 5 8 vss n l=1. 2 u w=62 u m 4 3 3 vdd p l=1. 2 u w=50 u RB vdd 11 7. 6 k Cc 6 7 2. 35 p vdd 0 dc 2. 5 vss 0 dc -2. 5 **** Common mode rejection ratio******* m 5 4 3 vdd p l=1. 2 u w=50 u Vi 1 1 0 dc 0 m 6 7 4 vdd p l=1. 2 u w=101 u Vi 2 2 1 dc 0 m 7 7 8 vss n l=1. 2 u w=62 u CL 7 0 20 p m 8 6 9 4 vdd p l=1. 2 u w=10 u m 10 9 9 10 vdd p l=1. 2 u w=4 u . print ac vdb(7) VP(7). ac dec 10 1 10 G *************************. op m 11 10 10 vdd p l=1. 2 u w=4 u ****** Model parameter ******* m 12 8 8 vss n l=1. 2 u w=6 u . model n nmos tox=200 e-10 uo=500 vto=0. 8 +lambda=0. 08 cgdo=300 p cgso=300 p cj=2. 75 e-4 cjsw=1. 9 e-10 +ld=0. 2 u level=1 phi=0. 7 pb=0. 8 gamma=0. 8. model p pmos tox=200 e-10 uo=200 vto=-0. 8 +lambda=0. 1 cgdo=300 p cgso=300 p cj=2. 75 e-4 cjsw=1. 9 e-10 +ld=0. 2 u level=1 phi=0. 7 pb=0. 8 gamma=0. 8 m 9 9 8 vss n l=1. 2 u w=6 u m 13 8 9 12 vdd p l=1. 2 u w=4 u m 14 12 10 11 vdd p l=1. 2 u w=16 u m 15 14 14 vss n l=1. 2 u w=6 u m 16 vdd 14 8 vss n l=1. 2 u w=6 u m 17 13 14 vss n l=150 u w=2. 5 u m 18 vdd 13 vss n l=150 u w=2. 5 u ******************** ac 1 *************************. probe. end

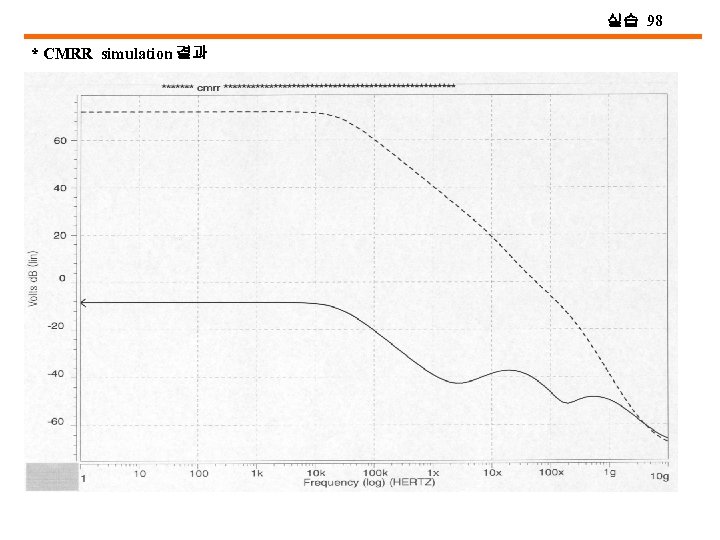

실습 98 * CMRR simulation 결과

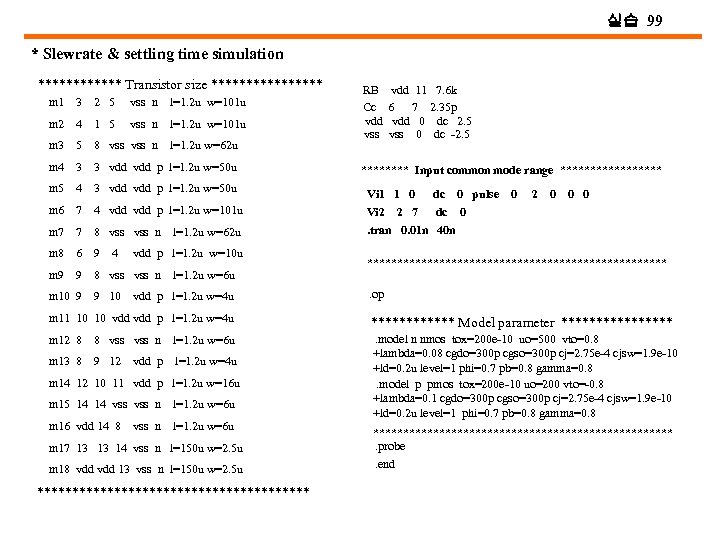

실습 99 * Slewrate & settling time simulation ****** Transistor size ******** m 1 3 2 5 vss n l=1. 2 u w=101 u m 2 4 1 5 vss n l=1. 2 u w=101 u m 3 5 8 vss n l=1. 2 u w=62 u m 4 3 3 vdd p l=1. 2 u w=50 u m 5 4 3 vdd p l=1. 2 u w=50 u m 6 7 4 vdd p l=1. 2 u w=101 u m 7 7 8 vss n l=1. 2 u w=62 u m 8 6 9 4 vdd p l=1. 2 u w=10 u m 9 9 8 vss n l=1. 2 u w=6 u RB vdd 11 7. 6 k Cc 6 7 2. 35 p vdd 0 dc 2. 5 vss 0 dc -2. 5 **** Input common mode range ********* Vi 1 1 0 dc 0 pulse Vi 2 2 7 dc 0. tran 0. 01 n 40 n 0 2 0 0 0 ************************* m 10 9 9 10 vdd p l=1. 2 u w=4 u . op m 11 10 10 vdd p l=1. 2 u w=4 u ****** Model parameter ******** m 12 8 8 vss n l=1. 2 u w=6 u . model n nmos tox=200 e-10 uo=500 vto=0. 8 +lambda=0. 08 cgdo=300 p cgso=300 p cj=2. 75 e-4 cjsw=1. 9 e-10 +ld=0. 2 u level=1 phi=0. 7 pb=0. 8 gamma=0. 8. model p pmos tox=200 e-10 uo=200 vto=-0. 8 +lambda=0. 1 cgdo=300 p cgso=300 p cj=2. 75 e-4 cjsw=1. 9 e-10 +ld=0. 2 u level=1 phi=0. 7 pb=0. 8 gamma=0. 8 m 13 8 9 12 vdd p l=1. 2 u w=4 u m 14 12 10 11 vdd p l=1. 2 u w=16 u m 15 14 14 vss n l=1. 2 u w=6 u m 16 vdd 14 8 vss n l=1. 2 u w=6 u m 17 13 14 vss n l=150 u w=2. 5 u m 18 vdd 13 vss n l=150 u w=2. 5 u *********************************************. probe. end

실습 100 * Slewrate & settling time simulation 결과

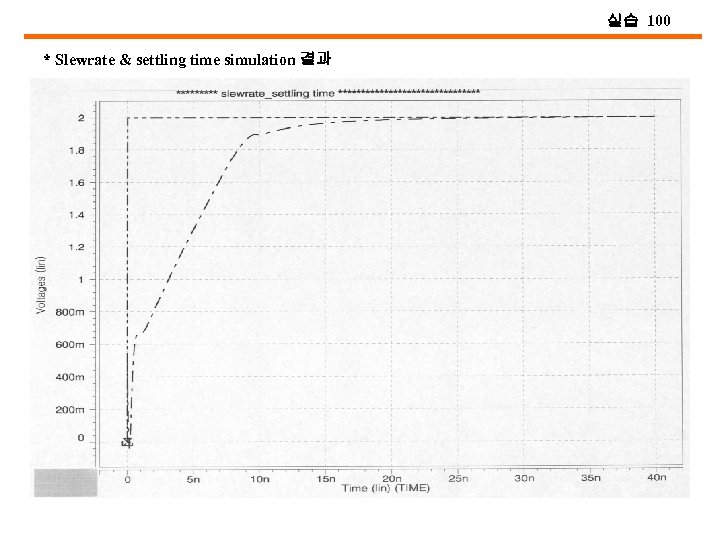

실습 101 * PSRR_Vdd simulation ****** Transistor size ******** m 1 3 2 5 vss n l=1. 2 u w=101 u m 2 4 1 5 vss n l=1. 2 u w=101 u m 3 5 8 vss n l=1. 2 u w=62 u RB vdd 11 7. 6 k Cc 6 7 2. 35 p **** Power supply (Vdd) rejection ratio ***** m 4 3 3 vdd p l=1. 2 u w=50 u vdd 0 dc 2. 5 ac 1 vss 0 dc -2. 5 m 5 4 3 vdd p l=1. 2 u w=50 u Vi 1 1 0 dc 0 m 6 7 4 vdd p l=1. 2 u w=101 u Vi 2 2 0 dc 0 m 7 7 8 vss n l=1. 2 u w=62 u CL 7 0 20 p m 8 6 9 4 vdd p l=1. 2 u w=10 u . print ac vdb(7) Vp(7). ac dec 10 1 10 G *************************. op m 9 9 8 vss n l=1. 2 u w=6 u m 10 9 9 10 vdd p l=1. 2 u w=4 u m 11 10 10 vdd p l=1. 2 u w=4 u ****** Model parameter ******** m 12 8 8 vss n l=1. 2 u w=6 u . model n nmos tox=200 e-10 uo=500 vto=0. 8 +lambda=0. 08 cgdo=300 p cgso=300 p cj=2. 75 e-4 cjsw=1. 9 e-10 +ld=0. 2 u level=1 phi=0. 7 pb=0. 8 gamma=0. 8. model p pmos tox=200 e-10 uo=200 vto=-0. 8 +lambda=0. 1 cgdo=300 p cgso=300 p cj=2. 75 e-4 cjsw=1. 9 e-10 +ld=0. 2 u level=1 phi=0. 7 pb=0. 8 gamma=0. 8 m 13 8 9 12 vdd p l=1. 2 u w=4 u m 14 12 10 11 vdd p l=1. 2 u w=16 u m 15 14 14 vss n l=1. 2 u w=6 u m 16 vdd 14 8 vss n l=1. 2 u w=6 u m 17 13 14 vss n l=150 u w=2. 5 u m 18 vdd 13 vss n l=150 u w=2. 5 u *********************************************. probe. end

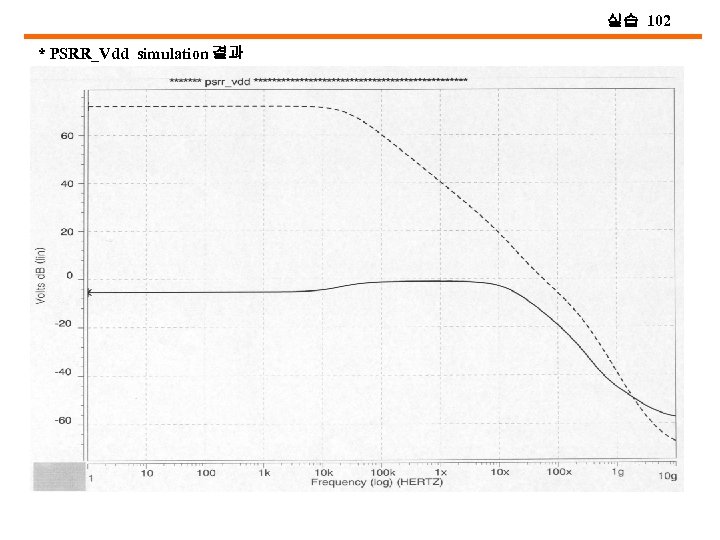

실습 102 * PSRR_Vdd simulation 결과

실습 103 * PSRR_Vss simulation ****** Transistor size ******** m 1 3 2 5 vss n l=1. 2 u w=101 u m 2 4 1 5 vss n l=1. 2 u w=101 u m 3 5 8 vss n l=1. 2 u w=62 u RB vdd 11 7. 6 k Cc 6 7 2. 35 p **** Power supply (Vss) rejection ratio ***** m 4 3 3 vdd p l=1. 2 u w=50 u vdd 0 dc 2. 5 vss 0 dc -2. 5 ac 1 m 5 4 3 vdd p l=1. 2 u w=50 u Vi 1 1 0 dc 0 m 6 7 4 vdd p l=1. 2 u w=101 u Vi 2 2 0 dc 0 m 7 7 8 vss n l=1. 2 u w=62 u CL 7 0 20 p m 8 6 9 4 vdd p l=1. 2 u w=10 u . print ac vdb(7) Vp(7). ac dec 10 1 10 G *************************. op m 9 9 8 vss n l=1. 2 u w=6 u m 10 9 9 10 vdd p l=1. 2 u w=4 u m 11 10 10 vdd p l=1. 2 u w=4 u ****** Model parameter ******** m 12 8 8 vss n l=1. 2 u w=6 u . model n nmos tox=200 e-10 uo=500 vto=0. 8 +lambda=0. 08 cgdo=300 p cgso=300 p cj=2. 75 e-4 cjsw=1. 9 e-10 +ld=0. 2 u level=1 phi=0. 7 pb=0. 8 gamma=0. 8. model p pmos tox=200 e-10 uo=200 vto=-0. 8 +lambda=0. 1 cgdo=300 p cgso=300 p cj=2. 75 e-4 cjsw=1. 9 e-10 +ld=0. 2 u level=1 phi=0. 7 pb=0. 8 gamma=0. 8 m 13 8 9 12 vdd p l=1. 2 u w=4 u m 14 12 10 11 vdd p l=1. 2 u w=16 u m 15 14 14 vss n l=1. 2 u w=6 u m 16 vdd 14 8 vss n l=1. 2 u w=6 u m 17 13 14 vss n l=150 u w=2. 5 u m 18 vdd 13 vss n l=150 u w=2. 5 u *********************************************. probe. end

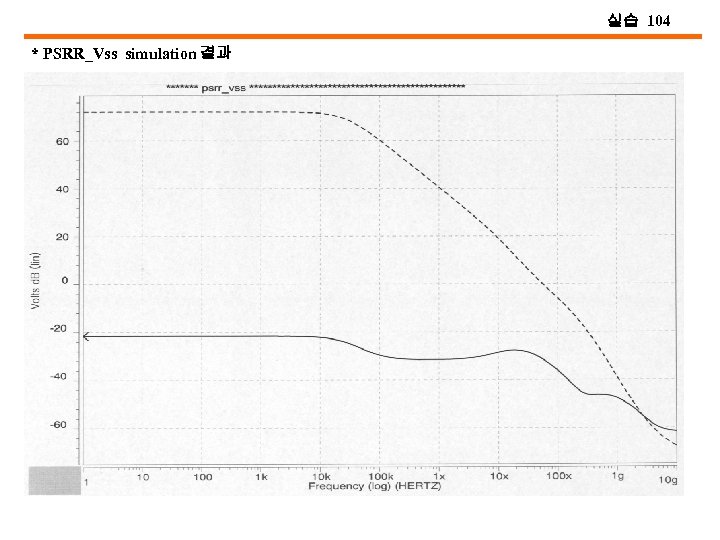

실습 104 * PSRR_Vss simulation 결과

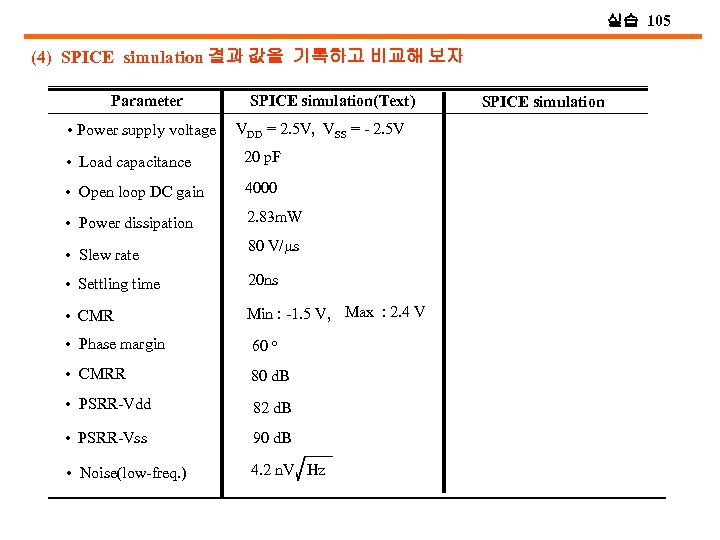

실습 105 (4) SPICE simulation 결과 값을 기록하고 비교해 보자 Parameter • Power supply voltage SPICE simulation(Text) VDD = 2. 5 V, VSS = - 2. 5 V • Load capacitance 20 p. F • Open loop DC gain 4000 • Power dissipation 2. 83 m. W • Slew rate 80 V/ms • Settling time 20 ns • CMR Min : -1. 5 V, Max : 2. 4 V • Phase margin 60 o • CMRR 80 d. B • PSRR-Vdd 82 d. B • PSRR-Vss 90 d. B • Noise(low-freq. ) 4. 2 n. V Hz SPICE simulation

실습 106 실습 2. SPICE Simulation을 통하여 Folded cascode Op-Amp의 특성을 조사하시오 10 VDD 12 IB M 4 4 25 m. A M 13 M 14 M 7 M 6 13 1 Vi 1 14 M 16 5 13 M 12 15 M 17 M 5 M 1 M 2 3 2 6 Vi 2 B M 8 7 M 9 9 M 3 VSS 11 M 10 8 M 11 CL=10 p. F

실습 107 Netlist ************************** m 1 W=120 u L=1. 2 u m 2 W=120 u L=1. 2 u m 3 W=32 u L=1. 2 u m 4 W=24 u L=1. 2 u m 5 W=24 u L=1. 2 u m 6 W=40 u L=1. 2 u m 7 W=40 u L=1. 2 u m 8 W=12 u L=1. 2 u m 9 W=12 u L=1. 2 u m 10 W=4 u L=1. 2 u m 11 W=4 u L=1. 2 u m 12 W=4 u L=3 u m 13 W=8 u L=1. 2 u m 14 W=8 u L=1. 2 u m 15 W=8 u L=1. 2 u m 16 W=8 u L=1. 2 u m 17 W=8 u L=1. 2 u ? CL 7 0 10 p ************************** Vi 1 1 0 dc 0 ac 0 Vi 2 2 0 dc 0 ac 1 Vdd 10 0 dc 2. 5 Vss 11 0 dc -2. 5 IB 10 14 25 u. A ************************** . dc vi 1 -5 m 10 m 0. 1 m. print dc v(7) . ac dec 10 1 1 G. probe vdb(7) vp(7). op ****** Model parameter ***********. model n nmos tox=200 e-10 uo=500 vto=0. 8 +lambda=0. 08 cgdo=300 p cgso=300 p cj=2. 75 e-4 cjsw=1. 9 e-10 +ld=0. 2 u level=1 phi=0. 7 pb=0. 8 gamma=0. 8. model p pmos tox=200 e-10 uo=200 vto=-0. 8 +lambda=0. 1 cgdo=300 p cgso=300 p cj=2. 75 e-4 cjsw=1. 9 e-10 +ld=0. 2 u level=1 phi=0. 7 pb=0. 8 gamma=0. 8 *************************. end

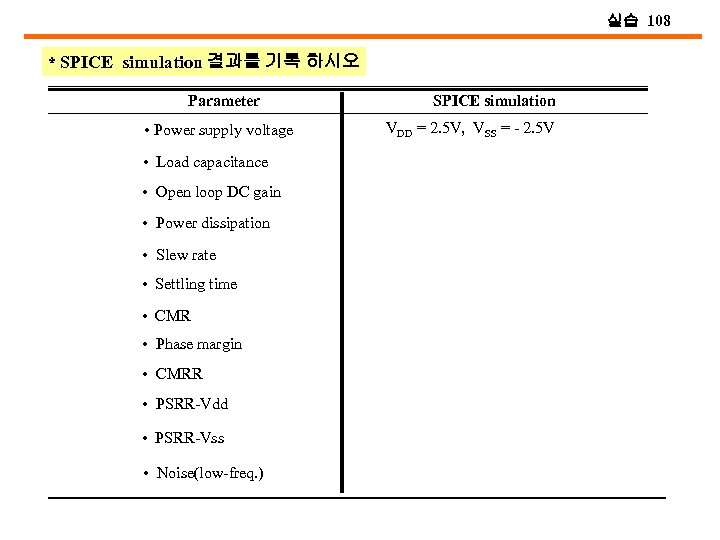

실습 108 * SPICE simulation 결과를 기록 하시오 Parameter • Power supply voltage • Load capacitance • Open loop DC gain • Power dissipation • Slew rate • Settling time • CMR • Phase margin • CMRR • PSRR-Vdd • PSRR-Vss • Noise(low-freq. ) SPICE simulation VDD = 2. 5 V, VSS = - 2. 5 V

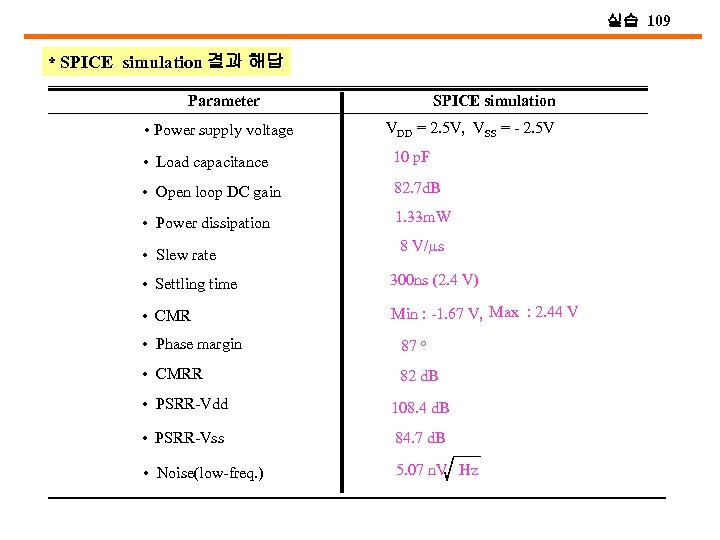

실습 109 * SPICE simulation 결과 해답 Parameter • Power supply voltage SPICE simulation VDD = 2. 5 V, VSS = - 2. 5 V • Load capacitance 10 p. F • Open loop DC gain 82. 7 d. B • Power dissipation 1. 33 m. W • Slew rate 8 V/ms • Settling time 300 ns (2. 4 V) • CMR Min : -1. 67 V, Max : 2. 44 V • Phase margin 87 o • CMRR 82 d. B • PSRR-Vdd 108. 4 d. B • PSRR-Vss 84. 7 d. B • Noise(low-freq. ) 5. 07 n. V Hz

![실습 110 [ 참고 문헌 ] 1. 박홍준 “CMOS 아날로그 집적회로 설계”, 시스마 프레스, 실습 110 [ 참고 문헌 ] 1. 박홍준 “CMOS 아날로그 집적회로 설계”, 시스마 프레스,](https://present5.com/presentation/f7b7944291c64c5c02b677b74a890756/image-111.jpg)

실습 110 [ 참고 문헌 ] 1. 박홍준 “CMOS 아날로그 집적회로 설계”, 시스마 프레스, 1999. 2. B. Razavi “Design of Analog CMOS Integrated Circuits” , 2000. 3. P. E. Allen, D. R. Holberg “CMOS analog circuit design” , 1987. 4. 반도체 설계 교육센터 “ Analog IC design” , 1997. 5. IDEC Star-HSPICE 공개 강좌 , Davan Tech. Co. 1999.

f7b7944291c64c5c02b677b74a890756.ppt