0e923c8159162304f52838a546cf9d64.ppt

- Количество слайдов: 20

High-Level Modeling General-Purpose Languages, High-Level Synthesis John Sanguinetti 1

High-Level Modeling General-Purpose Languages, High-Level Synthesis John Sanguinetti 1

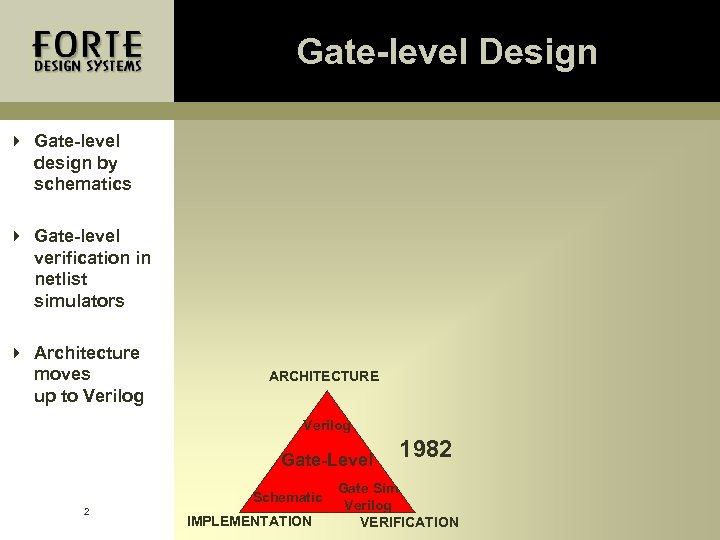

Gate-level Design 4 Gate-level design by schematics 4 Gate-level verification in netlist simulators 4 Architecture moves up to Verilog ARCHITECTURE Verilog Gate-Level Schematic 2 IMPLEMENTATION 1982 Gate Sim Verilog VERIFICATION

Gate-level Design 4 Gate-level design by schematics 4 Gate-level verification in netlist simulators 4 Architecture moves up to Verilog ARCHITECTURE Verilog Gate-Level Schematic 2 IMPLEMENTATION 1982 Gate Sim Verilog VERIFICATION

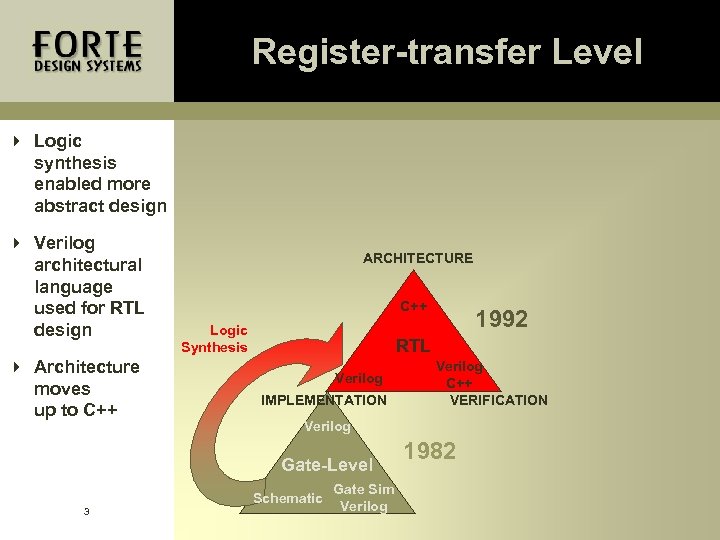

Register-transfer Level 4 Logic synthesis enabled more abstract design 4 Verilog architectural language used for RTL design 4 Architecture moves up to C++ ARCHITECTURE C++ Logic Synthesis RTL Verilog IMPLEMENTATION Verilog C++ VERIFICATION Verilog Gate-Level Schematic 3 1992 Gate Sim Verilog 1982

Register-transfer Level 4 Logic synthesis enabled more abstract design 4 Verilog architectural language used for RTL design 4 Architecture moves up to C++ ARCHITECTURE C++ Logic Synthesis RTL Verilog IMPLEMENTATION Verilog C++ VERIFICATION Verilog Gate-Level Schematic 3 1992 Gate Sim Verilog 1982

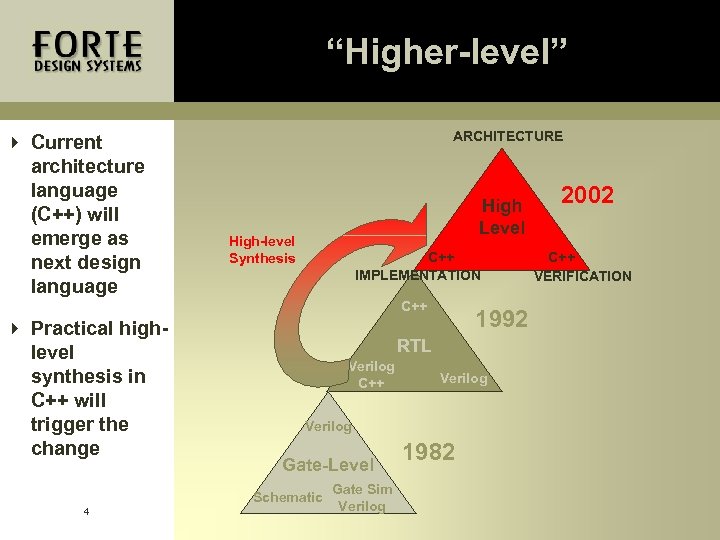

“Higher-level” 4 Current architecture language (C++) will emerge as next design language ARCHITECTURE High Level High-level Synthesis C++ IMPLEMENTATION C++ 4 Practical highlevel synthesis in C++ will trigger the change RTL Verilog C++ Verilog Gate-Level Schematic 4 1992 Gate Sim Verilog 1982 2002 C++ VERIFICATION

“Higher-level” 4 Current architecture language (C++) will emerge as next design language ARCHITECTURE High Level High-level Synthesis C++ IMPLEMENTATION C++ 4 Practical highlevel synthesis in C++ will trigger the change RTL Verilog C++ Verilog Gate-Level Schematic 4 1992 Gate Sim Verilog 1982 2002 C++ VERIFICATION

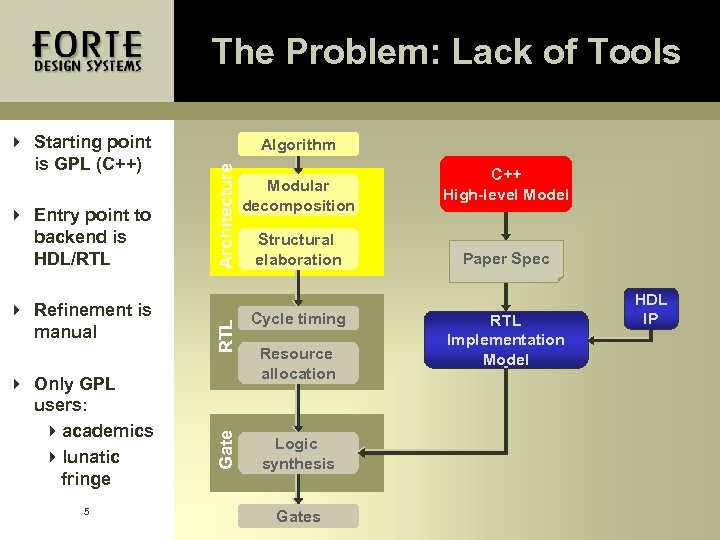

The Problem: Lack of Tools 4 Refinement is manual 4 Only GPL users: 4 academics 4 lunatic fringe 5 Architecture RTL 4 Entry point to backend is HDL/RTL Algorithm Gate 4 Starting point is GPL (C++) Modular decomposition Structural elaboration Cycle timing Resource allocation Logic synthesis Gates C++ High-level Model Paper Spec RTL Implementation Model HDL IP

The Problem: Lack of Tools 4 Refinement is manual 4 Only GPL users: 4 academics 4 lunatic fringe 5 Architecture RTL 4 Entry point to backend is HDL/RTL Algorithm Gate 4 Starting point is GPL (C++) Modular decomposition Structural elaboration Cycle timing Resource allocation Logic synthesis Gates C++ High-level Model Paper Spec RTL Implementation Model HDL IP

GPL candidates 4 Spec. C 4 Handle. C 4 Java 4 C++/Cynlib 4 C++/System. C 4 Extended System. C 4 We’ve made good progress 6

GPL candidates 4 Spec. C 4 Handle. C 4 Java 4 C++/Cynlib 4 C++/System. C 4 Extended System. C 4 We’ve made good progress 6

HLS: The Promise 4 High-level Synthesis 4 Enables higher levels of design abstraction 4 Connects the starting point with the ending point 4 Allows architectural exploration 4 Eases technology process migration 4 Achieves better results with less effort 4 Enables faster simulation and design debugging at the behavioral level 7

HLS: The Promise 4 High-level Synthesis 4 Enables higher levels of design abstraction 4 Connects the starting point with the ending point 4 Allows architectural exploration 4 Eases technology process migration 4 Achieves better results with less effort 4 Enables faster simulation and design debugging at the behavioral level 7

HLS: The Experience 4 Behavioral synthesis was not successful 4 QOR marginal 4 Hard to use, non-intuitive 4 Results nearly impossible to verify 4 Poisoned the market 4 What went wrong? 4 Started with the wrong input 4 Point tool solution for a design flow problem 8

HLS: The Experience 4 Behavioral synthesis was not successful 4 QOR marginal 4 Hard to use, non-intuitive 4 Results nearly impossible to verify 4 Poisoned the market 4 What went wrong? 4 Started with the wrong input 4 Point tool solution for a design flow problem 8

HLS: The Future is Now … 4 High-level Synthesis 4 We have the right starting point 4 We can use a common test bench 4 We can keep the interfaces constant 4 We can produce RTL which meets timing constraints 9

HLS: The Future is Now … 4 High-level Synthesis 4 We have the right starting point 4 We can use a common test bench 4 We can keep the interfaces constant 4 We can produce RTL which meets timing constraints 9

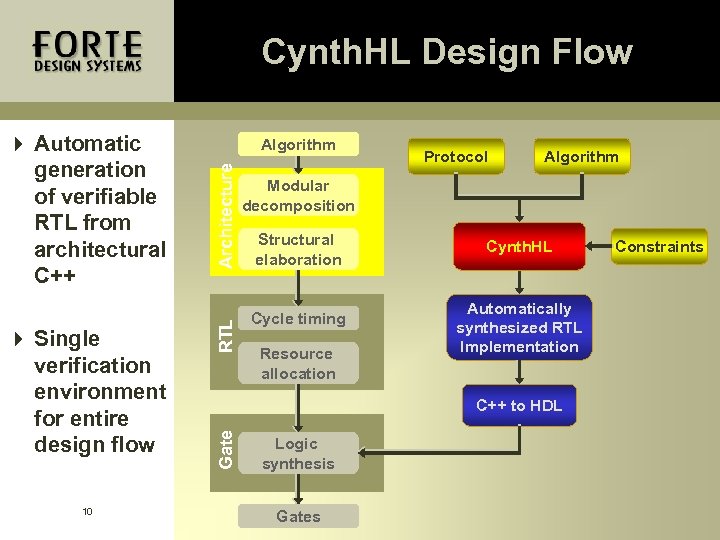

Cynth. HL Design Flow 10 Architecture RTL 4 Single verification environment for entire design flow Algorithm Protocol Algorithm Modular decomposition Structural elaboration Cycle timing Resource allocation Cynth. HL Automatically synthesized RTL Implementation C++ to HDL Gate 4 Automatic generation of verifiable RTL from architectural C++ Logic synthesis Gates Constraints

Cynth. HL Design Flow 10 Architecture RTL 4 Single verification environment for entire design flow Algorithm Protocol Algorithm Modular decomposition Structural elaboration Cycle timing Resource allocation Cynth. HL Automatically synthesized RTL Implementation C++ to HDL Gate 4 Automatic generation of verifiable RTL from architectural C++ Logic synthesis Gates Constraints

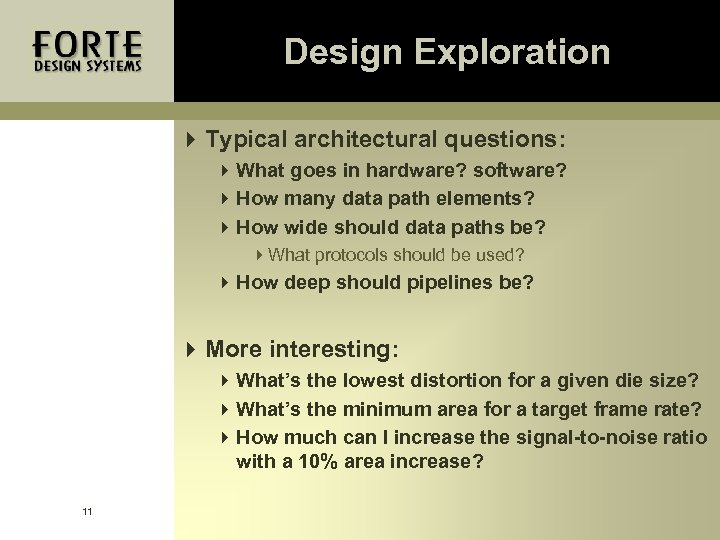

Design Exploration 4 Typical architectural questions: 4 What goes in hardware? software? 4 How many data path elements? 4 How wide should data paths be? 4 What protocols should be used? 4 How deep should pipelines be? 4 More interesting: 4 What’s the lowest distortion for a given die size? 4 What’s the minimum area for a target frame rate? 4 How much can I increase the signal-to-noise ratio with a 10% area increase? 11

Design Exploration 4 Typical architectural questions: 4 What goes in hardware? software? 4 How many data path elements? 4 How wide should data paths be? 4 What protocols should be used? 4 How deep should pipelines be? 4 More interesting: 4 What’s the lowest distortion for a given die size? 4 What’s the minimum area for a target frame rate? 4 How much can I increase the signal-to-noise ratio with a 10% area increase? 11

Design Exploration 4 These are all speed vs. area tradeoffs 4 Speed: latency, throughput 4 Area: how much parallel hardware 4 Answers aren’t available until RTL has been produced 4 Most answers require multiple implementation data points => Evaluating an architectural decision is very expensive 12

Design Exploration 4 These are all speed vs. area tradeoffs 4 Speed: latency, throughput 4 Area: how much parallel hardware 4 Answers aren’t available until RTL has been produced 4 Most answers require multiple implementation data points => Evaluating an architectural decision is very expensive 12

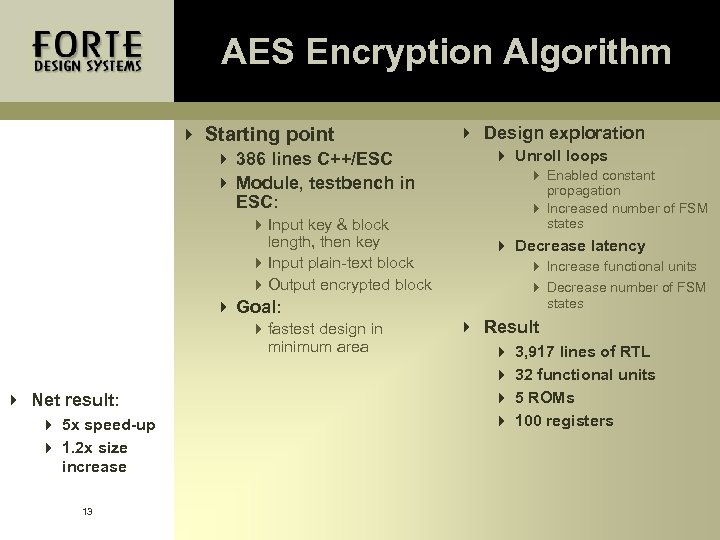

AES Encryption Algorithm 4 Starting point 4 386 lines C++/ESC 4 Module, testbench in ESC: 4 Input key & block length, then key 4 Input plain-text block 4 Output encrypted block 4 Design exploration 4 Unroll loops 4 Enabled constant propagation 4 Increased number of FSM states 4 Decrease latency 4 Increase functional units 4 Decrease number of FSM states 4 Goal: 4 fastest design in minimum area 4 Net result: 4 5 x speed-up 4 1. 2 x size increase 13 4 Result 4 4 3, 917 lines of RTL 32 functional units 5 ROMs 100 registers

AES Encryption Algorithm 4 Starting point 4 386 lines C++/ESC 4 Module, testbench in ESC: 4 Input key & block length, then key 4 Input plain-text block 4 Output encrypted block 4 Design exploration 4 Unroll loops 4 Enabled constant propagation 4 Increased number of FSM states 4 Decrease latency 4 Increase functional units 4 Decrease number of FSM states 4 Goal: 4 fastest design in minimum area 4 Net result: 4 5 x speed-up 4 1. 2 x size increase 13 4 Result 4 4 3, 917 lines of RTL 32 functional units 5 ROMs 100 registers

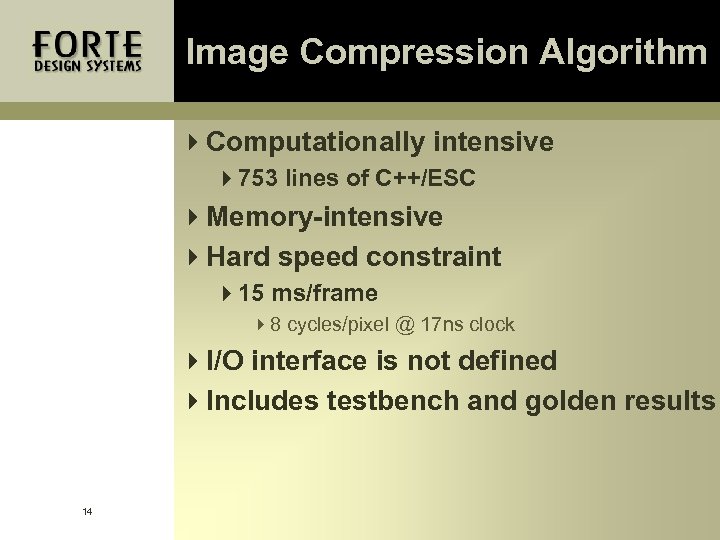

Image Compression Algorithm 4 Computationally intensive 4753 lines of C++/ESC 4 Memory-intensive 4 Hard speed constraint 415 ms/frame 48 cycles/pixel @ 17 ns clock 4 I/O interface is not defined 4 Includes testbench and golden results 14

Image Compression Algorithm 4 Computationally intensive 4753 lines of C++/ESC 4 Memory-intensive 4 Hard speed constraint 415 ms/frame 48 cycles/pixel @ 17 ns clock 4 I/O interface is not defined 4 Includes testbench and golden results 14

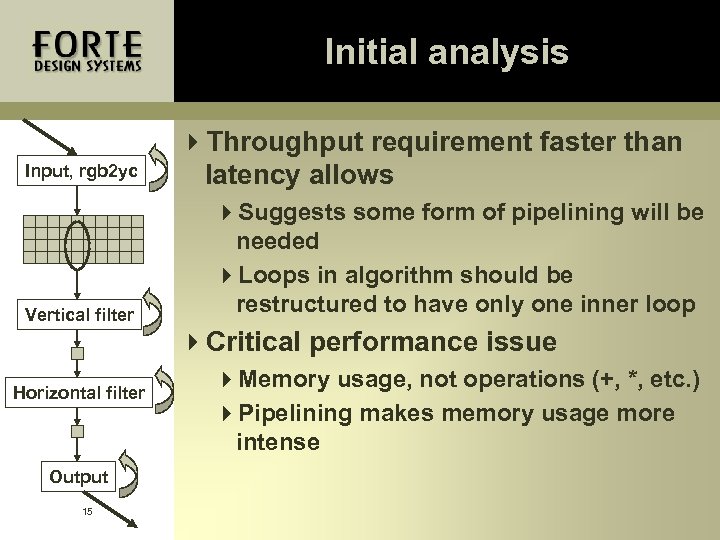

Initial analysis Input, rgb 2 yc Vertical filter 4 Throughput requirement faster than latency allows 4 Suggests some form of pipelining will be needed 4 Loops in algorithm should be restructured to have only one inner loop 4 Critical performance issue Horizontal filter Output 15 4 Memory usage, not operations (+, *, etc. ) 4 Pipelining makes memory usage more intense

Initial analysis Input, rgb 2 yc Vertical filter 4 Throughput requirement faster than latency allows 4 Suggests some form of pipelining will be needed 4 Loops in algorithm should be restructured to have only one inner loop 4 Critical performance issue Horizontal filter Output 15 4 Memory usage, not operations (+, *, etc. ) 4 Pipelining makes memory usage more intense

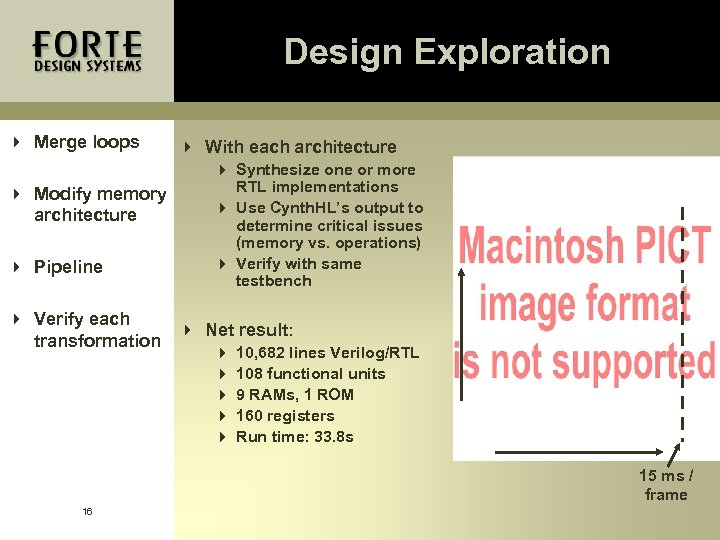

Design Exploration 4 Merge loops 4 Modify memory architecture 4 Pipeline 4 With each architecture 4 Synthesize one or more RTL implementations 4 Use Cynth. HL’s output to determine critical issues (memory vs. operations) 4 Verify with same testbench 4 Verify each 4 Net result: transformation 4 4 4 10, 682 lines Verilog/RTL 108 functional units 9 RAMs, 1 ROM 160 registers Run time: 33. 8 s 15 ms / frame 16

Design Exploration 4 Merge loops 4 Modify memory architecture 4 Pipeline 4 With each architecture 4 Synthesize one or more RTL implementations 4 Use Cynth. HL’s output to determine critical issues (memory vs. operations) 4 Verify with same testbench 4 Verify each 4 Net result: transformation 4 4 4 10, 682 lines Verilog/RTL 108 functional units 9 RAMs, 1 ROM 160 registers Run time: 33. 8 s 15 ms / frame 16

Synergy 4 General-purpose programming language 4 High-level synthesis 4 4 System. C Together, high-level design is a reality Separately, they are just curiosities + Cynth. HL = High-level Design 17

Synergy 4 General-purpose programming language 4 High-level synthesis 4 4 System. C Together, high-level design is a reality Separately, they are just curiosities + Cynth. HL = High-level Design 17

High-Level Modeling General-Purpose Languages, High-Level Synthesis John Sanguinetti 18

High-Level Modeling General-Purpose Languages, High-Level Synthesis John Sanguinetti 18

Cynth. HL Product Status 4 Currently in Beta 4 Beta released January 2002 4 Available Today – Everything you need: 4 Synthesis to “correct gates” 4 Design exploration 4 Predictable timing helps timing closure 4 Beta period being used to improve usability in “real world” design and verification flows 4 Official product announcement 2 H 2002 19

Cynth. HL Product Status 4 Currently in Beta 4 Beta released January 2002 4 Available Today – Everything you need: 4 Synthesis to “correct gates” 4 Design exploration 4 Predictable timing helps timing closure 4 Beta period being used to improve usability in “real world” design and verification flows 4 Official product announcement 2 H 2002 19

Integrated Design and Verification Environment 4 System-level model used for verification 4 Spend time at the algorithmic level to “get it right” 4 Reuse verification environment at lower levels 4 Same TB used for algorithm and synthesized RTL 4 System-level model used for design 4 Once the architecture is verified, automatically create RTL implementation(s) 4 Explore trade-offs between design goals by creating multiple implementations 4 Automated path to CORRECT gates 20

Integrated Design and Verification Environment 4 System-level model used for verification 4 Spend time at the algorithmic level to “get it right” 4 Reuse verification environment at lower levels 4 Same TB used for algorithm and synthesized RTL 4 System-level model used for design 4 Once the architecture is verified, automatically create RTL implementation(s) 4 Explore trade-offs between design goals by creating multiple implementations 4 Automated path to CORRECT gates 20